Изобретение относится к вычислительной технике, позволяет выполнять операции цифровой двумерной свертки (1ЩС) и скользящего выравнивания гистограмм (СВГ) над двумерными цифровыми полями (в частности, изображениями) и может быть использовано при построении специализированных вычислительных систем, функционирующих в реальном масштабе времени.

Целью изобретения является повышение производительности устройства.

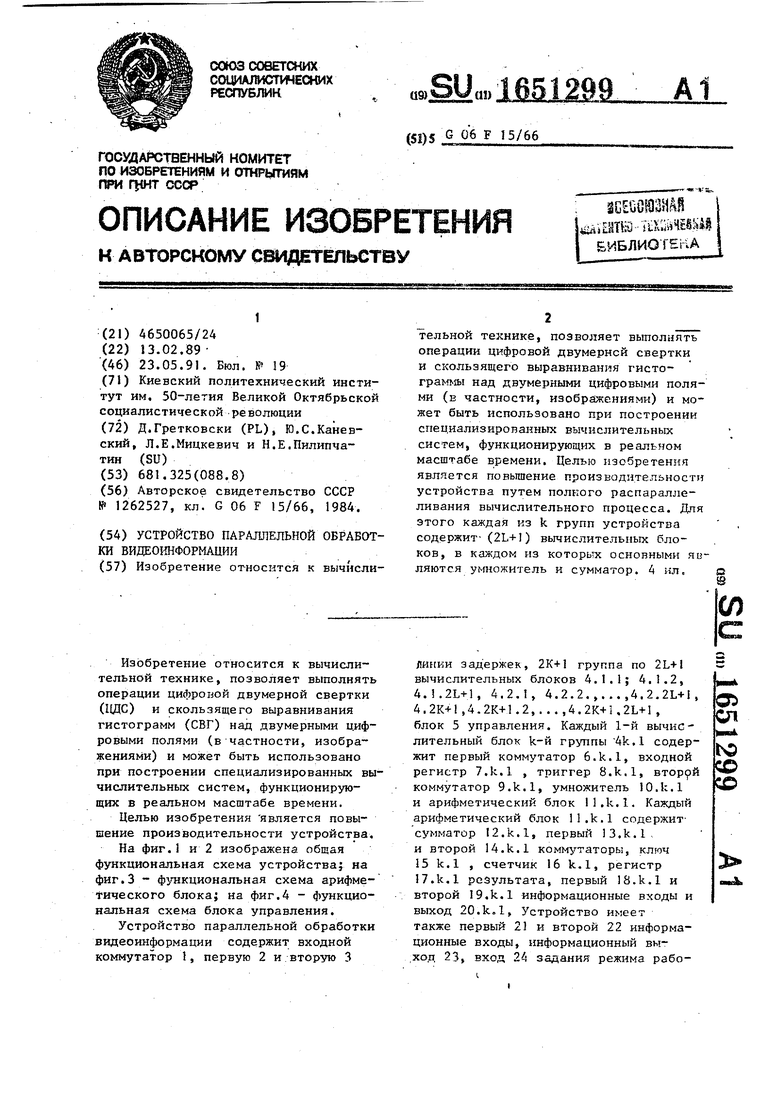

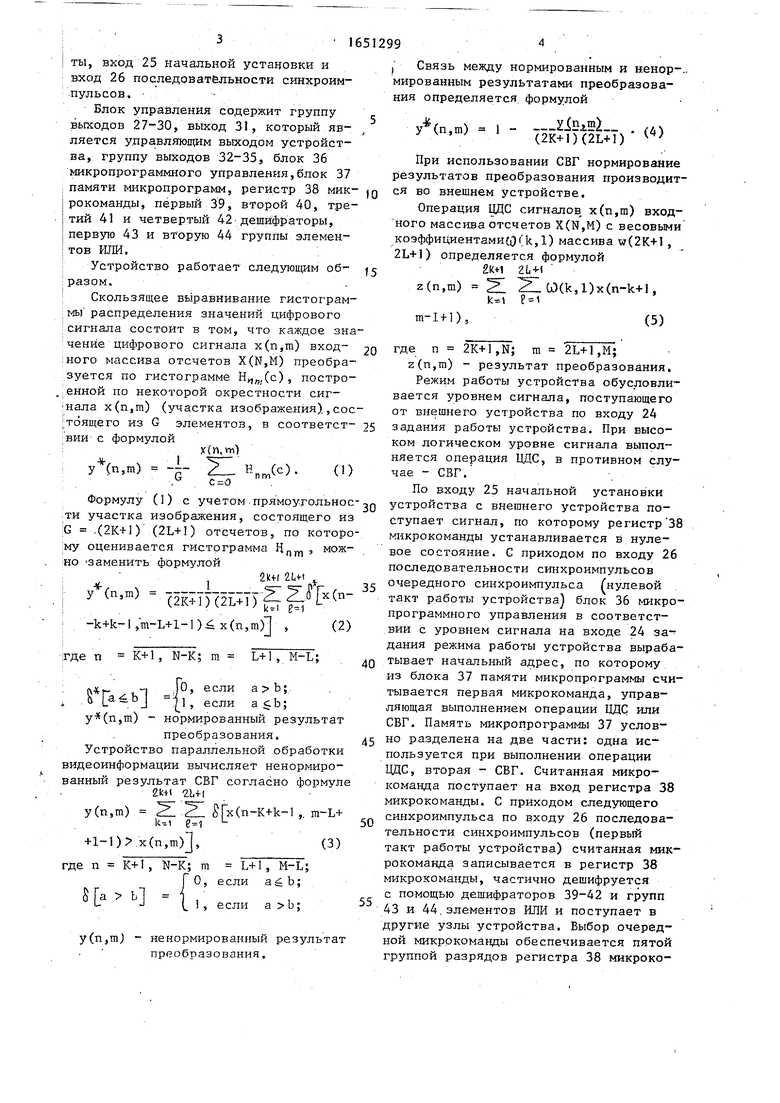

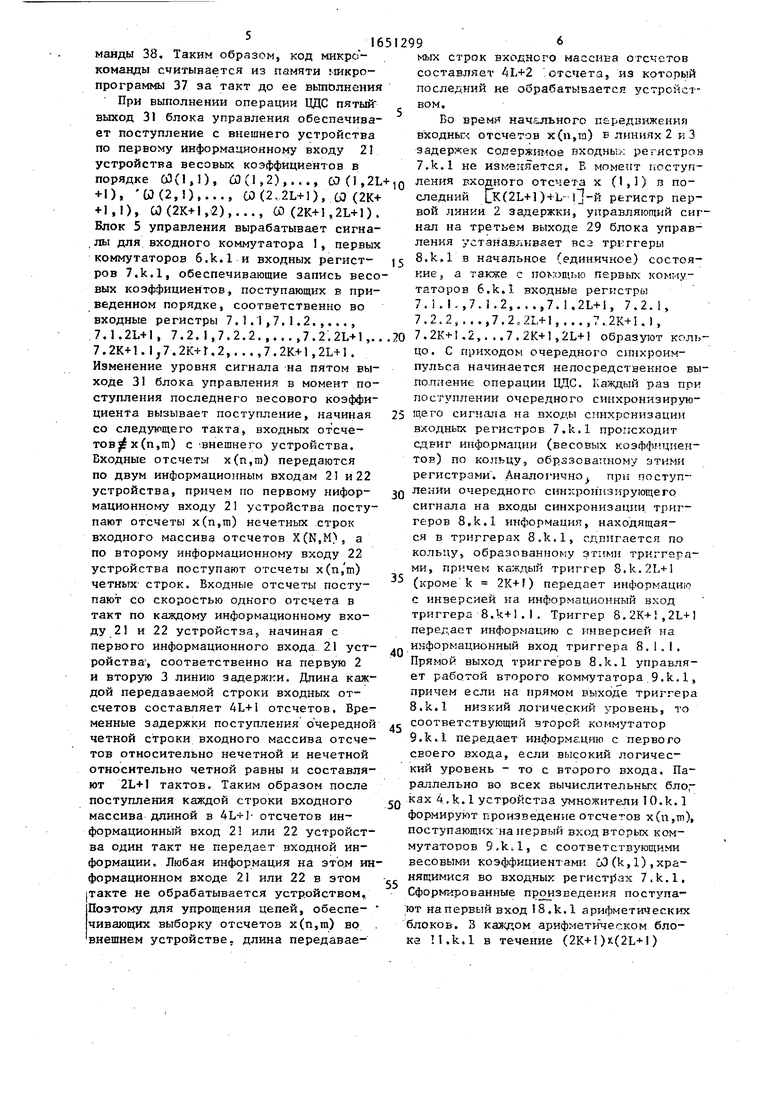

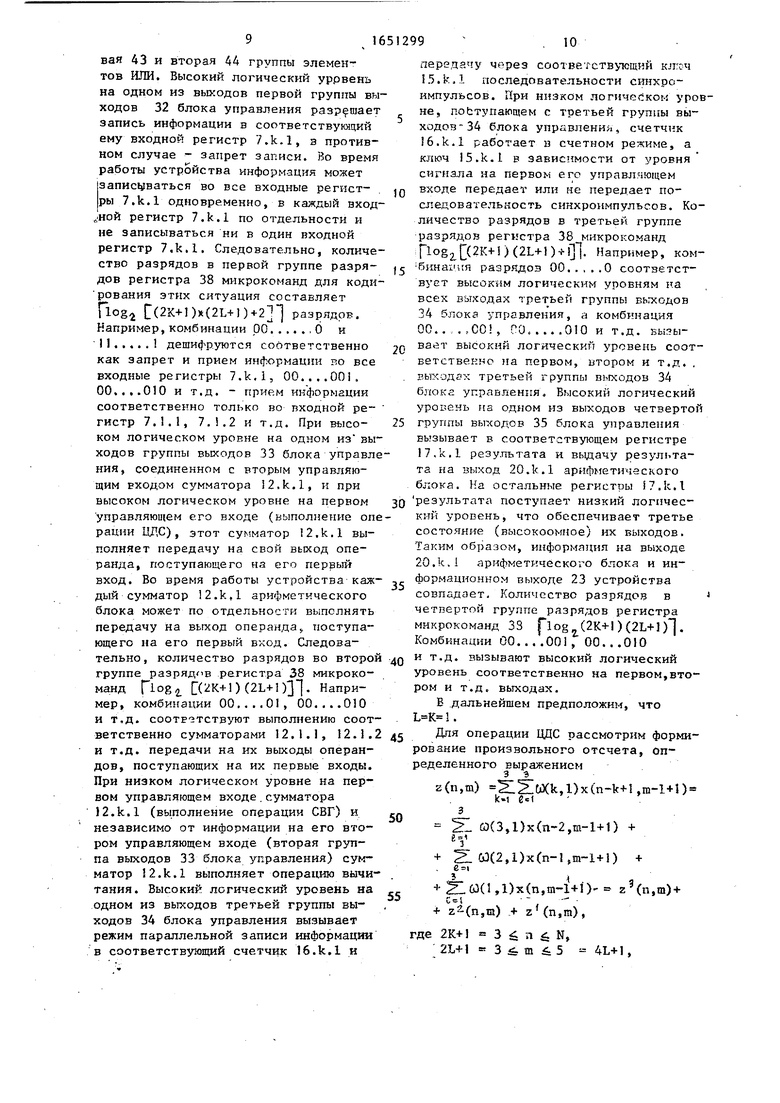

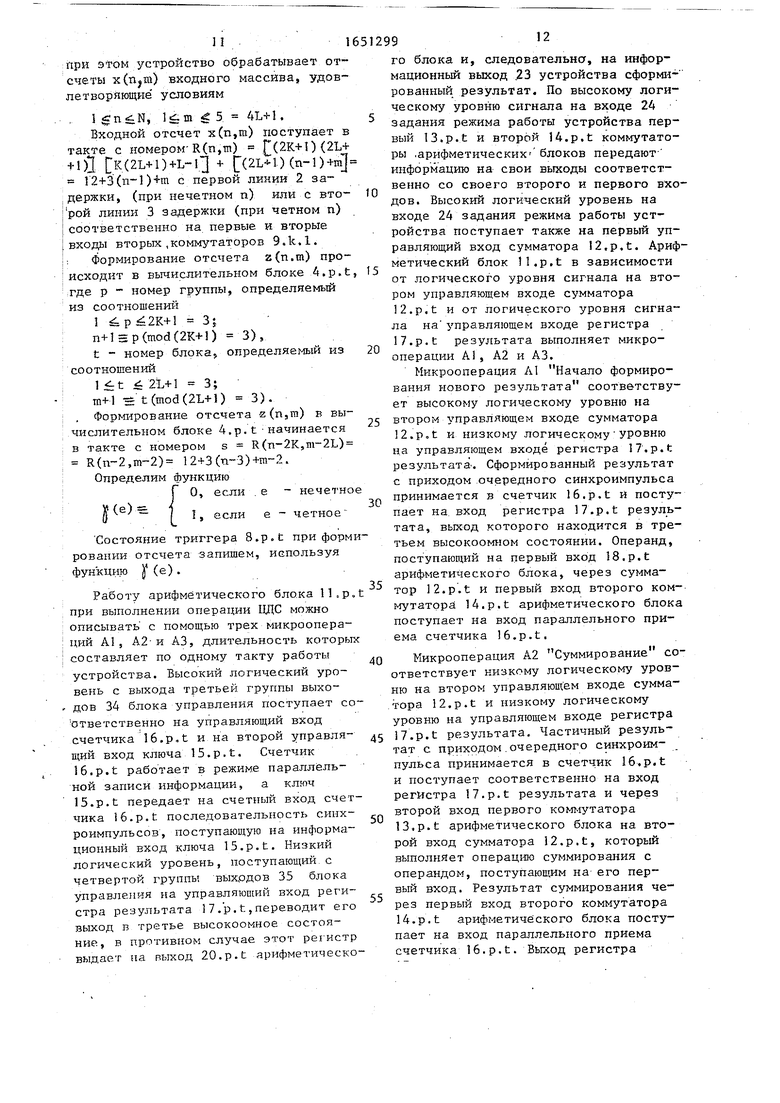

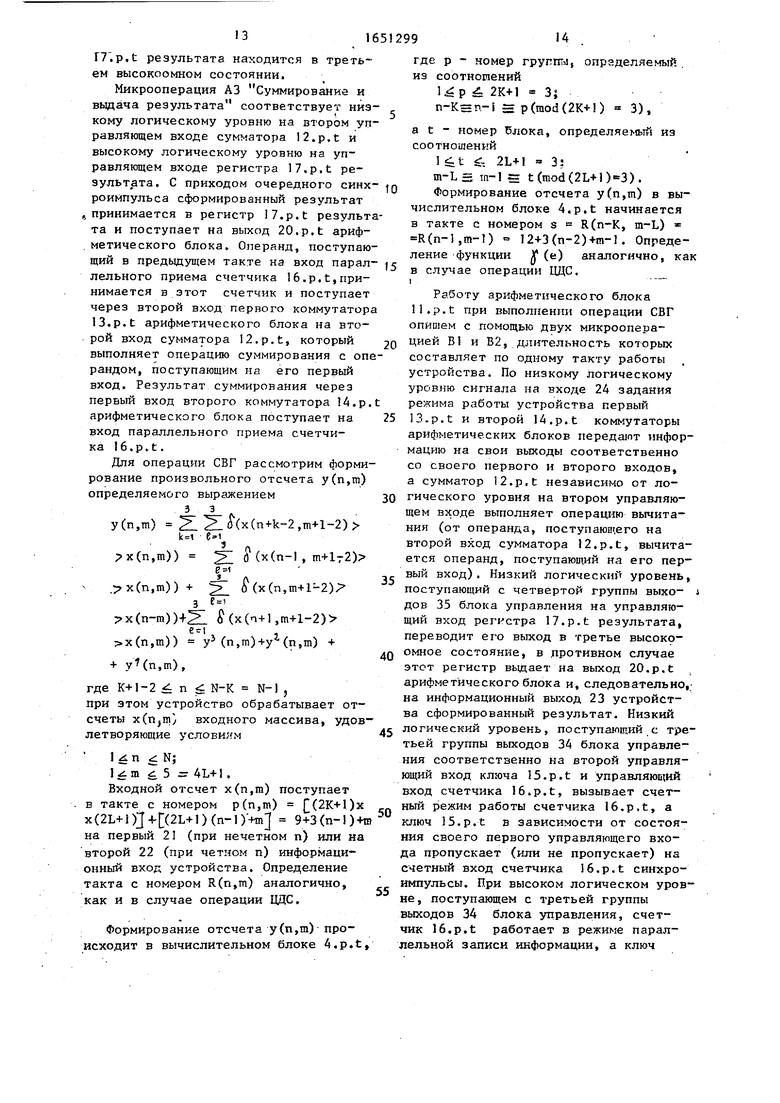

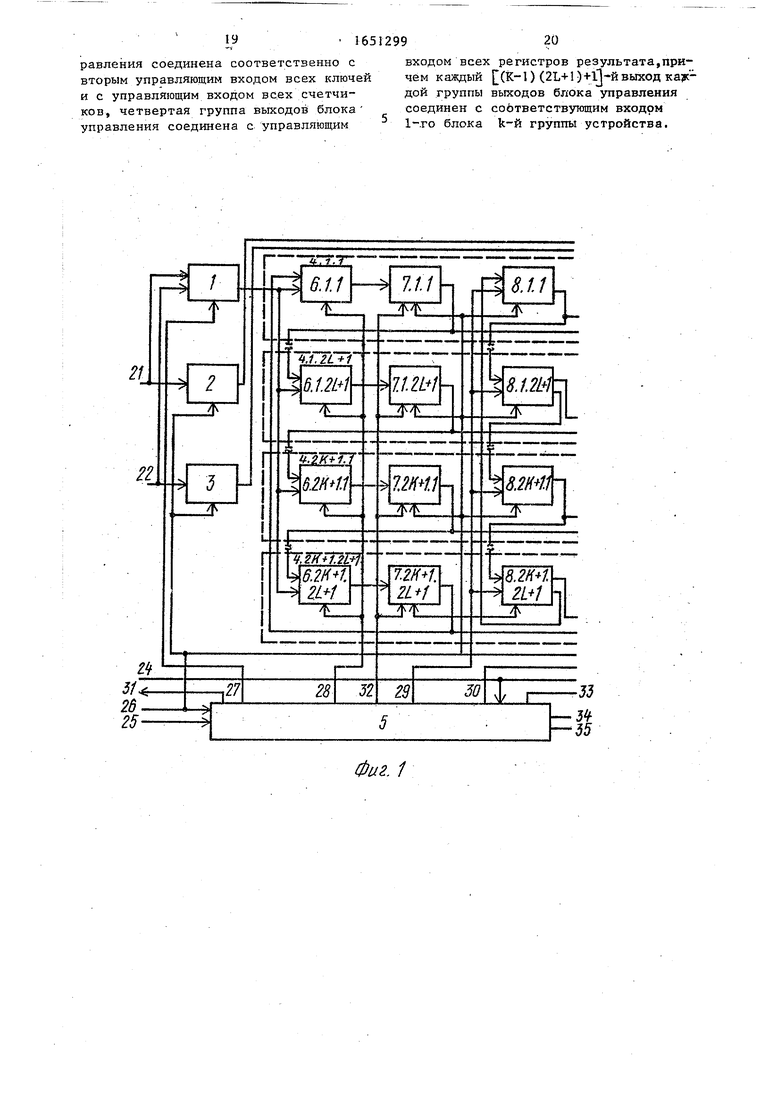

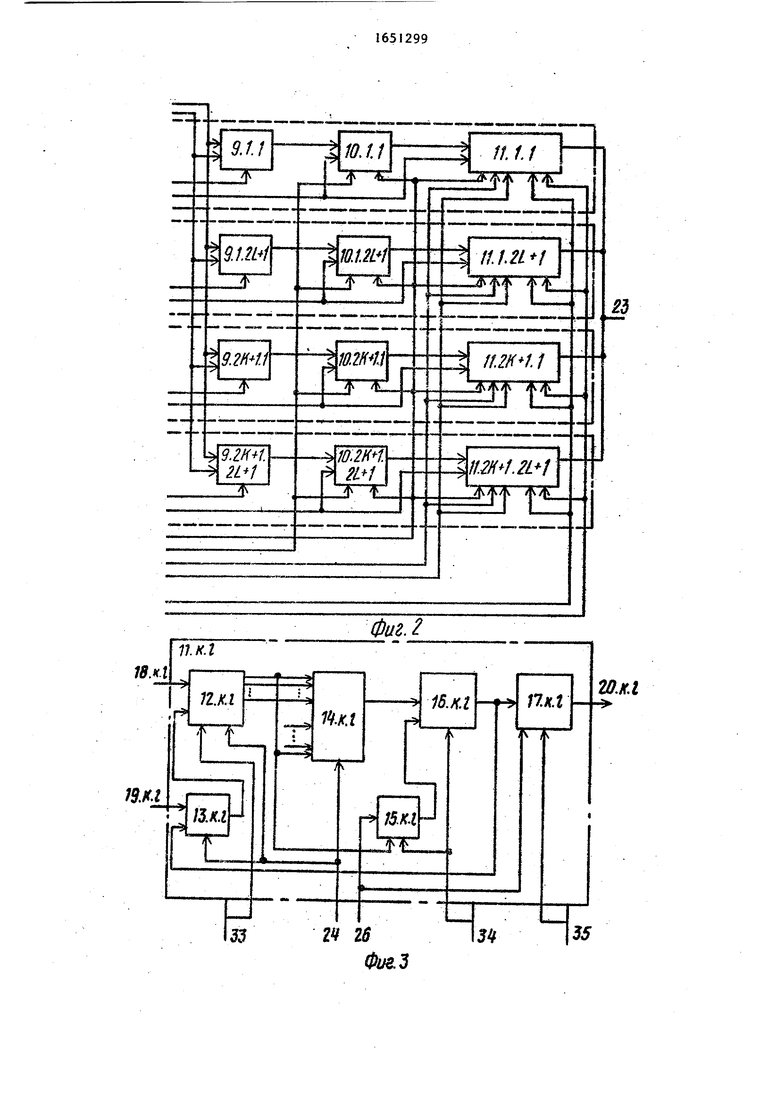

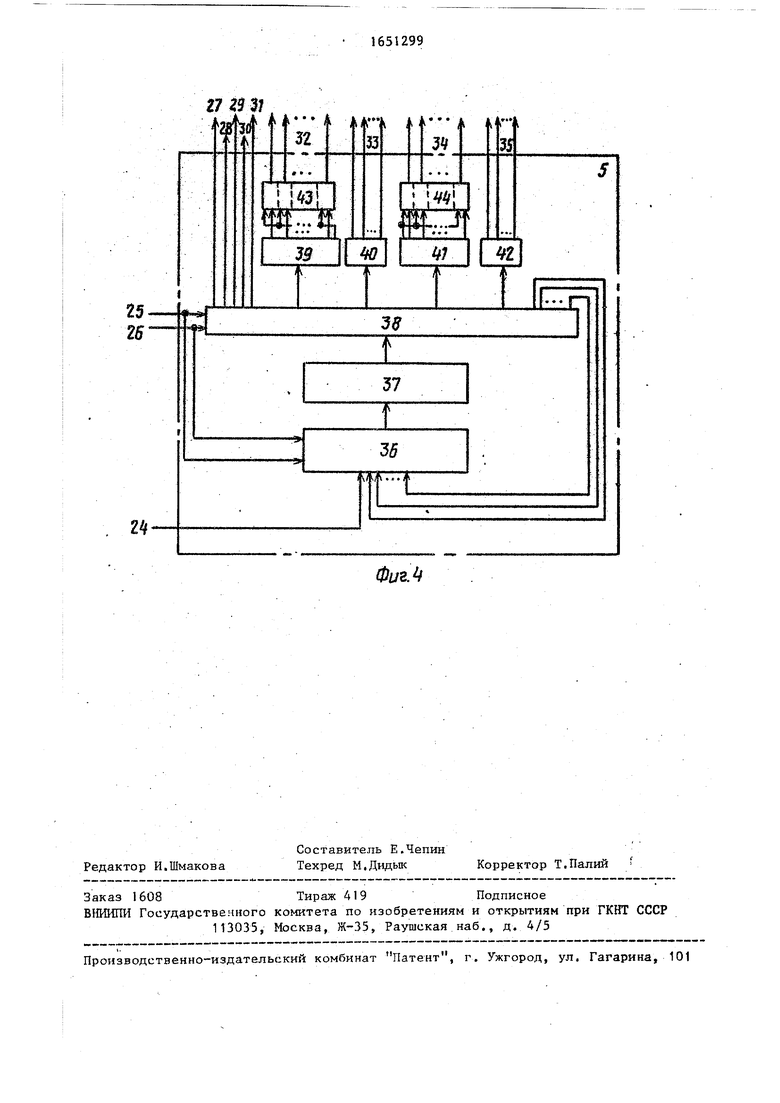

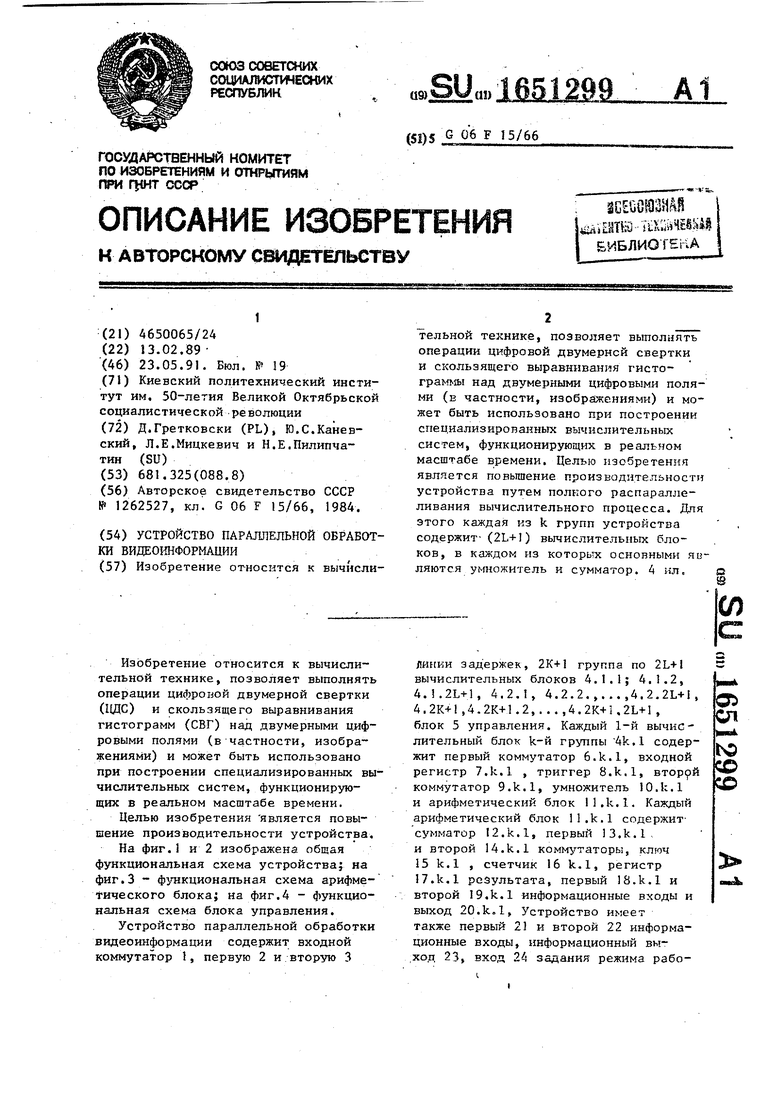

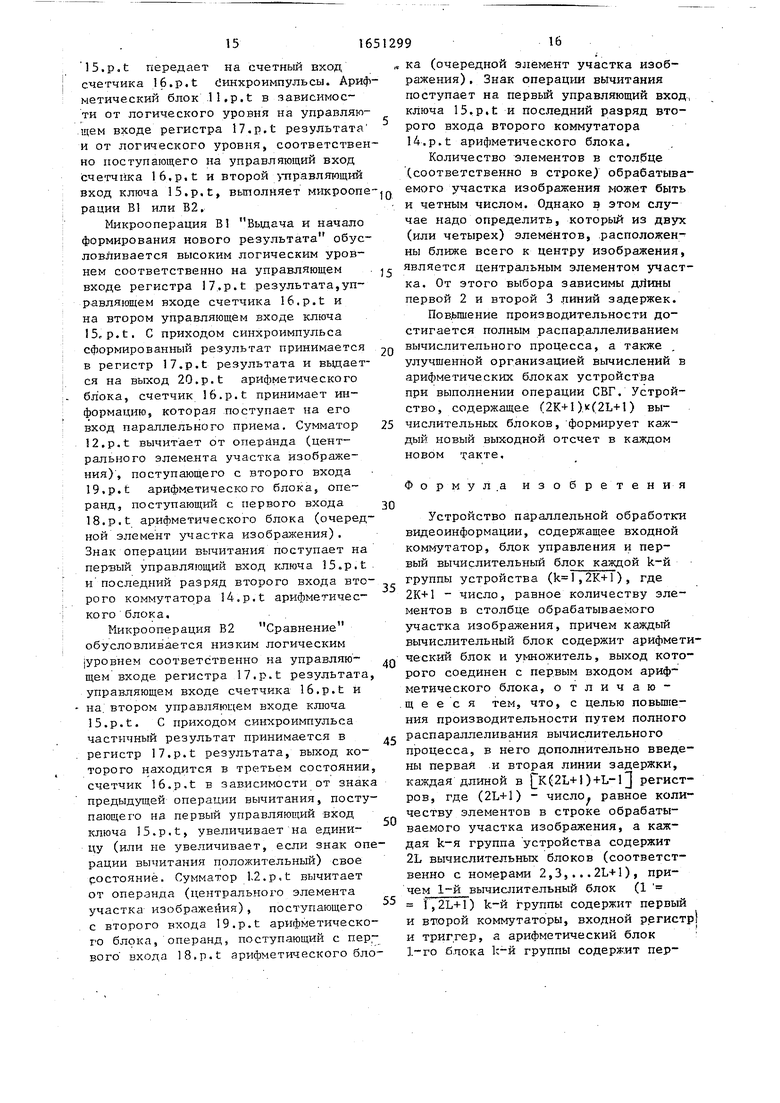

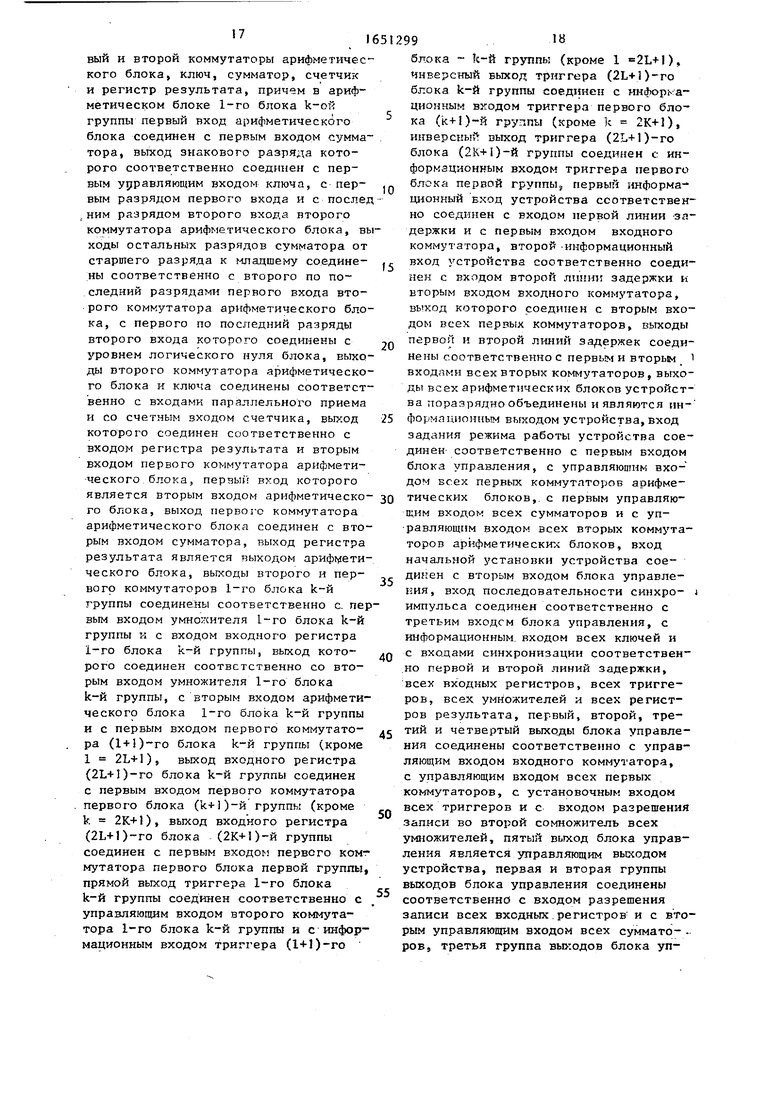

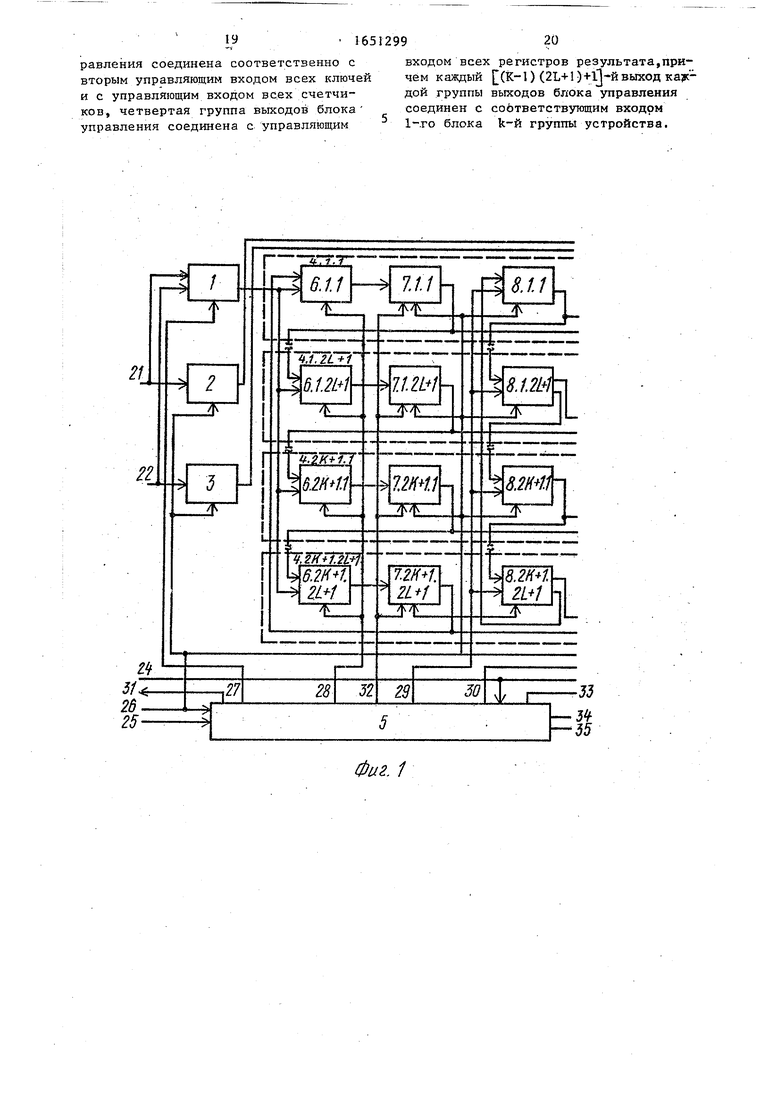

На фиг.1 и 2 изображена общая функциональная схема устройства} на фиг.З - функциональная схема арифметического блока; на фиг.4 - функциональная схема блока управления.

Устройство параллельной обработки видеоинформации содержит входной коммутатор 1, первую 2 и вторую 3

линии задержек, 2К+1 группа по 2L+1 вычислительных блоков 4.1.1; 4.1.2,

4.1.2L+1, 4.2.1, 4.2.24.2.2L-H,

4.2К+1.4.2К-Н.2,. ..,4.2K+;.2L+1 , блок 5 управления. Каждый 1-й вычислительный блок k-й группы 4k.1 содержит первый коммутатор 6.k.l, входной регистр 7.k.l , триггер 8.k.l, второй коммутатор 9.k.l, умножитель lO.k.l и арифметический блок ll.k.1. Каждый арифметический блок ll.k.l содержит сумматор 12.k.l, первый I3,k.l и второй 14.k.l коммутаторы, ключ 15 k.l , счетчик 16 k.l, регистр 17.k.l результата, первый 18.k.l и второй 19,k.l информационные входы и выход 20.k«.l, Устройство имеет также первый 21 и второй 22 информационные входы, информационный выход 23, вход 24 задания режима рабо« &,

ты, вход 25 начальной установки и вход 26 последовательности синхроимпульсов.

Блок управления содержит группу выходов 27-30, выход 31, который является управляющим выходом устройства, группу выходов 32-35, блок 36 микропрограммного управления,блок 37 памяти микропрограмм, регистр 38 мик- рокоманды, первый 39, второй 40, третий 41 и четвертый 42 дешифраторы, первую 43 и вторую 44 группы элементов ИЛИ.

Устройство работает следующим об- разом.

Скользящее выравнивание гистограммы распределения значений цифрового сигнала состоит в том, что каждое значение цифрового сигнала x(n,m) вход- ного массива отсчетов X(N,M) преобразуется по гистограмме Нп„,(с) , построенной по некоторой окрестности сигнала x(n,m) (участка изображения),, состоящего из G элементов, в соответст-

вии с формулой

Х(п.т)

Н(с). (О

/ у (n,m)

Формулу (1) с учетом прямоугольное-™ участка изображения, состоящего из .(2K+1) (2L+1) отсчетов, по которооценивается гистограмма Hnrn э мож заменить формулой

2км 2LH . , 5 Р Г / 35

У (п,ш) - 7mn72L+TTА- Л П(2K+1M2L+1) -k+k-1 ,m-L+l-l)Ј x(n,m)l ,

(2)

где n K+l, N-K; m L+l , M-L;

л.- -i JO если S ubj -|ls если a$b.

y(n,m) - нормированный результат

преобразования. Устройство параллельной обработки видеоинформации вычисляет ненормированный результат СВГ согласно формуле ИМ 2L-H

y(n,m) Z IE- &Гх(п-К+к-1, m-L+ ей L

+1-1) x(n,m)J,(3)

где n K+l, N-K; m L+l, M-L;

{О, если 1. если

y(n,m) - ненормированный результат преобразования.

i Связь между нормированным и ненормированным результатами преобразования определяется формулой

v(n m) 1 - ZlSiSl. . г/и

У n,m; i (2K+I)(2L+I)

При использовании СВГ нормирование результатов преобразования производится во внешнем устройстве.

Операция ЦДС сигналов x(n,m) входного массива отсчетов X(N,M) с весовыми коэффициентами({)( и,1) массива w(2K+l , 2L+1) определяется формулой 2fc+l 2L-I-I

z(n,m) ZI 21 W(k,l)x(n-k+1, 1

m-1+1),(5)

где n 2K+1,N; m 2L+1.M;

z(n,m) - результат преобразования.

Режим работы устройства обусловливается уровнем сигнала, поступающего от внешнего устройства по входу 24 задания работы устройства. При высоком логическом уровне сигнала выполняется операция ЦДС, в противном случае - СВГ.

По входу 25 начальной установки устройства с внешнего устройства поступает сигнал, по которому регистр 38 микрокоманды устанавливается в нулевое состояние, С приходом по входу 26 последовательности синхроимпульсов очередного синхроимпульса /нулевой такт работы устройства} блок 36 микропрограммного управления в соответствии с уровнем сигнала на входе 24 задания режима работы устройства вырабатывает начальный адрес, по которому из блока 37 памяти микропрограммы считывается первая микрокоманда, управляющая выполнением операции ЦДС или СВГ. Память микропрограммы 37 условно разделена на две части: одна используется при выполнении операции ЦДС, вторая - СВГ. Считанная микрокоманда поступает на вход регистра 38 микрокоманды. С приходом следующего синхроимпульса по входу 26 последовательности синхроимпульсов (первый такт работы устройства) считанная микрокоманда записывается в регистр 38 микрокоманды, частично дешифруется с помощью дешифраторов 39-42 и групп 43 и 44 элементов ИЛИ и поступает в другие узлы устройства. Выбор очередной микрокоманды обеспечивается пятой группой разрядов регистра 38 микроко165

манды 38. Таким образом, код микрокоманды считывается из памяти икрг программы 37 за такт до ее выполнения При выполнении операции ЦДС пятый выход 31 блока управления обеспечивает поступление с внешнего устройства по первому информационному входу 21 устройства весовых коэффициентов в

2996

мых строк входного массива отсчетов составляет 4L+2 отсчета, из который последний не обрабатывается устрсйс - вом.

Во время начального передвижения входных отсчетов x(n,ra) Ј линиях 2 и 3 задержек содержимое входнь. регистров 7.k.l не изменяется, Б момент ьоступпорядке С0{1,1), 60(1,2),..., 6Э (1, ления входного отсчета х (1,1) в по- + 1), 03(2,1),..., OH2-2L+I), 63 (2К+ следний k(2L+l ) ij-й регистр первой линии

+ 1,1), CO(2K+1,2),..., СО (2K+I.2L-H). Блок 5 управления вырабатывает сигналы для входного коммутатора 1, первых коммутаторов 6.R.1 и входных регистров 7.k.l, обеспечивающие запись весовых коэффициентов, поступающих в приведенном порядке, соответственно во входные регистры 7.1.1,7.1.2.,..,, 7.1.2L+1, 7.2.1,7.2.2.....,7.2.2L+1,.. . 7.2К+1.1,7.2К+Г,2,..,,7.2K+1,2L+. Изменение уровня сигнала на пятом выходе 31 блока управления в момент поступления последнего весового коэффи циента вызывает поступление, начиная со следующего такта, входных от сче- товуЈх(п,га) с -внешнего устройства. Входные отсчеты x(n,m) передаются по двум информационным входам 21 и 22 устройства, причем по первому информационному входу 21 устройства поступают отсчеты x(n,m) нечетных строк входного массива отсчетов X(N,M), a по второму информационному входу 22 устройства поступают отсчеты x(n, tn) четных строк. Входные отсчеты поступают со скоростью одного отсчета в такт по каждому информационному входу 21 и 22 устройстваs начиная с первого информационного входа 21 устройства , соответственно на первую 2 и вторую 3 линию задержки. Длина каждой передаваемой строки входных отсчетов составляет 4L+1 отсчетов. Временные задержки поступления очередной четной строки входного массива отсчетов относительно нечетной и нечетной относительно четной равны и составляют 2L+1 тактов. Таким образом после поступления каждой строки входного массива длиной в 4L-H- отсчетов информационный вход 2 или 22 устройства один такт не передает входной информации. Любая информация на этом информационном входе 21 или 22 в этом такте не обрабатывается устройством. Поэтому для упрощения цепей, обеспечивающих выборку отсчетов x(n,m) во внешнем устройстве, длина передаваг15

20

25

30

2 задержки, управляющий сиг нал на третьем выходе 29 блока управления устанавливает всэ тргггеры S.k.l в начальное - единичное) состояние, а также о иоь.ошыл первых комну- таторов 6,k.l вхоцные регистры 7..1.,7.1.2,...,7.I.2L+1, 7.2.1, 7.2.2,...,7.2,П-Н,.. ..7.2К+1.), 7.2К+.2,... 7.2К+1,2L+ образуют коль цо. С приходом очередного синхроимпульса начинается непосредственное вы попнение операции ЦДС. Каждый раз при поступлении очередного синхронизирующего сигнала на входы синхронизации входных регистров 7.U.1 происходит сдвиг информации (весовых коэффициентов) по кольцу, образованному этими регистрами. Аналогично при поступлении очередного синхронизирующего сигнала на входы синхронизации триггеров 8,k.l информация, находящаяся в триггерах 8,k.l, сдгшгается по кольцу, образованному этими трнггеса- ми, причем каждый триггер 8.k.2L+l (кроме k 2К-Н) передает информации с инверсией на информационный вход триггера 8A+1.I. Триггер 8. 2К+ ,2L+ передает информацию с инверсией на информационный вход триггера 8.1.1. Прямой выход триггеров S.k.l управляет работой второго коммутатора 9.k.l, причем если на прямом выходе триггера S.k.l низкий логический уровень, то соответствующий второй коммутатор 9«k,l передает информгцию с первого своего входа, если высокий логический уровень - то с второго входа. Параллельно во всех вычислительных блоках 4.k.l устройства умножители I0.k. 1 формируют произведение отсчетов x(n,ir), поступающих на первый вход вторых коммутаторов 9,k.l, с соответствующими весовыми коэффициент амн u) (k,1),хранящимися во входных регистрах 7.k.l. Сформированные произьРденкя поступают на первый вход 1 S.k.l арифметических блоков. 3 каждом арифметическом блоке M.k.l в течение (2К+1)к(2Ь+1)

40

45

50

55

2996

мых строк входного массива отсчетов составляет 4L+2 отсчета, из который последний не обрабатывается устрсйс - вом.

Во время начального передвижения входных отсчетов x(n,ra) Ј линиях 2 и 3 задержек содержимое входнь. регистров 7.k.l не изменяется, Б момент ьоступ0 ления входного отсчета х (1,1) в по- следний k(2L+l ) ij-й регистр первой линии

5

0

5

0

2 задержки, управляющий сигнал на третьем выходе 29 блока управления устанавливает всэ тргггеры S.k.l в начальное - единичное) состояние, а также о иоь.ошыл первых комну- таторов 6,k.l вхоцные регистры 7..1.,7.1.2,...,7.I.2L+1, 7.2.1, 7.2.2,...,7.2,П-Н,.. ..7.2К+1.), 7.2К+.2,... 7.2К+1,2L+ образуют кольцо. С приходом очередного синхроимпульса начинается непосредственное вы- попнение операции ЦДС. Каждый раз при поступлении очередного синхронизирующего сигнала на входы синхронизации входных регистров 7.U.1 происходит сдвиг информации (весовых коэффициентов) по кольцу, образованному этими регистрами. Аналогично при поступлении очередного синхронизирующего сигнала на входы синхронизации триггеров 8,k.l информация, находящаяся в триггерах 8,k.l, сдгшгается по кольцу, образованному этими трнггеса- ми, причем каждый триггер 8.k.2L+l (кроме k 2К-Н) передает информации с инверсией на информационный вход триггера 8A+1.I. Триггер 8. 2К+ ,2L+ передает информацию с инверсией на информационный вход триггера 8.1.1. Прямой выход триггеров S.k.l управляет работой второго коммутатора 9.k.l, причем если на прямом выходе триггера S.k.l низкий логический уровень, то соответствующий второй коммутатор 9«k,l передает информгцию с первого своего входа, если высокий логический уровень - то с второго входа. Параллельно во всех вычислительных блоках 4.k.l устройства умножители I0.k. 1 формируют произведение отсчетов x(n,ir), поступающих на первый вход вторых коммутаторов 9,k.l, с соответствующими весовыми коэффициент амн u) (k,1),хранящимися во входных регистрах 7.k.l. Сформированные произьРденкя поступают на первый вход 1 S.k.l арифметических блоков. 3 каждом арифметическом блоке M.k.l в течение (2К+1)к(2Ь+1)

0

5

0

5

71

тактов работы накапливаются (суммируются) произведения, а один раз в (2К-Н )tf(2L+l) тактов очередной результат операции ЦДС, сформированный в вычислительном блоке 4.k.l, передается на информационный выход 23 устройства.

При выполнении операции СВР пятый выход 31-блока управления обеспечивает поступление с внешнего устройства, по первому информационному входу 21 устройства единичных сигналов, которые записываются во входные регистры 7.k.l и переписываются в регистр второго сомножителя умножителей lO.k.l. Изменение уровня сигнала на четвертом выходе 30 блока управления, после записи единичных сигналов в регистр второго сомножителя всех умножителей lO.k.l, приводит к тому, что умножители lO.k.l до конца выполнения операции СВГ без изменения пердают на свои выходы данные, поступающие на их первые входы. Изменение уровня сигнала на пятом выходе 3 блка управления в момент поступления последнего единичного сигнала вызывает поступление, начиная со следующег такта, входных отсчетов x(n,m) с вне него устройства. Способ и порядок их поступления аналогичный, как при выполнении операции ЦЦС. В момент поступления входного отёчета х(3,1) в последний JJK.(2L+) -L-lJ-ft регистр первой линии 2 задержки управляющий сигнал на третьем выходе 29 блока управления устанавливает все триггеры 8,k.l в начальное единичное состояние. С приходом следующего синхросигнала начинается непосредственное выполнение операции СВГ. Аналогично, как в случае выполнения операции ЦДС триггеры 8.L.1 образуют кольцо, по которому с приходом очередных синхроимпульсов сдвигается информация. С задержкой на такт относительно момента начала непосредственного выполнения операции СВГ все первые коммутаторы 6.k.l начинают передавать инфор мацию с второго своего входа на вход соответствующих входных регистров 7.k,1.Одновременно входной коммутатор 1 начинает передавать информацию с первого (при четном К) или с второго (при нечетном К) входа на вторые входы первых коммутаторов 6.1с. (В дальнейшем входной коммутатор 1 передает информацию на вторые входы

8

0

5

0

5 0

5

0

5

5

первых коммутаторов 6.k.l то с первого, то с второго своего входа с периодом в 2L+1 тактов).Работа входного коммутатора 1 и первых коммутаторов 6,k.l позволяет выделить и записать во входные регистры 7.U.1 центральные элементы участков изображений. Параллельно во всех арифметических блоках ll.k.l устройства выполняется операция вычитания (от центрального элемента участка вычитается очередной элемент участка), а знак результата прибавляется к содержимому счетчика 16.k.l. Один раз в (2К+1) х x(2L+i) тактов очередной результат операции СВГ. сформированный в вычи- тательном блоке ll.k.l, передается на информационный выход 23 устройства. Каждые (2К+1)x(2L+l) тактов во входной регистр 6.k.l принимается новый центральный элемент участка изображения.

Блок управления сигнала для других узлов устройства. Низкий логический уровень на первом выходе 27 блока управления соответствует передаче информации с первого входного коммутатора 1 на его выход, в- противном случае - с второго входа. Низкий логический уровень на втором выходе 28 блока управления соответствует передаче информации с первых входов первых коммутаторов 6.k.l соответственно на их входы, в противном случае - с вторых входов. Высокий логический уровень на третьем выходе 29 блока управления устанавливает все триггеры S.k.l в единичное состояние. Высокий логический уровень на четвертом выходе 30 блока управления разреишет запись информации во второй сомножитель всех умножителей lO.k.l, в противном случае - запрет записи. Высокий логический уровень на пятом выходе 31 блока управления соответствует поступлению в следующем такте в параллельное устройство обработки видеоинформации входных отсчетов x(n,m). Низкий логический уровень на управляющем выходе 31 устройства обеспечивает псдачу в следующем такте на первый информационный вход 21 устройства весовых коэффициентов C0(k,l) в случае выполнения ЦДС и единичных отсчетов в случае выполнения операции СВГ. С целью экономии памяти микропрограмм 37 и учитывая специфику вычислений используются дешифраторы 39-42, пер10

15

20

91651299 10

вая 43 и вторая 44 группы элементов ИЛИ. Высокий логический уррвень на одном из выходов первой группы выходов 32 блока управления разрешает запись информации в соответствующий ему входной регистр 7.k.l, в противном случае - запрет записи. Во время работы устройства информация может записываться во все входные регистры 7.R.1 одновременно, в каждый вход- , НОЙ регистр 7.k.l по отдельности и не записываться ни в один входной регистр 7.k.l. Следовательно, количество разрядов в первой группе разрядов регистра 38 микрокоманд для коди- рования этих ситуация составляет flog (2K+I)x(2L+l) раэрлдор.

Например,комбинации 00,0 и

111 дешифруются соответственно

как запрет и прием информации го все входные регистры 7.k.l3 00....00, 00..,.010 и т.д. - прием информации соответственно только во входной ре- гистр 7.1.1, 7.1.2 и т.д. При высоком логическом уровне на одном из выходов группы выходов 33 блока управления, соединенном с вторым управляющим входом сумматора 12,k.l, и при высоком логическом уровне на первом 30 управляющем его входе (выполнение операции ЦДС), этот сумматор 12.k.l выполняет передачу на свой выход операнда, поступающего на его первый вход. Во время работы устройства каж- 35 формационном выходе 23 устройства дый сумматор 12.k,l арифметического совпадает. Количество разрядов в блока может по отдельности выполнять четвертой группе разрядов регистра передачу на выход операнда,, поступа- микрокоманд 33 (2K+l ) (2L+I ). ющего на его первый вход. Следова- Комбинации 00....001, 00...010 тельно, количество разрядов во второй 40 и вызывают высокий логический группе разрядов регистра 38 микроко- уровень соответственно на первом,вто- манд flog г. C(K+1)(2L+1)I. Например, комбинации 00....01, 00....010 и т.д. соответствуют выполнению соответственно сумматорами 12.1.1, 12.1.2 д5 и т.д. передачи на их выходы операндов, поступающих на их пеовые входы. При низком логическом уровне на первом управляющем входе.сумматора 12.k.l (выполнение операции СВГ) и независимо от информация на его втором управляющем входе (вторая группа выходов 33 блока управления) сумматор 12.R.1 выполняет операцию вычитания. Высокий логический уровень на одном из выходов третьей группы выходов 34 блока управления вызывает режим параллельной записи информации в соответствующий счетчик 16.U.1 и

передачу через соответствующий кл сч 15. К последовательности синхроимпульсов. При низком логическом уров не, поЬтупающем г третьей группы выходов- 34 блока управления, счетчик 16.k.l работает в счетном режиме, а ключ 15.К.1 в зависимости от уровня сигнала на первом его управляющем входе передает или не передает последовательность синхроимпульсов. Количество разрядов в третьей группе разрядов регистра 38 микрокоманд (2K+l)(2L-H) + ffj Например, ком- бинаиня разрядов 00О соответствует высоким логическим уровням на всех выходах третьей группы выходов 34 блока управления, а комбинация

00.. .,00, 0.010 и т.д. ны- ывает высокий логический уровень соответственно на первом, втором и т.д. . выходах третьей группы выходов 34 блока управления. Высокий логический уровень па одном из выходов четвертой 25 группы выходов 35 блока управления вызывает в соответствующем регистре 17.k.l результата и выдачу результата на выход 20.k.l арифметического блока. На остальные регистоы J7.k.l результата поступает низкий логический уровень, что обеспечивает третье состояние (высокоомное) их выходов. Таким образом, информация на выходе 20.k.l арифметического блока и ин

50

ром и т.д. выходах.

Б дальнейшем предположим, что .

Для операции ЦДС рассмотрим формирование произвольного отсчета, определенного выражением з -ь

,m) SL§LU(k,l)x(n-k+I(m-l+i)«

k-i e«i з

51 Ј(3,l)x(n-2,m-l+1) +

55

t

+ iEL G3(2,l)x(n-l,m-l+l)

.

+ ,l)x(n,m-l-H

C i

4- (n,m) + zf (n,m),

z (n,m) +

где 2К+1 3 Ј n N,

2L-H 3 & m & 5 4L+1,

0

5

0

0 5 формационном выходе 23 устройства совпадает. Количество разрядов в четвертой группе разрядов регистра микрокоманд 33 (2K+l ) (2L+I ). Комбинации 00....001, 00...010 0 и вызывают высокий логический уровень соответственно на первом,вто- 5

передачу через соответствующий кл сч 15. К последовательности синхроимпульсов. При низком логическом уровне, поЬтупающем г третьей группы выходов- 34 блока управления, счетчик 16.k.l работает в счетном режиме, а ключ 15.К.1 в зависимости от уровня сигнала на первом его управляющем входе передает или не передает последовательность синхроимпульсов. Количество разрядов в третьей группе разрядов регистра 38 микрокоманд (2K+l)(2L-H) + ffj Например, ком- бинаиня разрядов 00О соответствует высоким логическим уровням на всех выходах третьей группы выходов 34 блока управления, а комбинация

00.. .,00, 0.010 и т.д. ны- ывает высокий логический уровень соответственно на первом, втором и т.д. . выходах третьей группы выходов 34 блока управления. Высокий логический уровень па одном из выходов четвертой 5 группы выходов 35 блока управления вызывает в соответствующем регистре 17.k.l результата и выдачу результата на выход 20.k.l арифметического блока. На остальные регистоы J7.k.l результата поступает низкий логический уровень, что обеспечивает третье состояние (высокоомное) их выходов. Таким образом, информация на выходе 20.k.l арифметического блока и ин

3035 формационном выходе 23 устройства совпадает. Количество разрядов в четвертой группе разрядов регистра микрокоманд 33 (2K+l ) (2L+I ). Комбинации 00....001, 00...010 40 и вызывают высокий логический уровень соответственно на первом,вто- д5

50

ром и т.д. выходах.

Б дальнейшем предположим, что .

Для операции ЦДС рассмотрим формирование произвольного отсчета, определенного выражением з -ь

,m) SL§LU(k,l)x(n-k+I(m-l+i)«

k-i e«i з

51 Ј(3,l)x(n-2,m-l+1) +

5

t

+ iEL G3(2,l)x(n-l,m-l+l)

.

+ ,l)x(n,m-l-H

C i

4- (n,m) + zf (n,m),

z (n,m) +

формационном выходе 23 устрой совпадает. Количество разрядо четвертой группе разрядов рег микрокоманд 33 (2K+l ) (2 Комбинации 00....001, 00...01 и вызывают высокий логич уровень соответственно на пер

где 2К+1 3 Ј n N,

2L-H 3 & m & 5 4L+1,

1

при э гом устройство обрабатывает отсчеты х() входного массива, удовлетворяющие условиям

1 ЈriЈN, lЈm Ј 5 4L+1. Входной отсчет х(п,га) поступает в такте с номером-R(n,m) Ј(2K+I)(2L+

-t-Ol O(2L+i)+L-Q + Ј(2L+i)(n-i)+m

12+3()-hn с первой линии 2 задержки, (при нечетном п) или с вто- рой линии 3 задержки (при четном п) соответственно на первые и вторые входы вторых.коммутаторов 9.U.I.

Формирование отсчета 2(п.т) происходит в вычислительном блоке 4.p.t где р - номер группы, определяемый из соотношений

1 3;

n+l5p(mod(2K+l)

t - номер блока, соотношений

1 Јt Ј 2L+1 3;

m+1 - t(inod(2L+l) 3).

Формирование отсчета г(п,та) в вы числительном блоке 4,p.t начинается в такте с номером s R(n-2K.,m-2L) R(,m-2) 12-«-3(n-3)+m-2.

Определим функцию

f 0, если (е)а

3),

определяемый из

- нечетно

I, если е - четное

1

Состояние триггера S.p.t при формровании отсчета запишем, используя функцию (е).

Работу арифметического блока ll.p. при выполнении операции ЦДС можно описывать с помощью трех микроопераций А1, А2 и A3, длительность которых составляет по одному такту работы устройства. Высокий логический уровень с выхода третьей группы выходов 34 блока управления поступает соответственно на управляющий вход счетчика 16.p.t и на второй управля- щий вход ключа 15.р.t. Счетчик IG.p.t работает в режиме параллельной записи информации, а ключ IS.p.t передает на счетный вход счетчика I6.p.t последовательность синхроимпульсов, поступающую иа информационный вход ключа IS.p.t. Низкий логический уровень, поступающий с четверток группы выходов 35 блока управления на управляющий вход регистра результата 17.p.t,переводит его выход в третье высокоомное состояние, в противном случае этот peiистр выдает иа выход 20.p.t арифметическо

10

15

20

25

35

45

.„ 65129912

го блока и, следовательно, на информационный выход 23 устройства сформированный результат. По высокому логическому уровню сигнала на входе 24 задания режима работы устройства первый 13,p.t и второй 14.p.t коммутаторы .арифметических блоков передают информацию на свои выходы соответственно со своего второго и первого входов. Высокий логический уровень на входе 24 задания режима работы устройства поступает также на первый управляющий вход сумматора 12.p.t. Арифметический блок ll.p.t в зависимости от логического уровня сигнала на втором управляющем входе сумматора 12.p.t и от логического уровня сигнала на управляющем входе регистра 17.p.t результата выполняет микрооперации Al, A2 и A3.

Микрооперация А1 Начало формирования нового результата соответствует высокому логическому уровню на втором управляющем входе сумматора 12.p.t и низкому логическому уровню ца управляющем входе регистра 17.p.t результата. Сформированный результат с приходом очередного синхроимпульса принимается в счетчик 16.p.t и поступает на вход регистра 17.p.t результата, выход которого находится в третьем высокоомном состоянии. Операнд, поступающий на первый вход IS.p.t арифметического блока, через сумматор 12.p.t и первый вход второго коммутатора 34.p.t арифметического блока поступает на вход параллельного приема счетчика 16.p.t.

Микрооперация А2 Суммирование соответствует низкому логическому уровню на втором управляющем входе сумматора 12.p.t и низкому логическому уровню на управляющем входе регистра 17.p.t результата. Частичный результат с приходом очередного синхроим- пульса принимается в счетчик 16.p.t и поступает соответственно на вход регистра 17.p.t результата и через второй вход первого коммутатора IS.p.t арифметического блока на второй вход сумматора 12,p.t, который выполняет операцию суммирования с операндом, поступающим на его первый вход. Результат суммирования через первый вход второго коммутатора 14.p.t арифметического блока поступает на вход параллельного приема счетчика 16.p.t. Выход регистра

30

50

55

T7.p,t результата находится в третьем высокоомном состоянии.

Микрооперация A3 Суммирование и выдача результата соответствует низкому логическому уровню на втором управляющем входе сумматора 12.p.t и высокому логическому уровню на управляющем входе регистра 17,p.t результата. С приходом очередного синх- JQ роимпульса сформированный результат принимается в регистр 17.p.t результата и поступает на выход 20.p.t арифметического блока. Операнд, поступающий в предыдущем такте на вход парал- лельного приема счетчика 16.p.t,принимается в этот счетчик и поступает через второй вход первого коммутатора 13.p.t арифметического блока на второй вход сумматора 12.p.tt который ро выполняет операцию суммирования с операндом, поступающим на его первый вход. Результат суммирования через первый вход второго коммутатора 14.p.t арифметического блока поступает на 25 вход параллельного приема счетчика 16.p.t.

Для операции СВГ рассмотрим формирование произвольного отсчета y(n,m) определяемого выражением30

33

У(п,тп) Z- (n+k-2,m+l-2)

x(n,m)) ,x(n,m)) +

Ј(x(n-l , m+lT2) Ј(x(n,m+l-2) 35

3

x(n-m))4-21 Ј(x(n+l,m+l-2)

e t . x(n,m)) y3 (n,m)+y4(n,m) +

+ y (n,m),

где K+l-2 Ј n Ј N-K N-l, при этом устройство обрабатывает отсчеты x(njHi} входного массива, удов летворяющие условиям

40

45

1 n N;

Јiu Г 5 4L+1 .

Входной отсчет х(п,га) поступает в такте с номером p(n,m) Ј(2K+l)x x(2L+iy - -(2L-H)(n-l)Vm 9+3(п-1 )-Ип на первый 21 (при нечетном п) или на второй 22 (при четном п) информационный вход устройства. Определение такта с номером R(n,m) аналогично, как и в случае операции ЦДС.

Формирование отсчета y(n,m) происходит в вычислительном блоке 4 . р. t,

JQ о 5

0

5

0

5

U

5

где р - номер гругпч, опрэделаемый из соотношений

2К-Н 3;

p(mod(2K+l) 3),

at- номер блока, определяемый из соотношений

1 6L Ј-. 2L+1 3s

m-L тп-1 н t(mod(2L+I)).

Формирование отсчета y(n,m) в вычислительном блоке 4.p.t начинается в такте с номером s R(n-K, m-L) R(n-l,m-l) 12+3(n-2)+m-l . Определение функции Л (е) аналогично, как

в случае операции ЦДС. i

Работу арифметического блока ll.p.t при выполнении операции СВГ опишем с помощью двух микрооперацией В1 и В2, длительность которых составляет по одному такту работы устройства. По низкому логическому уровню сигнала на рхо/де 24 задания режима работы устройства первый IS.p.t и второй 14.p.t коммутаторы арифметических блоков передают информацию на свои выходы соответственно со своего первого и второго входов, а сумматор 12.p.t независимо от логического уровня на втором управляющем входе выполняет операцию вычитания (от операнда, поступающего на второй вход сумматора 12.p.t, вычитается операнд, поступающий на его первый вход). Низкий логически уровень, поступающий с четвертой группы выхо- дов 35 блока управления на управляющий вход регистра 17.p.t результата, переводит его выход в третье высоко- омное состояние, в .противном случае этот регистр выдает на выход 20.p,t 1 арифметического блока и, следовательно, на информационный выход 23 устройства сформированный результат. Низкий логический уровень, поступающий с третьей группы выходов 34 блока управления соответственно на второй управляющий вход ключа 15.p.t и управляющий вход счетчика 16.p.t, вызывает счетный режим работы счетчика 16.p.t, a ключ IS.p.t в зависимости от состояния своего первого управляющего входа пропускает (или не пропускает) на счетный вход счетчика I6.p.t синхроимпульсы. При высоком логическом уровне, поступающем с третьей группы выходов 34 блока управления, счетчик 16.p,t работает в режиме параллельной записи информации, а ключ

15

IS.p.t передает на счетный вход счетчика 16.p.t Синхроимпульсы. Арифметический блок ll.p.t в зависимости от логического уровня на управляющем входе регистра 17.p.t результата и от логического уровня, соответственно поступающего на управляющий вход счетчика 16.p,t и второй управляющий вход ключа IS.p.t, выполняет микроопе рации В1 или В2.

Микрооперация В1 Вьщача и начало формирования нового результата обусловливается высоким логическим уровнем соответственно на управляющем входе регистра I7.p.t результата,управляющем входе счетчика 16.p.t и на втором управляющем входе ключа 15,p.t. С приходом синхроимпульса сформированный результат принимается в регистр 17.p.t результата и выдается на выход 20.p.t арифметического блока, счетчик 16.p.t принимает информацию, которая поступает на его вход параллельного приема. Сумматор 2.p.t вычитает от операнда (цент рального элемента участка изображения), поступающего с второго входа 19.p.t арифметического блока, операнд, поступающий с первого входа IS.p.t арифметического блока (очередной элемент участка изображения). Знак операции вычитания поступает на первый управляющий вход ключа IS.p.t и последний разряд второго входа второго коммутатора I4.p.t арифметического блока.

Микрооперация В2 Сравнение обусловливается низким логическим уровнем соответственно на управляющем входе регистра 17.p.t результата, управляющем входе счетчика I6.p.t и на втором управляющем входе ключа IS.p.t. С приходом синхроимпульса частичный результат принимается в регистр 17.p.t результата, выход которого находится в третьем состоянии, счетчик 16.p,t в зависимости от знака предыдущей операции вычитания, поступающего на первый управляющий вход ключа IS.p.t, увеличивает на единицу (или не увеличивает, если знак one рации вычитания положительный) свое состояние. Сумматор 1.2.p.t вычитает от операнда (центрального элемента участка изображения), поступающего с второго входа 19.p.t арифметического блока, операнд, поступающий с пер- вого входа IS.p.t арифметического бло

jQ

129916

„ ка (очередной элемент участка изображения) , Знак операции вычитания поступает на первый управляющий вход, ключа IS.p.t и последний разряд второго входа второго коммутатора 14.p.t арифметического блока.

Количество элементов в столбце (соответственно в строке) обрабатываемого участка изображения может быть и четным числом. Однако в этом случае надо определить, который из двух (или четырех) элементов, расположен- ны ближе всего к центру изображения,

является центральным элементом участка. От этого выбора зависимы дл ины первой 2 и второй 3 линий задержек. Повышение производительности достигается полным распараллеливанием

2Q вычислительного процесса, а также улучшенной организацией вычислений в арифметических блоках устройства при выполнении операции СВР. Устройство, содержащее С2К+1)x(2L+l) вы25 числительных блоков, формирует каждый новый выходной отсчет в каждом новом т.акте.

0

5

0

5

0

5

Формула изобретения

Устройство параллельной обработки видеоинформации, содержащее входной коммутатор, блок управления и первый вычислительный блок каждой k-й группы устройства (,2K+l), где 2К+1 - число, равное количеству элементов в столбце обрабатываемого участка изображения, причем каждый вычислительный блок содержит арифметический блок и умножитель, выход которого соединен с первым входом арифметического блока, отличающееся тем, что, с целью повышения производительности путем полного распараллеливания вычислительного процесса, в него дополнительно введены первая и вторая линии задержки, каждая длиной в K(2L+ ) регистров, где (2L+1) - число, равное количеству элементов в строке обрабатываемого участка изображения, а каждая k-я группа устройства содержит 2L вычислительных блоков (соответственно с номерами 2,3,...2L+1), при- чем 1-й вычислительный блок (1 1,2L+1) k-й группы содержит первый и второй коммутаторы, входной регистр) и триггер, а арифметический блок 1-го бпока k-й группы содержит пер

вый и второй коммутаторы арифметического блока, ключ, сумматор, счетчик и регистр результата, причем в арифметическом блоке 1-го блока k-o:4 группы первый вход арифметического блока соединен с первым входом сумма тора, выход знакового разряда которого соответственно соединен с первым управляющим входом ключа, с первым разрядом первого входа и с пос.гед , ним разрядом второго входа второго коммутатора арифметического блока, выходы остальных разрядов сумматора от старшего разряда к младшему соединены соответственно с второго по последний разрядами первого входа второго коммутатора арифметического блока, с первого по последний разряды второго входа которого соединены с уровнем логического нуля блока, выходы второго коммутатора арифметического блока и ключа соединены соответственно с входами параллельного приема и со счетным входом счетчика, выход которого соединен соответственно с входом регистра результата и вторым входом первого коммутатора арифметического блока, первый вход которого является вторым входом арифметическо- го блока, выход первого коммутатора арифметического блока соединен с вторым входом сумматора, выход регистра результата является выходом арифметического блока, выходы второго и первого коммутаторов 1-го блока k-й группы соединены соответственно с пер вым входом умножителя 1-го блока k-й группы к с входом входного регистра 1-го блока k-й группы, выход которого соединен соответственно со вторым входом умножителя 1-го блока k-й группы, с вторым входом арифметического блока 1-го блока k-й группы и с первым входом первого коммутатора (1+1)-го блока k-й группы (кроме 1 2L+1), выход входного регистра (2L+l)-ro блока k-й группы соединен с первым входом первого коммутатора первого блока ( к+1)-й группы (кроме k 2K-H), выход входного регистра (2L+I)ro блока (2К-И)-й группы соединен с первым входом первого коммутатора первого блока первой группы, прямой выход триггера 1-го блока k-й группы соединен соответственно с управляющим входом второго коммутатора 1-го блока k-й группы и с информационным входом триггера (1+1)-го

10

15

20

25

зо

35

40

45

50

5

блока - k-й группы (кроме 1 2L+I), инверсный выход триггера (2L+l)-ro блока k-й группы соединен с информационным ВУОДОМ триггера первого блока (к+1)-й грулпы (кроме к 2К+1). инверсный выход триггера (2L+l)-ro блока (2К+1)-й группы соединен с информационным входом триггера первого блока первой группыf первый информационный вход устройства соответственно соединен с входом первой линии задержки и с первым входом входного коммутатора, второй информационный вход устройства соответственно соединен с входом второй линии задержки h вторым входом входного коммутатора, выход которого соединен с вторым входом всех первых коммутаторов, выходы первой и второй линий задержек соединены соответственное первыми вторым ч входами всех вторых коммутаторов, выходы всех арифметических блоков устройства поразрядно объединены и являются ин- формациопиым выходом устройства, вход задания режима работы устройства соединен соответственно с первым входом блока управления, с управлякшшм входом всех первых коммутаторов арифметических блоков, с первым управляющим входом всех сумматоров и с управляющим входом всех вторых коммутаторов арифметических блоков, вход начальной установки устройства соединен с вторым входом блока управления, вход последовательности синхро- J импульса соединен соответственно с третьим входгм блока управления, с информационным входом всех ключей и с входами синхронизации соответственно первой и второй линий задержки, всех входных регистров, всех триггеров, всех умножителей и всех регистров результата, первый, второй, третий и четвертый выходы блока управления соединены соответственно с управляющим входом входного коммутатора, с управляющим входом всех первых коммутаторов, с установочным входом всех триггеров и с входом разрешения записи во второй сомножитель всех умножителей, пятый выход блока управления является управляющим выходом устройства, первая и вторая группы выходов блока управления соединены соответственно с входом разрешения записи всех входных регистров и с вторым управляющим входом всех суммато- . ров, третья группа выходов блока управления соединена соответственно с вторым управляющим входом всех ключей и с управляющим входом всех счетчиков, четвертая группа выходов блока управления соединена с управляющим

входом всех регистров результата,при- чем каждый (К-1) (2L+1 ) выход кардой группы выходов блока управления соединен с соответствующим входом 1-го блока k-й группы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

| Устройство для параллельного вычисления цифровой двумерной свертки | 1986 |

|

SU1416976A1 |

| Устройство для вычисления свертки | 1986 |

|

SU1319045A1 |

| Устройство для цифровой двумерной свертки | 1986 |

|

SU1363250A1 |

| Параллельное устройство для вычисления двухмерной свертки | 1985 |

|

SU1269237A1 |

| Устройство параллельной обработки видеоинформации | 1984 |

|

SU1262527A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1425708A1 |

Изобретение относится к вычнслительной технике, позволяет выполнять операции цифровой двумерной свертки и скользящего выравнивания гистограммы над двумерными цифровыми полями (в частности, изображениями) и может быть использовано при построении специализированных вычислительных систем, функционирующих в реальном масштабе времени. Целью изобретения явлтется повышение производительности устройства путем полного распараллеливания вычислительного процесса. Для этого каждая кэ k групп устройства содержит (2L-H) вычислительных блоков, в каждом из которых основными являются умножитель и сумматор. 4 ил. Ј5 ®

Фиг. 1

18л1

Фиг. 2

W.K.I

Фие.3

z # 3

25

25

ФигМ

| Устройство параллельной обработки видеоинформации | 1984 |

|

SU1262527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-23—Публикация

1989-02-13—Подача