1

Изобретение относится к вычислительной технике и предназначено для решения задач цифровой обработки сигналов, включающих выполнение алгоритмов быстрого преобразования Фурье /БПФ) и свертки.

Целью изобретения является расширение функциональных возможностей за счет вычисления алгоритмов линейной и циклической свертки.

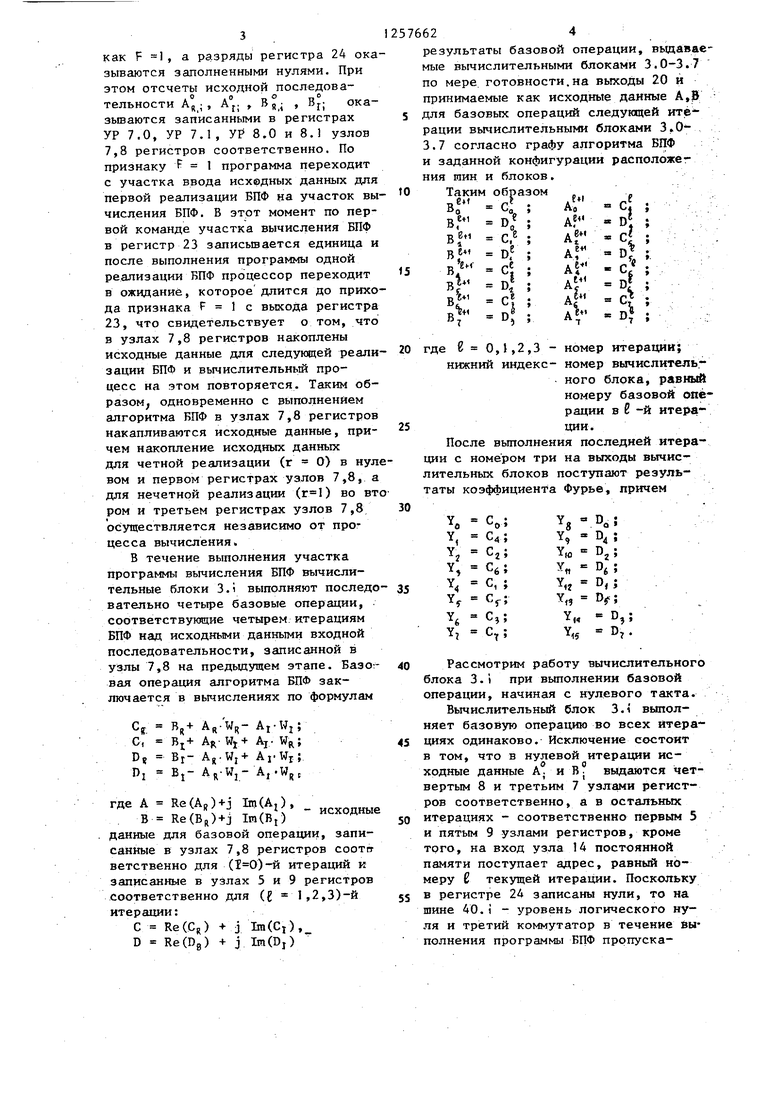

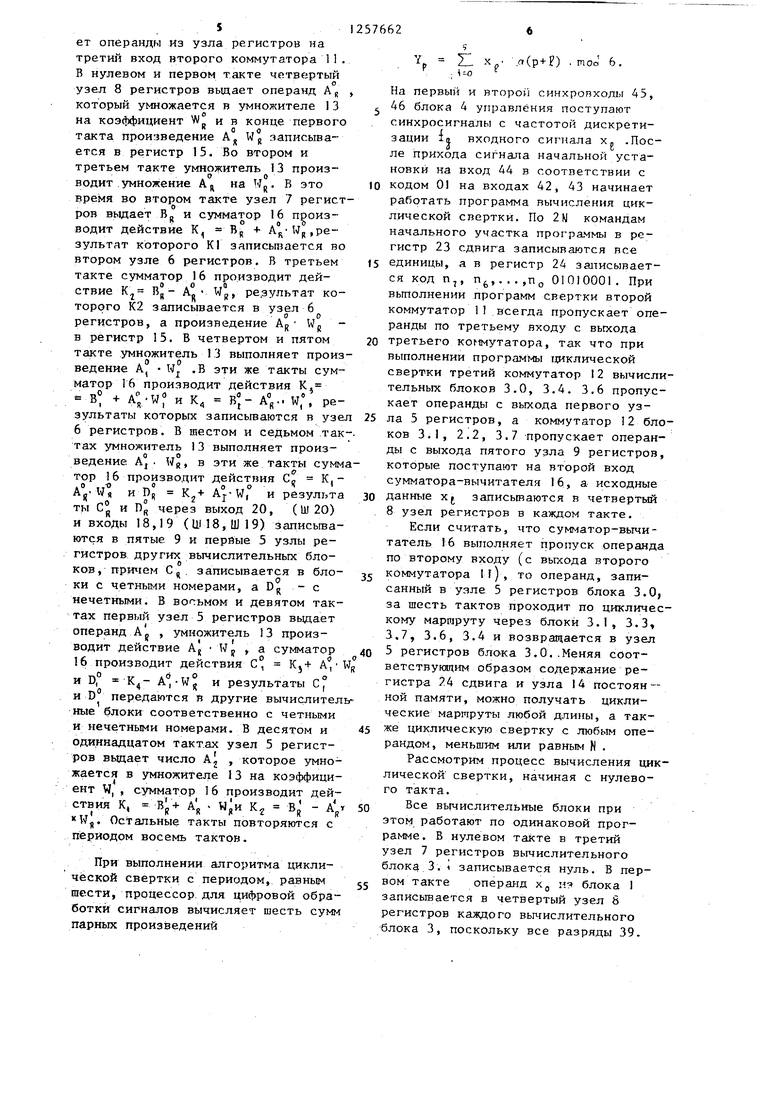

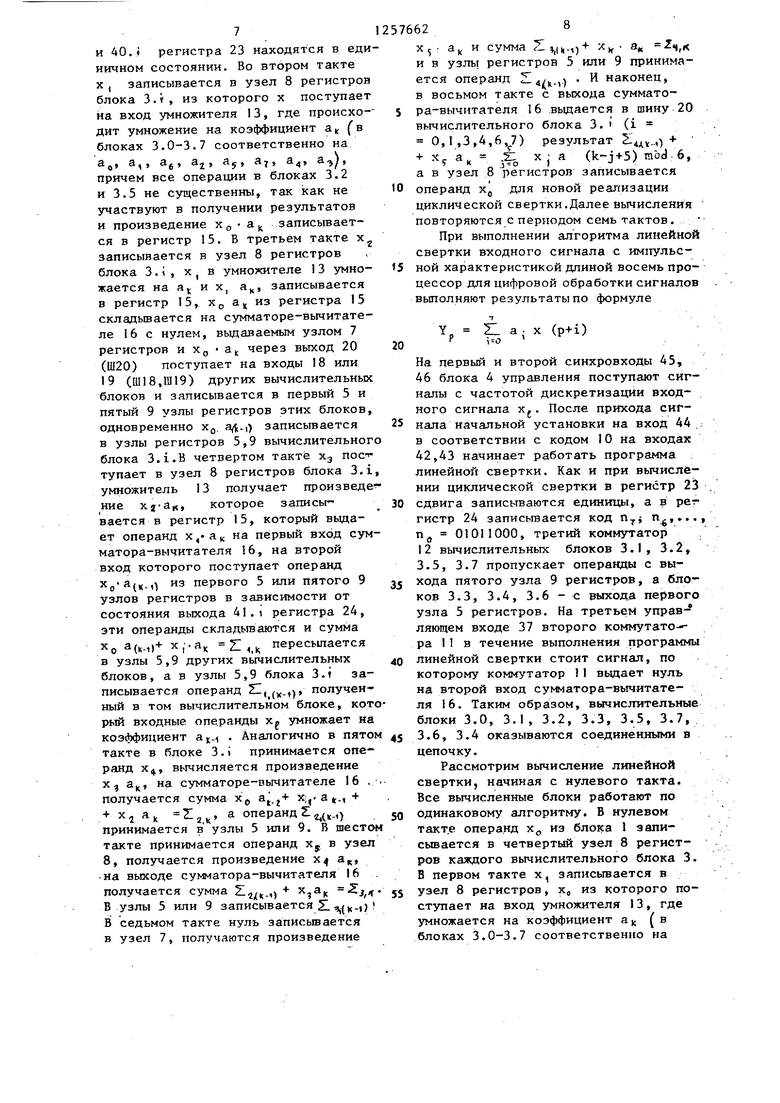

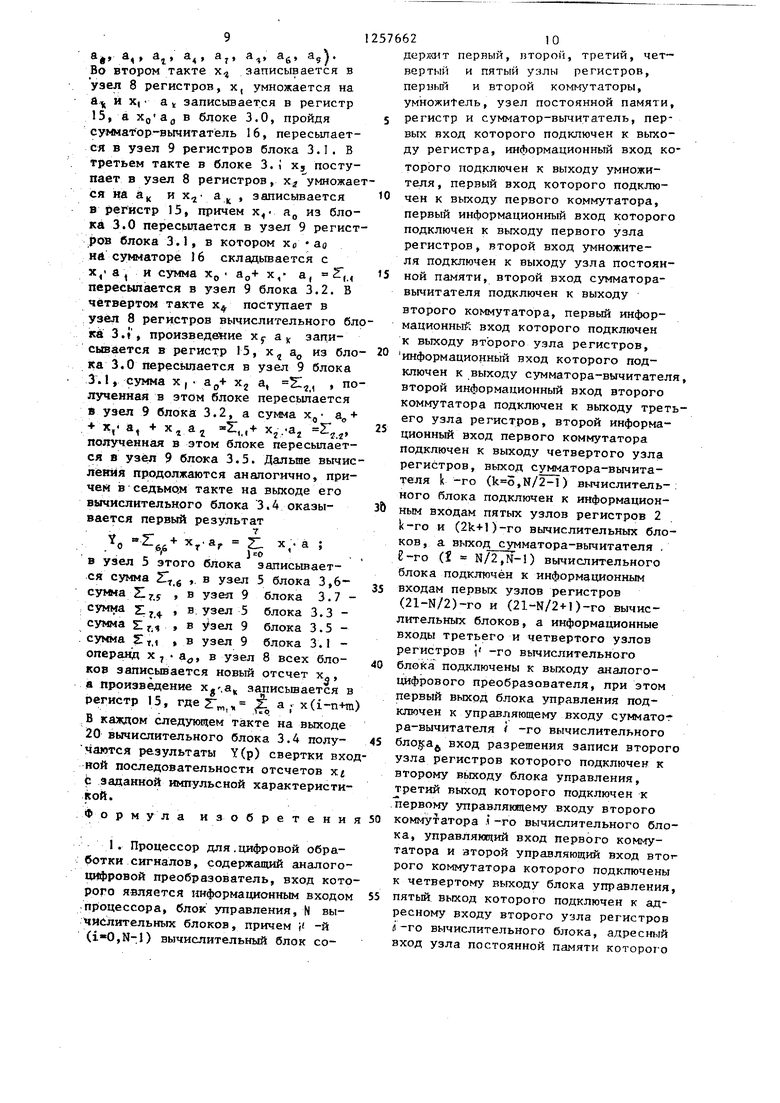

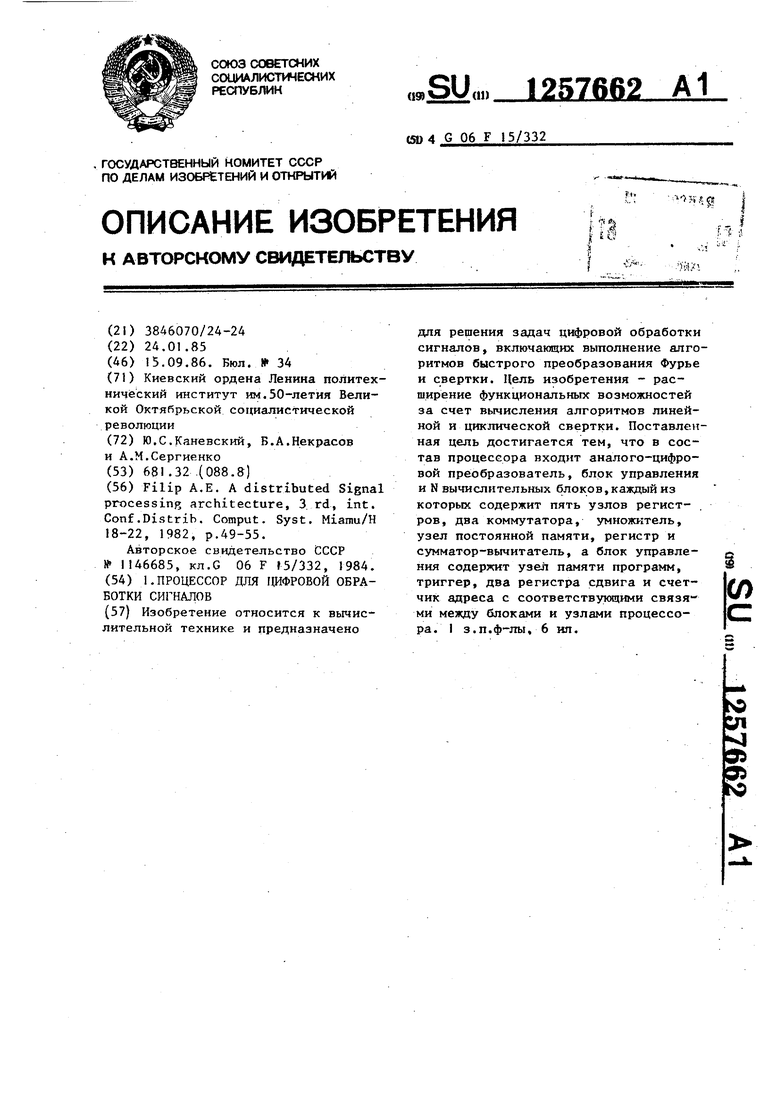

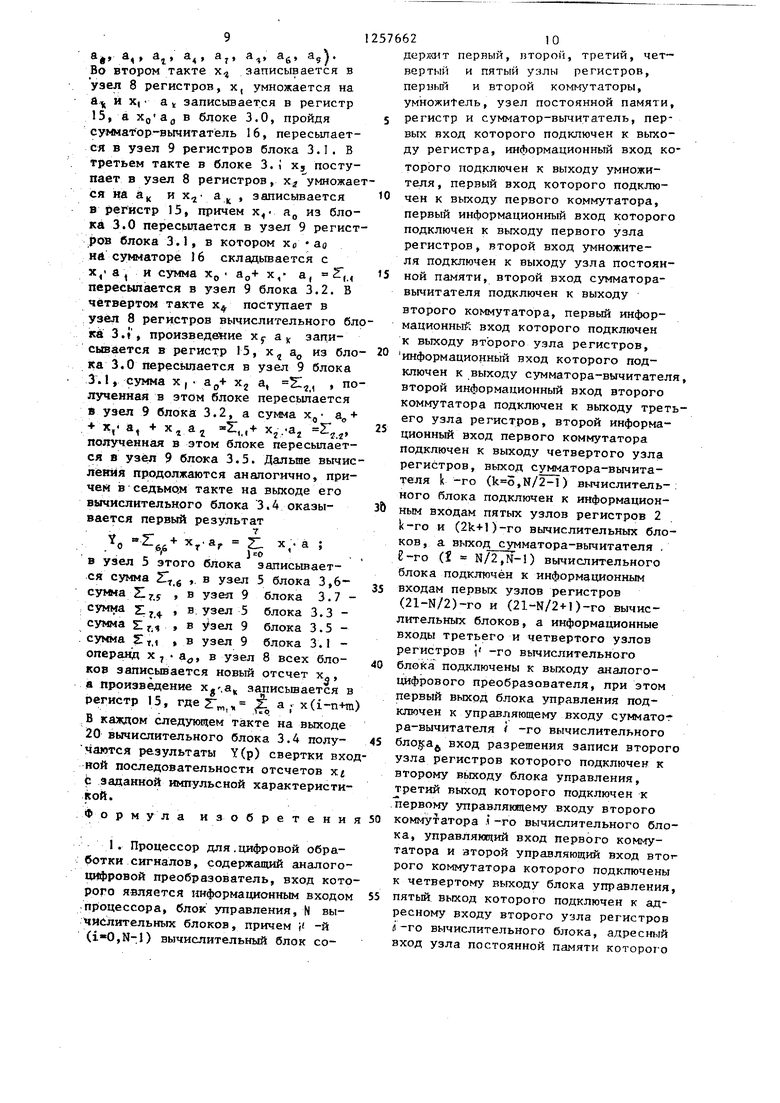

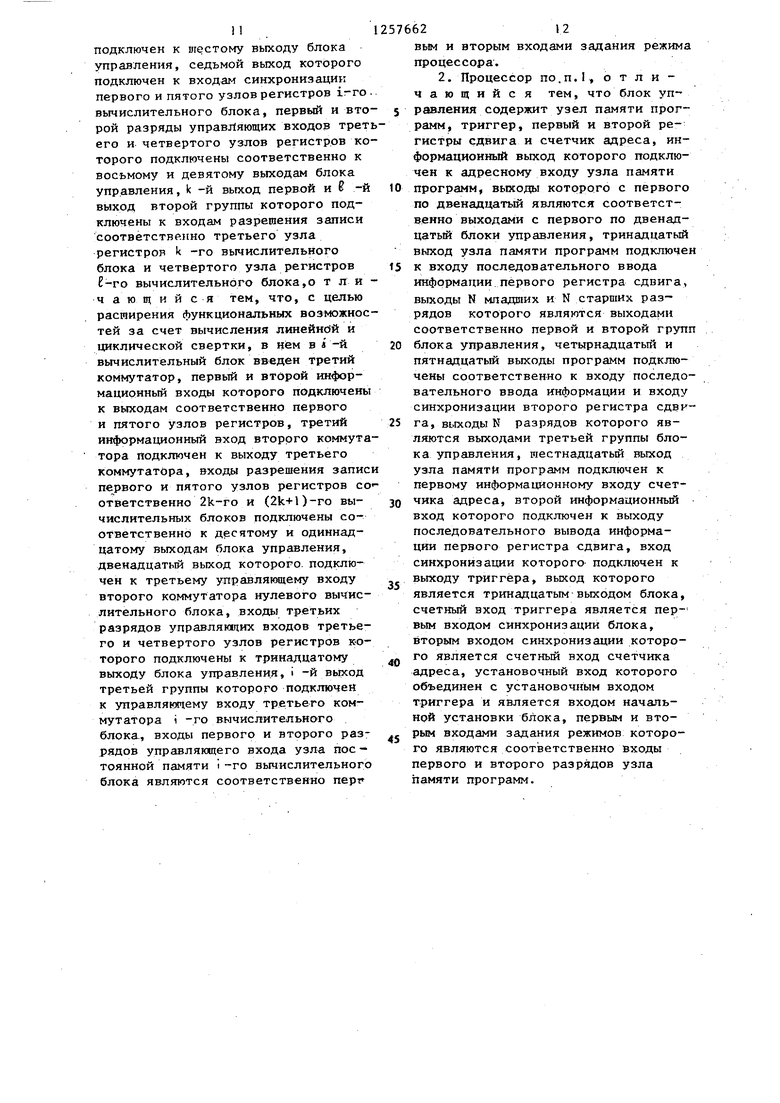

На фиг.1 изображена структура процессора цифровой обработки сиггт налов; на фиг.2 - структура вычислительного блока; на фиг.З - функциональная схема блока управления; на фиг.4,5,6 -обобщенные граф-схемы алгоритмов ВПФ, циклической и линейной свертки соответственно.

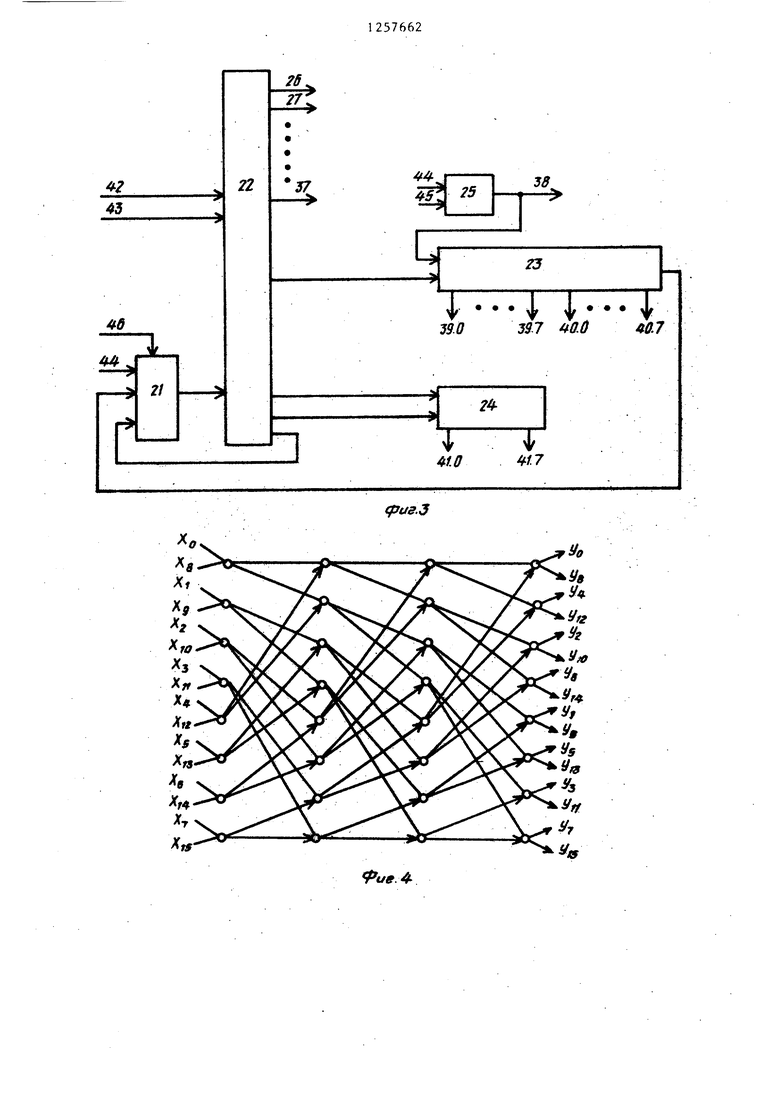

Процессор цифрс вой обработки сигналов содержит анапого-цифро- йой преобразователь 1,N 8 шин 2.0 2.1...., 2.7. N 8 вычислительных блоков 3.0, 3.1,...,3,7 и блок 4 управления. Каждый вычислительный блок фиг.2 содержит с первого по пятьй 5-9 регистров, первый 10, второй П, третий 12 коммутаторы, умножитель 13, узел 14 постоянной памяти, регистр 15, сумматор- вычитатель 16, первый 17, второй 18 и третий 19 входы и выход 20 нычис- дительного блока. Блок 4 управления (фнг.З) содержит счетчик 2} адреса, узел 22 памяти программ, первый 23 И второй 24 регистры сдвига, триггер 25, с Первого по тринадцатый выходы 26-38, первую группу выходов 39.0-39.7, вторую группу выходов 40.0-40.7 и третью группу выходов 41.0-41.7, первый 42 и второ 43 входы задания режимов, вход 44 начальной установки, первый 45 и второй 46 входы синхронизации.

При выполнении алгоритма БПФ процессор для цифровой обработки сигналов работает -следующим образом

В один и тот же момент времени все вычнслительные блоки выполкя- йт одну из п logjN+1 итераций алг ритма ВПФ, которой соответствует один ярус обобщенного графа алгоритма (фиг.4) . При обработке входной последовательности длиной 2N «16 вычислительный блок 3 J выполняет 1 -то базовую операцию данной итерации, обозначенную на графе Кружком, где i 0, N-1.Процессор дбрабаТьшает входные последователь57662

нести комплексных чисел: В°, В° ,.. . , By, АО Л|,.,., Rf х ( ,...,х, , которые поступают из блока 1 с частотой дискретизации ia входного сиг5 нала на входы 17 вычислительных блоков. На первый вход 45 синхронизации блока 4 управления поступает синхросигнал с частотой f- , получаемой из блока 1. На второй вход 46

О синхронизации блока 4 поступают синхроимпульсы с тактовой частотой i работы вычислительных блоков, причем соотношение частот синхронизации составляет

5 f,/f 2 ()/N.

По сигналу начальной установки на входе 44 блока 4 управления триггер 25 устанавливается в нуль, счетчик 21 устанавливает на своем выходе

20 нулевой адрес и из узла 22 памяти . программ в соответствии с кодом номера вьтолняемой программы 00 на входах 42,43 выбирается нулевая команда

программы БП. по которой на вход

25 ,

последовательного занесения регистров 23 и 24 подаются соответственно единица (S, 1) и нуль (82 О). В следующих тактах на вход синхронизации регистра 23 поступает синхг росигнап с частотой fa/2 с выхода триггера 25. Этот же синхросигнал поступает на разряд 38 управляющего входа узлов 7,8 регистров и по его уровню логического нуля в четный ре35 гистр узлов 7, 8 заггасывается реальная часть Afj или Bjj , а по уровню логической единицы - мнимая часть Ajj или Bj; - в нечетный регистр узлов 7,8. В каждом следую 0 щам такте в счетчике 21 увеличивается на единицу адрес команды и по следующим командам на входы регистров 23.24 подаются нули (S, О, Sg О), В следующем такте сигнала час 5 тоты 5j/2 единица с разряда 39(1-1) передвигается в разряд 39.1.Одновременно наличие единицы на выходах 39.1 и 40.1 разрядов регистра 23 является разрешением для записи

50 в, и А; соответственно в узлы 7 и 8 регистров вычислительного блока 3. Таким образом, за 4 fl тактов частоты ij, единица, зачисленная в регистр 23 при начальной установке

55 проходит весь регистр 23 от младшего разряда к старшему и поступает с выхода страршего разряда регистра 23 на вход признака счетчика 21,

зЬ

3

как F 1, а разряды регистра 24 оказываются заполненными нулями. При этом отсчеты исходной последовательности Ад;, A J. , BR, « BI; ока- зьшаются записанными в регистрах УР 7.0, УР 7.1, УР 8.0 и 8.1 узлов 7,8 регистров соответственно. По признаку F 1 программа переходит с участка ввода исходных данных для первой реализации ВПФ на участок вычисления БПФ. В этот момент по первой команде участка вычисления ВПФ в регистр 23 записьшается единица и после выполнения программы одной реализации БПФ процессор переходит в ожидание, которое длится до прихода признака F 1 с выхода регистра 23, что свидетельствует о том, что в узлах 7,8 регистров накоплены исходные данные для следующей реализации БПФ и вычислительный процесс на этом повторяется. Таким образом, одновременно с выполнением алгоритма БПФ в узлах 7,8 регистров накапливаются исходные данные, причем накопление исходных данных для четной реализации (г О) в нулевом и первом регистрах узлов 7,8, а для нечетной реализации () во вто ром и третьем регистрах узлов 7,8 осуществляется независимо от прО цесса вычисления.

В течение выполнения участка программы вычисления БПФ вычислительные блоки 3.i выполняют последовательно четыре базовые операции, соОтветствуклцие четырем, итерациям БПФ над исходными данными входной последовательности, записанной в узлы 7,8 на предьщутцем этапе. Базовая операция алгоритма БПФ заключается в вычислениях по формулам

Cf. RR+ AR-WR- AI-WI;

с, BI+ AR-Wi+ Aj, WR;

Dj Bf- AU-WJ-I- AI-WI;

DI BI- AR-WJ- Aj.Wg,

где A Re(An)+j Iin(A,),

B Re(B;)j ImCBS) « ««««e данные для базовой операции, записанные в узлах 7,8 регистров соотсг ветственно для ()-и итераций к записанные в узлах 5 и 9 регистров соответственно для (I 1,2,3)-й итерации:

С Re(Cg) + j Ira(Ci),

D Re(Dg) + j Im(Dj)

576624

результаты базовой операции, выдавав мые вычислительными блоками 3.0-3.7 по мере готовности.на выходы 20 и принимаемые как исходные данные А,Э 5 для базовых операций следующей ите рации вычислительными блоками 3.0- 3.7 согласно графу алгоритма БПФ и заданной конфигурации расположения шин и блоков.

Таким образом

e.,

В

ВГ

R

R 6+

f D

где 2 0,1,2,3 - номер итеращ1и; нижний индекс- номер вычислительного блока, равный номеру базовой операции в 2 -и итерации.

После вьтолнения последней итерации с номером три на выходы вычислительных блоков поступают результаты коэффициента Фурье, причем

30

35

Рассмотрим работу вычислительиого блока 3.1 при выполнении базовой операции, начиная с нулевого такта. Вычислительный блок 3.i выполняет базовую операцию во всех итерациях одинаково. Исключение состоит в том, что в нулевой итерации исходные данные А; и В| выдаются четвертым 8 и третьим 7 узлами регистров соответственно, а в остальных

итерациях - соответственно первым 5 и пятым 9 узлами регистров, кроме того, на вход узла 14 постоянной памяти поступает адрес, равный номеру текущей итерации. Поскольку

в регистре 24 записаны нули, то на шине 40.i - уровень логического нуля и третий коммутатор в течение Выполнения программы БЦФ пропускает операнды из узла регистров на третий вход второго коммутатора 11. В нулевом и первом такте четвертый узел 8 регистров выдает операнд Ар который умножается в умножителе I3 на коэффициент W и в конце первого такта произведение А W,, записывается в регистр 15. Во втором и

третьем такте умножитель 13 произо о водит.умножение Ац на W. В это

время во втором такте узел 7 регистров выдает Ви и сумматор 16 производит действие К, В + ,результат которого К1 записьпзается во втором узле 6 регистров. В третьем такте сумматор 16 производит действие Kj В„- w, результат которого К2 записывается в узел 6

.00

регистров, а произведение W - в регистр 15. В четвертом и пятом такте умножитель 13 выполняет произведение А W .В эти же такты сумматор 16 производит действия К, В° + и К, Bj- AV- W;. ре- зультаты которьгх записьтаются в узе 6 регистров. В шестом и седьмом так тах умножитель 13 выполняет произведение А|. Wg, в эти же такты cyNw ТОР 16 производит действия С К,- и D Aj-W° и резултмта ты Сд и Г) через выход 20, (Ш 20) и входы 18,19 (Ш18,Ш19) записываются в пятые 9 и первые 5 узлы регистров других вычислительных блоков, причем Со записывается в бло-

и

ки с четными номерами, а Dj - с нечетными. В восьмом и девятом тактах первый узел 5 регистров вьщает операнд А , умножитель 13 производит действие А W,j , а сумматор 16 производит действия С, Kj+ A., и D. Kj- A°-W.. и результаты С

л .

и D передаются в другие вычислител ные блоки соответственно с четными и нечетными номерами. В десятом и одиннадцатом тактах узел 5 регистров вьщает число Aj , которое умножается в умножителе 13 на коэффициент W,, сумматор 16 производит действия К, А - К Вд - А Д W. Остальные такты повторяются с периодом восемь тактов.

При выполнении алгоритма циклической свертки с периодом, равным шести, процессор, для цифровой обработки сигналов вычисляет шесть сумм парных произведений

Y Z1 X .nr(p-i-F) .moo 6. . Uo

На первый и BTOpoii синхровходы 45, 46 блока 4 управления поступают синхросигналы с частотой дискретизации In входного сигнала х. .После прихода сигнала начальной установки на вход 44 в соответствии с кодом 01 на входах 42, 43 начинает работать программа вычисления циклической свертки. По 2N командам начального участка программы в регистр 23 сдвига записываются все единицы, а в регистр 24 записывается код п,, п,...,П(, 01010001. При вьтолнении программ свертки второй коммутатор 11 всегда пропускает операнды по третьему входу с выхода третьего коммутатора, так что при выполнении программы 1 клической свертки третий коммутатор 12 вычислтельных блоков 3.0, 3.4. 3,6 пропускает операнды с выхода первого узла 5 регистров, а коммутатор 12 блков 3.1, 2.2, 3.7 пропускает операнды с выхода пятого узла 9 регистров которые поступают на второй вход сумматора-вычитателя 16, а исходные данные xj записьгоаются в четвертый 8 узел регистров в каждом такте.

Если считать, что сумматор-вычи- татель 16 выполняет пропуск операнд по второму входу (с вьгхода второго коммутатора If), то операнд, записанный в узле 5 регистров блока 3.0 за шесть тактов проходит по цикличекому маршруту через блоки 3.1, 3.3 3,7, 3.6, 3.4 и возвращается в узел 5 регистров блока З.О..Меняя соот- ветствугадим образом содержание регистра 24 сдвига и узла 14 постоянной памяти, можно получать циклические марпгруты любой длины, а также циклическую свертку с любым операндом, меньшим или равным N .

Рассмотрим процесс вычисления цилической свертки, начиная с нулевого такта.

Все вычислительные блоки при этом работают по одинаковой программе. В нулевом такте в третий узел 7 регистров вычислительного блока 3. записывается нуль. В первом такте операнд Хд н блока 1 записьшается в четвертый узел 8 регистров каждого вычислительного блока 3, поскольку все разряды 39.

7

и 40. регистра 23 находятся в единичном состоянии. Во втором такте X , записывается в узел 8 регистров блока 3.V, из которого х поступает на вход умножителя 13, где происходит умножение на коэффициент а (в блоках 3.0-3.7 соответственно на

0 6 Z У Т 4

причем все операции в блоках 3.2 и 3.5 не существенны, так как не участвуют в получении результатов и произведение х а записывается в регистр 15. В третьем такте х записывается в узел 8 регистров блока 3.1, X, в умножителе 13 умножается на а и X, Яц, записывается в регистр 15, Хр а из регистра 15 складьюается на сумматоре-вычитате- ле 16 с нулем, выдаваемым узлом 7 регистров и Х(, а через выход 20 (Ш20) поступает на входы 18 или 19 (Ш18,Ш19) других вычислительных блоков и записывается в первый 5 и пятый 9 узлы регистров этих блоков, одновременно х. а/.,) записьгеается в узлы регистров 5,9 вычислительног блока 3.1.В четвертом такте Xj пос- тупает в узел 8 регистров блока 3.1 умножитель 13 получает произведе ние XJ-HK, которое записывается в регистр 15, который выдает операнд х, а на первый вход сум- матора-вычитателя 16, на второй вход которого поступает операнд первого 5 или пятого 9 узлов регистров в зависимости от состояния выхода 41.t регистра 24, эти операнды складъшаются и сумма 0 (и-1)+ ZI,,, пересылается в узлы 5,9 других вычислительных блоков, а в узлы 5,9 блока 3.i записывается операнд ZI,.,), полученный в том вычислительном блоке, который входные операнды Хр умножает на коэффициент a.i . Аналогично в пятом такте в блоке 3.i принимается операнд х, вычисляется произведение х а,, на сумматоре-вычитателе 16 . получается сумма х, 3.j.j+ Х;,.а.,

+ Xj а г,к а операнд Z,j,(it-i) принимается в узлы 5 или 9. В шестом такте принимается операнд х в узел 8, получается произведение yi а, на выходе сумматора-вычитателя 16 . получается сумма 21 . + В узлы 5 или 9 записывается 21 ч,( к-|) В седьмом такте нуль записьгоается в узел 7, получаются произведение

576628

X,: а и сумма ,,.,,+ х. а ч,л и в узль регистров 5 или 9 принимается операнд 214/.,л И наконец, в восьмом такте с выхода суммато- 5 ра-вычитателя 16 выдается в шину 20 вычислительного блока 3. (1 0,1,3,4,6.7) результат + х а .г:, xj а (k-j-f5) mod.6, а в узел 8 регистров записывается

10 операнд х, для новой реализации

циклической свертки.Далее вычисления повторяются с периодом семь тактов.

При выполнении алгоритма линейной свертки входного сигнала с им1тульс 5 ной характеристикой длиной восемь процессор для цифровой обработки сигналов выполняют результаты по формуле

20

Y z:

р а . X (р+1)

г

На первый и второй синхровходы 45, 46 блока 4 управления поступают сигналы с частотой дискретизации входного сигнала х. После прихода сигнала начальной установки на вход 44., в соответствии с кодом 10 на входах 42,43 начинает работать программа линейной свертки. Как и при вычислении циклической свертки в регистр 23

сдвига записываются единицы, а в per- гистр 24 записывается код п. п,.., Пд 01011000, третий коммутатор 12 вычислительных блоков 3.1, 3.2, 3.5, 3.7 пропускает операнды с выхода пятого узла 9 регистров, а бло ков 3.3, 3.4, 3.6 -с выхода первого узла 5 регистров. На третьем управляющем входе 37 второго коммутато- ра 11 в течение выполнения программы

линейной свертки стоит сигнал, по которому коммутатор I1 выдает нуль на второй вход сумматора-вычитателя 16. Таким образом, вычислительные блоки 3.0, 3.1, 3.2, 3.3, 3.5, 3.7,

3.6, 3.4 оказываются соединенными в цепочку.

Рассмотрим вычисление линейной свертки, начиная с нулевого такта. Все вычисленные блоки работают по

одинаковому алгоритму. В нулевом такте операнд х из блока 1 записывается в четвертый узел 8 регистров каждого вычислительного блока 3. В первом такте х записывается в

узел 8 регистров, х, из которого поступает на вход умножителя 13, где умножается на коэффициент а (в блоках 3.0-3.7 соответственно на

Й|| 1

4 7

ag,

держит первый, второй, третий, четвертый и пятый узлы регистров, периьй и второй коммутаторы, yмнoжиteль, узел постоянной памяти, 5 регистр и сумматор-вычитатель, первых вход которого подключен к выходу регистра, информационный вход которого подключен к выходу умножителя , первый вход которого подключен к выходу первого коммутатора, первый информационный вход которого подключен к выходу первого узла регистров, второй вход умножителя подключен к выходу узла постоян- 15 ной памяти, второй вход сумматора- вьгчитателя подключен к выходу

второго коммутатора, первый информационный вход которого подключен к выходу второго узла регистров.

25

Во втором такте х записывается в узел 8 регистров, х, умножается на в.у и Х| а записывается в регистр 15, а Хд ад в блоке 3.0, пройдя сумматор-вычитатель 16, пересыпается в узел 9 регистров блока 3.1. В третьем такте в блоке 3.i Xj поступает в узел 8 регистров, х умножается на Эк и а , записывается Ю в регистр 15, причем а из блока 3.0 пересьшается в узел 9 регистров блока 3.1, в котором хо ао НА сумматоре 16 складывается с X, а , и сумма х АО i ° (м пересьшается в узел 9 блока 3.2. В четвертом такте х поступает в узел 8 регистров вычислительного блоке 3.i , произведение Xf а записьшается в регистр 15, х а из бло- 20 информационньй вход которого под- ка 3.0 пересьщается в узел 9 блока ключен к выходу сумматора-вычитателя,

второй информационный вход второго коммутатора подключен к выходу третьего узла регистров, второй информационный вход первого коммутатора подключен к выходу четвертого узла регистров, выход су| атора-вычита- теля k -го (,N/2-l) вычислитель-: ного блока подключен к информацион- 3& ным входам пятых узлов регистров 2 k-ro и (2k-H)-ro вычислительных блоков, а выход сумматора-вычитателя , -го (f N/2,N-1) вычислительного блока подключён к информационным 35 входам первых узлов регистров

(21-N/2)-ro и (21-N/2-i-l)-ro вычислительных блоков, а информационные входы третьего и четвертого узлов регистров i -го вьтчислительного 40 блока подключены к выходу аналого- цифрового преобразователя, при этом первый выход блока управления подключен к управляющему входу сумматог ра-вычитателя -го вычислительного бло§:а вход разрешения записи второго узла регистров которого подключен к второму выходу блока управления, третий выход которого подключен к ,первому управляющему входу второго

Формула и 3 о б р е т е н и я 50 коммутатора л-го вычислительного блока, управлямщий вход первого коммутатора и зторой управляющий вход рого коммутатора которого подключены к четвертому выходу блока управления.

3.1, сумма X,- а„+ х а, I, полученная в этом блоке пересылается в узел 9 блока: 3.2, а сумма а„+ + х,- а, + Xj aj 5:,,,-4- Xj.-a г.г полученная в этом блоке пересьшается в узел 9 блока 3.5. Дальше вычисления продолжаются аналогично, при- чен в седьмом такте на выходе его вычислительного блока 3.4 оказывается первый результат

Л -г «г х,.а ; в узел 5 этого блока записьшает- ся сумма 2Г g ,. в узел 5 блока 3,6- сумна Z.7.f в узел 9 блока 3.7 - сумма 217ц. . в узел 5 блока 3.3 - сумма ЕГ/, , в Узел 9 блока 3.5 - сумма 2Гт,1 в узел 9 блока 3.1 - операад х а, в узел 8 всех блоков записывается новый отсчет х, а произведение .а записьюается в регистр 15, где2 „,, Я; x(i-n+m) В каждом следующем такте на выходе 20 вычислительного блока 3.4 полу- чаются результаты Y(p) свертки входной последовательности отсчетов х t заданной импульсной характеристикой.

1. Процессор для.цифровой обработки сигналов, содержащий аналого- цифровой преобразователь, вход кото45

рого является информационным входом 55 пятьй выход которого подключен к ад- процессора, блок управления, N вы- ресному входу второго узла регистров

i-го вычислительного блока, адресный вход узла постоянной памяти которого

чи Лительных блоков, причем Н -и (i«0,N-l) вычислительный блок со5766210

держит первый, второй, третий, четвертый и пятый узлы регистров, периьй и второй коммутаторы, yмнoжиteль, узел постоянной памяти, 5 регистр и сумматор-вычитатель, первых вход которого подключен к выходу регистра, информационный вход которого подключен к выходу умножителя , первый вход которого подключен к выходу первого коммутатора, первый информационный вход которого подключен к выходу первого узла регистров, второй вход умножителя подключен к выходу узла постоян- 15 ной памяти, второй вход сумматора- вьгчитателя подключен к выходу

второго коммутатора, первый информационный вход которого подключен к выходу второго узла регистров.

Ю20 информационньй вход которого под- ключен к выходу сумматора-вычитателя

11 .

подключен к шестому выходу блока управления, седьмой выход которого подключен к входам синхронизации первого и пятого узлов регистров i-ro . вычислительного блока, первый и второй разряды управляющих входов треть его и четвертого узлов регистров которого подключены соответственно к восьмому и девятому выходам блока управления, k -и выход первой и f -и выход второй группы которого подключены к входам разрешения записи соответственно третьего узла регистров k -го вычислительного блока и четвертого узла регистров Е-го вычислительного блока,о т л и - ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей за счет вычисления линейжЗй и циклической свертки, в нём в « -и вычислительный блок введен третий коммутатор, первый и второй информационный входы которого подключены к выходам соответственно первого и пятого узлов регистров, третий информационный вход второго коммутатора подключен к выходу третьего коммутатора, входы разрешения записи первого и пятого узлов регистров со ответственно 2k-ro и (2k+l)-ro вычислительных блоков подключены соответственно к десятому и одиннадцатому выходам блока управления, двенадцатый выход которого, подключен к третьему управляющему входу второго коммутатора нулевого вычислительного блока, входы третьих разрядов управляющих входов третьего и четвертого узлов регистров которого подключены к тринадцатому выходу блока управления, i -и выход третьей группы которого подключен к управляющему входу третьего коммутатора i -го вычислительного блока., входы первого и второго разрядов управляющего входа узла пос- тоянной памяти 1-го вычислительного блока являются соответственно перт

5766212

вым и вторым входами задания режима процессора.

2. Процессор ПО.П.1, о т л и - чающийся тем, что блок уп- 5 равления содержит узел памяти программ, триггер, первый и второй регистры сдвига и счетчик адреса, информационный выход которого подключен к адресному входу узла памяти

10 программ, выходы которого с первого по двенадцатый являются соответственно выходами с первого по двенадцатый блоки управления, тринадцатый выход узла памяти программ подключен

15 к входу последовательного ввода

информации.первого регистра сдвига, выходы N мпадпшх и N старщих разрядов которого являются выходами соответственно первой и второй групп

20 блока управления, четырнадцать и пятнадцатый выходы программ подключены соответственно к входу последовательного ввода информации и входу синхронизации второго регистра сдви25 га, выходы N разрядов которого являются выходами третьей группы блока управления, шестнадцатый выход узла памяти программ подключен к первому информационному входу счет30 чика адреса, второй информационный вход которого подключен к выходу последовательного вывода информации первого регистра сдвига, вход синхронизации которого подключен к выходу триггера, выход которого является тринадцатым выходом блока, счетный вход триггера является первым входом синхронизации блока, вторым входом синхронизации которого является счетный вход счетчика адреса, установочный вход которого объединен с установочным входом триггера и является входом начальной установки блока, первым н втоj рым входами задания режимов которого являются соответственно входы первого и второго разрядов узла памяти программ.

5

tpU8.3

УО

ug 4

Хз , X

Xs Ха Хг X, Xj К,о

(риг 5

Фиг 6

Составитель А.Баранов Редактор Н.Швыдкая Техред Л.Сердюкова Корректор С.Черни

Заказ 4958/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Арифметическое устройство для быстрого преобразования фурье | 1984 |

|

SU1234846A1 |

| Устройство для вычисления многочленов | 1988 |

|

SU1617445A1 |

Изобретение относится к вычислительной технике и предназначено для решения задач цифровой обработки сигналов, включающих выполнение алгоритмов быстрого преобразования Фурье и свертки. Цель изобретения - расширение функциональных возможностей за счет вычисления алгоритмов линейной и циклической свертки. Поставленная цель достигается тем, что в состав процессора входит аналого-цифровой преобразователь, блок управления и N вычислительных блоков,каждый из которых содержит пять узлов регистров, два коммутатора, умножитель, узел постоянной памяти, регистр и сумматор-вычитатель, а блок управления содерз-сит узел памяти программ, триггер, два регистра сдвига и счетчик адреса с соответствующими связями между блоками и узлами процессора. 1 з.п.ф-лы, 6 ил. W с д ел 41 0д

| Filip А.Е | |||

| А distributed Signal processing architecture, 3 rd, int | |||

| Conf.Distrib | |||

| Comput | |||

| Syst | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Авторское свидетельство СССР 1146685, кл.С 06 F J5/332, 1984. | |||

Авторы

Даты

1986-09-15—Публикация

1985-01-24—Подача