Изобретение относится к измерительной технике и предназначено для автоматизации измерения и контроля линейных перемещений.

Целью изобретения является повышение точности преобразователя.

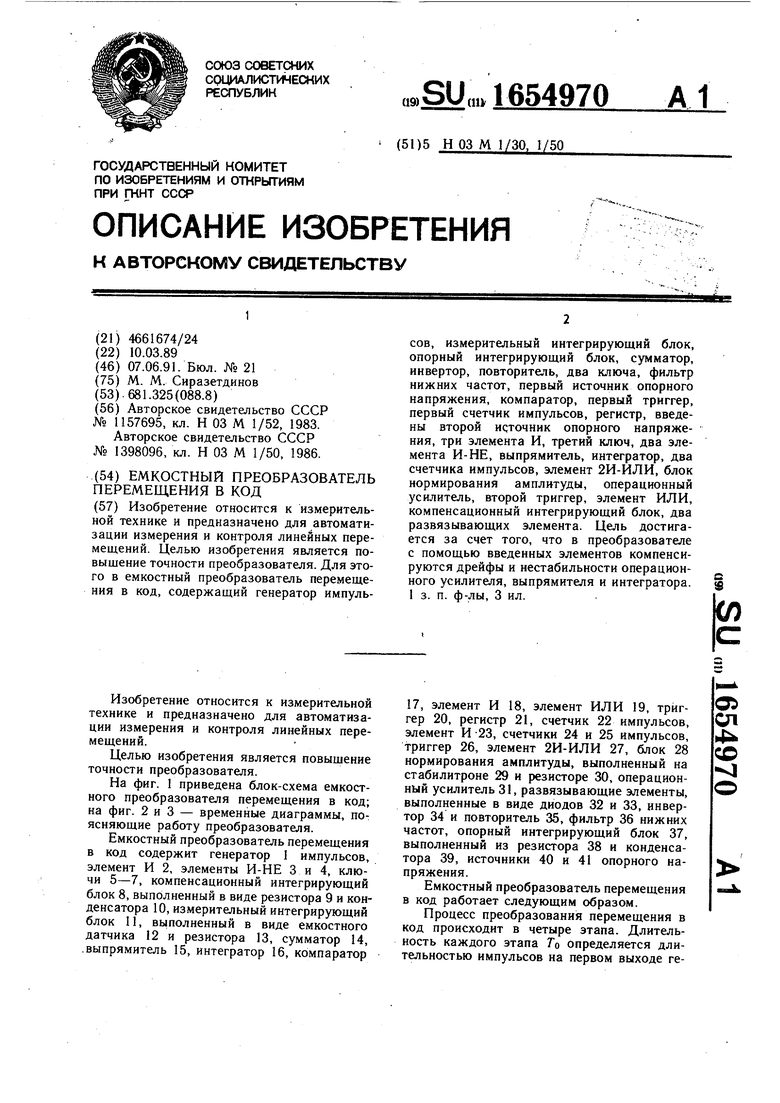

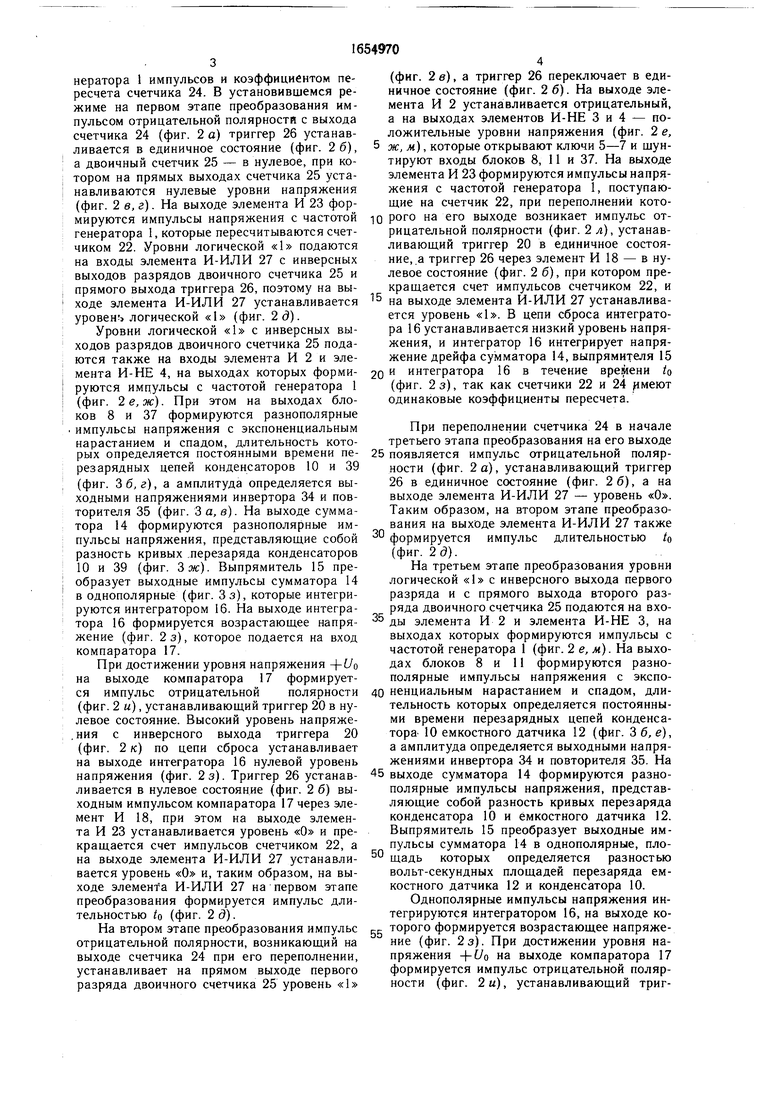

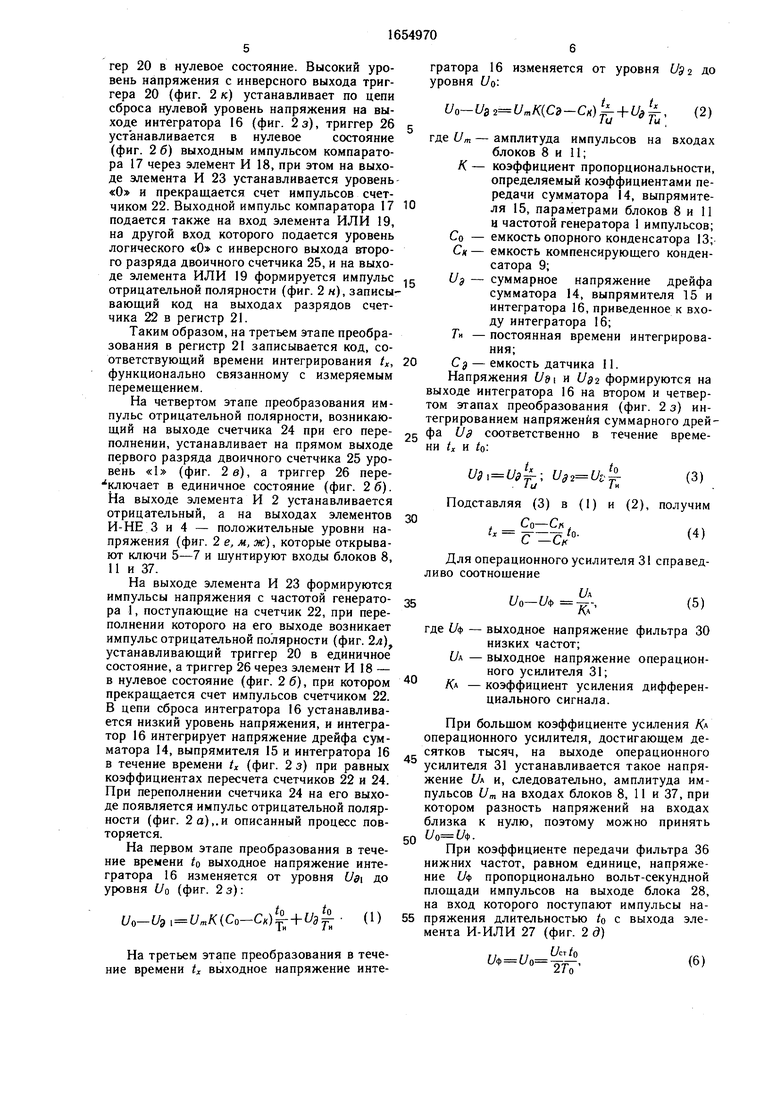

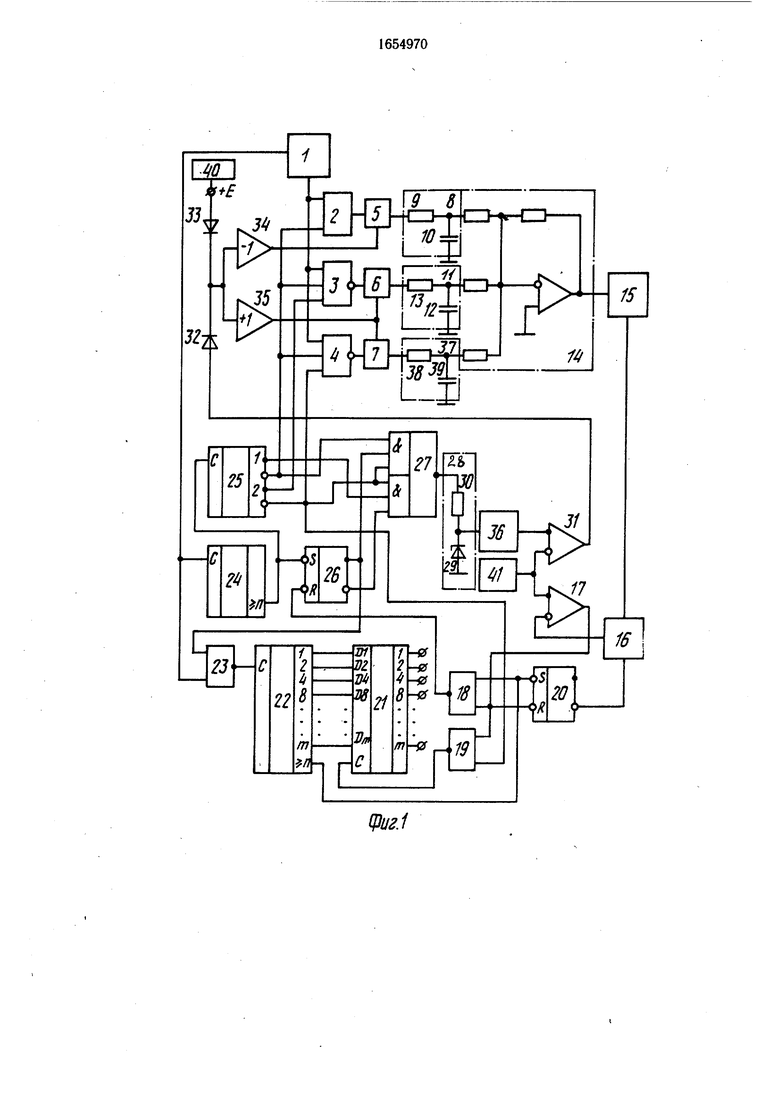

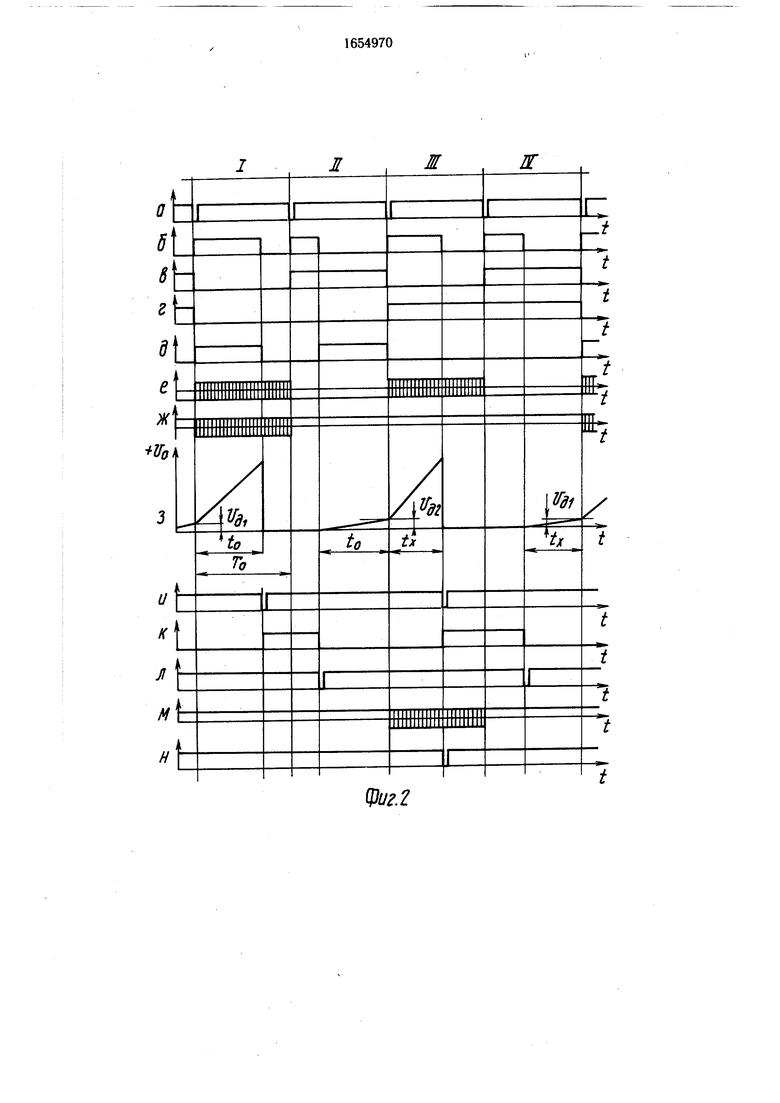

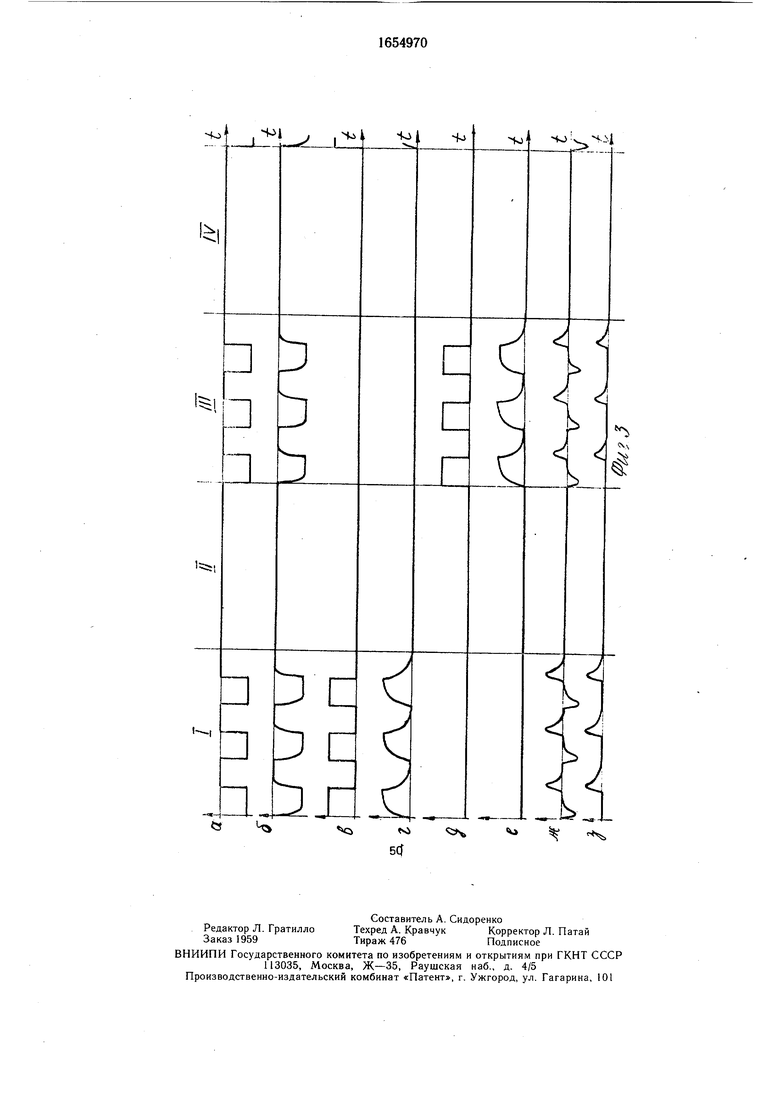

На фиг. 1 приведена блок-схема емкостного преобразователя перемещения в код; на фиг. 2 и 3 - временные диаграммы, поясняющие работу преобразователя.

Емкостный преобразователь перемещения в код содержит генератор 1 импульсов, элемент И 2, элементы И-НЕ 3 и 4, ключи 5-7, компенсационный интегрирующий блок 8, выполненный в виде резистора 9 и конденсатора 10, измерительный интегрирующий блок 11, выполненный в виде емкостного датчика 12 и резистора 13, сумматор 14, выпрямитель 15, интегратор 16, компаратор

17, элемент И 18, элемент ИЛИ 19, триггер 20, регистр 21, счетчик 22 импульсов, элемент И 23, счетчики 24 и 25 импульсов, триггер 26, элемент 2И-ИЛИ 27, блок 28 нормирования амплитуды, выполненный на стабилитроне 29 и резисторе 30, операционный усилитель 31, развязывающие элементы, выполненные в виде диодов 32 и 33, инвертор 34 и повторитель 35, фильтр 36 нижних частот, опорный интегрирующий блок 37, выполненный из резистора 38 и конденсатора 39, источники 40 и 41 опорного напряжения.

Емкостный преобразователь перемещения в код работает следующим образом.

Процесс преобразования перемещения в код происходит в четыре этапа. Длительность каждого этапа Т0 определяется длительностью импульсов на первом выходе геОЭ

сд

Ј

СО

нератора 1 импульсов и коэффициентом пересчета счетчика 24. В установившемся режиме на первом этапе преобразования импульсом отрицательной полярности с выхода счетчика 24 (фиг. 2 а) триггер 26 устанавливается в единичное состояние (фиг. 26), а двоичный счетчик 25 - в нулевое, при котором на прямых выходах счетчика 25 устанавливаются нулевые уровни напряжения (фиг. 2 в, г). На выходе элемента И 23 формируются импульсы напряжения с частотой генератора 1, которые пересчитываются счетчиком 22. Уровни логической «1 подаются на входы элемента И-ИЛИ 27 с инверсных выходов разрядов двоичного счетчика 25 и прямого выхода триггера 26, поэтому на выходе элемента И-ИЛИ 27 устанавливается уровень логической «1 (фиг. 2(5).

Уровни логической «1 с инверсных выходов разрядов двоичного счетчика 25 подаются также на входы элемента И 2 и элемента И-НЕ 4, на выходах которых формируются импульсы с частотой генератора 1 (фиг. 2е, ж). При этом на выходах блоков 8 и 37 формируются разнополярные импульсы напряжения с экспоненциальным нарастанием и спадом, длительность которых определяется постоянными времени перезарядных цепей конденсаторов 10 и 39 (фиг. 36, г), а амплитуда определяется выходными напряжениями инвертора 34 и повторителя 35 (фиг. За, s). Ha выходе сумматора 14 формируются разнополярные импульсы напряжения, представляющие собой разность кривых перезаряда конденсаторов 10 и 39 (фиг. Зж). Выпрямитель 15 преобразует выходные импульсы сумматора 14 в однополярные (фиг. Зз), которые интегрируются интегратором 16. На выходе интегратора 16 формируется возрастающее напряжение (фиг. 2з), которое подается на вход компаратора 17.

При достижении уровня напряжения на выходе компаратора 17 формируется импульс отрицательной полярности (фиг. 2 и), устанавливающий триггер 20 в нулевое состояние. Высокий уровень напряжения с инверсного выхода триггера 20 (фиг. 2 к) по цепи сброса устанавливает на выходе интегратора 16 нулевой уровень напряжения (фиг. 2з). Триггер 26 устанавливается в нулевое состояние (фиг. 2 б) выходным импульсом компаратора 17 через элемент И 18, при этом на выходе элемента И 23 устанавливается уровень «О и прекращается счет импульсов счетчиком 22, а на выходе элемента И-ИЛИ 27 устанавливается уровень «О и, таким образом, на выходе элемента И-ИЛИ 27 на первом этапе преобразования формируется импульс длительностью to (фиг. 2д).

На втором этапе преобразования импульс отрицательной полярности, возникающий на выходе счетчика 24 при его переполнении, устанавливает на прямом выходе первого разряда двоичного счетчика 25 уровень «1

(фиг. 2 в), а триггер 26 переключает в единичное состояние (фиг. 26). На выходе элемента И 2 устанавливается отрицательный, а на выходах элементов И-НЕ 3 и 4 - положительные уровни напряжения (фиг. 2 е,

ж, м), которые открывают ключи 5-7 и шунтируют входы блоков 8, 11 и 37. На выходе элемента И 23 формируются импульсы напряжения с частотой генератора 1, поступающие на счетчик 22, при переполнении кото0 рого на его выходе возникает импульс отрицательной полярности (фиг. 2 л), устанавливающий триггер 20 в единичное состояние, а триггер 26 через элемент И 18 - в нулевое состояние (фиг. 2 б), при котором прекращается счет импульсов счетчиком 22, и

5 на выходе элемента И-ИЛИ 27 устанавливается уровень «1. В цепи сброса интегратора 16 устанавливается низкий уровень напряжения, и интегратор 16 интегрирует напряжение дрейфа сумматора 14, выпрямителя 15

0 и интегратора 16 в течение времени to (фиг. 2з), так как счетчики 22 и 24 имеют одинаковые коэффициенты пересчета.

При переполнении счетчика 24 в начале третьего этапа преобразования на его выходе

5 появляется импульс отрицательной полярности (фиг. 2 а), устанавливающий триггер 26 в единичное состояние (фиг. 26), а на выходе элемента И-ИЛИ 27 - уровень «О. Таким образом, на втором этапе преобразования на выходе элемента И-ИЛИ 27 также

0 формируется импульс длительностью /о (фиг. 2(3).

На третьем этапе преобразования уровни логической «1 с инверсного выхода первого разряда и с прямого выхода второго разряда двоичного счетчика 25 подаются на вхо5 ды элемента И 2 и элемента И-НЕ 3, на выходах которых формируются импульсы с частотой генератора 1 (фиг. 2 е, м). На выходах блоков 8 и 11 формируются разно- полярные импульсы напряжения с экспо0 ненциальным нарастанием и спадом, длительность которых определяется постоянными времени перезарядных цепей конденсатора 10 емкостного датчика 12 (фиг. 36, е), а амплитуда определяется выходными напряжениями инвертора 34 и повторителя 35. На

5 выходе сумматора 14 формируются разно- полярные импульсы напряжения, представляющие собой разность кривых перезаряда конденсатора 10 и емкостного датчика 12. Выпрямитель 15 преобразует выходные импульсы сумматора 14 в однополярные, площадь которых определяется разностью вольт-секундных площадей перезаряда емкостного датчика 12 и конденсатора 10.

Однополярные импульсы напряжения интегрируются интегратором 16, на выходе которого формируется возрастающее напряжение (фиг. 2з). При достижении уровня напряжения + С/о на выходе компаратора 17 формируется импульс отрицательной полярности (фиг. 2 и), устанавливающий триг0

rep 20 в нулевое состояние. Высокий уровень напряжения с инверсного выхода триггера 20 (фиг. 2 к) устанавливает по цепи сброса нулевой уровень напряжения на выходе интегратора 16 (фиг. 2з), триггер 26 устанавливается в нулевое состояние (фиг. 2 б) выходным импульсом компаратора 17 через элемент И 18, при этом на выходе элемента И 23 устанавливается уровень «О и прекращается счет импульсов счетчиком 22. Выходной импульс компаратора 17 подается также на вход элемента ИЛИ 19, на другой вход которого подается уровень логического «О с инверсного выхода второго разряда двоичного счетчика 25, и на выходе элемента ИЛИ 19 формируется импульс отрицательной полярности (фиг. 2 н), записывающий код на выходах разрядов счетчика 22 в регистр 21.

Таким образом, на третьем этапе преобразования в регистр 21 записывается код, соответствующий времени интегрирования tx, функционально связанному с измеряемым перемещением.

На четвертом этапе преобразования импульс отрицательной полярности, возникающий на выходе счетчика 24 при его пере- полнении, устанавливает на прямом выходе первого разряда двоичного счетчика 25 уровень «1 (фиг. 2 в), а триггер 26 пере- ключает в единичное состояние (фиг. 26). На выходе элемента И 2 устанавливается отрицательный, а на выходах элементов И-НЕ 3 и 4 - положительные уровни напряжения (фиг. 2 е, м, ж), которые открывают ключи 5-7 и шунтируют входы блоков 8, 11 и 37.

На выходе элемента И 23 формируются импульсы напряжения с частотой генерато- ра 1, поступающие на счетчик 22, при переполнении которого на его выходе возникает импульс отрицательной полярности (фиг. 2л)г устанавливающий триггер 20 в единичное состояние, а триггер 26 через элемент И 18 - в нулевое состояние (фиг. 2 б), при котором прекращается счет импульсов счетчиком 22. В цепи сброса интегратора 16 устанавливается низкий уровень напряжения, и интегратор 16 интегрирует напряжение дрейфа сумматора 14, выпрямителя 15 и интегратора 16 в течение времени tx (фиг. 2 з) при равных коэффициентах пересчета счетчиков 22 и 24. При переполнении счетчика 24 на его выходе появляется импульс отрицательной полярности (фиг. 2 а),.и описанный процесс повторяется.

На первом этапе преобразования в течение времени to выходное напряжение интегратора 16 изменяется от уровня U$ до уровня UQ (фиг. 2 з):

UQ-U9 ,t/«/f(Co-C)jr + I/aЈ

гратора 16 изменяется от уровня t/$2 до уровня UQ:

U0-UBF UaK(C9-C,f) + U9 (2)

где Uт - амплитуда импульсов на входах

блоков 8 и 11;

К - коэффициент пропорциональности, определяемый коэффициентами передачи сумматора 14, выпрямителя 15, параметрами блоков 8 и 11 и частотой генератора 1 импульсов; С0 - емкость опорного конденсатора 13; С - емкость компенсирующего конденсатора 9;

Ug - суммарное напряжение дрейфа сумматора 14, выпрямителя 15 и интегратора 16, приведенное к входу интегратора 16;

Т« - постоянная времени интегрирования;

С 0 - емкость датчика 11. Напряжения 1)$ и Ugz формируются на выходе интегратора 16 на втором и четвертом этапах преобразования (фиг. 2 з) интегрированием напряжения суммарного дрейфа U д соответственно в течение времени tf и to

U9i

. 1Ц/и

(3)

Подставляя (3) в (1) и (2), получим

, Со-Сл

- (4)

Для операционного усилителя 3 справедливо соотношение

Г ГIIkfo

U о- t/ф -тг-, ДА

(5)

где t/Ф - выходное напряжение фильтра 30

низких частот;

ЈЛ - выходное напряжение операционного усилителя 31;

ЯА - коэффициент усиления дифференциального сигнала.

35

При большом коэффициенте усиления /(А операционного усилителя, достигающем десятков тысяч, на выходе операционного усилителя 31 устанавливается такое напряжение Lfo и, следовательно, амплитуда импульсов Um на входах блоков 8, 11 и 37, при котором разность напряжений на входах близка к нулю, поэтому можно принять

50 .

При коэффициенте передачи фильтра 36 нижних частот, равном единице, напряжение f/Ф пропорционально вольт-секундной площади импульсов на выходе блока 28, на вход которого поступают импульсы на55 пряжения длительностью to с выхода элемента И-ИЛИ 27 (фиг. 2д)

| название | год | авторы | номер документа |

|---|---|---|---|

| Емкостный преобразователь перемещения в код | 1986 |

|

SU1398096A1 |

| Емкостно-электронный преобразователь перемещения | 1984 |

|

SU1221483A1 |

| Способ преобразования перемещения в длительность импульсов и устройство для его осуществления (его варианты) | 1984 |

|

SU1227939A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Устройство для преобразования перемещения во временной интервал | 1986 |

|

SU1415035A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

Изобретение относится к измерительной технике и предназначено для автоматизации измерения и контроля линейных перемещений. Целью изобретения является повышение точности преобразователя. Для этого в емкостный преобразователь перемещения в код, содержащий генератор импульсов, измерительный интегрирующий блок, опорный интегрирующий блок, сумматор, инвертор, повторитель, два ключа, фильтр нижних частот, первый источник опорного напряжения, компаратор, первый триггер, первый счетчик импульсов, регистр, введены второй идточник опорного напряжения, три элемента И, третий ключ, два элемента И-НЕ, выпрямитель, интегратор, два счетчика импульсов, элемент 2И-ИЛИ, блок нормирования амплитуды, операционный усилитель, второй триггер, элемент ИЛИ, компенсационный интегрирующий блок, два развязывающих элемента. Цель достигается за счет того, что в преобразователе с помощью введенных элементов компенсируются дрейфы и нестабильности операционного усилителя, выпрямителя и интегратора. 1 з. п. ф-лы, 3 ил. I Л

На третьем этапе преобразования в течение времени tx выходное напряжение инте,,.,t/ст/о

,

(6)

(7)

где и„ напряжение стабилизации стабилитрона 29. Из выражений (4) и (6) получим

2UoT0 Со-С

t/стСдС К

В выражении (7) результат преобразования определяется отношением напряжений, которое может быть воспроизведено с достаточно высокой точностью, и отношением емкостей и поэтому не зависит от изменений диэлектрической проницаемости среды. Длительность этапа преобразования Т0 может быть получена с высокой точностью стабилизацией частоты генератора импульсов кварцевым резонатором.

Формула изобретения

10

15

митель с информационным входом интегратора, выход которого соединен с вторым входом компаратора, выход которого соединен с первыми входами второго элемента И, элемента ИЛИ и первого триггера, выход которого соединен с управляющим входом интегратора, выход первого источника опорного напряжения соединен с первым входом операционного усилителя, выход которого соединен через второй развязываю-, щий элемент с входом инвертора, второй выход генератора импульсов соединен со счетным входом второго счетчика импульсов, первым входом третьего элемента И, выход которого соединен со счетным входом первого счетчика импульсов, выход переполнения которого соединен с вторыми входами первого триггера и второго элемента И, выход которого соединен с первым входом второго триггера, выход второго счетчика импульсов соединен со счетным входом третьего счетчика импульсов и вторым входом второго триггера, инверсный выход которого соединен с первым входом первого элемента И элемента 2И-ИЛИ, прямой выход соединен с вторым входом третьего элемента И и первым входом второго элемен- 25 та И элемента 2И-ИЛИ, прямой выход первого разряда третьего счетчика импульсов соединен с вторым входом первого элемента И элемента 2И-ИЛИ, инверсный выход первого разряда третьего счетчика импульсов соединен с вторыми входами первого элемента И, элементов И-НЕ и второго элемента И элемента 2И-ИЛИ, прямой выход второго разряда третьего счетчика импульсов соединен с третьим входом первого элемента И-НЕ, инверсный выход второго разряда третьего счетчика соединен с третьими входами второго элемента И-НЕ, первого и второго элементов И элемента 2И-ИЛИ и вторым входом элемента ИЛИ, выход которого соединен с входом записи регистра, выход элемента 2И-ИЛИ соединен с входом

20

30

35

ИЛИ, компенсационный интегрирующий 40 блока нормирования амплитуды, выход котоблок, два развязывающих элемента, выполненных в виде диодов, выход второго источника опорного напряжения соединен через первый развязывающий элемент с входом инвертора, выход которого соединен с информационным входом третьего ключа, первый выход генератора импульсов соединен с первыми входами элементов И-НЕ и первого элемента И, выход которого соединен с управляющим входом третьего ключа, выход которого соединен с входом компенсационного интегрирующего блока, выход которого соединен с третьим входом сумматора, выход которого соединен через выпря45

50

рого соединен через фильтр нижних частот с вторым входом операционного усилителя, выходы первого и второго элементов И-НЕ соединены с управляющими входами одноименных ключей.

5

митель с информационным входом интегратора, выход которого соединен с вторым входом компаратора, выход которого соединен с первыми входами второго элемента И, элемента ИЛИ и первого триггера, выход которого соединен с управляющим входом интегратора, выход первого источника опорного напряжения соединен с первым входом операционного усилителя, выход которого соединен через второй развязываю-, щий элемент с входом инвертора, второй выход генератора импульсов соединен со счетным входом второго счетчика импульсов, первым входом третьего элемента И, выход которого соединен со счетным входом первого счетчика импульсов, выход переполнения которого соединен с вторыми входами первого триггера и второго элемента И, выход которого соединен с первым входом второго триггера, выход второго счетчика импульсов соединен со счетным входом третьего счетчика импульсов и вторым входом второго триггера, инверсный выход которого соединен с первым входом первого элемента И элемента 2И-ИЛИ, прямой выход соединен с вторым входом третьего элемента И и первым входом второго элемен- 5 та И элемента 2И-ИЛИ, прямой выход первого разряда третьего счетчика импульсов соединен с вторым входом первого элемента И элемента 2И-ИЛИ, инверсный выход первого разряда третьего счетчика импульсов соединен с вторыми входами первого элемента И, элементов И-НЕ и второго элемента И элемента 2И-ИЛИ, прямой выход второго разряда третьего счетчика импульсов соединен с третьим входом первого элемента И-НЕ, инверсный выход второго разряда третьего счетчика соединен с третьими входами второго элемента И-НЕ, первого и второго элементов И элемента 2И-ИЛИ и вторым входом элемента ИЛИ, выход которого соединен с входом записи регистра, выход элемента 2И-ИЛИ соединен с входом

0

0

5

5

0

рого соединен через фильтр нижних частот с вторым входом операционного усилителя, выходы первого и второго элементов И-НЕ соединены с управляющими входами одноименных ключей.

О 5 6

г

д

е ж1

+V0

t

к л

#t

4

ж

К

Фиг. 2

| Авторское свидетельство СССР № 1157695, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Емкостный преобразователь перемещения в код | 1986 |

|

SU1398096A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-07—Публикация

1989-03-10—Подача