(21)46206-17/09

(22) 15 12 88

(46) 15 0691 Бюл №22

(71)Куйбышевский авиационный институт им акад С П Королева

(72)В И Иванченко, С. Б Мирошниченко, С В Мурзина и В А Абакумов

(53)621 375026(0888)

(56)Патент США № 3319175, кл. 330-22, 1967.

(54) ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ

(57)Изобретение относится к электронике. Цель изобретения - увеличение выходного напряжения Двухтактный усилитель мощ носги содержит два плеча на трантисторах нагрузку, источник питания с заземленной

средней точкой, ключи, компараторы, источники напряжения смещения, диоды В каждом плече усилителя напряжение не превышает заранее установленной величины ист (в случае равных ступеней источника питания). Поэтому величину выходного напряжения l/вых можно задавать выбором напряжения ист одной ступени питания и количеством п ступеней одинаковой полярности источника питания по ф-ле иВых--п11ст. В предельном случае напряжение DCT одной ступени источника питания можно выбрать близким к граничному напряжению транзисторов UCT -Ј Укаогр. Выигрыш по величине выходного напряжения достигается в п раз 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| Резонансный преобразователь постоянного напряжения с защитой по току | 1989 |

|

SU1709457A1 |

| Универсальный время-импульсный интегрирующий преобразователь напряжения с четырьмя функциями широтно-импульсной модуляции | 2023 |

|

RU2822374C1 |

| Усилитель мощности | 1987 |

|

SU1510068A1 |

| Устройство для защиты усилителя мощности | 1984 |

|

SU1179477A1 |

| Самовозбуждающийся транзисторный инвертор | 1987 |

|

SU1573510A1 |

| Усилитель мощности | 1987 |

|

SU1532994A1 |

| Устройство для управления двухтактным транзисторным преобразователем | 1988 |

|

SU1642563A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1337887A1 |

| Двухтактный усилитель мощности | 1985 |

|

SU1290479A1 |

Изобретение относится к электронике и предназначено для усиления электрических сигналов

Цель изобретения - увеличение выходного напряжения

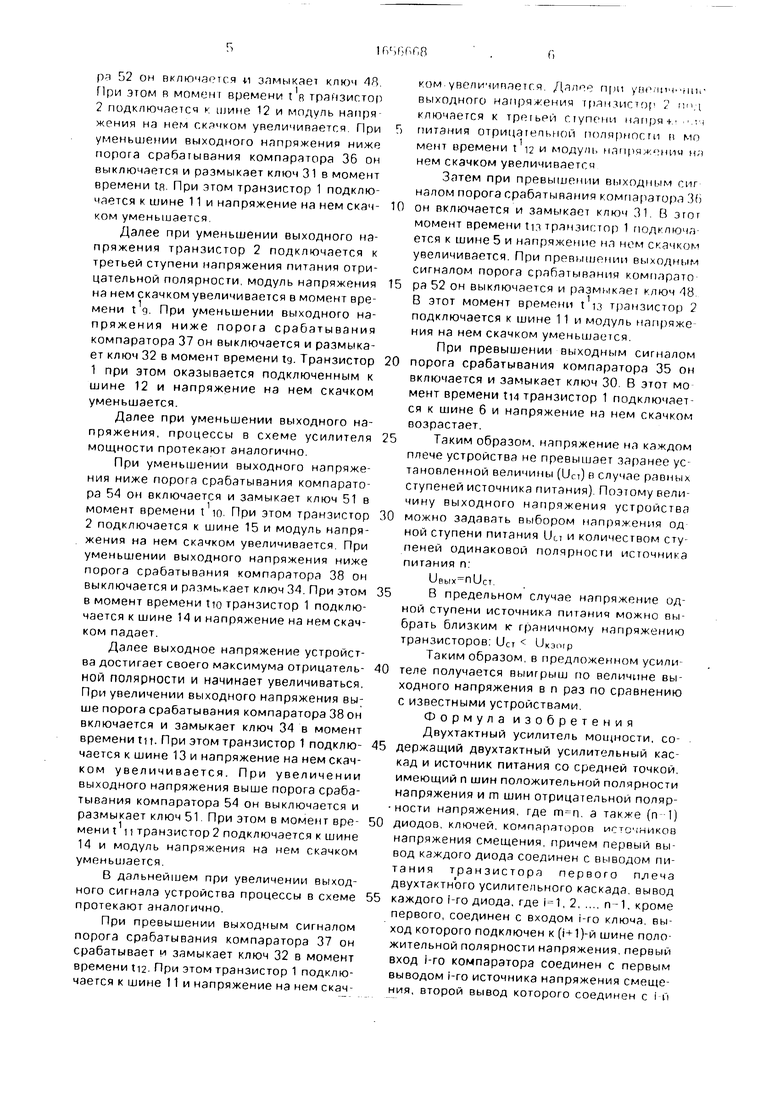

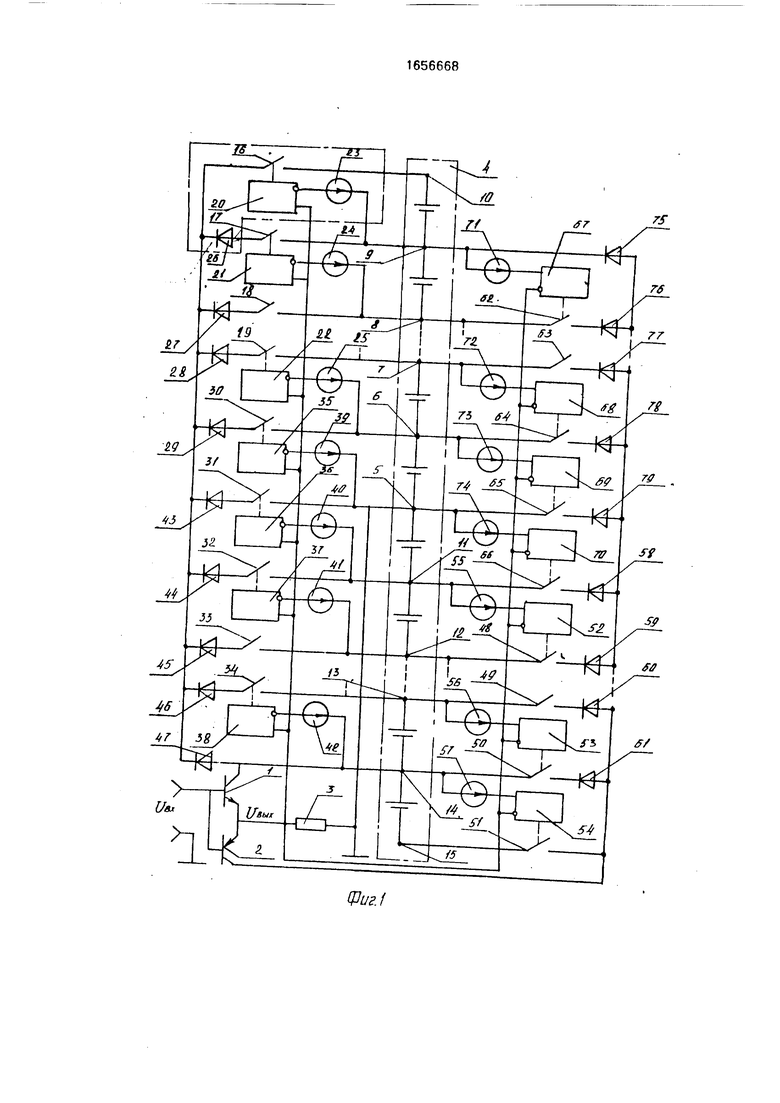

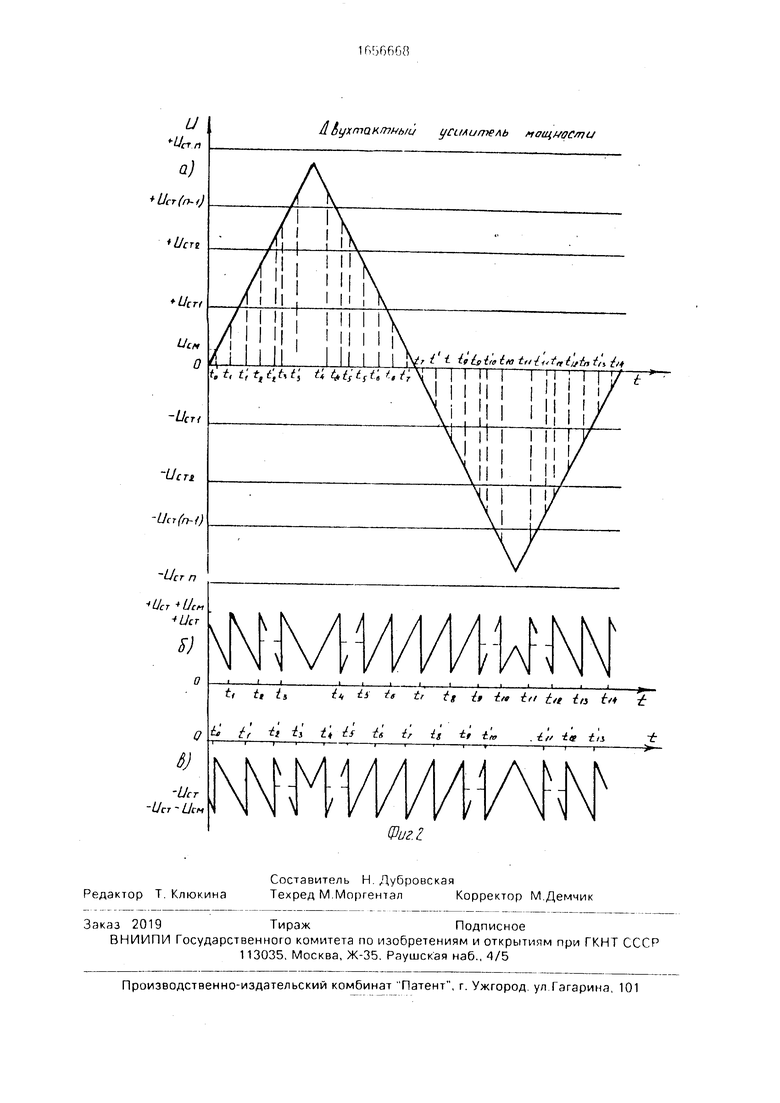

На фиг 1 представлена функциональная электрическая схема двухтактного усилителя мощности, на фиг. 2 - временные диаграммы его работы

Двухтактный усилитель мощности содержит транзисторы 1 и 2 (первого и второго плеча) двухтактного усилительного каскада, нагрузку 3, источник 4 питания с заземленной средней точкой-шиной 5, содержащей п шин 6-10 положительной полярности, m шин 11-15 отрицательной полярности, ключи 16 19. компараторы 20. 21 и 22, источники 23 24 и 25 напряжения смещения;диоды 26-29 первого плеча дополнительные клюСО

с

чи , дополнительные компараторы 35- 38, дополнительныеисточникиЗЭ 42 напряжения смещения, дополнительные диоды 43-47, ключи 48-51, компараторы 52, 53 и 54, источники 55, 56 и 57 напряжения смещения, диоды второго плеча, дополнительные ключи 62-66. дополнительные компараторы 67-70, дополнительные источники 71-74 напряжения смещения дополнительные диоды 75-79.

Двухтактный усилитель мощности работает следующим образом.

При отсутствии входного сигнала, выходной сигнал устройства Uewx также равен нулю Это напряжение более положительно, чем порог срабатывания компараторов 35- 38, поэтому эти компараторы срабатывают и ключи 30т34 оказываются замкнутыми. Транзистор 1 оказывается подключенным к

О СП

о о о

00

шине 6 источника 4 питания. Кроме того, нулевое выходное напряжение усилителя меньше порога срабатывания компараторов 70. 67, 68, 69 и они замыкают ключи 66, 62, 64, 65. Транзистор 2 оказывается под- ключенным к шине 11 источника 4 питания. Таким образом, напряжение на транзисторе 1 определяется разностью потенциалов шин 6 и 5 и равно Utri. Напряжение на транзисторе 2 равно разности потенциалов шин 11 и 5 и равно -1)Ст2. При подаче входного сигнала положительной полярности, транзистор 2 закрывается, транзистор 1 открывается и проводит ток в нагрузку. На нагрузке появляется напряжение положительной полярности (фиг. 2а), напряжение на транзисторе 1 (фиг. 26) убывает, на транзисторе 2 по модулю возрастает (фиг. 2в). Когда напряжение на нагрузке превысит по- рог срабатывания компаратора 70 (момент времени t 0, фиг. 2), он выключается и размыкает ключ 66. Транзистор 2 оказывается подключенным к шине 5 источника питания и модуль напряжения на нем скачком умень- шлется. При дальнейшем увеличении выходного напряжения в момент времени ti, когда напряжение Упых превысит порог срабатывания компаратора 22, он включается и замыкает ключ 19. Транзистор 1 оказывает- ся подключенным к шине 7 источника питания и напряжение на нем скачком возрастает.

При превышении выходным сигналом порога срабатывания компаратора 69 он выключается и размыкает ключ 65. Транзистор 2 оказывается подключенным к шине 6 источника питания в момент времени t 1 и модуль напряжения на нем скачком уменьшается

В дальнейшем при увеличении выходного сигнала на транзистор 1 подается напряжение третьей ступени источника питания положительной полярности и напряжение на нем скачком возрастает в мо- мент времени t. При превышении выходным напряжением порога срабатывания компаратора 68 он выключается и размыкает ключ 64. Транзистор 2 оказывается подключенным в момент времениt 2 к шине 7 и модуль напряжения на нем скачком уменьшается.

В дальнейшем при увеличении выходного напряжения процессы в схеме двухтактного усилителя мощности протекают аналогично.

При превышении порога срабатывания компаратора 20 (-иСт(п-1)иСм, фиг. 2а). он срабатывает и замыкает ключ 16. При этом в момент времени t3 транзистор 1 подклю

чается к шине 10 и напряжение на нем скачком увеличивается.

При превышении выходным напряжением порога срабатывания компаратора 67 он выключается и размыкает ключ 62. При этом в момент времени т,1з транзистор 2 оказывается подключенным к шине 9 источника питания и напряжение на нем скачком уменьшается.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 67 он выключается и замыкает ключ 62. Транзистор 2 оказывается подключенным к шине 8 в момент времени t 4 и модуль напряжения на нем скачком увеличивается.

В момент времени t4. при уменьшении выходного напряжения ниже порога срабатывания компаратора 20, он выключается и размыкает ключ 16. Транзистор 1 подключается к шине 9 и напряжение на нем скачком уменьшится. Далее, при уменьшении выходного напряжения процессы в схеме протекают аналогично. При уменьшении выходного напряжения ниже порога срабатывания компаратора 68 он включается в момент времени t 5 и замыкает ключ 64. Транзистор 2 подключается к шине 6 и модуль напряжения на нем скачком увеличится. В дальнейшем при уменьшении выходного напряжения транзистор 1 подключается к третьей ступени напряжения питания положительной полярности и напряжение на нем скачком уменьшается в момент времени ts.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 69 он включается и замыкает ключ 65 в момент времени tV При этом транзистор 2 подключается к шине 5 и модуль напряжения на нем скачком увеличивается. Затем приуменьшении выходного напряжения ниже порога срабатывания компаратора 22 он выключается и размыкает ключ 19 в момент времени te. При этом транзистор 1 подключается к шине 6 и напряжение на нем скачком уменьшается

При уменьшении выходного напряжения ниже порога срабатывания компаратора 70 он включается и замыкает ключ 66 в момент времени t у. В этот момент транзистор 2 подключается к шине 11 и модуль напряжения на нем скачком увеличивается.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 35 он выключается и размыкает ключ 30 в момент времени tr. При этом транзистор 1 подключается к шине 5 и напряжение на нем скачком уменьшается.

При уменьшении выходного напряже ния ниже порога срабатывания компаратоpa 52 он включается -и замыкает ключ 48. При этом в момент времени t в транзистор 2 подключается к шине 12 и модуль напряжения на нем скачком увеличивается. При уменьшении выходного напряжения ниже порога срабатывания компаратора 36 он выключается и размыкает ключ 31 в момент времени ta. При этом транзистор 1 подключается к шине 11 и напряжение на нем скачком уменьшается.

Далее при уменьшении выходного напряжения транзистор 2 подключается к третьей ступени напряжения питания отрицательной полярности, модуль напряжения на нем скачком увеличивается в момент времени t1g. При уменьшении выходного напряжения ниже порога срабатывания компаратора 37 он выключается и размыкает ключ 32 в момент времени tg. Транзистор

1при этом оказывается подключенным к шине 12 и напряжение на нем скачком уменьшается.

Далее при уменьшении выходного напряжения, процессы в схеме усилителя мощности протекают аналогично.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 54 он включается и замыкает ключ 51 в момент времени t ю. При этом транзистор

2подключается к шине 15 и модуль напряжения на нем скачком увеличивается. При уменьшении выходного напряжения ниже порога срабатывания компаратора 38 он выключается и размыкает ключ 34. При этом в момент времени tio транзистор 1 подключается к шине 14 и напряжение на немскач- ком падает.

Далее выходное напряжение устройства достигает своего максимума отрицательной полярности и начинает увеличиваться. При увеличении выходного напряжения выше порога срабатывания компаратора 38 он включается и замыкает ключ 34 в момент времени tit. При этом транзистор 1 подключается к шине 13 и напряжение на нем скачком увеличивается. При увеличении выходного напряжения выше порога срабатывания компаратора 54 он выключается и размыкает ключ 51. При этом в момент времени t 11 транзистор 2 подключается к шине 14 и модуль напряжения на нем скачком уменьшается.

В дальнейшем при увеличении выходного сигнала устройства процессы в схеме протекают аналогично.

При превышении выходным сигналом порога срабатывания компаратора 37 он срабатывает и замыкает ключ 32 в момент времени иг. При этом транзистор 1 подключается к шине 11 и напряжение на нем скачком увеличивается. Далпе при урнмпч гт. выходного напряжения транзистор п д ключаегся к третьей ступени напряг ч 5 питания отрицатепьной полярности и мо мент времени t 12 и модуль напряжении на нем скачком увеличивается

Затем при превышении выходным сиг налом порога срабатывания компаратора 36

10 он включается и замыкает ключ 31. В этот момент времени ti3 транзистор 1 подключается к шине 5 и напряжение на нем скачком увеличивается. При превышении выходным сигналом порога срабатывания компарато

15 ра 52 он выключается и размыкает ключ 48 В этот момент времени t 13 транзистор 2 подключается к шине 11 и модуль напряжения на нем скачком уменьшается.

При превышении выходным сигналом

0 порога срабатывания компаратора 35 он включается и замыкает ключ 30. В этот мо мент времени Ц4 транзистор 1 подключается к шине 6 и напряжение на нем скачком возрастает.

5Таким образом, напряжение на каждом

плече устройства не превышает заранее установленной величины (Ucr) в случае равных ступеней источника питания). Поэтому величину выходного напряжения устройства

0 можно задавать выбором напряжения од ной ступени питания Uu и количеством ступеней одинаковой полярности источника питания п:

UBblX nUcT.

5В предельном случае напряжение одной ступени источника питания можно выбрать близким к- граничному напряжению транзисторов: UCT UK3oip

Таким образом, в предложенном усили0 теле получается выигрыш по величине выходного напряжения в п раз по сравнению с известными устройствами.

Формула изобретения Двухтактный усилитель мощности, со5 держащий двухтактный усилительный каскад и источник питания со средней точкой, имеющий п шин положительной полярности напряжения и m шин отрицательной поляр- ности напряжения, где . а также (п-1)

0 диодов, ключей, компараторов источников напряжения смещения, причем первый вывод каждого диода соединен с выводом питания транзистора первого плеча двухтактного усилительного каскада, вывод

5 каждого 1-го диода, где , 2п-1, кроме

первого, соединен с входом i-ro ключа, выход которого подключен к (1+1)-й шине положительной полярности напряжения, первый вход 1-го компаратора соединен с первым выводом 1-го источника напряжения смещения, второй вывод которого соединен с I и

шиной положительной полярности напряжения, второй вход каждого компаратора соединен с выходом двухтактного усилительного каскада, и (гп-1) диодов, ключей, компараторов, источников напряжения смещения, причем первый вывод j-ro диода,

где j-1, 2т-1, кроме первого, соединен с

выходом j-ro ключа, выход которого подключен к 041)и шине отрицательной полярности напряжения, второй вывод каждого диода соединен с выводом питания транзистора второго плеча двухтактного усилительного каскада, первый вход каждого компаратора соединен с вторым выводом j-ro источника напряжения смещения, первый вывод которого соединен с j-й шиной отрицательной полярности напряжения, а выход каждого 1-го компаратора соединен с управляющим входом каждого 1-го ключа, выход каждого j-ro компаратора соединен с управляющим входом каждого J-ro ключа соответственно, отличающийся тем, что, с целью увеличения выходного напряжения, в него введено m дополнительных диодов, ключей, компараторов, источников напряжения смещения, причем первый вывод каждого дополнительного диода соединен с выводом питания транзистора первого плеча двухтактного усилительного каскада,второй вывод k-ro дополнительного диода, где

, 2m, кроме m-ro, соединен с входом

(k 1)-ro дополнительного ключа, выход которого соединен с (j-1)-u шиной отрицательной полярности напряжения, второй вывод т-го дополнительного диода соединен с(т- 1)-й шиной отрицательной полярности напряжения, вход первого дополнительного ключа соединен с вторым выводом первого диода, выход - с первой шиной положительной полярности напряжения, первый вход k-ro дополнительного компаратора соединен с первым выводом k-ro дополнительного источника напряжения смещения, второй вывод которого, кроме т-го дополнительного источника напряжения смещения, соединен с (J- 1)-й шиной отрицательной полярности напряжения, второй вывод m-ro дополнительного источника напряжения смещения соединен с (т -1)-й шиной отрицательной полярности напряжения, второй вход каждого дополнительного компаратора соединен с выходом двухтактного усили- тельного каскада, а выход k-ro дополнительного компаратора соединен с

управляющим входом k-ro дополнительного ключа соответственно, а также введено п дополнительных диодов, ключей, компара торов, источников напряжения смещения, причем первый вывод 1-го дополнительного

диода, где , 2п кроме n-го, соединен

с выходом (1+1)-го дополнительного ключа, вход которого соединен с (1-1)-й шиной отрицательной полярности напряжения, второй вывод каждого дополнительного диода соединен с выводом питания транзистора второго плеча двухтактного усилительного каскада, первый вывод n-го дополнительного диода соединен с (п-1)-й шиной положительной полярности напряжения, вход

первого дополнительного ключа соединен с первым выводом первого диода, выход с первой шиной отрицательной полярности напряжения, первый вход каждого дополнительного компаратора соединен с выходом

двухтактного усилительного каскада, второй вход 1-го дополнительного компаратора соединен с вторым выводом 1-го дополнительного источника напряжения смещения, первый вывод которого, кроме

n-го дополнительного источника напряжения смещения, соединен с (1-1)- й шиной положительной полярности напряжения, первый вывод n-го дополнительного источника напряжения смещения соединен с (п-1)-й шиной положительной полярности напряжения, а выход 1-го дополнительного компаратора соединен с управляющим входом 1-го дополнительного ключа соответственно.

/&,

rS

ц dyxmQKtriHb/u усилитель нощмос/пи

L/cn

и.

CTf

Г - i..,.i.-t.. ..i I1-i1111- r- . .

, м;.

r i.

-Ucri

-UcTi Ucr(n-()

Ucm

+ IJCM

5)

I II, I111111tt i, t,

it, If tr tg if e tti t,e in { -t

Q

& t t it з t if it ir it -b f -t .i tt is in

6)

Ucr

-Уст-Цен

VI

r- . .

r i. i- if is ire t«-Ln tat/jfa tn in

Л

l

Авторы

Даты

1991-06-15—Публикация

1988-12-15—Подача