Изобретение относится к электротехнике и может быть использовано для регулирования мощности подводимой нагрузки путем подключения ее на целочисленное число периодов напряжения к сети переменного тока.

Цель изобретения - расширение функциональных возможностей путем повышения помехоустойчивости, а также возможности управления аналоговым или цифровым управляющим сигналом.

На фиг. 1 представлена функциональная схема предлагаемого устройства цифрового управления мощностью; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг. 3 - схема детектора нуля; на фиг. 4 - схема формирователя последовательностей синхроимпульсов; на фиг. 5 - схема распределителя.

Обозначения Т, 8, 16, 24, 32, 40м, 48. 56, 64 на фиг. 1 и 4 указывают количество импульсов в последовательностях формирователя последовательностей синхроимпульсов.

Заявляемое устройство содержит детектор нуля 1, подключенный к трехфазной сети, один из выходов которого соединен с еходом формирователя 2 последовательностей синхроимпульсов, с входом генератора 3 ступенчатого напряжения и одним из входов элемента И 4. Выход генератора 3 подключен к одному из входов аналогового компаратора 5, выход компаратора 5 подсоединен к второму входу первого элемента И 4, а его выход к счетному входу третьего ш г;тиразрядного двоичного счетчика 6. Три млэдших разряда счетчика 6 подключены соответственно к трем младшим информа- ционныс входам первого двоичного счетчика 7. а три старших разряда третьего счетчика 6 подключены соответственно к трем младшим информационным входам второго двоичного счетчика 8. Счетный вход первого ДРОИЧНОГО счетчика 7 подключен к выход, В последовательности восьми импульсов j армирователя 2 последовательностей синхроимпульсов, а его три первых разряда - к соответствующим входам элемента И 9, выход которого через элемент задержки 10 соединен со счетным входом второго двоичного сметчика 8, четвертый информационней вход которого подключен к общей шине, о его три первых разряда - соответственно к дешифратору коммутатора 11, Информационные входы коммутатора 11 соединены с выходами формирователя 2 последовательностей синхроимпульсов, вход Разрешение с четвертым разрядом СЧЕТЧИКА 8 Btr-од коммутатора 11 подключен к входу распределителя импульсов управления 12. информационные входы которого соединены с выходами детектора нуля 1. Выходы распределителя импульсов управления 12 соединены с соответствующими входами трехфазного тиристорного ключа 13, подключенного последовательно с сетью к нагрузкам 14-16. Выход 1 формирователя 2 последовательности синхроимпульсов соединен с входами Сброс

генератора 3 ступенчатого напряжения, первого, второго и третьего двоичных счетчиков 7, 8 и 6, а также с входами Запись первого счетчика 7 и второго счетчика 8. Причем совокупность элементов 3-6 составляет аналого-цифровой преобразователь 17. а 2, 7, 8, 9, 10 и 11 - управляемый делитель частоты 18.

Детектор нуля, формирователь последовательностей синхроимпульсов и распределитель управляющих импульсов могут быть выполнены по схемам фиг. 3-5.

Детектор нуля содержит три одинаковых схемы формирования синхроимпульсов L, М, N. Каждая схема формирования имеет

диодную оптопару 19, светодиод которой через диод 20 и резистор 21 подключается к фазе А (В, С) и нулю сети, а также резисторы 22-24, операционный усилитель 25, инвертор 26, фазовращатель 27, элемент И 28,

причем фотодиод оптопары 19 подсоединен своим анодом к общему выводу источника питания, а катодом через сопротивление 22 к положительному выходу источника питания и на неинвертирующий вход операционного усилителя 25, второй вход которого подключен к общей точке делителя (резисторы 23, 24), соединенного с источником питания. Выход операционного усилителя 25 подсоединен к входам инвертора 26 и элемента И 28, выход инвертора 2.6 через фазовращатель 27 подключен к второму входу элемента И 28. Выход элемента И 28 является одним из выходов детектора нуля и подключается согласно схеме фиг. 1.

Формирователь последовательностей синхроимпульсов (фиг. 4) содержит шестиразрядный двоичный счетчик 29, одиннадцать инверторов 30-40 и восемь элементов И 41-48. причем вход счетчика 29 является

входом формирователя последовательностей синхроимпульсов и подключается согласно схеме фиг. 1. Все шесть разрядов счетчика 29 черээ инверторы 30-35 подсоединены к одному из входов соответственно

элементов И 41-43 и к трем входам элемента И 44, второй вход элемента И 41 объединен с одним из входов элементов И 45-47 и подсоединен через инвертор 36 к входу счетчика 29, выход этого элемента И 41 - к

одному из входов элементов И 42 и 48 через

инвертор 37. Выход элемента И 42 подключен к второму входу элемента И 46 и через инверто р 38 - к второму входу элемента И 43, выход которого соединен с вторыми входами элементов И 47 и 48 и через инвертор 39 к четвертому входу элемента И 44. Выход элемента И 48 подключен через инвертор 40 к второму входу элемента И 45. Выходы элементов И 41-48, а также вход инвертора 36 являются выходами формирователя последовательностей синхроимпульсов и подключены соласно схеме фиг. 1.

Генератор 3 ступенчатого напряжения выполнен по известной схеме шестиразрядного двоичного счетчика, входящего в состав формирователя 2 последовательностей синхроимпульсов, и резистивной матрицы типа R-2R.

Элемент задержки 10 включает в себя RC-фазовращатель и инвертор.

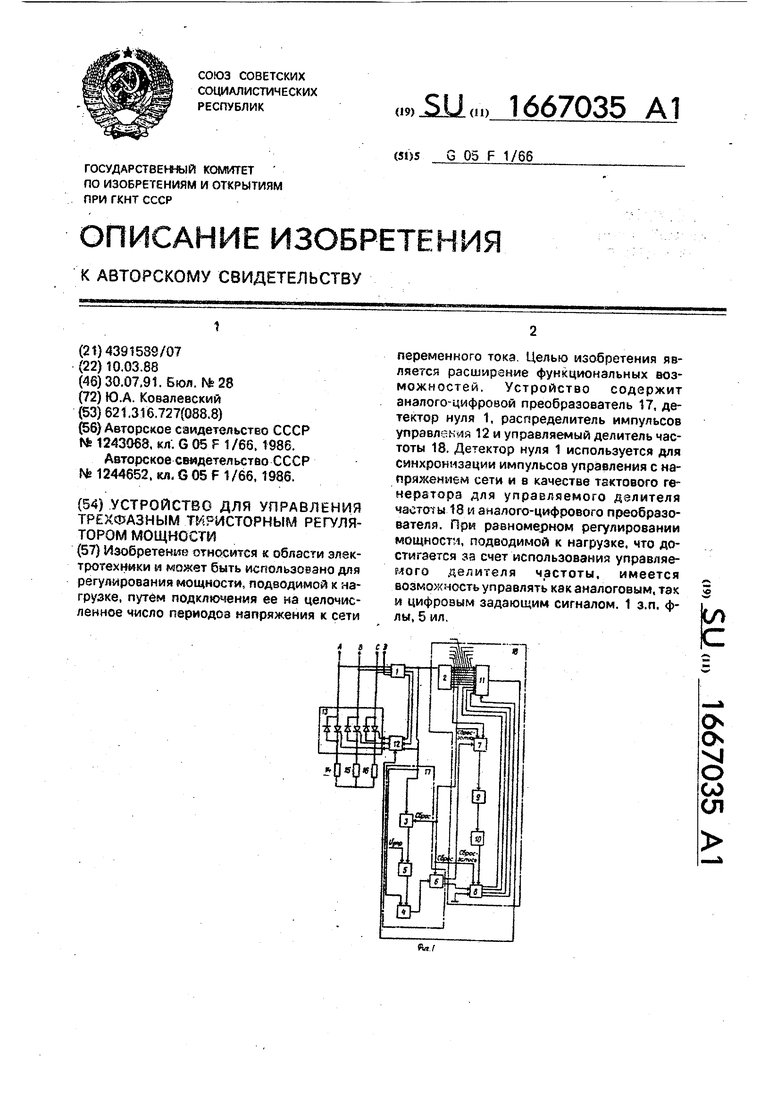

Распределитель содержит интегральный таймер 49. времязадающую цепочку R 50 и С 51 и три двувходовые элемента И 52-54. Вход Запуск таймера 49 является тактовым входом, первые из входов элементов И 52-54 - информационными входами, а выходы этих элементов И - выходами распределителя и подключаются согласно схеме фиг. 1. Входы таймера Пороговый вход и Разряд объединены и подключены к общей точке резистора R 50 и конденсатора С 51, через которые эта точка подсоединена соответственно к положительному и к общему выводам источника питания, выход таймера подключен к вторым входам элементов И 52-54.

Устройство работает следующим образом.

При появлении напряжения на шинах А, В, С сети детектор нуля 1 вырабатывает синхронизирующие импульсы при переходе через нуль напряжений фаз сети (фиг. 3). Гальваническая развязка с сетью осуществлена с помощью диодных оптопар 19. Операционные усилители 25, включенные в режиме компараторов, позволяют получить синхронизирующий импульс, максимально приближенный к точке перехода напряжения через нуль. Импульсы от фазы А поступают на входы формирователя 2 последовательностей синхроимпульсов, генератора 3 ступенчатого напряжения и один из входов первого элемента И 4. Формирователь 2 последовательностей синхроимпульсов, выполненный по схеме фиг. 4. вырабатывает восемь последовательностей синхроимпульсов, распределенных по интервалу регулирования, и сам интервал регулирования (фиг. 2а, б, в, г, д, е, ж, з). Каждый шестьдесят четвертый импульс является замыкающим периода регулирования. Последовательности имеют следующие значения: первая - восемь импульсов, вторая - шестнадцать импульсов, третья двадцать четыре, четвертая - тридцать два, пятая - сорок, шестая - сорок восемь, седьмая - пятьдесят шесть и восьмая - шестьдесят четыре импульса.

Генератор ступенчатого напряжения 3

0 вырабатывает напряжение ступенчатой формы синхронно с поступающими на вход импульсами. Нарастание напряжения происходит от нуля в начале периода регулирования до напряжения питания в конце

5 периода. Сигнал от генератора 3 ступенчатого напряжения подается на один из входов аналогового компаратора 5, на второй вход которого подается аналоговый сигнал управления. В момент равенства этих сиг0 налов аналоговый компаратор 5 опрокидывается и запирает элемент И 4, препятствуя прохождению тактовых импульсов на шестиразрядный третий двоичный счетчик 6. Таким образом, в каждый

5 период регулирования на двоичный счетчик 6 будет подано количество импульсов, пропорциональное управляющему сигналу, которые установят его в соответствующее состояние. Информация с трех младших

0 разрядов этого счетчика 6 передается на три младших соответствующих информационных входа первого двоичного счетчика 7, а информация с трех старших разрядов счетчика 6 - на три младших соответствующих

5 информационных входа второго двоичного счетчика 8, и в момент наступления следующего периода регулирования записывается в регистры счетчиков 7 и 8. Каждый восьмой импульс, поступающий на счетный вход

0 счетчика 7 с выхода последовательности восьми импульсов формирователя 2 последовательностей синхроимпульсов, вычитает записанное в его регистры число и в момент обнуления, когда все разряды счетчика 7

5 имеют нулевое значение, элемент И 9 выдает импульс на счетный вход третьего двоичного счетчика 8 через элемент задержки 10. Элемент задержки 10 введен для того, чтобы из работы не выпадали каждые вось0 мые импульсы (фиг. 2). В начале каждого периода регулирования информация с трех младших разрядов счетчика 8 передается на дешифратор коммутатора 11 и на вход распределителя 12 начинает поступать

5 последовательность импульс с формирователя 2 последовательностей синхроимпульсов через один из соответствующих каналов. В момент прихода импульса на счетный вход счетчика 8, который работает в режиме вычитания, код на дешифраторе

уменьшается на единицу, коммутатор 11 переключается на соседний канал и на вход распределителя импульсов управления 12 с этого момента начинает поступать последовательность импульсов, которая меньше первоначальной на восемь, Например, (фиг. 2) в момент времени Т сигнал управления стал равен сигналу, выработанному генератором 3 ступенчатого напряжения, компаратор 5 опрокинулся и закрыл элемент И 4. На счетный вход счетчика 6 поступило восемнадцать тактовых импульсов. Двоичный счетчик 6 установился в состояние 010010. Три младших разряда 010 (фиг. 2 к, л, м) и три старших разряда 010 (фиг. 2н, о, п) по приходу шестьдесят четвертого импульса переписываются соответственно в двоичные счетчики 7 и 8. На дешифраторе коммутатора 11, который подключен к трем младшим разрядам счетчика 8, в начале периода регулирования устанавливается код 010 и открытым становится канал, пропускающий последовательность двадцати четырех импульсов. На счетчике 7 в начале периода регулирования установлен код 010. Так как на счетный вход этого счетчика подходят восьмой, шестнадцатый, двадцать четвертый и т.д. тактовые импульсы (фиг. 2 р), то шестнадцатый импульс обнуляет счетчик 7 и через элемент задержки 10 на половину периода сети (фиг. 2 с) перейдет на счетный вход счетчика 8. В этот момент времени из счетчика 8 вычитается единица, код на дешифраторе коммутатора 11 устанавливается 001, и открывается канал, пропускающий последовательность из шестнадцати импульсов. В итоге на распределитель 12 приходят восемнадцать импульсов управления (фиг. 2 т).

Распределитель 12 работает следующим образом (фиг. 5). По приходу тактового импульса, совпадающего по времени с приходом синхронизирующего импульса от фазы А, таймер 49 включается на время, которое определяется постоянной времени RC. Значения R и С подбираются таким образом, чтобы выключение таймера 49 происходило в середине промежутка времени между приходами синхронизирующих импульсов фаз С и А. Таким образом, распределитель 12 пропускает на вход ключа 13 восемьнадцать импульсов управления по каждой фазе А, В и С.

Таким образом, устройство осуществляет управление трехфазным тиристорным регулятором с равномерным потреблением мощности из сети на цикле регулирования, а использование в составе устройства аналого-цифрового преобразователя позволяет управляющее воздействие вводить в

аналоговом-и цифровом видах. Причем приведенное выполнение управляемого делителя частоты позволяет повысить помехоустойчивость устройства за счет дискретного исполнения на помехоустойчивых микросхемах.

Формула изобретения

1.Устройство для управления трехфазным тиристорным регулятором мощности,

0 содержащее синхронизатор, входы которого предназначены для подключения к питающей сети, и распределитель импульсов, управляющие входы которого соединены с выходами синхронизатора, а выходы пред5 назначены для связи с управляющими электродами тиристоров регулятора мощности, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены аналого-цифровой пре0 образователь и управляемый делитель частоты, тактовые входы которых соединены с одним из выходов синхронизатора, управляющие входы управляемого делителя частоты соединены с выходами аналого5 цифрового преобразователя, аналоговый вход которого предназначен для подключения к задатчику управляющего сигнала, а выход управляемого делителя частоты соединены с модулирующим входом распреде0 лителя импульсов.

2.Устройство по п. 1,отличающее- с я тем, что управляемый делитель частоты содержит формирователь последовательностей синхроимпульсов, коммутатор с дешиф5 ратором, первый и второй четырехразрядные двоичные счетчики с предустановкой, элемент задержки, логический элемент И, причем формирователь последовательностей синхроимпульсов снабжен девятью выхода0 ми, обозначенными как 1, 8, 16, 24, 32, 40. 48, 56. 64,, обозначения которых соответствуют числу синхроимпульсов на цикле регулирования, выходы, кроме 1, соединены с информационными входами

5 коммутатора с дешифратором, управляющие входы которого соединены с тремя младшими разрядами второго двоичного счетчика старший информационный вход которого соединен с общей шиной, а выход

0 коммутатора с дешифратором использован как выход управляемого делителя частоты, младшие разряды аналого-цифрового преобразователя соединены с младшими информационными входами первого

5 двоичного счетчика, выходы младших трех разрядов первого двоичного счетчика через элемент И и элемент задержки соединены со счетным входом второго двоичного счет- . чика, счетный вход первого двоичного счетчика соединен с выходом 8 формирователя

последовательностей синхроимпульсов, а выход 1 соединен с установочными входами первого и второго двоичных счетчиков и установочным входом аналого-цифрового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1985 |

|

SU1272327A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| Устройство для пуска асинхронного электродвигателя | 1984 |

|

SU1274099A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1985 |

|

SU1348806A2 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение относится к области электротехники и может быть использовано для регулирования мощности, подводимой к нагрузке, путем подключения ее на целочисленное число периодов напряжения к сети переменного тока. Целью изобретения является расширение функциональных возможностей. Устройство содержит аналого-цифровой преобразователь 17, детектор нуля 1, распределитель импульсов управления 12 и управляемый делитель частоты 18. Детектор нуля 1 используется для синхронизации импульсов управления с напряжением сети и в качестве тактового генератора для управляемого делителя частоты 18 и аналого-цифрового преобразователя. При равномерном регулировании мощности, подводимой к нагрузке, что достигается за счет использования управляемого делителя частоты, имеется возможность управлять как аналоговым, так и цифровым задающим сигналом. 1 з.п. ф-лы, 5 ил.

Фиг2

Ј-И

Фиг.з

PH2.f

50

запуск

пороговый вход

разряд

W

52

53

Фиг. 5

| Совмещенная электромашинная обмотка | 1984 |

|

SU1243063A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1984 |

|

SU1244652A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-07-30—Публикация

1988-03-10—Подача