ной памяти и к первому входу третьего триггера, выход второго элемента И подключен к четвертому входу первого сумматора и к первому входу вто рого триггера, выход третьего элемен та И подключен к первому входу первого, триггера и к входу первого дели теля частоты, выход четвертого элемента И подключен к входам управления записью первого и второго блоков оперативной памяти, к вторым входампервого и второго триггеров и через первый элемент задержки к третьему входу первого интегратора, к четвертому входу второго интегратооа и к входу блока управления, выход первого интегратора соединен с входом дан ных первого блока оперативной памяти, выход которого .подключен к чет.вертрму входу первого интегратора, выход второго интегратора соединен с входом данных второго блока оперативной памяти , выход которого подключен к пятому входу второго ратора, восьмой выход блока управления соединен с адресными входами преобразователя кодов, первого к вто рого блоков оперативной памяти и пре образователя фаза-код, второй выход ограничителя тока соединен с кодовым входом преобразователя кодов, а выход первого делителя частоты соединен с вторым входом третьего триггеря и с входом записи преобразователя кодов, выходы синхронизатора подключены к соответству1эщим входам синхронизации преобразователя кодов, группы выходов КОТОРОГО.соединены с

08703

входами соответствующих силовых коммутаторов.

2. Электропривод по п.1, о т л ичающийся тем, что преобразот ватель кодов содержит дешифратор, группу регистров и гоуппу формирователей сигналов, каждый из которых содержит программный счетчик, четвертый триггер, группу мультиплексоров и группу коммутаторов, синхровход дешифратора является входом записи преобразователя кодоя, информационный вход является адресным входом преобразователя, а выходы подключены к входам записи соответствующих регистров группы, информационные входы которых являются кодовым входом преобразователя, входы .синхронизации которого соответственно подключены к первому входу четвертого триггера и установочному входу программного счетчика каждого из формирователей сигналов группы, в котором второй вход четвертого триггера соединен с выходом переполнения программного счетчика, счетный вход которого является тактовым входом преобразователя кодов, а выход соединен с информационными входами мультиплексоров группы, выходы которых соединены с первыми входами коммутаторов группы, вторые входы которых подключены к выходу четвертого триггера, а третьи входы - к выходам соответствующих регистров группы, коммутаторов группы являются выходами соответствующей группы преобразователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для контроля качества ферромагнитных изделий | 1987 |

|

SU1499212A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1989 |

|

SU1712957A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1983 |

|

SU1141439A2 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

. 1

Изобретение относится к автоматике и может быть использовано при автоматическом регулировании многокоординатного объекта управления.

Известен следящий электропривод, содержащий интерполятор, два цифроаналоговых преобразователя, преобразователи кода скорости и кода положения, блок выбора входной информации, коммутатор и в каждом канале последовательно соединенные привод, аналоговое запоминающее устройство, сумматор и блок соавнения l .

Недостатком известного устройства является низкая точность.

Наиболее близким к изобретению по технической сущности является цифровой следящий привод, содержащий генератор импульсов, последовательно соединенные блок силовых коммутирующих элементов (блок силовых тиристоров ), двигатель, датчик и преобразователь

фаза-коп, синхронизатор, котопрго подключен к выходу блока силовых коммутирующих элементов, а также блок управления и последовательно соединенные первый сумматор, первый интег- 5 ратор,,второй сумматор, второй ратор, ограничитель тока и третий сумматор, причем первый выход блока управления подключен к первому входу первого сумматора и второму входу второ- to го сумматора, а второй выход соединен с вторым входом первого сумматора, тр тий вход которого объединен с выходом преобразователя фаза-код и с третьим входом второго сумматора, к четвертому входу которого подключен четвертый выхпд блока управления , третий KOTODoro соединен с вторым входами первого и второго интеграто13ов, пятый выход блока управления подключен к третьему вхопу второго интегратора. а шестой и седьмой выходы - соответственно к вторым входам третьего сумматора и ограничителя тока, третий вход которого соединен с выходом третьёго сумматора, вГорой вход которого соединен с выходом второго сумматора и первым входом второго интегратора 2 Недостатком этого цифрового следящего электропривода является ограниченная область применения вследствие регулирования только однркоординатного объекта управления. Цель изобретения - расширение области применения электропривода путем обеспечения регулирования многокоординатного объекта управления. Поставленная цель достигается тем, что в цифровой следящий электропривод содержащий генератор импульсов, последовательно соединенные группы силовых коммутаторов , электродвигателей и датчиков, выходы которых подключены к соответствующим входам преобразователя фаза-код, синхронизатор , о первый вход которого подключен к второму выходу одного из силовь1х коммутаторов, блок управления и последовательно соединённые первый сумматор , первый интегратор, второй сумматор, второй интегратор, ограничитель тока и третий сумматор, первый выход блока управления подключен к первому входу первого сумматора и второму входу второго сумматора, второй выход соединен с вторым входом первого сумматора, третий вход которого соединен с первым выходом преобразователя фаза-код и с третьеим входом второго

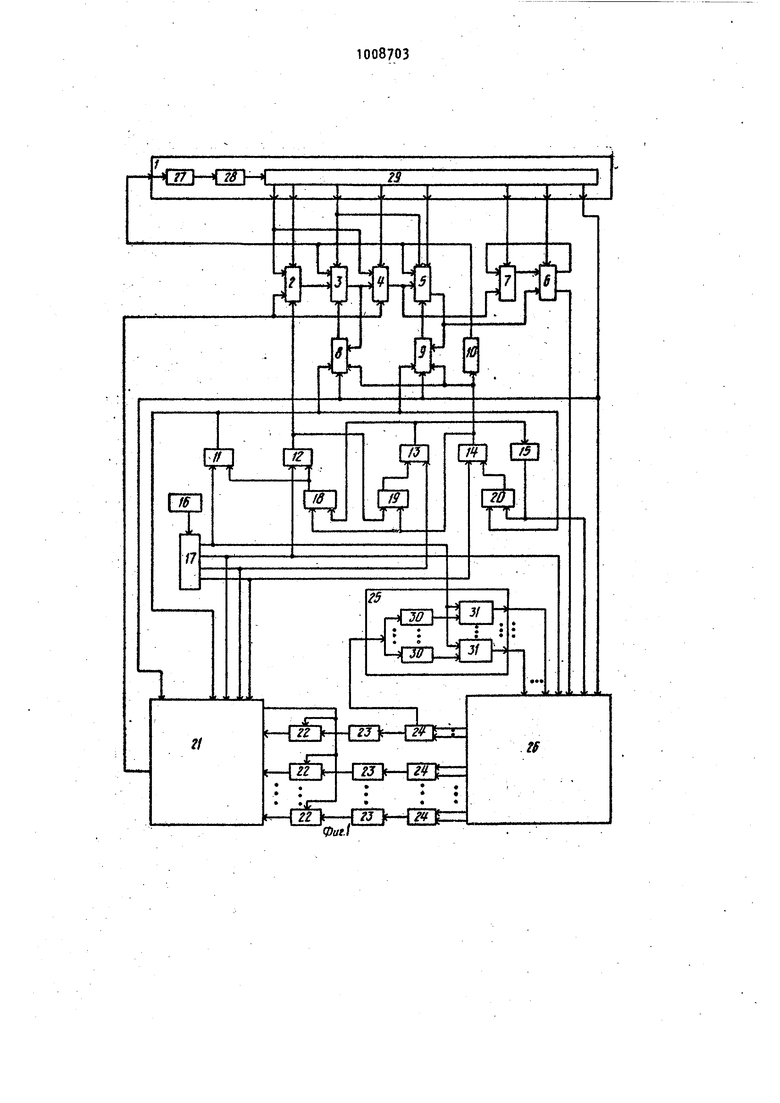

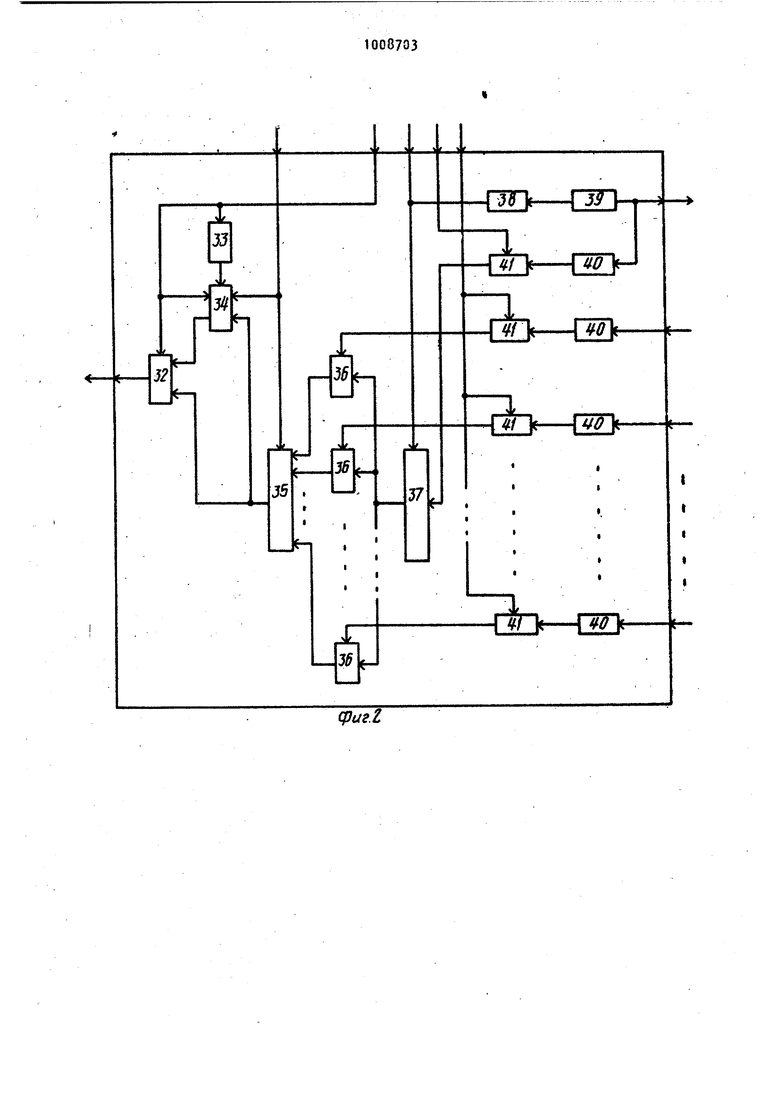

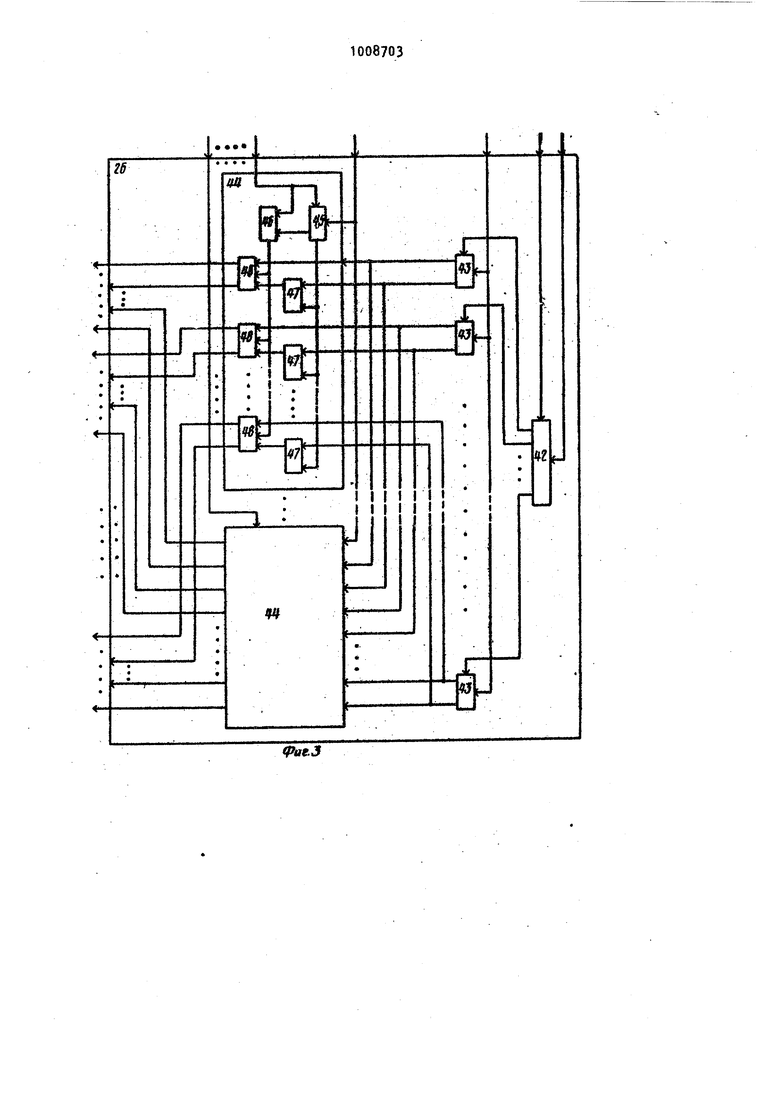

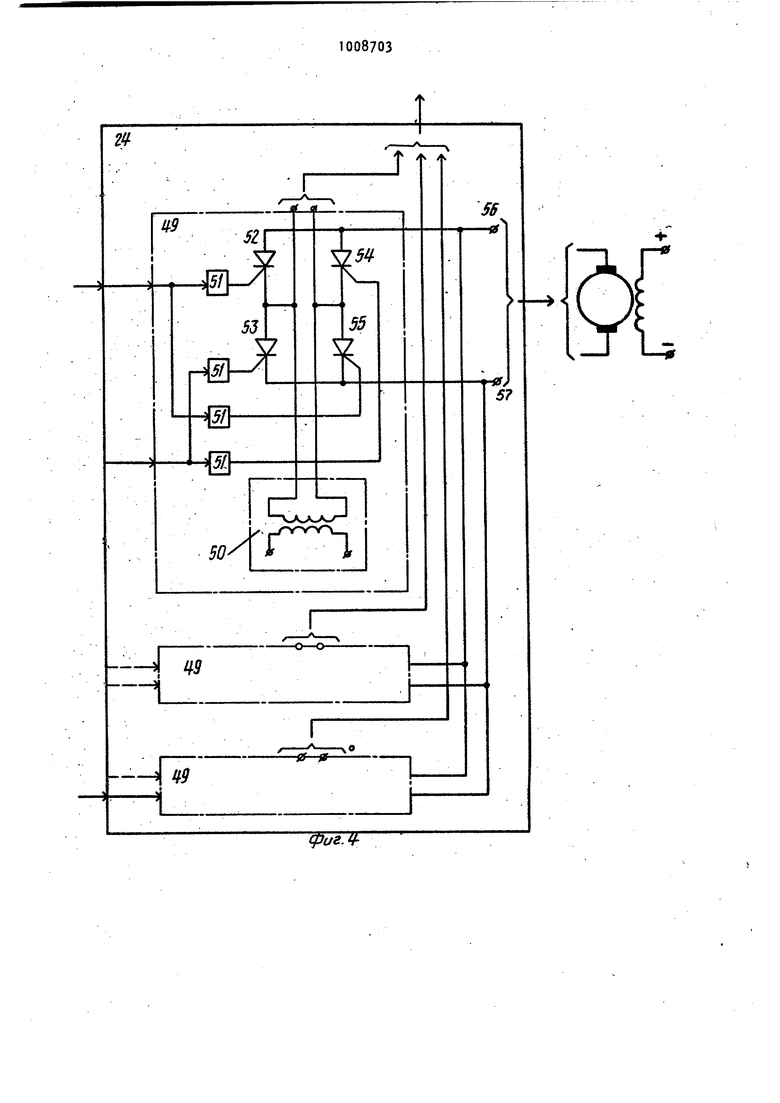

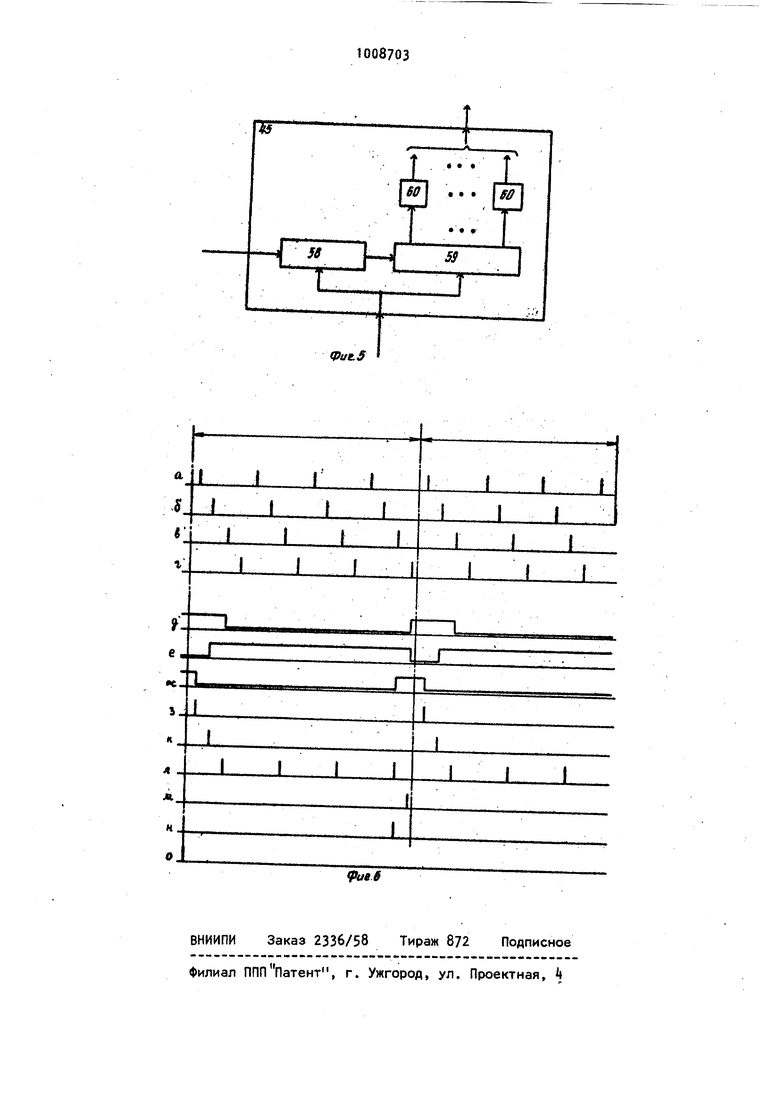

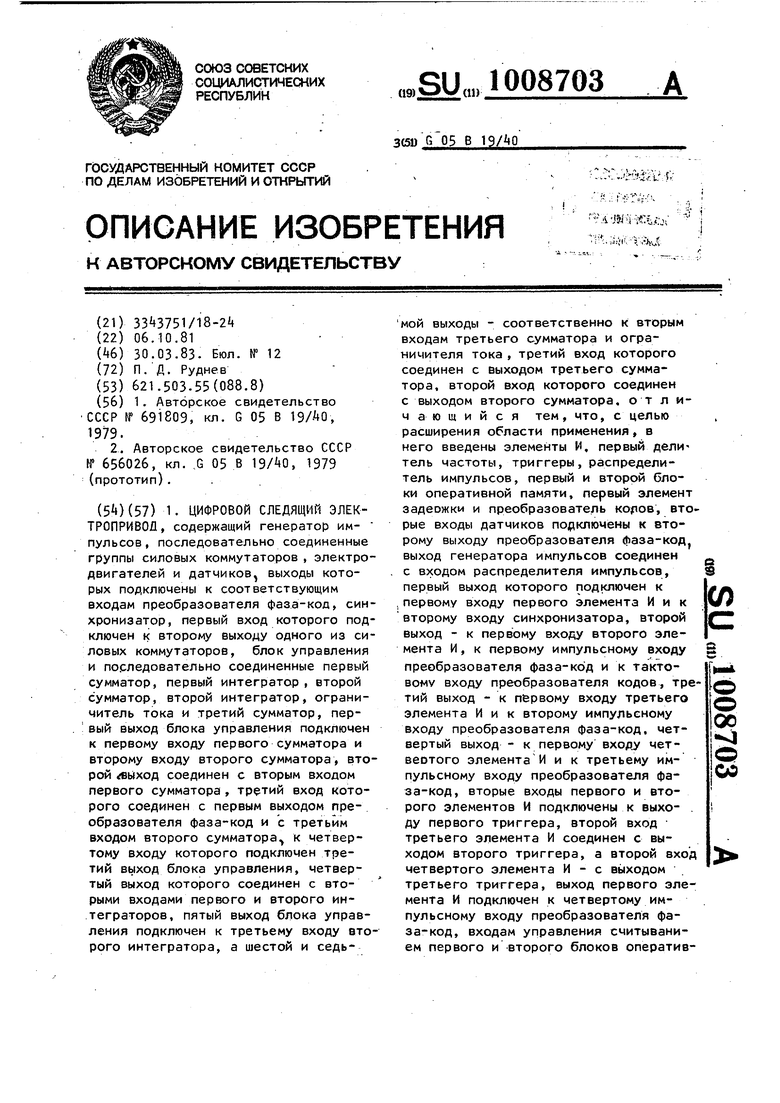

су мматора, к четвертому входу которого подключен третий выход блока управления, четвертый выход которого соединен с вторыми входами первого и второго интеграторов, пятый выход блока управления подключен к третьему входу второго интегратора, а шестой и седьмой выходы - соответственно к вторым входам третьего сумматора и ограничителя тока, третий вход котоого соединен с выходом третьего суматора, второй вход которого соединен выходом второго сумматора, введены лементы И, первый делитель частоты, риггеры, распределитель импульсов, ервый и второй блоки оперативной паяти, первый элемент задержки и пребразователь кодов, вторые входы датиков подключены к второму выходу преобразователя фаза-код, выход генератора импульсов соединен с входом распределителя импульсов, счервый выход которого подключен к первому входу первого элемента И, и к второму входу синхронизатора , второй выход - к первому входу второго элемента И, к первому импульсному входу преобразователя фаза-код и к тактовому входу пре-. образователя кодов, третий выход - к первому входу третьего элемента И и к второму импульсному входу преобразователя фаза-код, четвертый выход к первому входу четвертого элемента И и к третьему импульсному входу преобразователя фаза-код, вторые входы первого и второго элементов И Подключены к ВЫХОДУ первого триггера, второй вход третьего элемента И соединен с выходом второго триггера, а второй вход четвертого элемента И с выходом третьего триггера , выход первого элемента И подключен к четвертому импульсному входу преобразователя фаза-код, к входам управления считыванием первого и второго блоков оперативной памяти и к первому входу третьего триггера, выход второго элемента И подключен к четвертому входу первого сумматора и к первому входу второго триггера, выход третьего элемента И подключен к первому входу первого триггера и к входу первого делителя частоты, выход 4etBepToro элемента И подключен к входам vnpae ления записью первого и второго бло-. ков оперативной памяти, к вторым входам первого и второго триггеров-и через первый элемент задержки к третьему входу первого интегратора, к четвертому входу второго интегратора и к входу блока управления, выход первого интегратора соединен с входом данных первого блока оперативной памяти, выход которого подключен к четвертому входу первого интегратора, выход второго интегратора соединен с входом данных второго блока оперативной паг мяти, выход которого подключен к пятому входу второго интегратора, восьмой выход блока управления соединен с адресными входами преобразователя кодов, первого и,второго блоков рперативной памяти и преобразователя фаза-код, второй выход ограничителя тока соединен с кодовым входом преобразов-ателя кодов, а выход первого делителя частоты соединен с вторым входом третьего триггера и с входом записи преобразователя кодов, выходы синхронизатора подключены к соответствующим входам синхронизации преобразователя кодов, группы выходов которого соединены с входами соответствующих силовых коммутаторов. Кроме того, преобразователь кодов содержит дешифратор , группу регистров и группу формирователей сигналов, каждый из которых содержит программный счетчик, четвертый триггер, группу мультиплексоров и группу коммутаторов, синхровход дешифратора является входом записи преобразователя кодов, информационный вхрд является адресным входом преобразователя, а выходы подключены к входам записи соответ- . ствующих регистров группы, информационные входы которых являются кодовым входом преобразователя, входы синхронизации которого соответственно подключены к первому .входу четвертого триггера и установочному входу программного счетчика каждого из формирователей сигналов группы, в котором второй вход четвертого триггера соединен с выходом переполнения npoi- раммного счетчика, счетный вход которого является тактовым входом преобра зователя кодов, а выход соединен с информационными входами мультиплексоров группы, выхолы J oтopыx соединены с первыми входами коммутаторов группы , вторые входы которых подключены к выходу четвертого триггера, а третьи входы - к выходам соответствующих регистров группы, выходы коммутаторов группы являются выходами соответствующей группы преобразовател кодов, На фиг. 1 приведена блок-схема цифрового следящего электропривода; на фиг,2 - блок-схема преобразователя фаза-код; на фиг.3 - блок-схема преоброзователя кодов; на фиг.- блок-схема силового коммутатора; на фиг.5 блок-схема программного счетчика, на фиг.6 - временные диаграммы работы устройства. Электропривод содержит блок 1 управления, первый сумматор, 2, первый интегратор 3, второй сумматор t, второй интегратор 5, ограничитель 6 тока, третий сумматор 7, первый 8 и второй 9 блоки оперативной памяти, первый элемент 10 задержки, первый Т1, второй 12, третий 13 и четвертый l4 элементы И, первый делитель 15 частоты, генератор 16 импульсов, распределитель 17-импульсов, первый 18,второй 19 и третий 20 триггеры, преобразователь 21 фаза-код, датчики22, электродвигатели 23, силовые коммутаторы 2, синхронизатор-/25, преобразователь26 кодов, счетчик 27 команд, блок 28 памяти команд, шифратор 29 команд, первые нуль-компараторы 30, первые элементы 31 синхронизации. Преобразователь 21 (фиг.2) содержим четвертый сумматор 32, второй элемент 33 задержки, третий блок 3 оперативной памяти, коммутатор 35, регистры 3& счетчик 37, второй делитель 38 частоты, фильтр 39, .вторые нуль-компараторы 0, вторые элементы -Ifl синХ Ьониззции, Преобразователь. 26(фиг. 3) содержит дешифратор 2, группу регистров АЗ , группу формирователей j сигналов, каждый иа которых содержит программный счетчик 5 , четвертый триггер 46, группу мультиплексоров 47 и группу коммутаторов . Коммутаторы 2k содержат фиг. выключатели 9 трансформатор 50, усилители-формирователи 51, тиристоры 52-55, клеммы 56 и 57Счетчик 5 содержит(фиг.5) третий делитель 58 частоты, двоичный счетчик 39 и формирователи 60 длительности импульсов. На фиг. 6 последовательности тактовых импульсов с первого, второго, третьего и четвертого выходов распределителя 17 импульсов обозначены а,5,ВЛ, сигналы с выходов первого 18, второго 19 и третьего 20 тригт геров -Э,е,ж, сигналы с выходов перврго.11, второго 12, третьего 13 и четвертого 14 элементов и -3, к,л,м, импульс переполнения с выхода делителя 15 частоты -н , сигнал на выходе элемента 10 -задержки -о. Устройство работает следующим образом. . Распределитель 1 формирует последовательности импульсов высокой частоты, вырабатываемой генератором 16 (четыре последовательности тактовых импульсов, фиг,6 О1,Б, 8,г) сдвинутые по фазе относительно друг друга на ЗГ/2, с равными частотами. Последовательность и с первого выхода распределителя 17 поступает на первый вход первого элемента И 11 и через второй вход синхронизатора 25 на вторые входы первых элементов 31 синхронизации. Последовательность б с второго выхода распределителя 17 по.ступает на пер-i вый вход второго элемента И 12, на второй импульсный вход преобразователя 21 фаза-код и на импульсный вход преобразователя 2б кодов. Последова.тельность в с третьего выхода распределителя 17 поступает на первый вход третьего элемента И 13 и на третий импульсный вход преобразователя 21 фаза-код. Последовательность ъ с четвертого выхода распределителя 17 поступает на первый вход четвертого эле мента И 1 и на четвертый импульсный вход преобразователя 21 фаза-код. Синхронизирующие фазные переменные напряжения Цф (t) частоты fgnc второ го выхода из силовых коммутаторов 2 поступает через первый вход синхронизатора 25 на входы соответст.eyioiuVix первых нуль-компараторов 30, каждый из которых в момент перехода через нуль напряжения синхронизации формирует один раз за период импульс, поступающий на первые (синхронизируемые входы соответсТвующйх первых элементов 31 синхронизации, на вторы (синхронизирующий) входы которых с ВТОрого входа синхронизатора 25 поступают импульсы последоавтельности а. На выхо дах каждого первого элемента 31 синхрони.зации формируются импульсы с частотой .следования, равной частоте питающего электродвигатель переменного н,апЪяжения (синхронизиоованное Иоследова1ельностью а). Сформированные с помощью первых элементов 31 синхронизации импульсы поступают через соответствующие синхронизирующие входы преобразователя 26 кодов и синхронизирующий вход со103 тветствующего формирователя « .сигалов на первый вход четвертого триггера 46, устанавливая на его выходе огический ноль, и на вход установки в ноль программного счетчика 45, устанавливая его триггеры в ноль. Импульсы последовательности б, пройдя через второй импульсный вход преобразователя 21 фаза-код посту-пают на вход второго делителя 38 частоты и счетный вход счетчика 37. На выходе второго делителя 38 частоты образуется последовательность импульсов со скважностью 2 и частотой следования fe, подаваемая на фильтр 39 3 выходе фильтра 39 формируется гармоническое напряжение частоты поступающее на 1д, поступающее на вход одного из вторых нуль-компараторов 4О и через второй выход (выход напряжения питания датчиков) преобразователя 21 фаза-код,-на вторые входы (обмотки возбуждения) всех датчиков 22. При этом на выходе указанного нуль-конпаратора 40 формируются импульсы, поступающие на синхронизируемый вход соответствующего второго элемента 41 синхронизации, на синхронизирующий вход которого с третьего импульсного входа преобразователя 21 фаза-код г поступают импульсы последовательности в. На выходе элемента 41 синхронизации образуются импульсы, называемые опорными импульсами , с частогой следования f, синхронизированные с последовательностью и сдвинутые по фазе относительно импульсов на выходе второго делителя 38 частоты, так как фильтр 39 вносит дополнительный фазовыйсдвиг при формировании гармонического напряжения. Опорные импульсы с выхода втброго элемента 41 синхронизации периодически, с частотой f устана ивают в ноль двоичный счетчик 37, за полняемый.со стороны счетного входа импульсами последовательности 5. На выходе счетчика 37 формируется периодический линейно нарастающий код, достигающий максимального значения к кюменту и поступающий на входы всех регистров 36.На выходе каждого из датчиков 22 формируется гармониче.ское напряжение сдвинутое по фазечотносительно напряжения, поступающего на обмотку возбуждения, на угол, .пропорциональ ный углу поворота вала ротора датчика 22, кинематически связанного с осью вращения объекта управления. Напряжения с выходов- датчиков 22, пройдя через соответствующие входы преобразователя 21 фаза-код, поступают на входы соответствующих вторы нуль-компараторов 0, Импульсы с вы ходов вторых нуль-компараторов 40 подаются на синхронизируемые входы соответствующих вторых элементов 1 синхронизации , на синхронизирующие входы которых поступают через четвертый импульсный вход преобразователя 21 фаза-код импульсы последовательности X. На выходе каждого .из указанных вторых элементов 1 синхронизации образуются импульсы с частотой следования f, сдвинутые по фазе относительно опорных импульсов на угол , пропорциональный углу поворота соответствующего датчика 22. Импульсы с выходов соответствующих вторых элементов 1 син хронизации поступая на входы разрешения записи соответствующих регистров 36, периодически переписывают в регистры Зб код с выхода;сме чика 37. Код, переписанный в регист 36,пропорционален сдвигу фазы напряжения на выходе соответствующего датчика 22, а следовательно и углу поворота его ротора. Кроме того, импульсы последовательности б, пройдя через тактовый вход преобразователя 26 кода и тактовые входы всех формирователей сигналов, поступают в каждом формирователе kk сигналов на счетный вхо програмного f счетчика 15. который формирует N - ортогональных импульс ных последовательностей и импульс переполнения, где N - разрядность числа кода управления. N ортогональных импульсных последовательностей в программном счет чике 45 вырабатываются следующим образом. Третий делитель 58 частоты запол няется импульсами последовательности б, и на его выходе образуется после довательность счётных импульсов, еле с частотой f () дующая Последовательность счетных им.пуль сов частоты f. заполняет, двоичны счетчик 59, выходы N первых разрядов которого подключены к входам соответствующих формирователей 60 длительности импульсов. В момент изменения состояния каждого из первых 0310 разрядов двоичного счетчика 59 с О в 1 на выходе соответствующего формирователя 60 длительности импульсов появляется импульс, дпительность которого равна .„„(.)-Гс. Последовательности импульсов с выходов формирователей 60 длитёльности импульсов образуют ортогональную систему функций на отоезке длины 12 N , Прив;нзка ортогональной системы, вырабатываемой в каждом из формирователей k сигналов, к m-й фазе опорного напряжения, питающего электродвигатель, осуществляется с помощью синхронизирующего импульса, поступающего на первый вход четвертого триггера 46 и на вход установки в .ноль программного счетчика 45 через соответствующий вход преобразователя 2б кодов. При поступлении синхронизирующего импульса устанавливаются в ноль третий делитель 58 частоты и двоичный счетчик 59 Импульс переполнения появляется на выходе программного счетчика 45 после поступления 2 четных импульсов на вход двоичного счетчика 59, т.е. через время 2- Сс после прихода синхронизирующего импульса на вход установки в ноль. Импульс переполнения переключает четвертый тои1- гер 46 на выходе которого формируется сигнал фазыФ (t), принимающий значения при Уф (t)7/0 Ч- (t) j , 1 при ,(t). О Ортогональные импульсные последовательности поступают на первые входы всех мультиплексоров 47 формирователей 44 сигналов. На второй вход каждого мультиплексора 47 поступает прямой N-разрядный код числа кода управления А с соответствующего регистра 43 таким образом, что младший разряд кода числа Ац управляет подключением на выход мультиплексора 47 последовательности импульсов , формируемой в программном счетчике 45 формирователем 60 длительности импульсов, связанным с выходом N-ro разряда двоичного счетчика 59. С выхода каждого из мультиплексоров 47 на импульсный вход соответствующег.о коммутатора 48 поступает цифровая квэзичастотная последовательность/ З-ь- (t) , число импульсов котоtnрой за период фазы UA опорного напряжения, питающего электродвигатель 2 , определяется величиной кода управления Ац Коммутатор А8, выполняемый на ком бинационных логических элементах формирует сигналы , (i,,,4t,.z™ К„ (. Ct).Z,(:), где Z(t))5ic5nA +V(t).s4n.AK где signАц -знак кода управления, поступающий с (N+l)-ro разряда К-го регистра 3 на вход знака К-го коммутатора 8 .каждого формирователя kl сигналов. Сигналы Kxjj. и К2гц.,с выходов каждого коммутатора lo через соответствующие выходы формирователя k сигналов и преобразователя кодов подключены к входам сигналов управления силовых коммутаторов 24 и осуществляют управление коммутацией тока от соответствующей фазы ф якорно цепи электродвигателя.Сигналы К и .тк пройдя через -входы сигналов управления силовых коммутаторов 24 , поступают на входы выключателей 49. В выключателе 49 сигналы . 2 усиливаются с помощью усилителейформирователей 51, каждый из которы обеспечивает управление соответству щим силовым коммутиру1эщим элементом одним из запираемых тиристоров 5255. При открывании одного из тиристоров 52-55 якорная цепь электродви гателя подключается к вторичнойобмотке трансфторматора 50 на время действия управляющего сигнала .I 1 rV Вычисление кода управления по ка

кооодинат выполняется циклически (величина цикла повторения определяется параметрами и требуемыми показателями качества цифрового следящего электропривода), пс1следо- вательность обработки координат задается программно блоком 1 управления.

Перед началом вычислений кода управления по каждой.;-из К координат на п-ом шаге устройство находится в следующем исходном состоянии.

Первый делитель 15 частоты обнулен. На вторые входы первого 11 и

выводится код с выхода соответствующего регистра 36.

Вычисление кода управления А| на п-м шаге по К-й координате выполняется следующим образом.

Импульс последовательности 0 с первого выхода распределителя 17, пройдя через первый элемент И 11 (фиг.6з) поступает на первый импульсный вход преобразователя 21- фаза-код, на входы разрешения считывания первого 8, второго 9 и третьего 34 блоков оперативной памяти. Коды из первторого 12 элементов И с выхода первого триггера 18 поступает потенциал Лиг.бо), открывающий первый .11 и вто рой 12 элементы И. На вторые входы треть,его 13 и четвертого Т элементов И постуг1ают потенциалы соответственной с выходов второго 19 (фиг.бе) и третьего 20 (фиг. 6) триггеров, закоывающие тоетий 13 и четвертый 1 элементы И . С выходов шифратора 29 команд через выходы блока 1 управления выводятся по-зиционные коды, которые на первом выходе блока 1 управления представляют собой код скорости X на BTOpQM - константу Кх|,определяющую добротность следящего привода, на третьем - коэффициент пропорциональности К2,., зависящий от частоты замыкания контура Следящего электропривода, на четвертом - константу Кз-,, определяющую меру компенсации скоростной ошибки, на пятом - константу КА.,, определяющую . коэффициент усиления интегрального ка;нала регулятора в скоростном контуре привода, на шестом - константу Kg- , определяющую коэффициент усиления про.порционального канала регулятора скоростного привода, на седьмом - константу , определяющую максимальную величину сигнала управления подаваемого на электродвигатель, на восьмом - код адреса (.номера) обрабатываемой координаты. Константы с первого по седьмой выходов блока 1 управления вводятся в сумматоры 2, i и 7 и интеграторы 3 и 5, подготавливая их к выполнению на данном шаге вычислений-, необходимых для замыкания контура цифрового следящего электропривода по данной координате. С восьмого выхода блока 1 управления подается код адреса на блоки 8,9 и 34 оперативной памяти, дешифратор 42 и коммутатор 35 через который на . первый вход четвертого сумматора 32 вого 8 и второго 9 блоков оперативной памяти в качестве начальных условий при интегрировании на данном шаге выводятся соответственно на четвертый вход первого интегратора 3 и на пятый вход второго интегратора 5. По импульсу, поступающему свыхода первого элемента И 11 изменяет свое состояние третий три|- гер 20 , закрывая четвертый элемент И k. По импульсу,поступающему на первый импульсный вход преобразователя 21 фаза-код, из третьего блока 34 оперативной памяти по адресу, вводимому из блока 1 управления, считывается код,, пропорциональный величине угла поворота вала соответствующего датчика 22 на предыдущем шаге вычислений. Код поступает на второй вход четвертого сумматора 32. В четвертом сумматоре 32 вычисляется приращение пути ).Сп Хд {Ь ХдГп-13 за один цикл вычислений по данной координате, где - код пропорциональный величине угла поворрта соответствующего датчика и.-.выводимый через коммутатор 35 с выхода соответствующего регистра 36 на первый вход четвертого сумматора 32 и третьего блока 3 оперативной памяти. Код приращения через выход кода приращения преобразовате ля 21 фаза-код подается на третьи .входы первого 2 и втооого сумматиров. Кроме того, импульс,, поступающий на первый импульсный вход преобразователя 21 фаза-код, проходит через второй элемент 33 за(держГ --.,.. ки и по окончании вычисления величиЦы переписывает значение S ячейку третьего блока 3 оперативнои памяти, в которой ранее находилась величина Х n-l. Импульс последовательности. 5 с еторрго выхода распределителя 17 пройдя через второй элемент И 12 Чфиг.бк), поступает на первый вход второго триггера 19 и на четвертый вход первого сумматора 2. При этом второи триггер 19 переключается, открывая третий элемент И 13. А по импульсу, приходящему на четвертый вход сумматора 2 начинаются вычисления формульных зависимостей, определяющих качество цифрового следящего электропривода. При этом первый сумматор 2 вычисляет величину М-М кМ-ХоокИ () 1 03 На выходе первого интегратора 3 появляется величина 2 и п, (2) к п-1 -.выходная величина первого интегратора 3 в предыдущем цикле вычислений , хранения в первом блоке 8 оперативной памяти и выводимая на вход первого интегратора 3 Меред началом данного цикла вычислений. Второй сумматор k вычисляет величину.). Второй интегратор 5 на данном шаге формирует величину . (4,.U,tn)JC , (4) где Ц. п-1) - выходная величина второго интегратора 5 в предыдущем цикле вычислений по данной координате, хранимая во втором блоке 9 оперативной памяти и выводимая на вход второго интегратора 5 перед началом данного цикла вычислений, В ограничителе 6 тока величина МфцС сравнивается с константой .nictx К наименьшая по модулю величина , имеюшая знак величины Ib п J и обозначаемая , поступает на вход третьего сумматора 7 с первого выхода ограничителя 6 тока. На выходе третьего сумматора 7 образуется сигнал VK 4 3 V3K Значение Uynp.fc сравнивается в ограничителе 6 тока с константой Up ..наименьшая по модулю вели Р представляющая собой код управления А по К-й координате со знаком Uvinp.K выводится с выхода кода управления ограничителя 6 тока на вход кода управления преобразователя 26 кодов. При изменении величин коэффицициентов К, Кз, каждой из коо эдинат может быть осуществлено регулирование динамических характеристик электропривода. Привод является следящим с компенсацией скоростной ошибки, если Кз|.0 и без компенсации .. .1 М гч скоростной ошибки, если Кз1,0. Привод переводится в регулируемый режим если , и KSJ 0. Регулятор скоростного контура является пропорциональным, если и Ку 0 , интегральным, если и Кс-..0, интег15,1 рально-прогпорциональным, если K4..fO, Кроме того , изменение динаминеских характеристик электропривода, а также выбор приемлемого времени за грузки вычислительного комплекса, мо гут быть осуществлены с помощью изме нения частоты генератора 16. Импульс последовательности с тр тьего выхода распределителя 17, прой дя через третий элемент И 13 (.фиг.6л поступает на первый вход первого три гера 18 и на .счетный вход первого де лителя 15 частоты. При этом первый триггер 18 переключается , закрывая первый 11 и второй 12 элементы И. Последующие импульсы, проходящие через открытый третий элемент И 13 и поступающие на первый вход первого триггера 18 и на счетный вход первого делителя 15 частоты, заполняют первый делитель 15 частоты до тех пор, пока с его выходЪ не появится импульс переполнения (состояние первого триггера 18 не изменится, он продолжает закрывать первый 11 и вто рой 12 элементы И). Импульс переполнения .фиг.б h } с выхода первого делителя. 15 частоты появляется через время t 1цуцпосле поступления на четвертый вход первого сумматора 2 импульса с выхода первого элемента И 11, где t-,. - время, необходимое для реализации формульных зависимостей ( ) - (5). Импульс переполнения переключает третий триггер 20, при этом открывается четвертый элемент И, и пройдя через вход разрешения записи кода преобразователя 26 кодов на вход синхроимпульса дешифратора 42, поступает на вход разрешения записи соответствующего регистра 3 (.по адресу, вводимому в пр образователь 2б кодов с восьмого выхода блока 1 управления), разрешая перепись кода управления с выхода кода управления ограничителя 6 тока в данный регистр A3. Импульс последовательности в с четвертого выхода распределителя 17 0316 пройдя через открытый четбертый элемент И 1 (фиг.вм поступает на входы разрешения записи кода первого 8 и второго 9 блоков оперативной памяти, на вход первого элемента 10 задержки, на вторые входы первого 18 и второго. 19 триггеров. При этом с выходов первого 3 и второго 5 интеграторов соответственно в-первый 8 и второй 9 блоки оперативной памяти переписываются коды по адресу, выводимому с,восьмого выхода блока 1 уп равления, первый триггер 18 переключается, открывая первый 11 и второй 12 элементы И, второй триггер 19 переключается, закрывая третий элемент И 13. Кроме того, пройдя через первый элемент 10 задержки (фиг.бо), импульс с выхода четвертого элемента И 14 сбрасывает в О первый 3 и второй 5 интеграторы и через вход блока 1 управления поступает на счетный вход счетчика 27 команд, изменяя его состояние (при этом код с выхода счетчика 27 команд, поступающий на вход блока 28 памяти команд, увеличивается на один бит), соответственно изменяются кодь; на выходе блока 28 памяти команд, на выходах шифратора 29 команд, т.е. на первом - восьмом выходах блока 1 управления. Таким образом, цифровой следящий привод подготовлен к следующему циклу вычислений кода управления. Изобретение имеет более широкую область применения, так как позволяет осуществить регулирование многокоординатного объекта управления с максимальным использованием общих для всех координат вычислительных средств. Сокращение объема электронного оборудования в предлагаемом электроприводе - по сравнению с объемом электронного оборудования, необходимого при использовании устройства - прототипа, составляет при трехкоординатном объекте 32%, при четырехкоордииатном k2%, при восьмикоординатном 58%.

uz:tF

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для управления следящими приводами | 1977 |

|

SU691809A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой следящий электропривод | 1977 |

|

SU656026A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| . | |||

Авторы

Даты

1983-03-30—Публикация

1981-10-06—Подача