Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, контроля, а также при синтезе цифровых схем.

Целью изобретения является упрощение устройства.

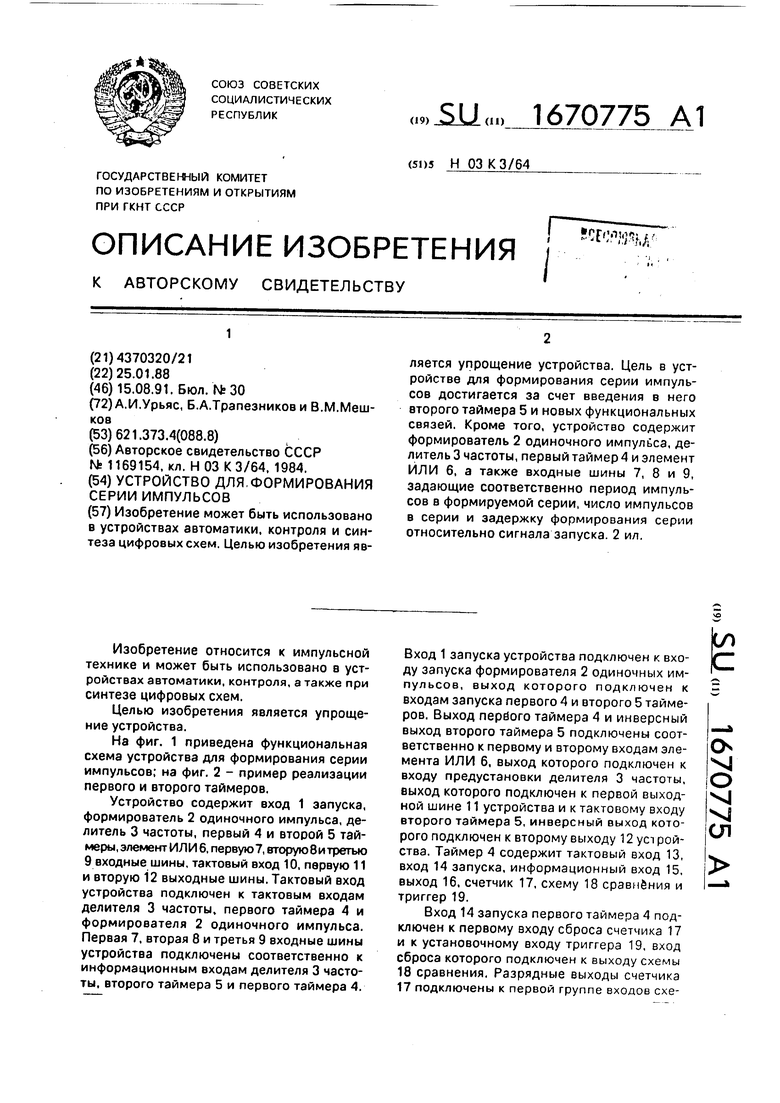

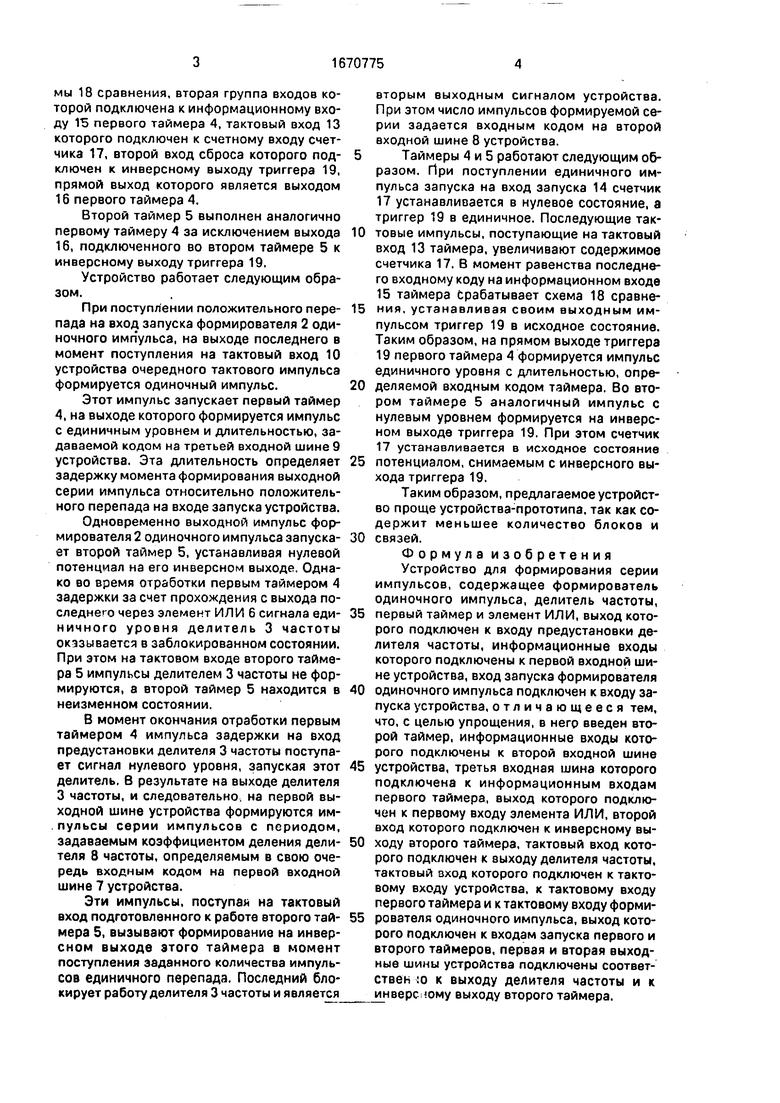

На фиг. 1 приведена функциональная схема устройства для формирования серии импульсов; на фиг. 2 - пример реализации первого и второго таймеров.

Устройство содержит вход 1 запуска, формирователь 2 одиночного импульса, делитель 3 частоты, первый 4 и второй 5 таймеры, элемент ИЛИ 6, первую 7, вторую 8 и третью 9 входные шины, тактовый вход 10, первую 11 и вторую 12 выходные шины. Тактовый вход устройства подключен к тактовым входам делителя 3 частоты, первого таймера 4 и формирователя 2 одиночного импульса. Первая 7, вторая 8 и третья 9 входные шины устройства подключены соответственно к информационным входам делителя 3 частоты, второго таймера 5 и первого таймера 4.

Вход 1 запуска устройства подключен к входу запуска формирователя 2 одиночных импульсов, выход которого подключен к входам запуска первого 4 и второго 5 таймеров. Выход перёого таймера 4 и инверсный выход второго таймера 5 подключены соответственно к первому и второму входам элемента ИЛИ 6, выход которого подключен к входу предустановки делителя 3 частоты, выход которого подключен к первой выходной шине 11 устройства и к тактовому входу второго таймера 5, инверсный выход которого подключен к второму выходу 12 уст рой- ства. Таймер 4 содержит тактовый вход 13, вход 14 запуска, информационный вход 15, выход 16. счетчик 17, схему 18 сравнения и триггер 19.

Вход 14 запуска первого таймера 4 подключен к первому входу сброса счетчика 17 и к установочному входу триггера 19, вход сброса которого подключен к выходу схемы 18 сравнения. Разрядные выходы счетчика 17 подключены к первой группе входов схеЁ

О

XI

о

XJ

VI

СЛ

мы 18 сравнения, вторая группа входов которой подключена к информационному входу 15 первого таймера 4, тактовый вход 13 которого подключен к счетному входу счетчика 17, второй вход сброса которого подключен к инверсному выходу триггера 19, прямой выход которого является выходом 16 первого таймера 4.

Второй таймер 5 выполнен аналогично первому таймеру 4 за исключением выхода 16, подключенного во втором таймере 5 к инверсному выходу триггера 19.

Устройство работает следующим образом.

При поступлении положительного перепада на вход запуска формирователя 2 одиночного импульса, на выходе последнего в момент поступления на тактовый вход 10 устройства очередного тактового импульса формируется одиночный импульс.

Этот импульс запускает первый таймер 4, на выходе которого формируется импульс с единичным уровнем и длительностью, задаваемой кодом на третьей входной шине 9 устройства. Эта длительность определяет задержку момента формирования выходной серии импульса относительно положительного перепада на входе запуска устройства. Одновременно выходной импульс формирователя 2 одиночного импульса запускает второй таймер 5, устанавливая нулевой потенциал на его инверсном выходе. Однако во время отработки первым таймером 4 задержки за счет прохождения с выхода последнего через элемент ИЛИ 6 сигнала еди- ничного уровня делитель 3 частоты оказывается в заблокированном состоянии. При этом на тактовом входе второго таймера 5 импульсы делителем 3 частоты не формируются, а второй таймер 5 находится в неизменном состоянии.

В момент окончания отработки первым таймером 4 импульса задержки на вход предустановки делителя 3 частоты поступает сигнал нулевого уровня, запуская этот делитель. В результате на выходе делителя 3 частоты, и следовательно, на первой выходной шине устройства формируются импульсы серии импульсов с периодом, задаваемым коэффициентом деления делителя 8 частоты, определяемым в свою очередь входным кодом на первой входной шине 7 устройства.

Эти импульсы, поступая на тактовый вход подготовленного к работе второго таймера 5, вызывают формирование на инверсном выходе этого таймера в момент поступления заданного количества импульсов единичного перепада. Последний блокирует работу делителя 3 частоты и является

вторым выходным сигналом устройства. При этом число импульсов формируемой серии задается входным кодом на второй входной шине 8 устройства.

Таймеры 4 и 5 работают следующим образом. При поступлении единичного импульса запуска на вход запуска 14 счетчик 17 устанавливается в нулевое состояние, а триггер 19 в единичное. Последующие тактовые импульсы, поступающие на тактовый вход 13 таймера, увеличивают содержимое счетчика 17. В момент равенства последнего входному коду на информационном входе 15 таймера срабатывает схема 18 сравнения, устанавливая своим выходным импульсом триггер 19 в исходное состояние. Таким образом, на прямом выходе триггера 19 первого таймера 4 формируется импульс единичного уровня с длительностью, определяемой входным кодом таймера. Во втором таймере 5 аналогичный импульс с нулевым уровнем формируется на инверсном выходе триггера 19. При этом счетчик 17 устанавливается в исходное состояние

потенциалом, снимаемым с инверсного выхода триггера 19.

Таким образом, предлагаемое устройство проще устройства-прототипа, так как содержит меньшее количество блоков и

связей.

Формула изобретения Устройство для формирования серии импульсов, содержащее формирователь одиночного импульса, делитель частоты,

первый таймер и элемент ИЛИ, выход которого подключен к входу предустановки делителя частоты, информационные входы которого подключены к первой входной шине устройства, вход запуска формирователя

одиночного импульса подключен к входу запуска устройства, отличающееся тем, что, с целью упрощения, в него введен второй таймер, информационные входы которого подключены к второй входной шине

устройства, третья входная шина которого подключена к информационным входам первого таймера, выход которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к инверсному вы0 ходу второго таймера, тактовый вход которого подключен к выходу делителя частоты, тактовый вход которого подключен к тактовому входу устройства, к тактовому входу первого таймера и к тактовому входу форми5 рователя одиночного импульса, выход которого подключен к входам запуска первого и второго таймеров, первая и вторая выходные шины устройства подключены соответствен :о к выходу делителя частоты и к

инверс юму выходу второго таймера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Устройство для измерения периода | 1988 |

|

SU1531068A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| Устройство для формирования временных интервалов | 1988 |

|

SU1584090A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2003 |

|

RU2248089C1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

Изобретение может быть использовано в устройствах автоматики, контроля и синтеза цифровых схем. Целью изобретения является упрощение устройства. Цель в устройстве для формирования серии импульсов достигается за счет введения в него второго таймера 5 и новых функциональных связей. Кроме того, устройство содержит формирователь 2 одиночного импульса, делитель 3 частоты, первый таймер 4 и элемент ИЛИ 6, а также входные шины 7, 8 и 9, задающие соответственно период импульсов в формируемой серии, число импульсов в серии и задержку формирования серии относительно сигнала запуска. 2 ил.

| Устройство для формирования серий импульсов | 1984 |

|

SU1169154A1 |

| Нефтяной конвертер | 1922 |

|

SU64A1 |

Авторы

Даты

1991-08-15—Публикация

1988-01-25—Подача