Изобретение относится к вычислительной технике и автоматике и может быть использовано в устройствах с широким диапазоном регулировки времени задержки. Известно устройство для задержки импульсов, содержащее генератор тактовых импульсов, элемент совпадения, рабочий и управляющий счетчики, управляющий ключ., триггер f . Недостатками этого устройства являются низкая точность задержки вследствие формирования выходного импульса схемой сравнения, взаимозависимость диапазона электронной регу лировки времени задержки и точности задержки и узкие функциональные возможности, обусловленные тем; что данная цифровая линия задержки не имеет промежуточных отводов. Известно также устройство для задержки импульсов, содержащее генератор тактовых импульсов, элемент совпадения, рабочий и управляющий счетчики, управляемый ключ, триггер, эле мент объединения, многовходовой элемент совпадения, п-входовые элементы совпадения 2 , Недостатками данного устройства являются взаимозависимость диапазо на электронной регулировки времени задержки и точности задержки импульсов . Такое устройство обеспечивает формирование импульса, задержанного относительно входного на величину где п - количество информационных разрядов в слое, хранящемся в управляющем счетчике; Т - период тактовых импульсов генератора тактовых импульсов, при этом точность задержки определяется величиной . Как видно из вышепрйведенного соотношения, при неизменном для обеспечения необходимого диапазона электронной регулировки времени задержки необходимо увеличить период тактовых импульсов, а для обеспечения точной величины задержки - уменьшить период тактовых импульсов. Таким образом, данное устройство обеспечивает высокую точность задержки при узком диапазоне электронной регулировки времени за,держки или обеспечивает широкий диапазон электронной регулировки времени згщержки при низкой точности величины задержки. Кроме того, для данного устройства характерны

низкая помехоустойчивость/ обусловленная тем, что поступление на его вход любого сигнала во время формирования задержанного выходного сигнала приводит к выдаче ложного сигнала, т.е. сигнала, имеющего задержку отличную от заданной а также узкие функциональные возможности, обусловленные тем, что данное устройство за один такт работы не обеспечивает формирование сетки задержанных друг относительно друга импульсов.

Цель изобретения - расширение диапазона электронной регулировки времени задержки . при сохранении точности задержки, повышение помехоустойчивости и расширение функциональных возможностей.

Для достижения указанной цели в устройство для задержки импульсов, содержащее генератор тактовых импульсов, элемент объединения, п двухвходовых логических элементов И, управляющий регистр, инверсные выходы разрядов которого соединены со входами одноименных двухвходовых логических элементов И, рабочий счетчик, многовходовой элемент совпадения, входы которого соединены с выходами разрядов рабочего счетчика, а выход соединен со входом элемента объединения и с первой выходной шиной, введены делитель частоты, логический элемент m И-ИЛИ, элемент запрета, Р входных логических элементов ИЛИ, счетчик масштабов, дешифратор, (т-1) инверторов, формирователь импульсов считывания кода задержки, m выходных логических элементов И, первые входы которых соединены с выходом многовходового элемента совпадения, а их вторые входы соединены с одноименными выходами дешифратора, при этом их выходы соединены с выходными шинами устройства, причем выход генератора тактовых импульсов соединенен со входом делителя, выходы которого от первого до (m-l)-ro соединены со входами одноименных инверторов и с первыми входами групп от первого до (т-1) логического элемента m И-ИЛИ, а т-ый выход соединен с первым входом т-ой группы логического элемента m И-ИЛИ, при этом вторые входы групп от первого до (т-1) логического элемента m И-ИЛИ соединены с одноименными выходами дешифратора и одноименными входгили формирователя импульсов считывания кода задержки, второй вход т-ой группы логического элемента m И-ИЛЙ соединен с т-ым выходом дешифратора, выход логического элемента m И-ИЛИ присоединен к счетному входу рабочего счетчика и к стробирующему входу многовходового элемента совпадения, первый вход элемента запрета соединен со входной шиной, а ее второй вход присоединен к нулевому выходу

дешифратора, при этом выход элемента запрета соединен со вторым входом элемента объединения и со вторыми входами первых Р двухвходовых логических элементов И, выходы которых присоединены к первым входам т-входовых логических элементов ИЛИ , вторые входы двухвходовых логических элементов И от (р+1) до 2р соединены с.первым выходом формирователя импульса считывания кода задержки, вторь:е входы двухвходовых логических элементов от (i р+1) до (i+1) Р соединены с i-ым выходом формирователя импульса считывания кода задержки, вторые входы двухвходовых логических элементов и от (п-р) до п соединены с (т-1) выходом формирователя импульсов считывания кода задержки, выходы двухвходовых логических элементов И от (р+1) до 2 Р соединены со вторыми входами т-входовых логических элементов ИЛИ, выходы двухвходовых логических элементов И от (i р+1) до (i+1)р соединены с (i+1) входами логических элементов ИЛИ ,,, выходы двухвходовых элементов И от (п-р) до п соединены с m входами т-входовых логических элементов ИЛИ, причем выходы т-входовых логических элементов ИЛИ присоединены с поразрядным входам рабочего счетчика, выход элемента объединения соединен со счетным входом счетчика масштабов выход которого присоединен ко входу дешифратора, при этом первый выход дешифратора соединен со вторым входом выходного логического элемента И, выход первого инвертора присоединен к m входу формирователя импульсов считывания кода задержки, выход i инвертора присоединен к (m-l+i) входу формирователя импульсов считывания кода задержки, ... выход (ш-1) инвертора присоединен к 2 (т-1 входу формирователя импульсов считывания кода задержки, вход Уст.О формирователя импульсов считывания кода задержки соединен с выходом многовходового элемента совпадения. .

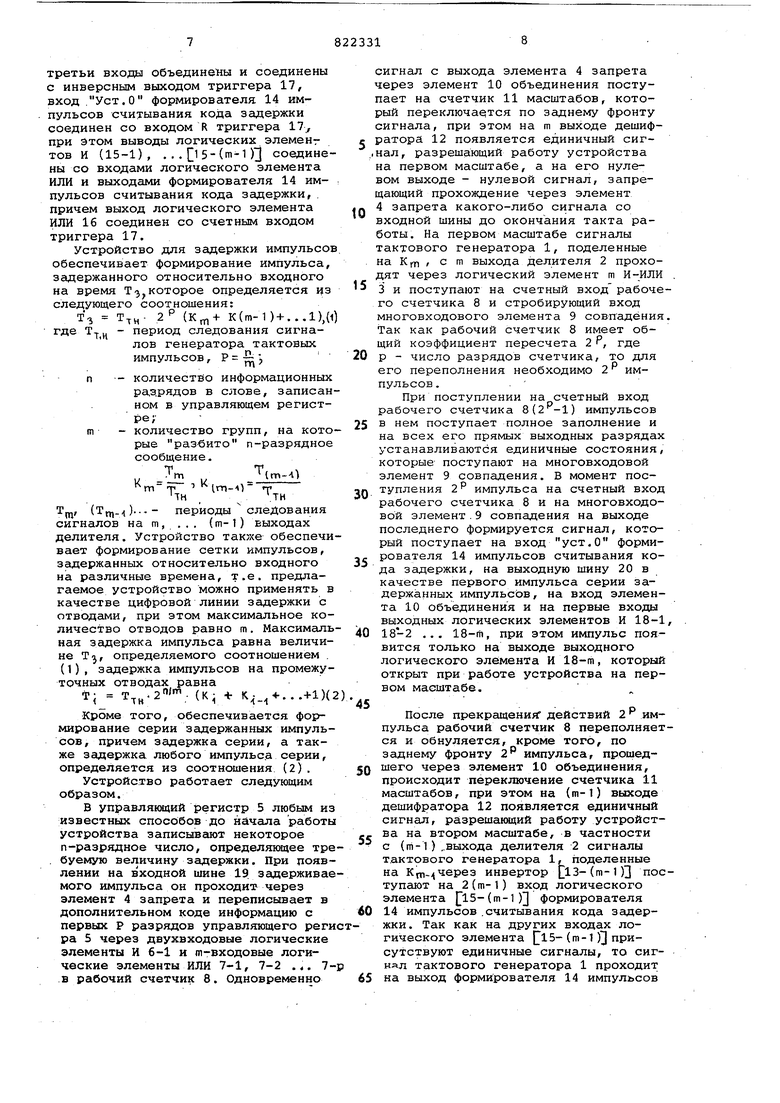

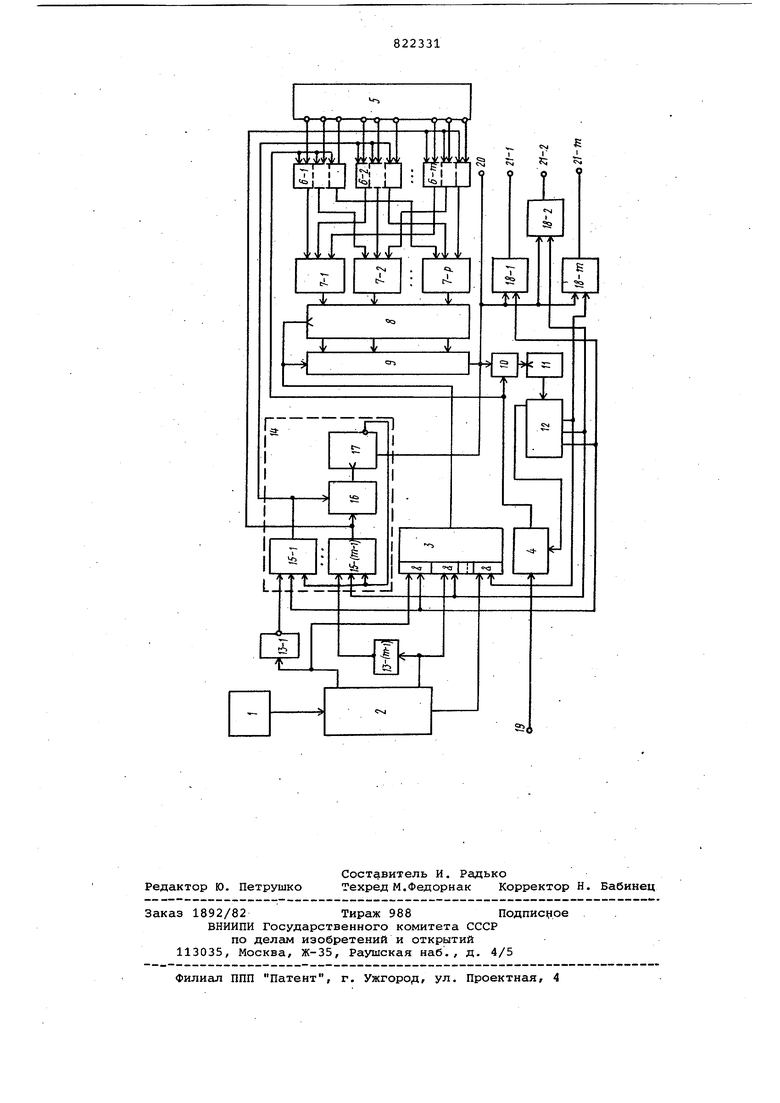

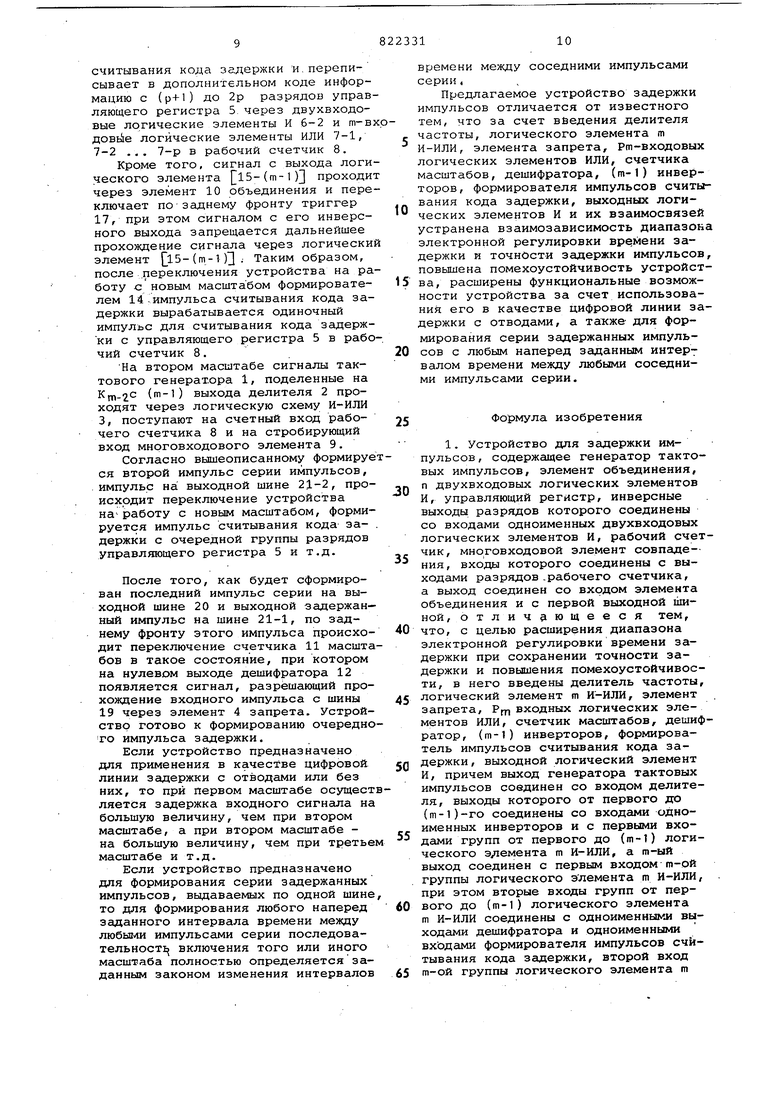

При этом формирователь импульсов считывания кода задержки содержит (ffl-1) трехвходовых логических элементов И, элемент объединения и триггер , причем первые входы логических элементов И соединены с одноименными входами формирователя импульсов считывания кода задержки, а его входы от (m-1)+l3 до,2(т-1) присоединены соответственно ко вторым входам логических элементов И, третьи входы логических элементов И объединены и соединены с инверсным выходом триггера, вход R которого соединен со входом Уст.О формирователя импульсов считывания кода задержки, выходы логических элементов. И соединены со входами логического элемента И.ЛИ и выходами формурователя импульсов считывания кода задержки, выход логического элемента ИЛИ соединен со счетным входом триггера. Кроме того,в устройство введены (т-1) выходных логических элементов И, первые входы которых соединены с выходом многовходового элемента сов падения, а их вторые входы соединен с одноименными выходами дешифратора при этом их выходы соединены с выхо ными шинами устройства. На чертеже представлена схема устройства. Устройство содержит генератор 1 тактовых импульсов, делитель 2 час ты, логический элемент m И-ИЛИ 3, элемент 4 запрета, управляющий рее гистр 5, п двухвходовых элементов И б,.при этом в каждой группе 6-1, б-2, ... 6-т содержится р элементов, причем р«т п, т-входовые ло гические элементы ИЛИ 7-1,7-2, ... 7-р, рабочий счетчик 8, многовходо вой элемент 9 совпадения, элемент 10 объединения , счетчик 11 масштабов., дешифратор 12, инверторы 13-1 13-2, ... 13-р, формирователь 14 «мпульсов считывания кода задержки который содержит логические элементы И 15-1, 15-2, ... 15-(т-1), логический элемент ИЛИ 16 и триггер 17, выходные логические элементы И 18-1, 18-2, ... 18-in, входную шину 19, выходные шины 20 и 21-1,21-2 ... 21-т. Генератор 1 тактовых импу сов соединен со входом делителя 2, выходы которого от первого до (т-1)-го соединены со входами одноименных инверторов 13-1, ... 13-(т-1) и с первыми входами групп от первой до (т-1)-ой логического элемента m И-ИЛИ 3, а т-ый выход делителя 2 соединен с первым входом т-ой группы логического элемента m И-ИЛИ 3, при этом вторые входы групп от первой до (т-1)-ой логичес кого элемента m И-ИЛИ 3 соединены с одноименн лми выходс ми дешифратора 12, С одноименными входами формирователя 14 импульсов считывания кода Эсшержки и со вторыми входами од ноименных выходных логических элементов И 18-1, 18-2, ... 18-(т-1), второй вход Л1-ОЙ группы логического элемента т И-ИЛИ 3 соединен с т-ым выходом дешифратора 12 и со вторым входом выходного логического элемен та И (l8-m), выход логического элемента m И-ИЛИ 3 присЬединен к счетному входу рабочего счетчика 8j пер вый вход элемента 4 запрета соединен со входной шиной 19, а ее второй вход присоединен к нулевому выходу дешифратора 12, при этом выход элемента 4 запрета соединен со вторым входом элемента 10 объединения со вторыми входами первых Р двухвходовых логических элементов И 6-1 инверсные выходы разрядов управляющего регистра 5 соединены с первыми входами одноименных двухвходовых логических элементов И 6-1, 6-2, ... 6-т, вторые входы Двухвходовых логических элементов И от (р+1) до 2р (6-2) соединены с первыми выходами формирователя 14 импульсов считывания кода задержки, вторые входы двухвходовых логических элементов от (i р+1) до (i+I)p (6-i+l) соединены с i-ым выходом формирователя 14 импульса считывания кода задержки, вторые входи двухвходовых логических элементов И от (п-р) до (6-.т) соединены с (т-1) выходом формирователя 14 импульса считывания кода задержки., при этом выходы первых Р двухвходовых1 логических элементов И (6-1) подключены к первым входам т-входовых логических элементов ИЛИ 7-1, выходы двухвходовых логических элементов И от (i р+1) до (i+1)p (6-i) подключены к (i+1) входам т-входовых логических элементов ИЛИ (7-i), выходы двухвходовых логических элементов И от (п-р) до п(6-т) соединены с m входами т-входовых логических элементов ИЛИ 7-р, причем выходы т-входовых элементов ИЛИ 7-1. 7-2, ... 7-р присоединены по подразрядным входам рабочего счетчика 8, выходы разрядов которого соединены со входё1ми многовходового элемента 9 совпадения, при этом выход многовходового элемента 9совпадения соединен с первым вхо-. дом элемента 10 объединения, со входом Уст.О формирователя 14 импульсов считывания кода задержки, с первыми входами логических элементов И 18-1, 18-2, ... 18-rti, с первой выходной шиной 20, выход элемента 10объединения соединен со счетным входом счетчика 11 масштабов, выход которого присоединен ко входу дешифратора 12, ;ПРИ этом выход ПврВОГО ИНвертора (13-1) присоединен к m входу формирователя 14 импульсов считывания кода задержки, выход i инвертора (13-0 присоединен к (m-l-fi) входу формирователя 14 импульсов считывания кода задержки, ... выход (т-1) инвертора l3-(m7l)J присоединен к 2(т-1).входу формирователя 14 импульсов считывания кода задержки, выходы выходных логических элементов И 18-1, 18-2, ... 18-т соединены с выходными шинами со второй до (т+1)-ой, при этом в формирователе 14 импульсов считывания кода задержки первые входы логических элементов и (15-1) ..., 15-(т-1)3 соединены с его одноименными входами, вторые входы логических элементов И (15-1), ... 15-(т-1) соединены соответственно со входами формировате- . я 14 импульсов считывания кода эаержки от Ctm-O + O до 2(т-1), а их третьи входы объединены и соединены с инверсным выходом триггера 17, вход.Уст.О формирователя 14 импульсов считывания кода задержки соединен со входом R триггера 17, при Этом выводы логических элемент тов И (15-1), . . . 15-( )j соедине ны со входами логического элемента ИЛИ и выходами формирователя 14 импульсов считывания кода задержки,. причем выход логического элемента ИЛИ 16 соединен со счетным входом триггера 17. Устройство для зсщержки импульсо обеспечивает формирование импульса, задержанного относительно входного на время Тэ,которое определяется из следующего соотношения: 2 Р K(m-1) + ...l),( Тз -тн где Т, -период следования сигналов генератора тактовых импульсов л Р -количестйо информационных разрядов в слове, записан ном в управляющем регистре;-количество групп, на кото рые раз-бито п-разрядное сообщение. lm-4) т тн тн Т, (Tffl.)..-- периоды следования сигналов на m, ... (m-l) выходах делителя. Устройство также обеспечи вает формирование сетки импульсов, задержанных относительно входного на различные времена, т.е. предлагаемое устройство можно применять в качестве цифровой линии задержки с отводами, при этом максимальное ко личество отводов равно m. Максимешь ная задержка импульса равна величине Tj, определяемого соотношением . (1), задержка импульсов на промежу точных отводах равна i-j .2. (К Ч: К «-...+)( Кроме того, обеспечивается формирование серии задержанных импуль сов, причем задержка серии, а также задержка любого импульса серии, определяется из соотношения (2). Устройство работает следующим образом. В управляющий регистр 5 любьпл и известных способов до начала работ устройства записывёиот некоторое п-разрядное число, определяющее тр буемую ве.аичину задержки. При появ лении на входной шине 19 задержива мого импульса он проходит через элемент 4 запрета и переписывает в дополнительном коде информацию с первых Р разрядов управляющего рег ра 5 через двухвходовые логические элементы И 6-1 и т-входовые логические элементы ИЛИ 7-1, 7-2 ... 7 в рабочий счетчик 8. Одновременно сигнал с выхода элемента 4 запрета ерез элемент 10 объединения постуает на счетчик 11 масштабов, котоый переключается по заднему фронту сигнала, при этом на m выходе дешифатора 12 появляется единичный сигнал, разрешающий работу устройства на первом масштабе, а на его нулевом выходе - нулевой сигнал, запреающий прохождение через элемент 4 запрета какого-либо сигнала со входной шины до окончания такта работы. На первом масштабе сигналы тактового генератора 1, поделенные на К , с m выхода делителя 2 прохоят через логический элемент m И-ИЛИ , 3 и поступают на счетный вход рабочего счетчика 8 и стробирующий вход многовходового элемента 9 совпадения. Так как рабочий счетчик 8 имеет общий коэффициент пересчета 2 Р, где Р - число разрядов счетчика, то для его переполнения необходимо 2 импульсов . . При поступлении на счетный вход рабочего счетчика 8(2-1) импульсов в нем поступает полное заполнение и на всех его прямых выходных разрядах устанавливаются единичные состояния, которые поступают на многовходовой элемент 9 совпадения. В момент поступления 2 импульса на счетный вход рабочего счетчика 8 и на многовходовой элемент.9 совпадения на выходе последнего формируется сигнал, который поступает на вход уст.О формирователя 14 импульсов считывания кода задержки, на выходную шину 20 в качестве первого импульса серии задержанных импульсов, на вход элемента 10 объединения и на первые входы выходных логических элементов И 18-1, 18-2 ... 18-т, при этом импульс появится только на выходе выходного логического элемента И 18-т, который открыт при работе устройства на первом масштабе. После прекращениуГ действий 2 импульса рабочий счетчик 8 переполняется и обнуляется, кроме того, по заднему фронту 2 импульса, прошедшего через элемент 10 объединения, происходит переключение счетчика 11 масштабов, при этом на (m-l) выходе дешифратора 12 появляется единичный сигнал, разрешающий работу устройства на втором масштабе, в частности с (т-1) ,выхода делителя 2 сигналы тактового генератора 1, поделенные на Кп1-,{через инвертор L13-(m-1)3 поступают на 2(m-l) вход логического э леме нта 15-(т-1) формиров ате л я 14 импульсов .считывания кода зещержки. Так как на других входах логического элемента 15-(m -1 ) присутствуют единичные сигналы, то сигнал тактового генератора 1 проходит на выход формирователя 14 импульсов считывания кода задержки и,переписывает в дополнительном кодге информацию с (р+1) до 2р разрядов управ ляющего регистра 5 через двухвходовые логические элементы И 6-2 и т-в довйе логические элементы ИЛИ 7-1, 7-2 ... 7-р в рабочий счетчик 8. Кроме того, сигнал с выхода логи ческого элемента 15-(т-1)3 проходи через элемент 10 объединения и пере ключает по-заднему фронту триггер 17, при этом сигналом с его инверсного выхода запрещается дальнейшее прохождение сигнала через логически элемент (15-(т-1 )3 . Таким образом, после .переключения устройства на ра боту с новым масштабом формирователем 14-импульса считывания кода задержки вырабатывается одиночный импульс для считывания кода задерж ки с управляющего регистра 5 в рабо чий счетчик 8. На втором масштабе сигналы тактового генератора 1, поделенные на Kfn.2 (m-l) выхода делителя 2 проходят через логическую схему И-ИЛИ 3, поступают на счетный вход рабочего счетчика 8 и на стробирующий вход мнрговходового элемента 9. Согласно вышеописанному формируе ся второй импульс серии импульсов, импульс на выходной шине 21-2, происходит переключение устройства на работу с новым масштабом, формируется импульс считывания кода задержки с очередной группы разрядов управляющего регистра 5 и т.д. После того, как будет сформирован последний импульс серии на выходной шине 20 и выходной задержанный импульс на шине 21-1, по заднему фронту этого импульса происходит переключение счетчика 11 масшта бов в такое состояние, при котором на нулевом выходе дешифратора 12 появляется сигнал, разрешающий прохождение входного импульса с шины 19 через элемент 4 запрета. Устройство готово к формированию очередно то импульса задержки. Если устройство предназначено для применения в качестве цифровой линии задержки с отводами или без них, то при первом масштабе осущест ляется задержка входного сигнала на большую величину, чем при втором масштабе, а при втором масштабе на большую величину, чем при третье масштабе и т.д. Если устройство предназначено для формирования серии задержанных импульсов, выдаваемых по одной шине то для формирования любого наперед заданного интервала времени между любыми импульсами серии последовательност включения того или иного масштаба полностью определяется заданным законом изменения интервалов времени между соседними импульсами серии, Предлагаемое устройство задержки импульсов отличается от известного тем, что за счет введения делителя частоты, логического элемента m И-ИЛИ, элемента запрета, Рт-входовых логических элементов ИЛИ, счетчика масштабов, дешифратора, (m-l) инверторов, формирователя импульсов считывания кода задержки, выходных логических элементов И и их взаимосвязей устранена взаимозависимость диапазона электронной регулировки времени задержки и точности задержки импульсов, повышена помехоустойчивость устройства, расширены функциональные возможности устройства за счет использования его в качестве цифровой линии задержки с отводами, а также- для формирования серии задержанных импульсов с любым наперед згщанным интер7 валом времени между любыми соседними импульсами серии. Формула изобретения 1. Устройство для задержки импульсов , содержащее генератор тактовых импульсов, элемент объединения, п двухвходовых логических элементов И, управляющий регистр, инверсные выходы разрядов которого соединены со входами одноименных двухвходовых логических элементов И, рабочий счетчик, многовходовой элемент совпаде-ния, входы которого соединены с выходами разрядов .рабочего счетчика, а выход соединен со входом элемента объединения и с первой выходной шиной, отличающееся тем, что, с целью расширения диапазона электронной регулировки времени задержки при сохранении точности задержки и повышения помехоустойчивости, в него введены делитель частоты, логический элемент m И-ИЛИ, элемент запрета, Pfn входных логических элементов ИЛИ, счетчик масштабов, дешифратор, (т-1) инверторов, формирователь импульсов считывания кода задержки , выходной логический элемент И, причем выход генератора тактовых импульсов соединен со входом делителя, выходы которого от первого до (т-1)-го соединены со входами одноименных инверторов и с первыми входами групп от первого до (т-1) логического элемента m И-ИЛИ, а т-ый выход соединен с первым входом т-ой группы логического элемента m И-ИЛИ, при этом вторые входы групп от первого до (т-1) логического элемента m И-ИЛИ соединены с одноименными выходами дешифратора и одноименными входами формирователя импульсов считывания кода задержки, второй вход ш-ой группы логического элемента m

И-ИЛИ соединен с т-ым шлходом дешифратора, выход логичьеского элемента m И-ИЛИ присоединен к счетному входу рабочего счетчика и к стробкрующему входу многовходового элемента совпадения, первый вход элемента запрета соединен со входной шиной, а ее второй вход присоединен с нулевому .выходу дешифратора, при этом выход элемента запрета соединен со вторым входом элемента объединения и со вторыми входами Р двухвходовых логических элементов И, выходы которых присоединены к первым входам m входовых логических элементов ИЛИ, вторые входа: двухвходовых логических элементов И от (р+1) до 2р соединены с первым выходом формирователя импульса считывания кода задержки , вторые входы двухвходовых логических элементов от (ip+1) до (i+1)P соединены с i-ым выходом формирователя импульса считывания кода задержки, вторые входы двухвходовых логических элементов И от (п-р) до п соединены с (т-1) выходом формирователя импульсов считывания кода задержки, выхода двухвходовых логических элементов И от (р+1) до 2р соединены со вторыми входами m входовых логических элементов ИЛИ, выходы двухвходовых логических элементов И от ( р+1) до (i+1)p соединены с (i+1) входами логических элементов ИЛИ ..., выходы двухвходовых элементов И от (п-р) до п соединены с m входами m входовых логических элементов ИЛИ, выходы т-входовых логических элементов ИЛИ присоединены к поря3радным входам рабочего счетчика, выход элемента объединени соединен со счетным входом счетчика масштабов, выход которого присоединен ко входу дешифратора, при этом первый выход д@1Шфратора соединен со вторым входом выходного логического элемента И, выход первого инвертора присоединен к m входу формирователя импульсов считывания код задержки, выход I инвертора присоединен к (m-1+i) входу формирователя импульсов считывания кода задержки, ..., выход (т-1) инвертора присоединен к 2 (m-l) входу формирователя импульсов считывания кода задержки, е ВХОД Уст.О формирователя импульсов счить1вания кода задержки соединен с выходом многовходового элемента совпадения.

2. Устройство по п. 1, о т л и. чающееся тем, что формирователь импульсов считывания кода задержки содержит (ffl-1) трехвходовых логических элементов И, элемент объединения и триггер, причем первые входы логических элементов И соедине-.

5 ны с одноименными входами формирователя импульсов считывания кода задержки, а его входы от {(m-O+l до 2 (т-1) присоединены соответственно ко вторым входам логических элемен0 тон И, третьи входы логических элементов И объединены и соединены с инверсными выходами триггера, вход R которого соединен со входом Уст,О формирователя импульсов считывания

5 кода задержки, выходы логических

элементов И соединены со входами логического элемента ИЛИ и с выходами формирователя импульсов считывания кода задержки, выход логического

элемента или соединен со счетным входом триггера.

3. Устройство по пп. 1 и 2, о тли чающееся тем, что,с целью расширения его функциональных возможностей, в него введены (т-1) выходных логических элементов И, первые входы которых соединены с выходом многовходового элемента совпадения, а их вторые входы соединены с одноименными выходами дешифратора, 0 при этом их выходы соединены с выходными шинами устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 5 457158, кл. Н 03 Н 9/30, 25,02.72.

2.Авторское свидетельство СССР

W 598224, кл, Н 03 К 5/13, 27.09.76,

С

оo-t

MKiJiU

r.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1985 |

|

SU1350823A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| УСТРОЙСТВО ДИСКРЕТНОГО КОНТРОЛЯ УРОВНЯ КУСКОВЫХ МАТЕРИАЛОВ В ПОДЗЕМНОЙ ЕМКОСТИ | 1989 |

|

RU2008626C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| Моментный вентильный электродвигатель | 1988 |

|

SU1751836A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1999 |

|

RU2153699C1 |

Авторы

Даты

1981-04-15—Публикация

1979-04-16—Подача