(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная цифровая телеметрическая система | 1982 |

|

SU1053127A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Многоканальная цифровая телеметрическая система | 1985 |

|

SU1280420A1 |

| Устройство для сжатия и передачи телеметрической информации | 1987 |

|

SU1640729A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1989 |

|

SU1656573A2 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2446461C2 |

| Устройство для передачи и приема телеметрической информации | 1986 |

|

SU1397956A1 |

| Устройство для обработки и сжатияиНфОРМАции | 1979 |

|

SU840914A2 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для сжатия и передачи телеметрической информации | 1983 |

|

SU1153336A1 |

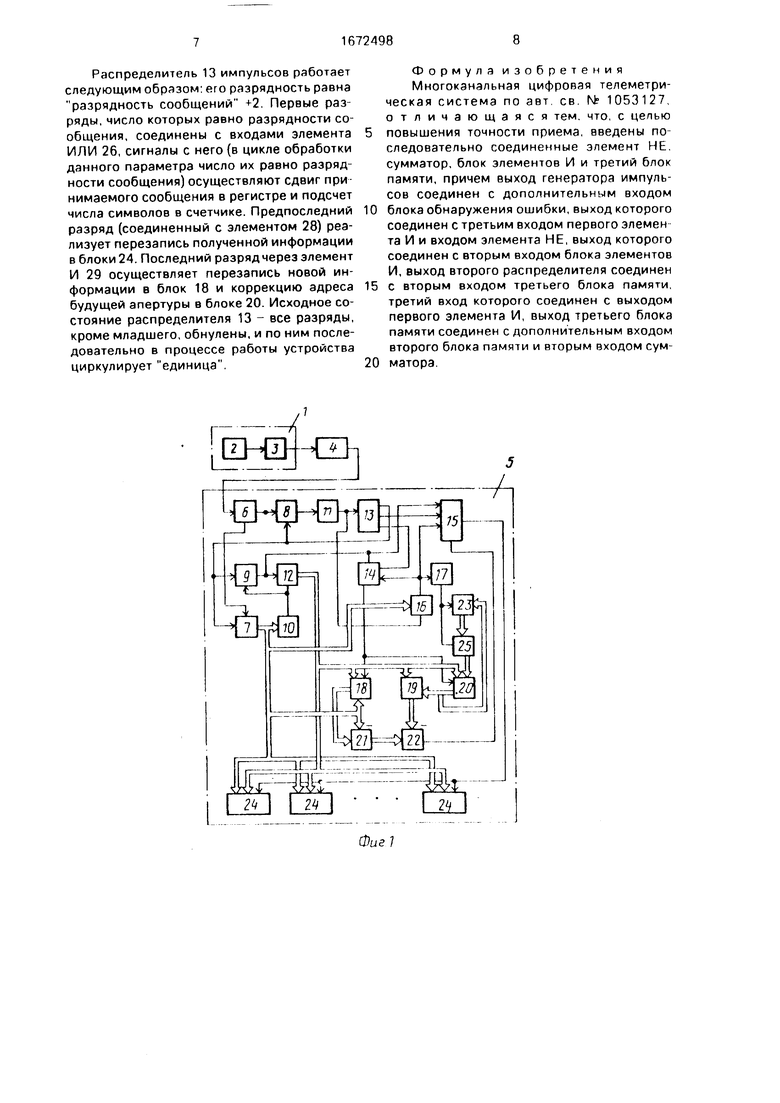

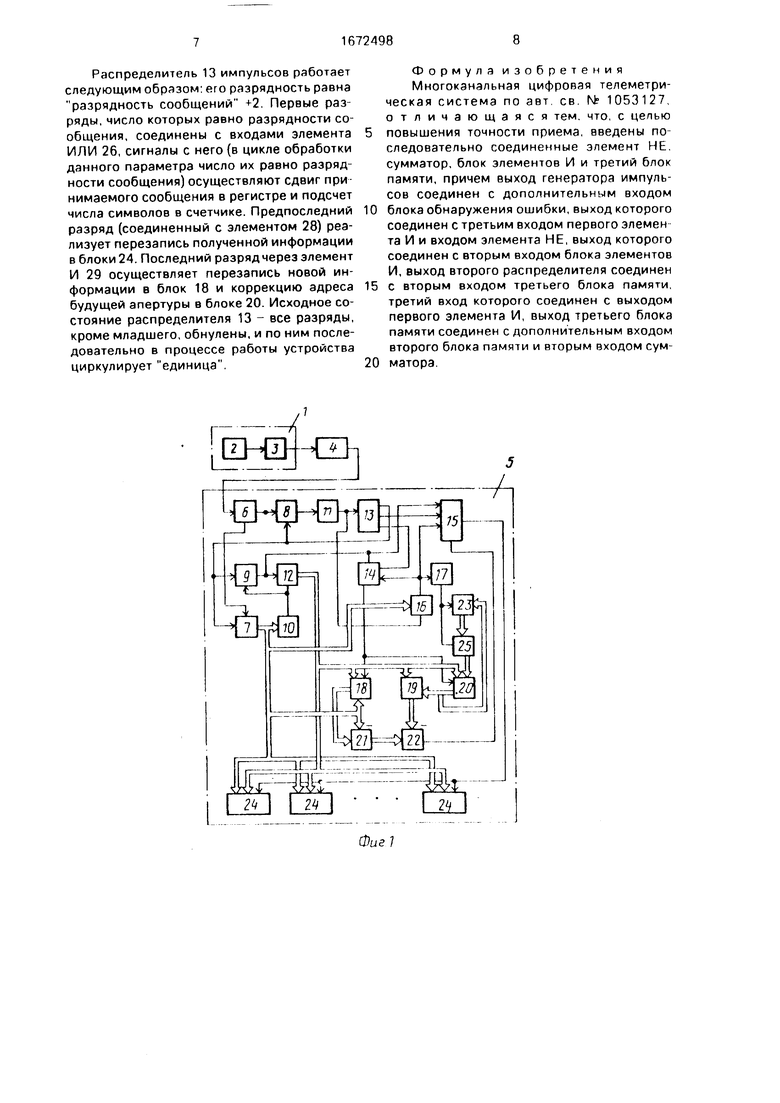

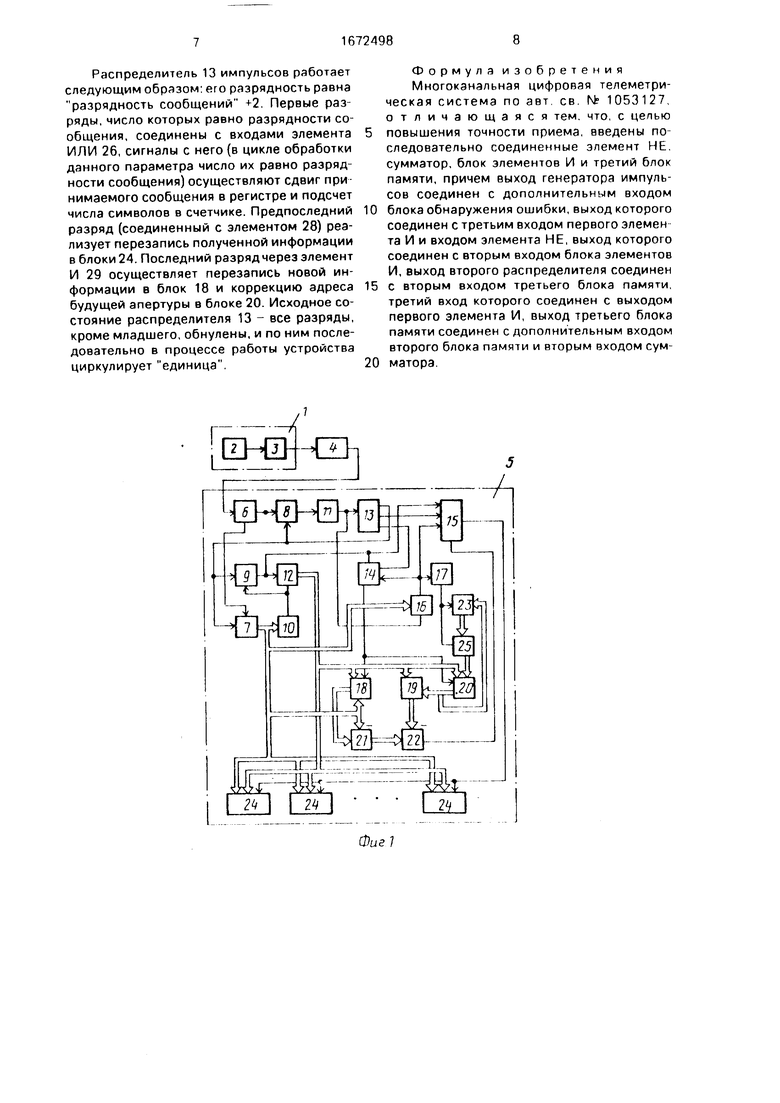

Изобретение относится к технике передачи данных. Цель изобретения - повышение точности приема. Многоканальная цифровая телеметрическая система содержит передающий полукомплект, состоящий из датчиков 2, передатчика 3, канал связи 4 и приемный полукомплект 5, состоящий из формирователя 6 импульсов, регистра 7 сдвига, блока 8 синхронизации, счетчика 9, блока 10 выделения маркерного сигнала, инициатора 11 импульсов, второго и первого распределителей 12, 13 импульсов, первого, второго элементов И 14, 15, блока 16 обнаружения ошибки, первого, второго блоков 18, 19 памяти, первого, второго вычитателей 21, 22, блоков 24 воспроизведения. Цель достигается введением элемента НЕ 17, сумматора 23, блока 25 элементов И и третьего блока 20 памяти. 3 ил.

Изобретение относится к технике передачи данных, дискретной информации и телемеханике, может применяться для информационного обеспечения сетей связи, систем передачи данных и автоматизированных систем управления

Цель изобретения повышение точности приема.

На фиг. 1 изображена структурная электрическая схема предложенной многоканальной цифровой телеметрической системы; на фиг. 2 - схема первого распределителя, на фиг. 3 - схема первого вычита- теля.

Многоканальная цифровая телеметрическая система содержит передающий полукомплект 1, состоящий из датчиков 2, передатчика 3, канал связи 4 и приемный полукомплект 5. состоящий из формирователя 6 импульсов, регистра 7 сдвига, блока

8 синхронизации, счетчика 9, блока 10 выделения маркерного сигнала, инициатора 11 импульсов, второго распределителя 12 импульсов (каналов), первого распределителя 13 импульсов, первого элемента И 14, второго элемента И 15, блока 16 обнаружения ошибки, элемента НЕ 17, первого, второго и третьего блоков 18-20 памяти, первого, второго вычитателей 21, 22, сумматора 23, блоков 24 воспроизведения, блока 25 элементов И.

Распределитель 13 состоит из элемента ИЛИ 26, элементов И 27-29 и кольцевого регистра 30 сдвига. Вычитатель 21 состоит из сумматора 31, сумматора 32 по модулю два, сумматора 33, сумматоров 34 по модулю два.

Многоканальная цифровая телеметрическая система работает следующим образом

О NJ

ГО

ь

Ю 00

Ю

Передатчик 3 производит опрос дат чиков 2 и формирует сообщения по результатам опроса отдельных датчиков, представляющее собой последовательную кодо-импульсную посылку информационных и контрольных символов кода, Конт рольные кодовые символы вводятся для проверки лишь ограниченного числа рлзря дов (младших или старших - в зависимости от цели передачи информации). Сообщения поступают в канал 4 связи циклически в определенной, заранее известной последовательности Циклы передачи отличаются друг от друга маркерным сигналом.

Приемный полукомплект 5, принимая кодовые сообщения из каналов связи, преобразует последовательный код в параллельный и выдает его в соответствующие блоки воспроизведения 24. В случае обнаружения ошибки в некотором сообщении, представляющем собой некоторое значение какого-либо параметра, выдача информации в соответствующий блок 24 запрещается Сигналы из канала связи 4 посыпают а фор мирователь 6 импульсов Блок 8 синхроьи зации сравнивает фазу выходных импульсов формирователя 6 с фазой импульсов нг выходе распределителя 13 Им осуществляет ся коррекция частоты и фазы импульсов генератора 11. Иначе говоря, блок 8 синх ронизирующий узел с непосредственным воздействием на задающий генератор Ре гистр 7 сдвига выполняет функции преобра зования последовательного кода в параллельный и запоминание информации, принятой в одном кодовом сообщении На информационный вход регистра 7 поступает последовательный код сообщения от формирователя 6. Сдвиг осуществляется импульсами, поступающими от распределителя 13 (конкретно с выхода элемента И 27). При поступлении на вход приемника последнего символа очередного сообщения (все сообщения имеют равную фиксированную длину, а разрядность регистра сдвига равна длине сообщений), на выходах регистра 7 имеется параллельный код. соответствующий этому сообщению. Одновременно с этим с выхода счетчика 9 (его емкость равна зарядности сообщения) появляется одиночный импульс, поступающий на элементы И t4 и 15.

В вычиУателе 21 определяется абсолютная величина разности между предыду щим значением данного параметра, записанным в блоке памяти 18. и новым значением этого же параметра, содержащимся в регистре 7. Вычитатель 21 работает следующим образом (на фиг. 3 приведен в качестве примера вычитатель. оперирую

щии с трехразрядными двоичными числами старшим, четвертым разрядом определяется знак числа О положительное 1 отрицательное) Определяется модуль раз

ности Вычитание заменяется сложением чисел в дополни гольном коде, причем новое значение параметра используется п качест ве уменьшаемого я старое как вычитаемое На сумматорах 14 фо пируете ч

0 дополнительный код отрицательного вычитаемого (с единицей в старшем, знаковом четвертом в данном случат, разряде с добавлением единицы в младший разрпд путем присоединения вводною перенося

5 РО к единичному потенциалу После сум мирования на сумматоах 32 и 33 произпо дится преобразование суммы в прямой код {..спи зсг -j am разряд суммы нуле вой то результат Ьез изменений выводит0 ся на выходах блок л ее .i знаковый разряд единичный, ш производится обычное преобразование инверсия суммы на сумм.-) торах 32 и добавление сдпни в младший разряд на сумматоре 33 ш калиг ; вход

Ь РО

Выбор элементов памяти п о юке 18, соответствующих этому параметру осущр ствляется адресным гчи чалом, поступающим от распределителя 12 Полученная на

0 выходе вычислителе21 разность пычмтастч в вычитателе 22 из соответствующего , наче- ния апертуры для ттого параметра и для текущего интервала времени г е -,ду данными значениями и предыдущим принятым

5 правильно Апертуры з.чписанн ь блоке 19(он выполняется в ii -де г еточною запоминающего устройства и то время как первый и третий бпоки намят щ. делэпляют собой оперативные запоминающие утрой

0 ства) Значение апергуры выбирается по адресам сформированием распределителем 12 и 20 Рели результат вычитания в блок. 22 больше нуля (апертура больше текущего изменения реального параметра), то на

5 элемент И 15 с выхода вычислителя 22 (выполненного в виде обычного, устройства сравнения, у которою для формирования выходного сигнала использутся выход типа больше) поступает разрешающий единичО ный сигнал

Таким образом запрещающий (по апертуре) сигнал формируется в зависимости от соотношения апертуры и текущей разности данного и предыдущего эначрнич дачного

5 параметра.

Блок 19 содержит две группы адресных разрядов Одна, с распределителя 12,определяет группу апертур для определенного параметра Остановим «н сколько подробнее на другой г УГ пе чдрег-нн разрядов

формируемых на блоке памяти 20. По адресам, вырабатываемым тем же распределителем 12, в блоке 20 хранятся для каждого параметра текущие значения предыдущих (последних смежных, т.е. идущих подряд) ошибочных передач. Таким образом, в блоке памяти 19 хранятся апертуры для следующих вариантов приема некоторого (любого) параметра (определяемых адресами из блока памяти 20):

а)предыдущая передача была безошибочной;

б)одна предыдущая передача имела ошибку в сообщении;

в)две предыдущие смежные передачи содержали ошибки и т.д.

Таким образом, запрещающий (по апертуре) сигнал поступает в зависимости от значений принятого в текущий момент времени параметра и его апертуры, зависящей от интервала времени между текущим и предыдущим правильно принятым значением (с учетом числа сообщений данного параметра между ними, принятых с ошибками).

Блок 16 обнаружения ошибки в кодовом сообщении осуществляет проверку на достоверность определенного числа(выбранных пользователем среди всех разрядов сообщений) разрядов путем анализа проверочных разрядов, поступивших из канала 4 связи и записанных в регистре 7, этот блок формирует запрещающий нулевой потенциал при обнаружении ошибок, и при отсутствии ошибок - разрешающий единичный потенциал, который поступает на вход элемента И 15, давая разрешение на прохождение записывающего импульса с выхода распределителя 13 в блоки 24. При этом код информации по данному параметру с регистра 7 переписывается в соответствующий блок воспроизведения. Это происходит в момент приема полностью сообщения (сигнал со счетчика) по разрешающим сигналам от распределителя 13 и вычитателя 22. Перезапись нового значения параметра (при отсутствии ошибки) осуществляется по сигналу с третьего выхода распределителя 13 на элемент И 14 по разрешающим сигналам со счетчика 9 и блока 16.

Перезапись нового значения параметра в блок 18 совпадает по времени с записью результата обнаружения ошибки в блок 20 памяти. В случае наличия ошибки из блока 16 поступает О - сигнал, преобразуемый элементом НЕ 17 в 1, и это значение суммируется на сумматоре 23 с текущим значением предыдущих смежных неверно принятых сообщений по данному параметру и по разрешающему сигналу с элемента

HI1 17 и по сигналу записи с элемента И 14 через блок И 25 записывается в блок 20, теперь это новый адрес, по которому при следующем принятии значения данного па5 раметра будет взято новое (как правило, большее) значение апертуры. Если же текущее сообщение принято без ошибки, то сигнал с выхода элемента НЕ 17 равен нулю, и по сигналу записи содержимое соответству0 ющей ячейки блока 20 обнуляется, для последующего значения параметра данное устройство будет работать аналогично прототипу. Перезапись параметра в блок 18 и корректировка адреса апертуры происходит

5 по сигналу с третьего входа распределителя 13. Переключение распределителя 12 производится по заднему фронту сигнала со счетчика 9. Обнаружив маркерный сигнал, блок 10 вырабатывает импульс, который, по0 ступая на установочные входы счетчика 9 и блока 12. устанавливает их в исходное состояние. Блок 10 может быть выполнен в виде обычного дешифратора, настроенного на кодовую последовательность, вы5 бранную в качестве маркерной (с одних триггеров снимаемые сигналы в регистре используются в прямой форме, с других - в инверсной).

0Блок 16 представляет собой декодер

произвольно выбранного для передачи кода, работающий в режиме обнаружения ошибок. Код может быть, например, циклическим, итеративным, Хеминга. Декодер вы5 полняется по стандартной схеме для конкретного кода. Например, при использовании кода с проверкой на нечетность (самый распространенный код) данный блок представляет собой совокупность включен0 ных последовательно (по пирамидальной схеме) сумматоров по модулю два либо стандартное устройство - микросхему. На входы сумматоров (свободные) поданы защищаемые кодом разряды информационной части

5 сообщения и проверочный разряд. При обнаружении ошибки (четное число единиц в сумме по модулю два) на выходе последнего сумматора будет нуль, что и требуется. Совместно с регистром 7 блок 16, выполнен0 ный в качестве дешифратора, легко образуют декодер кода Хемминга в режиме обнаружения ошибки,

Блок 8 синхронизации может быть выполнен по принципу обычного устройства

5 тактовой синхронизации с непосредственным воздействием на задающий генератор, где между выходом генератора и входом фазового детектора включается распределитель 13, что не изменяет принципа и характеристик работы устройства.

Распределитель 13 импульсов работает следующим образом: его разрядность равна разрядность сообщений +2. Первые разряды, число которых равно разрядности сообщения, соединены с входами элемента ИЛИ 26, сигналы с него (в цикле обработки данного параметра число их равно разрядности сообщения) осуществляют сдвиг при нимаемого сообщения в регистре и подсчет числа символов в счетчике. Предпоследний разряд (соединенный с элементом 28) реализует перезапись полученной информации в блоки 24. Последний разряд через элемент И 29 осуществляет перезапись новой информации в блок 18 и коррекцию адреса будущей апертуры в блоке 20. Исходное состояние распределителя 13 - все разряды, кроме младшего, обнулены, и по ним последовательно в процессе работы устройства циркулирует единица.

ЭЧ7Н0г

-J t j

Формула изобретения Многоканальная цифровая телеметрическая система по авт св. N 1053127, отличающаяся тем. что, с целью повышения точности приема, введены последовательно соединенные элемент НЕ. сумматор, блок элементов И и третий блок памяти, причем выход генератора импульсов соединен с дополнительным входом блока обнаружения ошибки, выход которого соединен с третьим входом первого элемен та И и входом элемента НЕ, выход которого соединен с вторым входом блока элементов И, выход второго распределителя соединен с вторым входом третьего блока памяти, третий вход которого соединен с выходом первого элемента И, выход третьего блока памяти соединен с дополнительным входом второго блока памяти и вторым входом сумматора.

7J

75

I 24

От 6л. 7

От бк. 18

+ ГБл 7

+ К 5л. 15 К 6л. Щ

Фиг. 2

Кбл.22

Фиг.З

| Многоканальная цифровая телеметрическая система | 1982 |

|

SU1053127A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-08-23—Публикация

1989-10-20—Подача