(5) УСТРОЙСТВО ДЛЯ СБОРА, КОДИРОВАНИЯ, ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С ИСПРАВЛЕНИЕМ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1983 |

|

SU1141439A2 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| ПОЕЗДНОЕ УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ С РЕГУЛИРОВАНИЕМ СКОРОСТИ | 1996 |

|

RU2120393C1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Система управления многоканальнымэлЕКТРОпРиВОдОМ РОбОТА | 1979 |

|

SU805246A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ПО БИОЛОГИЧЕСКИ АКТИВНЫМ ТОЧКАМ | 1991 |

|

RU2005460C1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| Устройство для передачи и приема сигналов по силовой электрической сети | 1986 |

|

SU1374267A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

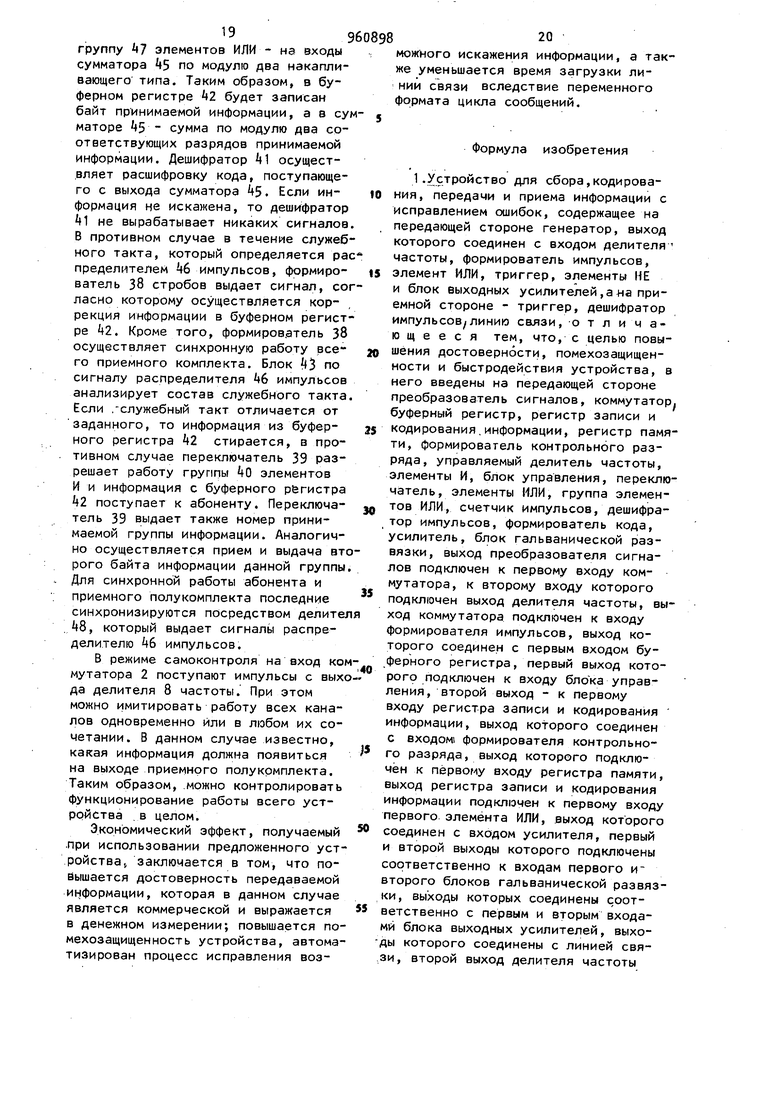

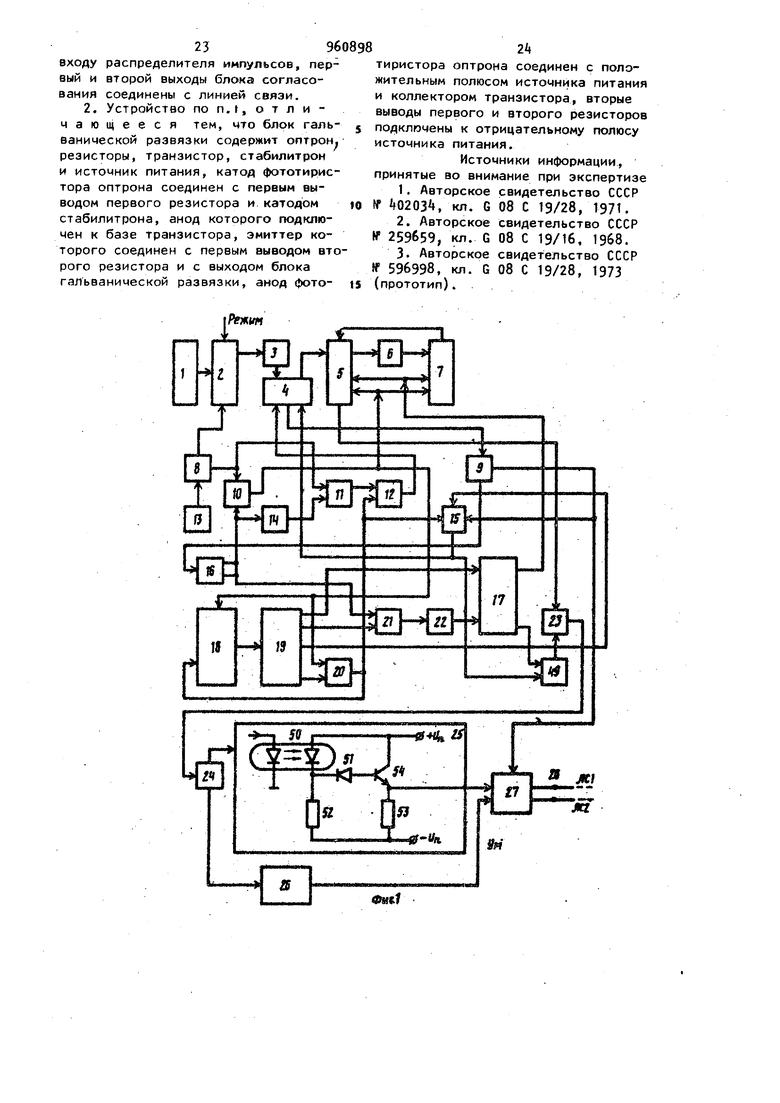

Изобретение относится к устройствам телемеханики и вычислительной те НИКИ и может быть использовано в аппаратуре передачи - приема и обработ ки информации в автоматизированных системах управления энергопотреблением промпредприятий, а также в других отраслях народного хозяйства, где требуется высокая достоверность принимаемой информации, и конкретно может быть использовано в комплексе технических средств информационно-измерительной системы учета и контроля энергопотребления энергопотребителей ИИСЭ2. При разработке системы ИИСЭ2 возникла задача передачи информации от счетчиков-датчиков в информационно-вычислительное устройство ,ИВУ) системы по выделенным телефонным линиям связи, при этом расстояние между счетчиками-датчиками и ИВУ может достигать десятков километров, а в линиях связи наблюдаются значительные помехи, искажающие передаваемую информацию и снижающие ее достоверность. Известно устройство, содержащее блок памяти, распределитель импульсов, блок управления, триггер и генератор импульсов 1 1 3Однако данное устройство имеет сложную конструкцию и низкую достоверность, поскольку в нем регистрируется не каждое изменение передаваемой информации, а лишь изменения в определенные промежутки времени. Второе из указанных устройств несколько проще, однако и в нем достоверность получаемой информации незначительна. Известно многоканальное телеизмерительное устройство с уплотнением информации, осуществляющее передачу только тех параметров, которые к момекту передачи отличаются от ранее переданных значений на некоторую, заранее заданную, величину, и содержащее коммутатор датчиков, аналого-циф ровой преобразователь, элемент сравнения, оперативный запоминающий блок программный блок, ключи передачи, блок передачи, канал связи, счетчик числа переданных слов, блок отсутствия информации, элемент ИЛИ и блок запоминания очередного адреса fzjНедостатком данного устройства является наличие обратного канала . связи и соответствующих блоков аппаратуры, с помощью которых осу- , ществляется передача и прием команды на повторение переданной информации в случае фиксации ошибки при ее приеме на приемной стороне, что снижает скорость передачи информации, усложняет конструкцию и увеличивает материальные затраты при практической реализации. Наиболее близким по технической сущности к изобретению является устройство для приема, кодирования и передачи информации, содержащее на передающей стороне генератор, выход которого соединен с входом делителя частоты, формирователь импульсов, формирователь контрольного разряда, элемент Гели, триггер, элементы НЕ и блок выходных усилителей, а на приемной стороне - триггер, дешифратор импульсов, а также блоки памяти, блок опроса, модулятор, регистр совпадения, переключатель 3 Однако известное устройство обладает низкой скоростью передачи информации, не осуществляет автоматической коррекции принятой информации ,при наличии в последней ошибки, а также сложно при практической реализации, что снижает надежность работы всего устройства в целом. Целью изобретения является повышение достоверности, помехозащищенности и быстродействия устройства. Поставленная цель достигается тем VTO на передающей стороне введены преобразователь сигналов, коммутатор буферный регистр, регистр записи и кодирования информации, регистр памяти, формирователь контрольного разряда, управляемый делитель часто ты, элементы И, блок управления, переключатель, элементы ИЛИ, группа элементов ИЛИ, счетчик импульсов, де иифратор.импульсов, формирователь к да, усилитель, блок гальванической развязки, выход преобразователя сиг налов подключен к первому входу ксЯ мутатора, к второму входу которого подключен выход делителя частоты, выход коммутатора подключен к входу формирователя импульсов, выход которого соединен с первым входом буферного регистра, первый выход которого подключен к входу блока управления, второй выход - к первому входу регистра записи и кодирования информации, выход которого соединен с входом формирователя контрольного разряда, выход которого подключен к первому входу, регистра памяти, выход регистра записи и кодирования информации подключен к первому входу первого элемента ИЛИ, выход которого соединен с входом усилителя, Нервый и второй выходы которого подключены соответственно к входам первого и второго блоков гальванической развязки, выходы которых соединены соответственно с первым и вторым входами блока выходных усилителей, выходы которого соединены с линией связи, второй выход делителя частоты подключен соответственно к первым входам управляемого делителя частоты и первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого Подключен к второму входу буферного регистра, выход управляемого делителя частоты подключен соответственно к вторым входам регистра записи и кодирования информации и регистра памяти и, соответственно,X первым входам счетчика импульсов и второго элемента И, выход которого соединен соответственно с вторыми входами счетЧика импульсов, второго элемента ИЛИ и с первым входом переключателя, выход которого подключен соответственно к третьему входу буферного регистра и к первому входу формироваеля кода, выход которого соединен вторым входом первого элемента ИЛИ, выход счетчика импульсов соединен с входом дешифратора импульсов, выход которого подключен к первому входу риггера, выход которого соединен сответственно с третьими входами ре гистра записи и кодирования информации и регистра памяти, выход которого соединен с четвертым входом регистра записи и кодирования информации, второй выход дешифратора импульсов подключен к первому входу третьего элемента ИЛИ, выход которого через элемент НЕ соединен с вторым вхо дом триггера, второй выход которого соединен с вторым входом формирователя кода, третий выход дешифратора импульсов соединен с вторым входом переключателя, четвертый выход дешифратора импульсов соединен с вторым входом второго элемента И, первый выход блока управления подключен соответственно с третьим входом блока выходных усилителей и переключа. теля,.второй выход блока управления соединен с входом группы элеме тов ИЛИ, первый выход которого подключен к второму входу третьего эле мента ИЛИ, второй выход группы элементов ИЛИ под.ключен соответственно к второму входу управляемого делителя частоты и к входу второго элемента НЕ, выход которого соединен с вторым входом первого элемента И, н приемной стороне введен блок согласования, фильтр, блок гальванической развязки, блок сравнения, линей ный усилитель, счетчик импульсов, элемент М, группа элементов И, формирователь стробов, переключатель, второй дешифратор импульсов, буферный регистр, сумматор, распределитель импульсов, блок контроля, груп па элементов ИЛИ и делитель частоты, выход блока согласования через последовательно соединенные фильтр и блок гальванической развязки соединен с входом линейного усилителя, первый и второй выходы которого сое динены соответственно с первым и вторым выходами блока сравнения, выход которого соответственно подключен к первым входам первого дешифратора импульсов, счетчика импульсов и элемента И, выход которого соединен с первым входом первой группы элементов И, выход которого подключенJсоответственно/ к первый входам блока контроля и буферного регистра и к входу группы элементов ИЛИ, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом второго дешифратора импульсов, выход которо го подключен к второму входу буферного регистра, к третьему входу которого подсоединен выход блока конт роля, выход счетчика импульсов подключен к второму входу первого дешифратора импульсов, первый и второ выходы которого подключены соответс венно с первым входом переключателя И с входом триггера, первый выход которого соединен с вторым входом счетчика импульсов, второй выход соответственно с вторым входом переключателя и элемента И, и к первому входу распределителя импульсов, выход которого соединен соответственно с вторым входом блока контроля и с входом формирователя стробов, первый выход которого подключен соответственно к второму входу второго дешифратора импульсов и третьему входу переключателя, второй выход фор. мирователя стробов подключен к второму входу сумматора, третий выход к четвертому входу переключателя, выход которого подключен к первому выходу устройства и к первому входу второй группы элементов И, выход которого подключен к второму выходу устройства, выход буферного регистра соединен с вторым входом второй группы элемента И, второй выход распределителя импульсов подключен к второму входу первой группы элементов И, выход делителя частоты подключен к второму входу распределителя импульсов, первый и второй выходы блока согласования соединены с линией связи. Устройство также содегржит блок гальванической развязки, состоящий из оптрона, резисторов, транзистора, стабилитрона и источника питания, катод фототиристора оптрона соединен с первым выводом первого резистора и катодом стабилитрона, анод которого подключен к базе транзистора, эмиттер которого соединен с первым выводом второго резистора и с выходом блока гальванической развязки, анод фототиристора оптрона соединен с положительным полюсом источника питания и коллектором транзистора, вторые выводы первого и второго резисторов подключены к отрицательному полюсу источника питания. На фиг. 1 представлена блок-схема передающей части устройства; на фиг. 2 - блок-схема приемной части. Устройство содержит преобразователь 1 сигналов, коммутатор 2, формирователь 3 импульсов, буферный регистр 4, регистр 5 записи и кодирования информации, формирователь 6 контрольного разряда, регистр 7 памяти, делитель частоты 8, блок 9 управления, управляемый делитель частоты 1. первый элемент И 11, второй эле79мент ИЛИ 12, генератор 13 импульсов, второй элемент НЕ 14, переключатель 15 группа элементов ИЛИ 16, триггер 17 счетчик 18 импульсов дешифратор 19 импульсов, второй элемент И 20, третий элемент ИЛИ 21, первый элемент НЕ 22, первый элемент ИЛИ 23 предварительный усилитель , блоки 25 и 26 гальванической развязки, блок 27 выходных усилителей, линию связи 28, блок 29 согласования, фильтр 30, блок 31 гал ванической развязки, блок 32 сравне ния, линейный усилитель 33.счетчик ;3 импульсов, первый дешифратор 35 импульсов, триггер 36, элемент И 37 формирователь 38 стробов , переключа тель 39 вторую группу элементов И второй дешифратор 1 импульсов, буферный регистр 42, блок 43 контроля вторую группу элементов И 44, сумматор45 распределитель 46 Импульсов, группу элементов ИЛИ 4 делитель 48 частоты, формирователь 49 кода. Блок 25 содержит оптрон 50, стабилитрон 51 резисторы 52 и 53, транзистор 54 и источник питания(не показан. Преобразователи 1 сигналов представляют собой трехфазные электросметчики, например, типов САЗУ-И687 или СР4У-И689, с частотным выходом, которые радиально, посредством-лини связи, подключены к входам коммутатора 2 и предназначены для выдачи информации о потреблении электроэне гии предприятием. Коммутатор 2 предназначен для ор ганизации режимов работы устройства и согласования линий связи, которыми подключены счетчики-датчики к входам устройства. В состав блока входят субблоки подстройки и индика ции, переключатели и измерительное устройство, например, типа М420б. Блоком задаются или стартстопный ре жим работы, или режим самоконтроля. В первом случае входной является информация, поступающая от счетчиков- датчиков, т.е. устройство работает на передачу, во втором--- устройство вырабатывает сигналы, имитирующие работу счетчиков-датчиков и позволяет ос ществлять подстройку основных блоков и судить о их работоспособности. Измерительное устройство позволяет при согласовании линий связи со входами устройства Уста навливать необходимое значение тока а линиях связи. Субблок индикации позволяет осуществлять визуальный кон троль поступающей на вход устройства информации и состоит из светодиодов, например, типа АЛ1025. При необходимости субблок индикации может быть отключен. Формирователь 3 импульсов состоит из фильтра и триггеров Шмитта и предназначен для формирования прямоугольных импульсов, необходимых для нормального функционирования интегральных схем, например, серии К155 из несинусоидальных колебаний, поступающих из линий связи, а также для защиты информационных входов устройства от помех. Буферный регистр 4 выполняет функции приема и распределения поступаедей информации, а также ее хранения в течение времени обработки, т.е. когда она кодируется-. В состав блока входят регистры сдвига, ключи, триггеры и отдельные логические цепи. Информация на вход блока поступает асинхронно, при этом сигналом для занесения информации в регистр является наличие ее на любом из входов блока. Занесение осуществляется после окончания входного информационного импульса. При появлении информации хотя бы в одной ячейке регистра последний вырабатывает сигналы, поступающие в блок 9 управления, который в cBOfo очередь, переводит устройство в режим передачи. Информация в буферном регистре объединяется в группы по два байта, причем выдача на кодирование осуществляется по байту и каждый байт кодируется отдельно. При передаче каждая группа имеет свой синхроимпульс. Выдача групп информации на кодирование осуществляется последовательно, начиная с младшей/по сигналам перек-. лючателя 15. Переданная на кодирование информация стирается и на ее место может быть записана новая, которая может поступить в течение времени передачи, при этом поступившая информация будет выдаваться на кодирование в следующем цикле пере-, дачи. Регистр 5 записи и кодирования информации выполняет функцию хранения в течение времени кодирова- . ния предназначенной для кодирования информации и является реверсивным. Занесение информации в регистр осу996ществляется параллельно, а выдача последовательно. Формирователь 6 контрольного раз ряда предназначен для повышения достоверности передаваемой информации и осуществляет кодирование последней в модифицированном коде Хэмг, .миига, при этом вырабатываются четыре контрольных разряда согласно выра жениям. К1 РЗ 1 Р5 + Р7 + Р9 + РМ; К2 РЗ Р6 + R7 + Р10 + РП; М Р5 + Рб + Р7 + Р12; К8 Р9 + Р10 + P12i где-знак плюс означает суммирование по модулю два; К1, К2, К и К8 - первый, второй третий и четвертый соответственно контрольные разряды; Р - номера разрядов информации в немодифицированном коде Хэм-мйнга,когда номера разрядов кратные степени 2, т.е. позиции 1 2, , 8, 16 пред назначены для контрольных сим волов. В данном случае передается инфор мация, начиная с младших разрядов, .после чего аналогично следуют контрольные разряды, позволяющие на прие ной стороне определить искажениепе.редаваемой информации,т.е. ошибку, и исправить ее. В состав блока входя элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выполняющие роль «сумматоров по модулю два. Регистр 7 памяти является реверсивным и предназначен для хранения зако дированной .информации. Делитель 8 ча тоты вырабатывает сигналы, которые поступают в коммутатор 2 и предназначены для имитации работы счетчиг ков-датчиков. На вход блока поступает опорная частота, вырабатываемая генератором 13 импульсов. В состав блока входят счетчики и триггеры. Блок 9 управления осуществляет обработку сигналов, поступающих из буферного регистра k при наличии информации, и переключает передающий полукомплект из ждущего режима работы в режим передачи. По сигналу блока 9 управления блок 27 выходных усилителей подключает к выходу устройства линию 28 связи, отключая с ее зажимов нулевой потенциал, который запирал приемный полукомплект, запрещая поступление каких-либо помех на вход последнего при отсутствии передаваемой информации, что повышает надежность функционирования всего устройства в целом. Управляемый делктель 10 частоты функционирует только во время кодирования и передачи информации и предназначен для формирования тактовой частоты. В состав делителя 10 входят счетчики и триггеры.. Элементы 1 |и и 12 ИЛИ предназначены для организации работы буферного регистра 4. Генератор 13 функционирует постоянно и предназначен для формирования стабильной опорной частоты. В состав генератора входят кварцевый задаю-. щий автогенератор и счетчики. Элемент .1 НЕ управляет работой элемента 11 И. Переключатель 15 предназначен для организации режимов работы буферного регистра 4 и состоит из счетчика и дешифратора. Группа 16 элементов ИЛИ согласно сигналам, поступающим от блока 9 управления, осуществляет управление делителем 10 и элементами 14 и 21. Триггер 17 предназначен для отработки сигнала синхроимпульса, а также для организации режимов работы регистра записи и кодирования информации 5 и регистра 7 памяти. Счетчик 18, дешифратор 19, второй элемент И 20, третий элемент ИЛИ 21 , элемент НЕ 22 и формирователь 49 образуют формирователь длительности синхроимпульса. Функционирует формирователь длительности синхроимпульса следующим образом. Как только в буферный регистр 4 поступает информация, блок 9 управления разрешает работу всего передающего полукомплекта и с выхода управляемого делителя 10 частоты начинают поступать импульсы тактовой частоты. Импульсы тактовой частоты .поступают на счетный вход счетчика 18, а также в регистры 5 и 7. Первый же импульс, поступивший в счетчик 18 и расшифрованный дешифратором 19. переводит триггер 17 в состояние логической единицы. При этом триггер 17 разрешает параллельную запись информации в регистрах 5 и 7, т.е. начинается процесс кодирования. Одновременно начинается отсчет длительности синхроимпульса. По сигналу переключателя 15 формирователь 49 кода формирует соответствующий код, который через элемент 23 ИЛИ поступает в усилитель 24 предварительного усиления и; далее, в линию 28 связи. Девятый импульс с выхода счетчика 18 через Qeшифратор 19 и элементы 21 и 22 переводит триггер 17 в исходное состояние. При этом оканчивается формирование синхроимпульса, длительность которого в данном случае равна восьми импульсам тактовой частоты, и регистры 5 и 7 переводятся в режим сдвига. Информация из регистра 7 памяти поступает в регистр 5 записи и кодирования информации, и через элемент 23 ИЛИ -,в усилитель 2.

Выдача информации осуществляется в следующем порядке. Сначала следует байт собственно передаваемой информации, далее конт)ольные символы и служебный такт, который передается отсутствием сигнала. Во время служебного такта, который является по счету тринадцатым, осуществляется анализ принятой информации в приемном полукомплекте на наличие ошибок iи их коррекции.Служебный такт предназначен также для самоконтроля приемного полукомплекта.при наличии сигнала во время служебного такта в приемном комплекте осуществляется стирание принятой информации из буферного регистра 42 и комплект переходит в ждущий режим, таким образом осуществляется защита от сбоев передающего полукомплекта. Кроме того, во время служебного такта в передающем комплекте осуществляется подготовка к занесению в регистр 5 следующей группы из буферного регистра Ц при наличии последней. Тридцать импульсом, поступающим из дешифратора 19, что означает конец передачи информации данной группы, счетчик 18 посредством элемента И 20 устанавливается в исходное, нулевое, состояние, а в регистр 1 посредством элемента ИЛИ 12 разрешается занесени новой порции информации вместо переданной. Если новая информация отсутствует и в других группах.регистра Ц также не было информации, то передающий полукомплект переводится в ждущий режим. В противном случае переключатель 15 разрешает работу со следующей группой информации, и цикл передачи повторяется.

Усилитель 2k осуществляет преобразование сигналов, поступающих с выхода интегральных схем устройства, а также их инвертирование. Прямой и инверсный сигналы поступают в блоки 25 и 2б соответственно. Блоки 2б и 25 гальванической развязки осуществляют гaль8aничecкytэ развязку передающего полукомплекта и линии связи, что повышает помехозащищенность, В состав блоков входят оптрон 50, транзистор 5 стабилитрон 51, резисторы 52 и 53 источник питания (не показан).

Блок 27 выходных усилителей формирует двухполярный сигнал, который поступает в линию связи. Параметры выходных сигналов- блока определяются скоростью передаваемой информации Блок 27 осуществляет также коммутации линии 28 связи, последняя соединяет между собой передающий и приемный ,полукомплекты устройства. Блок 29 согласования осуществляет согласование параметров-линии связи со входом приемного полукомплекта. Фильтр 30 пропускает на вход приемного полукомплекта сигналы, следующие с частотой передаваемой информации, повышая тем самым помехозащищенность устройства. Блок 31 гальванической развязки осуществляет гальваническую развязку линии связи и приемного полукомплекта. Блок 32 сравнения осуществляет обработку двухполярных импульсов поступающей иИ5)ормации и при соответствии положительного и отрицательного импульсов разрешает дальнейшее прохождение информации, осуществляя защиту приемно го полукомплекта от проникновения ложной информации, что повышает надежность устройства в целом.

Линейный усилитель 33 преобразует амплитуду сигналов, поступающих из блока 31, до уровня, необходимого для нормального функционирования логических интегральных схем.

Счетчик 3 первый дешифратор 35 и триггер 36 образуют селектор длительности синхроимпульса, который функционирует следующим образом. Принимаемая информация из блока 32 гравнения поступает на входы счетчика З J дешифратора 35 и элемента 37 И, который исходно находится в закрытом состоянии. Счетчик 3 определяет длительность синхроимпульса путем заполнения его импульсами тактовой частоты. Если длительность синхроимпульса соответствует заданной, в данном случае восьми тактам, то счетчик 3 через первый дешифратор 35 переводит триггер Зб в состояние логической единицы, разрешая тем самым работу элемента 1396 И 37. При этом разрешается дальней шее прохождение информации на дешифровку. Если длительность синхроимпульса- не соответствует заданной, то приемный полукомплект отключается. Дешифратор 35 согласно коду, поступа ющему в течение синхроимпульса, определяет номер передаваемой группы информации и выдает соответствующие сигналы переключателю 39. Селектор длительности синхроимпульса осуществляет также синфазирование передающего и приемного полукомплектов, при этом допускается расхождение длитель ности тактовых импульсов до Q%, Элемент И 37 выполняет функцию ключа, коммутирующего вход приемного полукомплекта. Формирователь 38 осуществляет тактирование отдельных блоков полукомплекта исостоит из счетчиков, дешифраторов и логических элементов. Переключатель 39 определяет принадлежность принятой информации определенной группе и управляет выдачей информации. Группа О эле ментов И предназначена для выдачи . принятой информации на выход устройства. Дешифратор 41 осуществляет оп-ределение номера разряда, в котором произошло искажение информации. Буфарный регистр k2 предназначен для хранения принятой информации до момента ее выдачи на выход устройства а также для исправления возможной ошибки по сигналам дешифратора 41. Блок 43 контроля осуществляет контроль за служебным тактом. При его отличии от заданного принятая информация стирается как ложная. Группа 44 элементов И осуществляет распределение поступающей информации выделение информационных и контрольных разрядов. Сумматор 45 по модулю два накапливающего типа предназначен для обработки поступающей информации с целью обнаружения номера возможного искаженного разряда. Сумматор 45 функционирует согласно выражениям1 Р1 + Р2 + Р4 + Р5 + Р7 + РЭ; 2 Р1 + РЗ + Р4 + Р6.+ Р7 + Р10; 3 Р2 + РЗ + Р4 + Р8 + РП; 4 Р5 + Рб + Р8 + Р12, где знак плюс означает суммирование по модулю два 1... 4 - номера проверок. Из полученных проверок дешифратор 41 определяет код искаженного разряда в виде 4321. Сумматор 45 состоит из регистра и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Распределитель 46 импульсов осуществляет синхронную работу блоков приемного полукомплекта и состоит из реверсивного регистра сдвига. Группа 47 элементов ИЛИ предназначена для организации ввода информации в сумматор 45. Делитель 48 осуществляет синхронизацию приемного полукомплекта и абонентов принятой информации . Формирователь 49 кода формирует синхроимпульс в соответствии с номером передаваемой группы информации. В состав блока входят счетчик и дешифратор. Принцип действия передающего и приемного полукомплектов устройства заключается в следующем. Цикл передачи. Генератор 13 постоянно вырабатывает импульсы опорной частоты, которые поступают на вход делителя 8 частоты. С первого выхода делителя 8 частоты импульсы поступают в блок коммутации, а со второго - на соответствующие входы управляемого делителя 10 частоты и элемента 11 И. При этом, если от преобразователей 1 сигналов в буферный регистр 4не поступило ни одного информационного сигнала, т.е. в буферном регистре 4 нет информации, то блок 9 управления, в соответствии с сигналами буферного регистра 4, запрещает работу блока 27 выходных усилителей и переключателя 13, а также вырабатывает сигналы, поступающие на входы группы 16 элементов ИДИ. Блок 27 вЬ1ходных усилителей отключает свои выходы от линии 28 связи, а к обоим входам линии 28 связи подключает нулевой потенциал, запрещая тем самым работу приемного полукомплекта. При этом исключается проникновение какого-либо рода помех из линии 28 связи в приемный полукомплект, что повышает помехозащищенность. Группа 16 элементов ИЛИ вырабатывает импульсы, которые через элемент 21 ИЛИ и элемент 22 НЕ поступают на вход Установка в О триггера 17, запрещая тем самым его работу, а также запрещает работу управляемого делителя 10 частоты, а через элемент 14 НЕ разрешает работу элемента 11 И. При этом импульсы с выхода делителя 8 через элемент 11 И и элемент 12 ИЛИ поступают в буферный регистр k, где ими осуществляется опрос ячеек регистра на наличие информации. Как только хотя бы в одной из яче ек 6уфе{)ногр регистра Ц появится информация, блок 9 управления переводи устройство в режим передачи. При это блок 27 выходных усилителей подключает к своим выходам линию 28 связи, разрешается работа переключателя 15 групп, а группа 16 элементов ИЛИ посредством элементов 21 ИЛИ и 22 НЕ разрешает работу триггера 17 и посредством элемента И НЕ запрещает ра боту элемента 11 И. Одновременно rpy па 16 элементов ИЛИ разрешает работу делителя 10. В буферный регист{ k прекращается поступление импульсов опроса, а тактовые импульсы с выхода управляемого делителя 10 начинают поступатБ в регистры 5 и 7, а также на входы счетчика 18 и элемента . 20 И. По сигналу переключателя 15 групп с буферного регистра k разрешается выдача первого байта первой группы информации на кодирование. Первый же тактовый импульс, поступивший в счетчик 18 через дешифратор 19 устанавливает триггер17 в состояние логической единицы, при этом регистры 5 и 7 переводятся в режим параллельного занесения информации. Одновременно начинается от работка синхроимпульса: сигнал со второго выхода триггера 17 разрешает работу формирователя Э кода. По сиг налу переключателя 15 формирователь кода вырабатывает соответствующий код, который с выходом блока через элемент 23 ИЛИ поступает в усилитель 2k и, далее, через блоки 25 и 26, а также блок 27 выходных усилителей, в линию 28 связи. Первым же тактовым импульсом, поступившим с выхода делителя 10; информация с выходов буферного регистра k параллель но заносится в регистр 5 с выходов же регистра 5 информация через формирователь 6 параллельно заносится в регистр 7. Таким образом, в регистре 5 окажется первый байт первой группы подлежащей передаче ин,формации, а в регистре 7 - контрольные разряды представляющие закодированную модифицированным кодом Хэммйнга информацию первого байта первой группы. Следующим тактовым импульсом анйлогично заносится и .кодируется второй байт первой груп9816 пы информации. Последующие же тактовые импульсы лишь подтверждают занесение информации из буферного регистра Ц в регистр 5 и, далее, из регистра 5 в регистр 7. Одновременно счетчик 18 осуществляет подсчет тактовых импульсов, в линию 28 связи поступает синхронно каждому тактовому импульсу соответствующий разряд кода группы. Девятый тактовый импульс, поступивший в счетчик 18, через дешифратор 19, элементы 21 ИЛИ и 22 НЕ, переводит триггер 17 в исходное состояние. При этом запрещается работа формирователя 49, оканчивается синхроимпульс, а регистры 5 и 7 переключаются в режим сдвига. Следующими тактовыми импульсами начинается последовательная выдача информации в линию 28 связи, которая осуществляется следующим образом. В данном случае регистры 5 и 7 образуют регистр сдвига, состоящий из двух последовательно включенных регистров. Контрольные разряды последовательно из регистра 7 кода поступают на вход регистра 5, с выхода регистра 5 через элемент 23 ИЛИ - в усилитель 2 и, далее, как описано выше. После сиихроимпульса передается первый байт информации первой группы, затем соответствующие ему контрольные разряды, далее следует служебный такт, который не несет информации какттаковой и в течение которого в- приемном полукомплекте осуществляется анализ Принятой информации на наличие ошибк 1, необходимости, исправление последней, а в передающем комплекте переключатель 15 подготавливает к занесению в регистр 5 следующей группы из буферного регистра 4 при наличии последней, а также разрешает формирователю 49 сформировать код следующей группы. Кроме того, в приемном полукомплекте служебный такт анализируется, при отличии его от заданного принятая информация счита ется ложной и стирается. После служебного такта передается второй байт информации с соответствующими контрольными разрядами и следующий служебный такт. Таким образом, цикл передачи одной группы осуществляется в течение 34-; тактовых импульсов, 35-ым тактовым импульсом счетчик 18; устанавливается в исходное, нулевое состояние, переключатель 15 переводится в состояние, соответствующее 1796 выдаче второй группы информации, одновременно тактовый импульс через элемент 20 И и элемент 12 ИЛИ поступает в буферный регистр k, где осуществляет последовательный опрос ячеек оставшихся, не переданных, групп информации. При отсутствии информации блок 9 управления переводит устройство в ждущий, ранее опи санный, режим. Если в буферном регистре 4 была информация в непереданных группах, то описанный процесс передачи повторяется. При этом, например, если во второй группе инфор мации не окажется, то опрашивается и передается третья группа и так да лее, вплоть до последней группы информации. Таким образом, формат цик ла передачи определяется наличием информации в определенных группах. отличие от последовательного опроса и передачи всех групп информации по добный режим сокращает время переда чи и позволяет использовать линию связи с большей нагрузкой.. Выходные блоки передающего комп лекта функционируют следующим образом. С выхода элемента 23 ИЛИ ин-формация поступает на вход усилителя 2k, который осуществляет разделение входного с.игнала на прямой и инверсный, а также преобразует амплитуду сигналов информации до ур ня, необходимого для нормального функционирования блоков 25 и 2б, на входы которых соответственно поступают прямой и инверсный информацион ные сигналы. Блоки гальванической развязки осуществляют гальваническую развязку передающего полукомпле та и линии 28 связи, повышая помехозащищенность устройства. С выходов оптронных блоков информация по.ступает в блок 27 выходных усилите лей, далее в линию 28 связи. Блок 27 выходных усилителей доводит ампл туду информационных сигналов до определенного уровня, определяемого скоростью передаваемой информации. Например, при скорости передачи 200 Бод амплитуда сигнала на входе линии связи 28 должна соответствовать 10 В. В линию 28 связи поступает двухполярный сигнал: прямым ин формационным сигналом соответствует положительный уровень, а инверсным. отрицательный. Блок 27 выходных уси лителей коммутирует также линию 28 связи. Цикл приема информации заключается в следующем. Посредством блока 29 согласования осуществляется согласование параметров линии 28 связи со входом приемного полукомплекта. Сигналы с линии 28 связи через блок 29 согласования поступают на вход фильтра 30, который пропускает лишь сигналы, следующие с частотой передаваемой информации, сигналы с другими частотами фильтром 30 демпфируются. Таким образом, повышается помехозащищенность устройств.а. С выхода фильтра 30 информация поступает на вход блока 31, который осуществляет гальваническую развязку линии связи с приемным.полукомплектом и, далее, на вход линейного усилителя 33, выходы которого соединены с входами блока 32 сравнения. С выходов усилителя 33 поступают прямой и инверсный информационные сигналы, соответствующие положительным и отрицательным сигналам, поступающим из линии связи. Элемент ИЛИ 23 преобразует амплитуду информационных сигналов до уровня, необходимого для нормального функционирова1:(ия интегральных схем. Блок 32 сравнения осуществляет анализ прямого и инверсного информационных сигналов, длительность каторых должна быть равна. В противном случае блок 32 запрещает дальнейшее прохождение информации. С выхода блока 32 признаков информация поступает на входы счетчика 3, первого дешифратора 35 и элемент И 37, работа которого запрещена триггером Зб. Счетчик 3 определяет длительность синхроимпульса, а дешифратор 35 определяет код принимаемой группы информации. После окончания синхроимпульса счетчик 3 выдает сигнал дешифратору 35, который, в свою очередь, переводит триггер 36 s состояние логической единицы и выдает сигналы .переключателю 39.. Триггер Зб запрещает дальнейшую работу счетчика , разрешает работу элемента 37 И и распределителя 46 импульсоа, а также разрешает прием переключателю 39 сигналов дешифратора 35- С выхода эле мента 37 И информация поступает на ВХОДЫ группы kk элементов И, работа которой синхронизирована распределителем 46 импульсоа. С выходор группы kk элементов И информация поступает в буферь ый регистр 2 и через группу 7 элементов ИЛИ - на входы сумматора Ц по модулю два накапливающего типа. Таким образом, в буферном регистре будет записан байт принимаемой информации, а в сум маторе сумма по модулю два соответствующих разрядов принимаемой информации. Дешифратор 1 осуществляет расшифровку кода, поступающего с выхода сумматора 45. Если информация не искажена, то дешифратор 1 не вырабатывает никаких сигналов В противном случае в течение служебного такта, который определяется рас пределителеМ 6 импульсов, формирователь 38 стробов выдает сигнал, сог ласно которому осуществляется коррекция информации в буферном регистре k2. Кроме того, формирователь 38 осуществляет синхронную работу всего приемного комплекта. Блок l3 по сигналу распределителя 46 импульсов анализирует состав служебного такта Если .-служебный такт отличается от заданного, то информация из буферного регистра 42 стирается, в противном случае переключатель 39 разрешает работу группы 4О элементов И и информация с буферного регистра 42 поступает к абоненту. Переключатель 33 выдает также номер принимаемой группы информации. Аналогично осуществляется прием и выдача вто рого байта информации данной группы Для синхронной работы абонента и приемного полукомплекта последние синхронизируются посредством делител .48, который выдает сигналь распределителю 46 импульсов. В режиме самоконтроля на вход ком мутатора 2 поступают импульсы с выхо да делителя 8 частоты. При этом можно имитировать работу всех каналов одновременно или в любом их сочетании. В данном случае известно, какая информация должна появиться на выходе приемного полукомплекта. Таким образом, .можно контролировать функционирование работы всего устройства .в целом. Экономический эффект, получаемый .при использовании предложенного устpoйcтвa заключается в том, что повышается достоверность передаваемой информации, которая в данном случае является коммерческой и выражается в денежном измерении; повышается помехозащищенность устройства, автоматизирован процесс исправления воз920 можного искажения информации, а также уменьшается время загрузки линии связи вследствие переменного формата цикла сообщений. Формула изобретения 1.Устройство для сбора,кодирования, передачи и приема информации с исправлением ошибок, содержащее на передающей стороне генератор, выход которого соединен с входом делителя частоты, формирователь импульсов, элемент ИЛИ, триггер, элементы НЕ и блок выходных усилителей,а на приемной стороне - триггер, дешифратор импульсов/линию связи, отличающееся тем, что, с целью повышения достоверности, помехозащищенности и быстродействия устройства, в него введены на передающей стороне преобразователь сигналов, коммутатор буферный регистр, регистр записи и кодирования.информации, регистр памяти, формирователь контрольного разряда, управляемый делитель частоты, элементы И, блок управления, переключатель, элементы ИЛИ, группа элементов ИЛИ, счетчик импульсов, дешифратор импульсов, формирователь кода, усилитель, блок гальванической развязки, выход преобразователя сигналов подключен к первому входу коммутатора, к второму входу которого подключен выход делителя частоты, выход коммутатора подключен к входу формирователя импульсов, выход которого соединен с первым входом буферного регистра, первый выход которого подключен к входу блока управления, второй выход - к первому входу регистра записи и кодирования информации, выход которого соединен с ВХОДОМ1 формирователя контрольного разряда, выход которого подключён к первому входу регистра памяти, выход регистра записи и кодирования информации подключен к первому входу первого элемента ИЛИ, выход которого соединен с входом усилителя, первый и второй выходы которого подключены соответственно к входам первого и второго блоков гальванической развязки, выходы которых соединены соответственно с первым и вторым входами блока выходных усилителей, выхоы которого соединены с линией связи, второй выход делителя частоты подключен соответственно к первым входам управляемого делителя частоты и первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход .которого подключен к второму входу буферного регистра, выход управляемого делителя частоты подключен соответственно к вторым входам регистра записи и кодирования информации и регистра па мяти и, соответственно к первым входам счетчика импульсов и второго эле мента И, выход которого соединен, со ответственно, с вторыми входами счет чика импульсов, второго элемента ИЛИ и с первым входом переключателя, выход которого подключен соответстЕ}енно к третьему входу буферного регист ра и к Первому входу формирователя кода, выход которого соединен с вторым входом первого элемента ИЛИ, выход счетчика импульсов соединен с входом дешифратора импульсов, выход которого подключен к первому входу триггера, выход которого соединен со ответственно с третьими входами регистра записи и кодирования информации и регистра памяти, выход которого соединен с четвертым входом регистра записи и кодирования информации , второй выход дешифратора импульсов подключен к первому входу третьего элемента ИЛИ, выход которого через элемент НЕ соединен с вторым входом триггера, второй выход которого соединен с вторым входом формирователя кода, третий выход дешифратора импульсов соединен с вто рым входом переключателя, четвертый выход дешифратора импульсов соединен с вторым входом второго элемента И, первый вывод блока управления подключен соответственно к третьим входам блока выходных усилителей и переключателя, второй выход блока управления соединен с входом группы элементов ИЛИ, первый выход которого подключен к второму входу третьего элемента ИЛИ, второй выход группы элементов ИЛИ подключен соответственно к второму входу управляемого делителя частоты и к входу второго элеме.нта НЕ, выход которого соединен с вторым входом первого элемента И, на приемной стороне введены блок согласования, фильтр, блок гальванической развязки, блок сравнения линейный усилитель, счетчик импульсов, элемент И, группа элементов И, 96 22 формирователь стробов, переключатель , второй дешифратор импульсов, буферный регистр, сумматор, распределитель Импульсов, блок контроля, группа элементов ИЛИ и делитель час- . тоты, выход блока согласования через последовательно соединенные фильтр и блок гальванической развязки соединен с вторьии входом линейного усилителя, первый и второй выходы которого соединены соответственно с первым и вторым выходами блока сравнения, выход которого соответственно подключен к первым входам первого дешифратора импульсов и счетчиka :импульсов и элемента И, выход которого соединен с первым входом первой группы элементов И, выход которого подключен,соответственно, к первым входам блока контроля и буферного регистра и к входу.группы элементов ИЛИ, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом второго дешифратора импульсов, выход которого подключен к второму входу буферного регистра, к третьему входу которого подсоединен выход блока контроля, выход счетчика импульсов подключен к второму входу первого дешифратора импульсов, первый и второй выхоДы которого соединены соответственно с первым входом переключателя и с входом триггера, первый выход которого соединен с вторым входом счетчика импульсов, второй выход - соответственно с вторым входом переклю-чателя и элемента И и с первым входом распределителя импульсов, выход которого соединен соответственно с вторым входом блока контроля и с вхо- дом формирователя стробов, первый выход которого пoдключeн соответственно, к второму входу дешифратора импульсов и третьему входу переключателя, второй выход формирователя стробов подключен к второму входу сумматора, третий выход - к четвертому входу переключателя, выход которого подключен к первому выходу устройства и к первому входу второй группы элементов И, выход которого подключен к второму выходу устройства, выход буферного регистра соединен с вторым входом второй группы элемента И,второй выход распределителя им пульсов подключен к второму входу первой группы элементов И, выход делителя частоты подключен к второму

входу распределителя иипульсов, первый и второй выходы блока согласования соединены с линией связи.

тиристора оптрона соединен с положительным полюсом источника питания и коллектором транзистора, вторые выводы первого и второго резисторов подключены к отрицательному полюсу источника питания.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-23—Публикация

1980-10-13—Подача