блока кодирования адреса, третий вход которого подключен к третьему выходу второго блока выделения существенных отсчетов, четвертый вход блока кодирования адреса подключен к второму выходу синхронизатора, первый выход блока кодирования адреса подключен к П1Ервому входу блока оперативной памяти, второй выход блока кодирования адреса подключен к первому входу третьего элемента ИЛИ и второму входу блока оперативной памяти, выход которого подключен к вто- рому входу блока регистров и второму входу третьего элемента ИЛИ, выход третьего элемента ШШ подключен к второму входу блока буферной памяти,

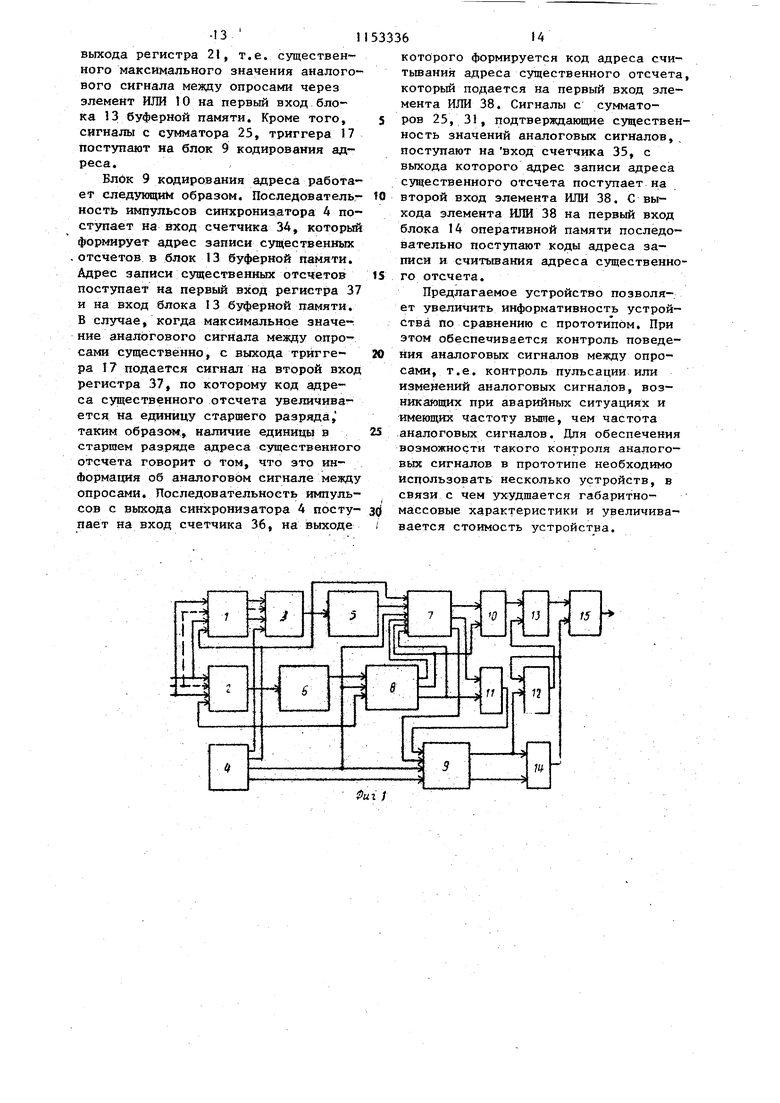

2, Устройство по п. 1, отличающееся тем, что первый блок вьщеления существенных отсчетов содержит элемент памяти, регистры, счетчик, сумматоры и элемент И, выход первого регистра подключен к первому входу первого сумматора я первому входу элемента И, выход которого подключен к первому входу элемента памяти, выход которого подключен через второй регистр к второму входу первого сумматора, выход которого подключен к первому входу второго сумматора, выход которого подключен к второму входу элемента И и первому входу счетчика, выход счетчика подключен к второму входу второго сумматора, вход первого регистра, второй вход элемента памяти и второй вход счетчика являются соотвгетствён- но первым, вторым и третьим входами первого блока вьщеления существенных отсчетов, выход второго регистра, выход элемента И и выход второго

сумматора являются.соответственно первым, вторым и третьим выходами первого блока вьщеления существенных отсчетов.

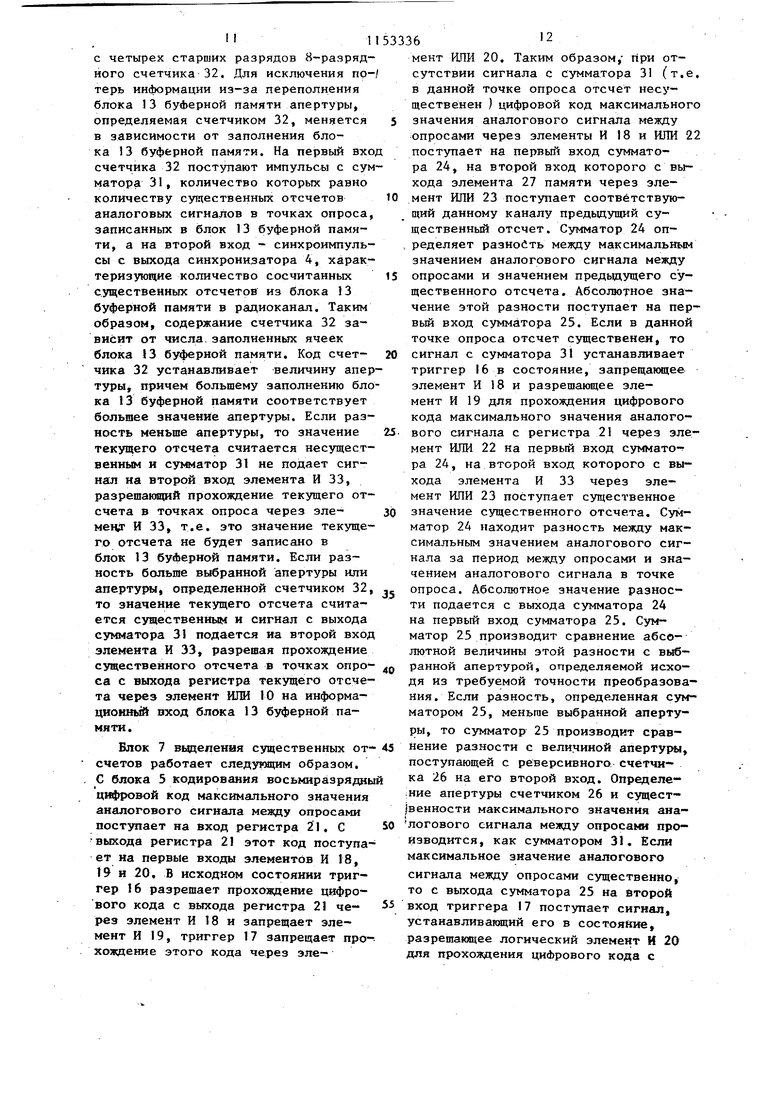

3, Устройство по п. 1, отличающееся тем, что второй блок выделения существенных отсчетов содержит регистр, сумматоры, триггеры, элементы И и элементы ИЛИ, выход регистра подключен к первым входам первого, второго и третьего элементов И, вторые входы первого и второго элементов И подключены соответственно к первому и второму выходам первого триггера, выходы первого и второго элементов И через первый элемент ИЛИ подключены к первому входу первого сумматора, второй вход которого подключен к выходу второго элемента ШШ, выход первого сумматор подключен к первому входу второго сумматора, выход которого подключен к первому входу второго триггера и первому входу счетчика, выход счетчика подключен к второму входу второго сумматора, выход второго триггера подключен к второму входу третьего элемента И, первые объединенные входы первого и второто триггеров, вход регистра, второй вход первого триггера, первый и второй входы второго элемента ИЛИ и второй вход счетчика являются соответственно с первого по тестой входами второго блока выделения существенных отсчетов, выход третьего элемента И, выход второго сумматора и выход второго триггера являются соответственно , вторым и третьим выходами второго блока выделения существенных отсчетов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Передающее многоканальное телеметрическое устройство | 1977 |

|

SU690523A1 |

| Устройство для преобразования Фурье | 1984 |

|

SU1195358A1 |

| Устройство для передачи телеметрической информации | 1981 |

|

SU1005147A2 |

| Устройство для уплотнения многоканальных сообщений с кодоимпульсной модуляцией | 1986 |

|

SU1365106A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Многоканальная телеизмерительная система | 1986 |

|

SU1310870A1 |

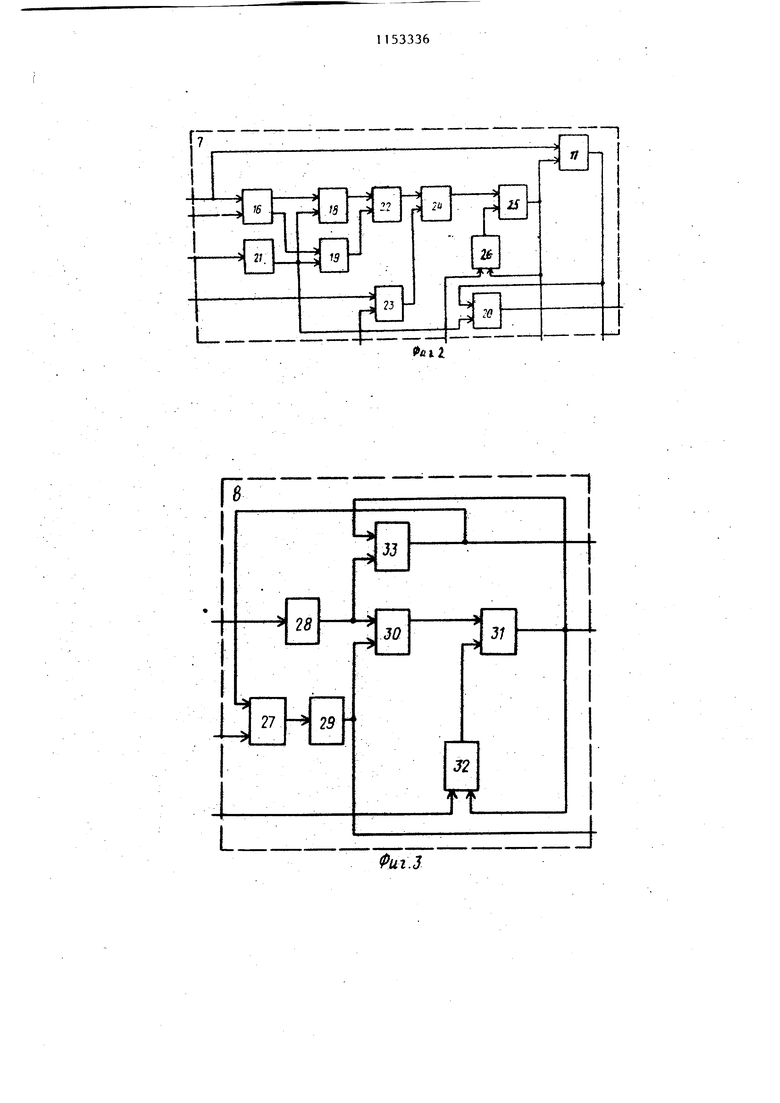

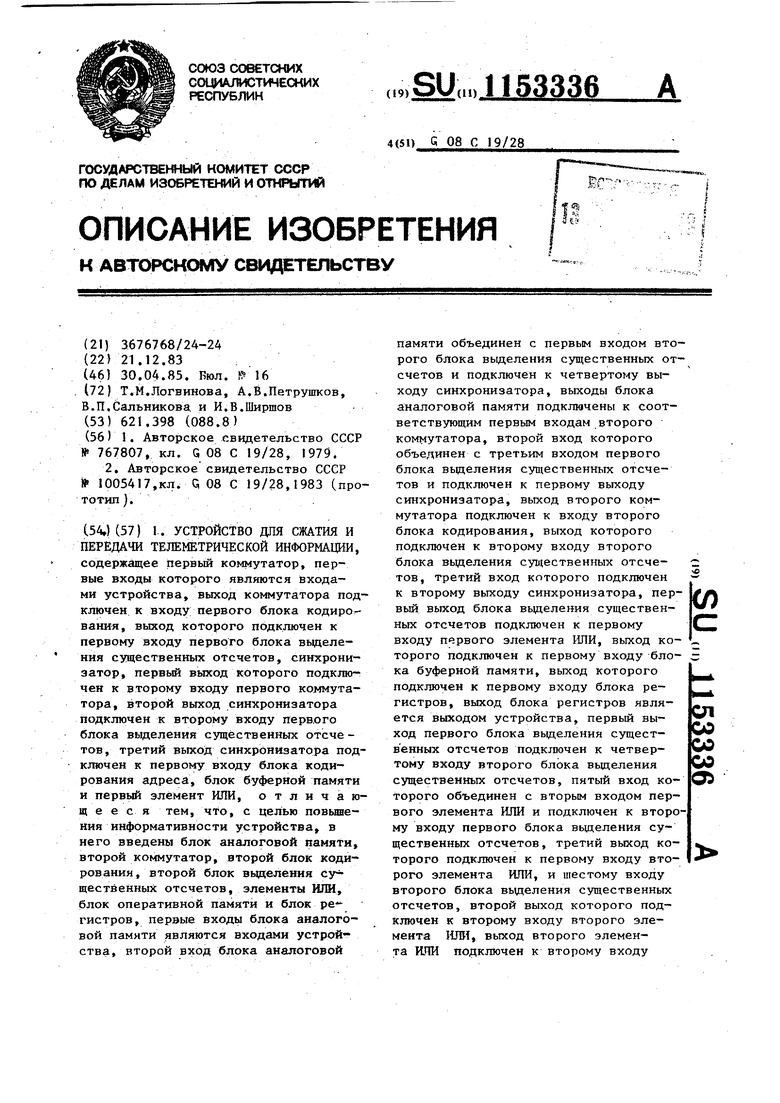

1.. УСТРОЙСТВО ДЛЯ СЖАТИЯ И ПЕРЕДАЧИ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ, содержащее первый коммутатор, первые входы которого являются входами устройства, выход коммутатора подключен к входу первого блока кодирования, выход которого подключен к первому входу первого блока вьвделения существенных отсчетов, синхронизатор, первый выход которого подключен к второму ВХОДУ первого коммутатора, второй выход синхронизатора подключен к второму входу первого блока вьщеления существенных отсче тов, третий выход синхронизатора подключен к первому входу блока кодирования адреса, блок буферной памяти и первый элемент ИЛИ, отличающееся тем, что, с целью повьшения информативности устройства, в него введены блок аналоговой памяти, второй коммутатор, второй блок кодирования , второй блок вьщеления су щественных отсчетов, элементы ИЛИ, блок оперативной памяти и блок ре гистров, первые входы блока аналоговой памяти являются входами устройства, второй вход блока аналоговой памяти объединен с первым входом второго блока вьщеления существенных отсчетов и подключен к четвертому выходу синхронизатора, выходы блока аналоговой памяти подключены к соответствующим первым входам второго коммутатора, второй вход которого объединен с третьим входом первого блока вьщеления существенных отсчетов и подключен к первому выходу синхронизатора, выход второго коммутатора подключен к входу второго блока кодирования, выход которого подключен к второму входу второго блока выделения существенных отсчетов, третий вход которого подключен «Л к второму вьгходу синхронизатора, первый выход блока вьщеления существенных отсчетов подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому входу блока буферной памяти, выход которого подключен к первому входу блока регистров, выход блока регистров являсд ется выходом устройства, первый выСАЭ СО ОО О) ход первого блока выделения существенных отсчетов пoдкJroчeн к четвертому входу второго блока вьщеления существенных отсчетов, пятый вход которого объединен с вторым входом первого элемента ИЛИ и подключен к второму входу первого блока вьщеления существенных отсчетов, третий выход которого подключен к первому входу второго элемента ИЛИ, и шестому входу второго блока вьщеления существенных отсчетов, второй выход которого подключен к второму входу второго элемента ИЛИ, выход второго элемента ИЛИ подключен к второму входу

1

Изобретение относится к информационно-измерительной технике и может найти применение в устройствах предназначенных для сжатия и передачи телеметрической информации

Известно устройство для сжатия аналоговых сигналов, содержащее датчики, коммутатора, операционный усилитель, ключевой элемент, блок срав-гнения, справочный запоминающий блок, бйок хронирования и управления, коммутируемый цифроаналоговый преобразователь, буферный запоминающий блок, формирователь кода выборки Cl.

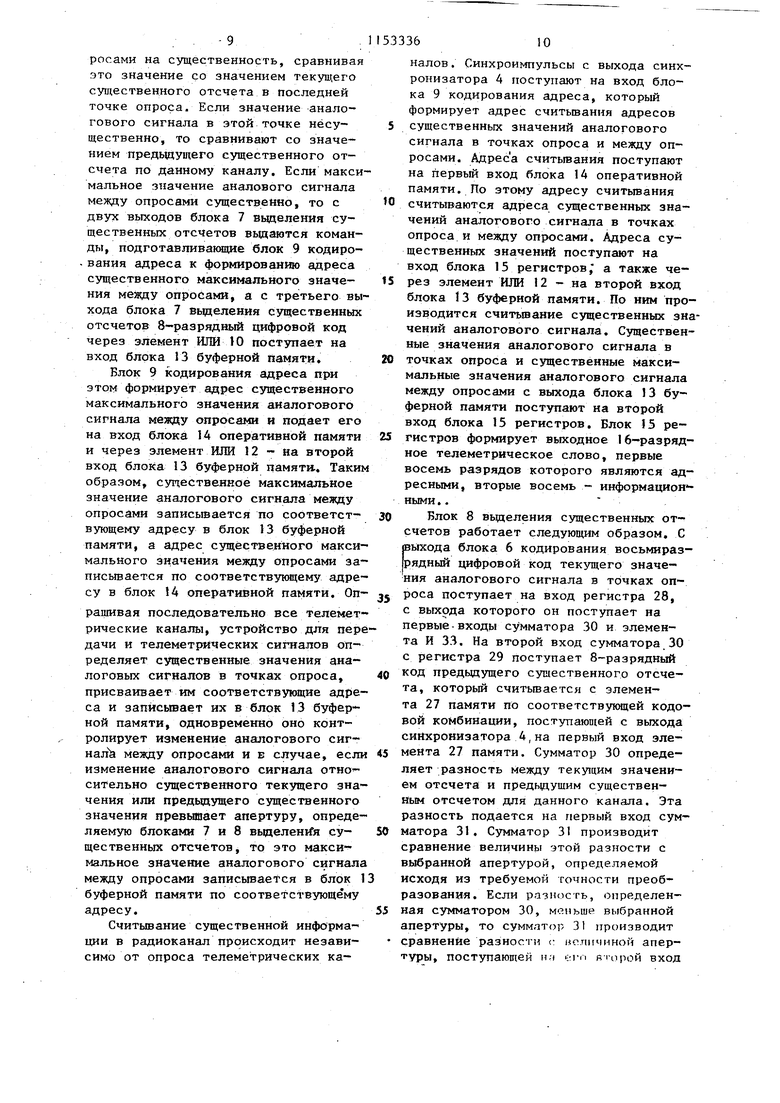

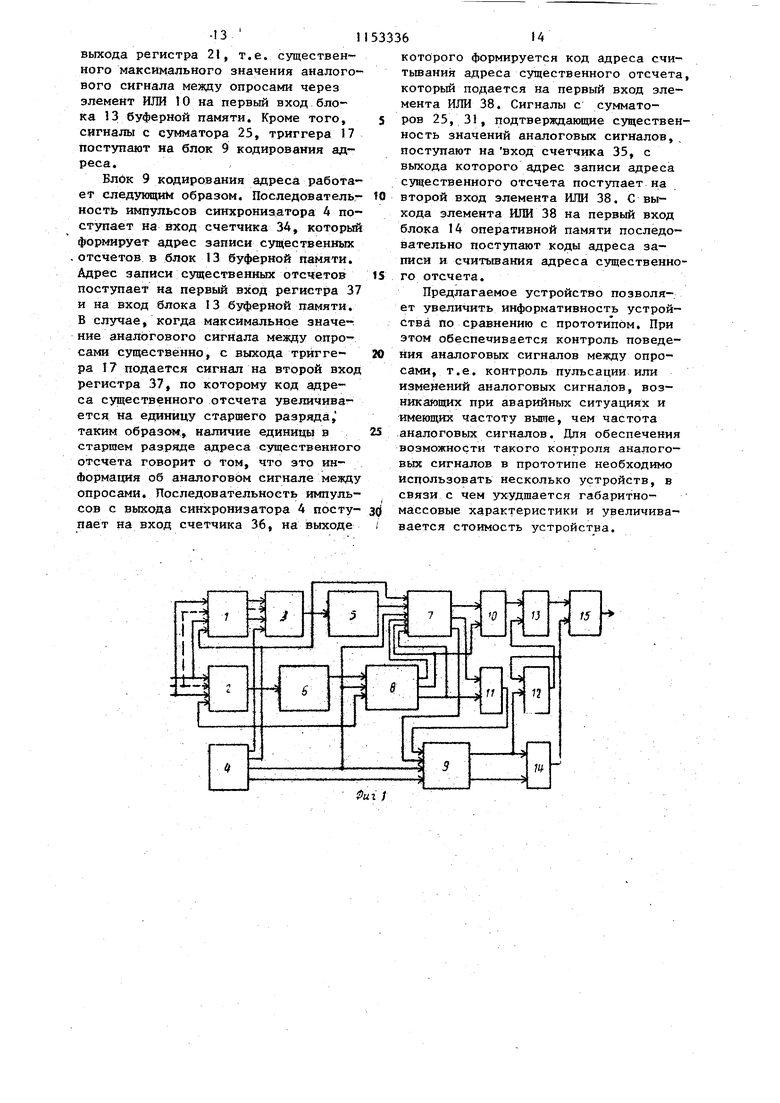

Недостатками известного устройст; ва являются неизменная величина апертуры, независимая от заполнения БЗУ и величины входного сигнала, что мо3жет привести к патере части информации, и низкая информативность устройства. Наиболее близким к предлагаемому по технической сущности является уст ройство, для передачи телеметрической ин(Ьормации, содержащее коммутатор ка налов, входы которого являются вхо дами устройства, выход подключен через блок кодирования измерительной информации к входу многоканального блока памяти и полных кодов сигналов и первому входу анализатора сигналов выход которого соединен с первым вхо дом блока памяти кодов приращений, выход которого подключен к второму входу блока сравнения кодов приращений, выход которого соединен с первом входом третьего элемента И и вхо дом элемента НЕ, выход элемента НЕ подклиочен к второму входу четвертого элемента И, первый вход которого сое дШ{вн с вторым входом третьего элемента И и вторым выходом синхронизатора,пе1)вьй выход синхронизатора соединен с первым входом буферного запоминающего блока, выход которого яв ляется выходом устройства, третий и четвертый выходы синхронизатора подк вочены соответственно к синхронизируюацш входам коммутатора каналов и многоканальных блоков памяти полных кодов сигнала и кодов приращений, пя тьА ВЕЛХод синхронизатора соеди11ен с первьм входом блокакодирования адре са каналов, второй вход которого сое динен с выходом второго элемента И, выход блока кодирования адреса каналов подключен к четвертому входу буферного запоминакяцего блока, к второму и третьему входам которого подключены соответственно выход блока кодирования времени и выход первого элемента И, шестой выход синхронизатора соединен с входом блока кодирования времени и вторым входом элемен та ИЛИ,, первый вход которого соединен с выходом элемента задержки, а выход подключен к установочному входу триггера, информационйьй вход которого соединен с выходом четвертого элемента И, вход элемента задержки соединен, с выходом третьего элемента И и вторыми входами первото и второго элементов И, к первому входу первого элемента И подключен второй вход анализатора сигналов и выход, блока памяти полных кодов сигнала, 36 первый вход второго элемента И соединен с выходом триггера. Анализатор сигналов, блок памяти полных кодов сигналов, блок сравнения кодов приращений, многоканальный блок памяти кодов приращений по существу представляют собой узел вьщеления существенных отсчетов С23. Недостатком описанного устройства является отсутствие возможности контроля поведения сигнала между соседними существенными отсчетами, т.е. низкая информативность устройства. Цель изобретения - повьтение ин- формативности устройства. Поставленная цель достигается тем, что в устройство, содержащее первьй коммутатора, первые выходы которого являются входами устройства, выход коммутатора подключен к входу первого блока кодирования, выход которого подключен к первому входу первого блока вьщеления сут ественных отсчетов, синхронизатор, первый вы- ход которого подключен к второму входу первого коммутатора, второй выход синхронизатора подключен к второму входу первого блока выделения существенных отсчетов, третий вь1ход синхронизатора подключен к первому входу блока кодирования адреса, блок буферной памяти и первый элемент ИЛИ, введены блок аналоговой памяти, второй коммутатор, второй блок кодиро- вания, второй блок вьщеления существенных отсчетов, элементы -ИЛИ, блок оперативной памяти и блок регистров, первые входы блока аналоговой памяти являются входами устройства, второй вход блока аналоговой памяти объединен с первым входом второго блока выделения существенных отсчетов и подключен к четвертому выходу синхронизатора, выходы блока аналоговой памяти подключены к соответствующим первьЕМ входам второго коммутатора, второй вход которого объединен с третьим входом первого блока выделения существенных отсчетов и подключен к первому выходу синхронизатора, выход второго коммутатора подключен к входу второго блока кодирования, выход которого подключен к второму входу второго блока выделения существенных отсчетов, третий вход которого подключен к второму выходу синхронизатора, первый выход блока вьщеления существенных отсчетов подключей к первому входу первого элемента ИЛИ, выход которого подключен к первому входу блока буферной памяти, выход которого подключен к первому входу блока регистров, выход блоКЗ регистров является выходом устройства, первый выход первого блока вьщеления сзш|ест8енных отсчетов подключен к четвертому входу второго блока вьщеления существенных отсчетов, пятый вход которого объединен с вторым входом первого элемента ИЛИ и подключен к второму входу первого блока выделения существенных отсчетов, третий выход которого подключен к первому входу второго элемента ШШ и шестому входу второго блока вьщеления существенных отсчетов, второй выход которого подключен к второму входу второго элемента ИЛИ, выход второго элемента ИЛИ подключен к второму входу блока кодирования адреса, третий вход которого подключен к третьему выходу второго блока вьзделения существенных отсчетов, четверть вход блока кодирования адреса подключен к второму выходу синхронизатора, первый выход блока кодирования адреса подключен к первому входу блока оперативной памяти, второй выход блока кодирования адреса подключен к первому входу третьего элемента ИЛИ и второму входу блока оперативной памяти, выход которого подключен к второму входу блока регистров и второму вхо,цу третьего элемента ИЛИ, вькод третьего элемента ШШ подключен к второму входу блока буферной памяти. Первый блок вьвделения существенных отсчетов содержит элемент памяти регистры, счетчик, сумматоры и элемент И, выход первого регистра подключен к первому входу первого сумматора и первому входу элемента И, вькод которого подключен к первому входу элемента памяти, выход которого подключен через второй регистр к второму входу первого сумматора, выход которого подключен к первому вхо ду второго сумматора, выход которого подключен к второму входу элемента И и первому входу счетчика, выход счет чика подключен к второму входу второго сумматора вход первого регист ра, второй вход элемента паМятии Вто рой вход счетчика являются соответственно первым, вторым и третьим вхо дами первого блока вьаделения существенных отсчетов, выход второго регистра, выход элемента И и выход второго сумматора являются соответственно первым, вторым и третьим вькодами первого блока вьщеления существенных отсчетов. Кроме того, второй блок вьщеления существенных отсчетов содержит регистр, сумматоры, триггеры, элементы И и элементы ИЛИ, выход регистра подключен к первым входам первого, второго и третьего элементов И, вторые входы первопо и второго элементов И подюБочены соответственно к первому и второму выходам первого триггера, выхода первого и второго элементов И через первый элемент ИЛИ подключены к первому входу первого сумматора, второй вход которого подключен к выходу второго элемента ИЛИ, выход первого сумматора подключен к первому входу второго сумматора, выход которого подключен к первому входу второго триггера и первому входу счетчика, выход счетчика подключен к второму входу второго сумматора, выход второго триггера подключен к второму входу третьего элемента И, первые объединенные входы первого и второго триггеров, вход регистра, второй вход первого триггера, пер-вый и второй входы второго элемента ИЛИ и второй вход счетчика являются соответственно с первого по шестой входами второго блока выделения существенных отсчетов, выход третьего элемента И, выход второго сумматора и выход второго триггера являются соответственно первьв, вторым и третьим .выходами второго блока вьщеления существенных отсчетов. На фиг;1 предс- авлена структурная схема устройства на фиг.2 структур- ная схема второго блока вьщеления существенных отс.четов; на фиг.З - структурная схема первого блока вьщеления существенных отсчетовJ на фиг.4 - структурная схема блока кодирования адреса-, на фиг.5 - временные диаграммы а) сигнала на входе устройства, б ) иллюстрация работы устройства-прототипа, в ) иллюстрация работы предлагаемого устройства, Устройство содержит блок 1 аналоговой памяти, коммутаторы 2 и 3, синхронизатор 4, блок 5 и 6 кодирования, блоки 7 и 8 выделения существенных отсчетов, блок 9 кодирования ад- реса, элементы ИЛИ 10, 11 и 12, блок 13 буферной памяти, блок 14 опе ративной памяти, блок 15 регистров, триггер J6 и 17, элементы И 18, 19 и 20, регистр 21, элементы ШМ, 22 и 23, сумматоры 24 и 25, счетчик 26 элемент 27 памяти, регистры 28 н 29 сумматоры 30 и 31, счетчнк 32, элемент И 33, счетчики 34, 35 н 36, регистр 37, элемент ИЛИ 38. Устройство работает следующим образом. . Аналоговые сигналы с телеметрических кайалов поступают на входы коммутатора 2 и блока 1 аналоговой памяти. Синхронизатор 4 последовательно с периодом коммутации формирует какую-либо кодовую комбинацию, подаваемую на входы управления коммутато1)ов 2 и 3 н на вход блока 8 вьщеления сзпцественных отсчетов. В соответствии с этой кодовой ксзмбинацией коммутатора 2 коммутирует соответствующий канал на вход блока 6 кодирования и подготавливает к работе блок 8 вьщеления существенны отсчетов. Блок 6 кодирования преобразует аналоговые сигналы телеметрических каналов в 8-разрядньй параллельный цис ровой код и подает его на вход блока 8 вьщеления существенных отсчетов. Кроме того, на вход блока 7 вмцеления существенных отсчетов и вход блока 9 кодирования адреса с синхронизатора 4 поступает последовательность HMnylibcoB, характеризую щая Частоту считывания информации с выхода устройства в радиоканал Блок 8 выделения существенных отсче тов производит оценку этой Информации на существенность. Если информация существенна, с выходов этого блока выдаются команды подготавливающие к работе блок 7 выделения су щественных отсчетов и блок 9 кодирования адреса, а цифровой 8-разряд ный код существенного отсчета подае ся на вход блока 7 выделения сущест венных отсчетов и через элемент ИЛИ 10 - на первый вход блока буферной памяти. Одновременно блок кодирования адреса из последователь ности импульсов, поступающих на его вход с синхронизатора 4, формирует адрес записи csmtecTBeHHoro отсчета блока-13 буфернойпамяти и адрес за писи адреса существенного отсчета в блок 14 оперативной памяти. Адрес записи существенного отсчета поступает через элемент ИЛИ 2 на второй вход блока 13 буферной памяти, разрешает запись этого существенного отсчета по этому адресу и на вход блока 14 оперативной памяти, на другой вход которого поступает адрес, по которому производится запись адреса существенного отсчета в блок 14 оперативной памяти. Наличие в предлагемом.устройстве блока 14 оперативной памяти позволяет использовать блок 13 буферной памяти любой емкости. Таким образом, значение существенных отсчетов в точках опроса с периодом коммутации заносятся по соответствующим адресам в блок I3 буферной памяти, а адреса этих существенных отсчетов заносятся в блок 14 оперативной памяти. При аварийной ситуации важно иметь информацию о поведении телеметрируемого аналогового сигнала во всем диапазоне частот. Для обеспечения контроля поведения аналогового сигнала между опросами блок 1 аналоговой памяти запоминает максимальное значение сигнала между опросами и подает его на входы коммутатора 3. После преобразования телеметрируемых аналоговых сигналов в каждом такте коммутации по сигналам с выхода синхронизатора 4 происходит сброс в исходное состояние блока 1 аналоговой памяти и блока 7 вьзделения существенных отсчетов. Коммутатор 3 синхронно с коммутатором 2 последовательно в соответствии с кодовыми комбинациями. формируемыми синхронизатором 4, коммутирует ячейки блока 1 аналоговой памяти на вход блока 5 кодирования. Таким образом, максимальиое значение аналогового сигнала между опросами каждого телеметрического канала подается на вход блока 5 кодирования синхронно с подачей на вход блока 6 кодирования значений сигналов в момент опроса телеметрируемых каналов коммутатором 2. Это максимальиое значение аналогового сигнала между опросами блоком 5 кодирования преобразуется в 8--разрядный цифровой код, который подается на вход блока 7 вьвделения существенных.отсчетов . Блок 7 выделения существенных отсчетов оценивает максимальное значение аналогового сигнала между оп-

росами на существенность, сравнивая это значение со значением текущего существенного отсчета в последней точке опроса. Если значение аналогового сигнала в этой точке несущественно, то сравнивают со значением предьщущего существенного отсчета по данному каналу. Если максимальное значение аналового сигнала между опросами существенно, то с двух выходов блока 7 вьщеления существенных отсчетов выдаются команды, подготавливающие блок 9 кодирования адреса к формированию адреса существенного максимального значения между опросами, а с третьего выхода блока 7 вьщеления существенных отсчетов 8--разрядш 1Й цифровой код через элемент ИЛИ 10 поступает на вход блока 13 буферной памяти.

Блок 9 кодирования адреса при этом формирует адрес существенного максимального значения аналогового сигнала между опросами и подает его на вход блока 14 оперативной памяти и через элемент ИЛИ 12 - на второй вход блока 13 буферной памяти.. Таким образом, супественное максимальное значение аналогового сигнала между опросами записывается по соответствующему адресу в блок 13 буферной памяти, а адрес сущёствениого максимального значения между опросами записывается по соответствующему адресу в блок 14 оперативной памяти. Опращивая последовательно все телеметрические кана1И 1, устройство для передачи и телеметрических сигналов определяет существенные значения аналоговых сигналов в точках опроса, присваивает им соответствукнцие адреса и записывает их в блок 13 буферной памяти, одновременно оно контролирует изменение аналогового сигнал между опросами и Б случае, если изменение аналогового сигнала относительно существенного текущего значения или предыдущего существенного значения превышает апертуру, определяемую блоками 7 и 8 вь дeлeнrfя существенных отсчетов, то это максимальное значение аналогового сигнала между опросами записывается в блок буферной памяти по соответствующему адресу.

Считывание существенной информации в радиоканал происходит независимо от опроса телеметрических каналов . Синхроимпульсы с выхода синхронизатора 4 поступают на вход блока 9 кодирования адреса, который формирует адрес считывания адресов существенных значений аналогового сигнала в точках опроса и между опросами. Адреса считывания поступают на первый вход блока 14 оперативной памяти. По этому адресу считьшания считываются адреса существенных значений аналогового сигнала в точках опроса и между опросами. Адреса существенных значений поступают на вход блока 15 регистров, а также через элемент ИЛИ 12 - на второй вход блока 13 буферной памяти. По ним производится считывание существенных знчений аналогового сигнала. Существенные значения аналогового сигнала в точках опроса и существенные максимальные значения аналогового сигнала между опросами с выхода блока 13 буферной памяти поступают на второй вход блока 15 регистров. Блок 15 регистров формирует выходное 16-разрядное телеметрическое слово, первые восемь разрядов которого являются адресными, вторые восемь - информационными..

Блок 8 вьщеления существенных отсчетов работает следующим образом. С рыхода блока 6 кодирования восьмиразрядный цифровой код текущего значения аналогового сигнала в точках опроса поступает на вход регистра 28, с выхода которого он поступает на первые-входы сумматора 30 и элемента И 33. На второй вход сумматора 30 с регистра 29 поступает 8-разрядный код предьщущего существенного отсчета, который считьгеается с элемента 27 памяти по соответствующей кодовой комбинации, поступающей с выхода сиихронизатора 4,на первый вход элемента 27 памяти. Сумматор 30 определяет разность между текущим значением отсчета и предьщушим существенным отсчетом для данного канала. Эта разность подается на первый вход сумматора 31. Сумматор 31 производит сравнение величины этой разности с выбранной апертурой, определяемой исходя из требуемой точности преобразования. Если разность, определенная сумматором 30, меньше выбранной апертуры, то сумматор 31 производит сравнение разности : не.пичиной апертуры, поступающей но егп в-1Ч1рой вход с четырех старших разрядов 8-разряд- ного счетчика 32. Для исключения потерь информации из-за переполиения блока 13 буферной памяти апертуры, определяемая счетчиком 32, меняется в зависимости от заполнения блока 13 буферной памяти. На первый вхо счетчика 32 поступают импульсы с сум матора 31, количество которых равно количеству существенных отсчетов аналоговых сигналов в точках опроса записанных в блок 13 буферной памяти, а на второй вход - синхроимпульсы с выхода синхронизатора 4, характеризующие количество сосчитанных существенных отсчетов из блока 3 буферной памяти в радиоканал. Таким образом, содержание счетчика 32 зависит от числа,заполненных ячеек блока 13 буферной памяти. Код счетчика 32 устанавливает величину апер туры, причем большему заполнению бло ка I3 буферной памяти соответствует большее значение апертуры. Если разность меньше апертуры, то значение текущего отсчета считается несущественным и сум«1атор 31 не подает сигнал на второй вход элемента И 33, разрешающий прохождение текущего отсчета в точках опроса через элемент И 33, т.е. это значение текущего отсчета не будет записано в блок 13 буферной памяти. Если разность больше выбранной апертуры или апертуры, определенной счетчиком 32 то значение текущего отсчета считается существенным и сигнал с выхода сумматора 31 подается иа второй вход элемента И 33, разрешая прохождение существенного отсчета в точках опроса с выхода регистра текущего отсчета через элемент ИЛИ 10 на информационный вход блока 13 буферной памяти. Блок 7 шоделения существенных отсчетов работает следукицим образом. . С блока 5 кодирования восьмиразрядны цифровой код максимального значения аналогового сигнала между опросами поступает на вход регистра 21. С выхода регистра 21 этот код поступает на первые входы элементов И 18, 19 и 20. В исходном состоянии триггер 6 разрешает прохождение цифрового кода с выхода регистра 21 через элемент И 18 и запрещает элемент И 19, триггер 17 запрещает прохождение этого кода через эле- мент ИЛИ 20, Таким образом, при отсутствии сигнала с сумматора 31 (т.е. в данной точке опроса отсчет несущественен ) цифровой код максимального значения аналогового сигнала между опросами через элементы И 18 и ИЛИ 22 поступает на первый вход сумматора 24, на второй вход которого с выхода элемента 27 памяти через элемент ИЛИ 23 поступает соответствующий данному каналу предьщущий существенный отсчет. Сумматор 24 оп- ределяет разнойть между максимальным значением аналогового сигнала между опросами и значением предьщущего существенного отсчета. Абсолютное значение этой разности поступает на первый вход сумматора 25. Если в данной точке опроса отсчет существенен, то сигнал с сумматора 31 устанавливает триггер 16 в состояние, запрещающее элемент И 18 и разрешающее элемент И 19 для прохождения цифрового кода максимального значения аналогового сигнала с регистра 21 через элемент ИЛИ 22 на первый вход сумматора 24, на второй вход которого с выхода элемента И 33 через элемент ИЛИ 23 поступает существенное значение существенного отсчета. Сумматор 24 находит разность между максимальным значением аналогового сигнала за период между опросами и значением аналогового сигнала в точке опроса. Абсолютное значение разности подается с выхода сумматора 24 на первый вход сумматора 25. Сумматор 25 производит сравнение абсолютной величины этой разности с выбранной апертурой, определяемой исходя из требуемой точности преобразования. Если разность, определенная сумматором 25, меньгае выбранной апертуры, то сумматор 25 производит сравнение разности с величиной апертурыу поступающей с реверсивного.- счетчика 26 на его второй вход, Определе- Ние апертуры счетчиком 26 и сущест- венности максимального значения ана- логового сигнала между опросаьш производится, как сумматором 31, Если максимальное значение аналогового сигнала между опросами существенно, то с выхода сумматора 25 на второй вход триггера 17 поступает сигнал, устанавливающий его в состояние, разрешающее логический элемент И 20 для прохождения цифрового кода с -3V, выхода регистра 21, т.е. существенного максимального значения аналогевого сигнала между опросами через элемент ИЛИ 10 на первый вход блока 13 буферной памяти. Кроме того, сигналы с сумматора 25, триггера 17 поступают на блок 9 кодирования адреса. Блок 9 кодирования адреса работает ел едукщим образом. Последовательность импульсов синхронизатора 4 поступает на вход счетчика 34, который формирует адрес записи существенных . отсчетов в блок 13 буферной памяти. Адрес записи существенных отсчетов Поступает на первый вход регистра 37 и на вход блока 13 буферной памяти. В случае, когда максимальное значение аналогового сигнала между опросами существенно, с выхода триггера 17 подается сигнал на второй вход регистра 37, по которому код адреса существенного отсчета увеличивается на единицу старшего разряда, таким образом, наличие единицы в старшем разряде адреса существенного отсчета говорит о том, что это информация об аналоговом сигнале между опросами. Последовательность импульсов с выхода синхронизатора 4 поступает на вход счетчика 36, на выходе 614 которого формируется код адреса считьшания адреса существенного отсчета, который подается на первый вход элемента ИЛИ 38. Сигналы с сумматоров 25, 3, подтверждающие существенность значений аналоговых сигналов, поступают на вход счетчика 35, с выхода которого адрес записи адреса существенного отсчета поступает на второй вход элемента ИЛИ 38. С выхода элемента ШШ 38 на первый вход блока 14 оперативной памяти последовательно поступают коды адреса записи и считьшания адреса существенного отсчета. Предлагаемое устройство позволяет увеличить информативность устройства по сравнению с прототипом. При этом обеспечивается контроль поведения аналоговых сигналов между опросами, т.е. контроль пульсации или изменений аналоговых сигналов, возникающих при аварийных ситуациях и имеющих частоту выие, чем частота .аналоговых сигналов. Для обеспечения возможности такого контроля аналоговых сигналов в прототипе необходимо Использовать несколько устройств, в связи с чем утсудшается габарнтномассовые характеристики и увеличивавается стоимость устройства.

te.J

П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сжатия аналоговых сигналов | 1978 |

|

SU767807A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 1005417,кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-04-30—Публикация

1983-12-21—Подача