20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки аналогового сигнала | 1988 |

|

SU1566370A1 |

| Устройство для цифровой обработки аналогового сигнала | 1990 |

|

SU1762311A1 |

| Вычислительное устройство для обработки термограмм | 1984 |

|

SU1223251A1 |

| Устройство для цифровой обработки аналогового сигнала | 1986 |

|

SU1332335A1 |

| Анализатор содержания кремния в жидком чугуне | 1990 |

|

SU1742691A1 |

| Устройство для оценки скорости изменения аналогового сигнала | 1991 |

|

SU1830538A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Датчик сил упругой деформации механизма и устройство для его настройки | 1985 |

|

SU1288511A1 |

| Анализатор аналоговых сигналов | 1988 |

|

SU1520551A1 |

| Кодирующее устройство с дельта-модуляцией и импульсно-кодовой модуляцией | 1984 |

|

SU1182681A2 |

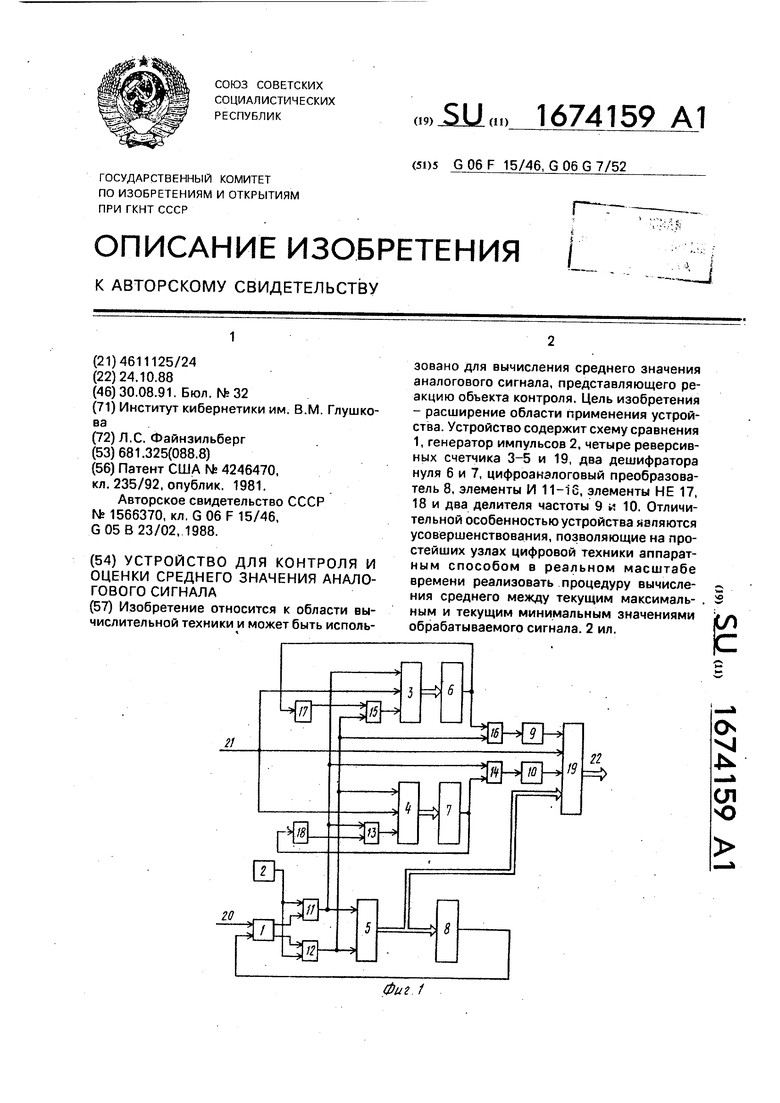

Изобретение относится к области вычислительной техники и может быть использовано для вычисления среднего значения аналогового сигнала, представляющего реакцию объекта контроля. Цель изобретения - расширение области применения устройства. Устройство содержит схему сравнения 1, генератор импульсов 2, четыре реверсивных счетчика 3 и 19, два дешифратора нуля 6 и 7, цифроаналоговый преобразователь 8, элементы И 11 - 16, элементы НЕ 17, 18 и два делителя частоты 9 и 10. Отличительной особенностью устройства являются усовершенствования, позволяющие на простейших узлах цифровой техники аппаратным способом в реальном масштабе времени реализовать процедуру вычисления среднего между текущим максимальным и текущим минимальным значениями обрабатываемого сигнала. 2 ил.

Фиг f

Изобретение относится к вычислитель ной технике и может бить использовано для автоматического определения в цифровой форме вприации среднего между максимальным и минимальным значениями обрабатываемого аналогового сигнала, поступающего от различного рода источников, например, датчиков технологических процессов.

Цель изобретения - расширение области применения устройства.

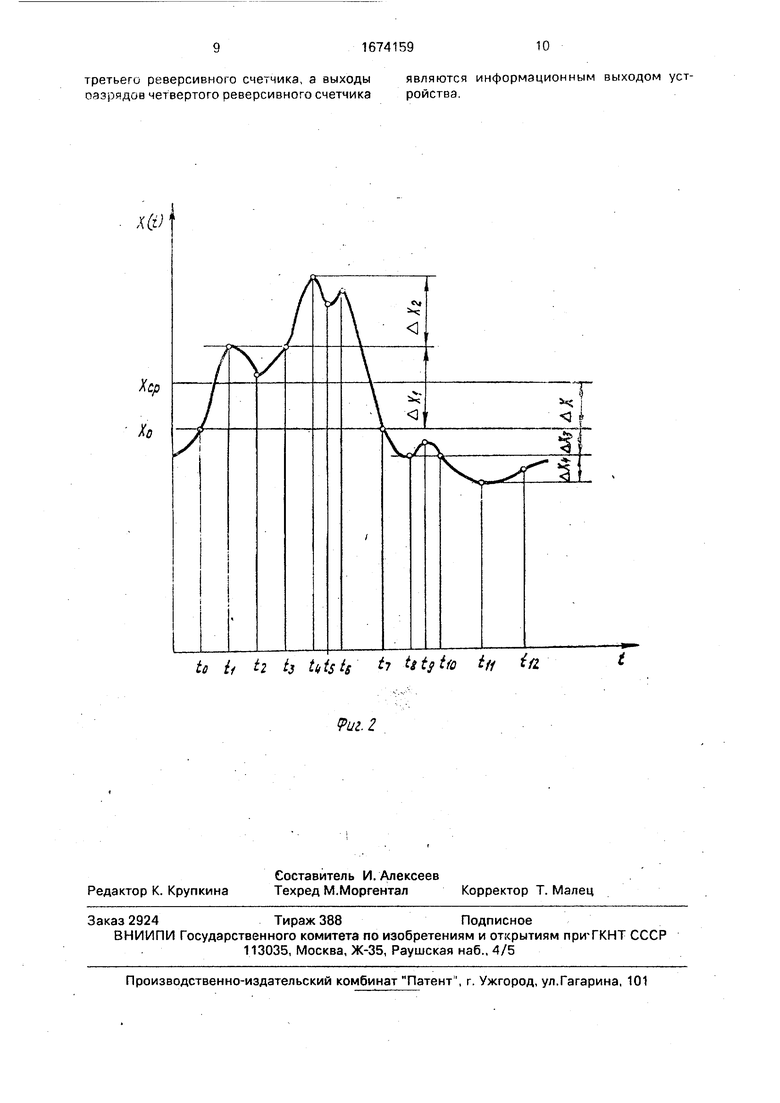

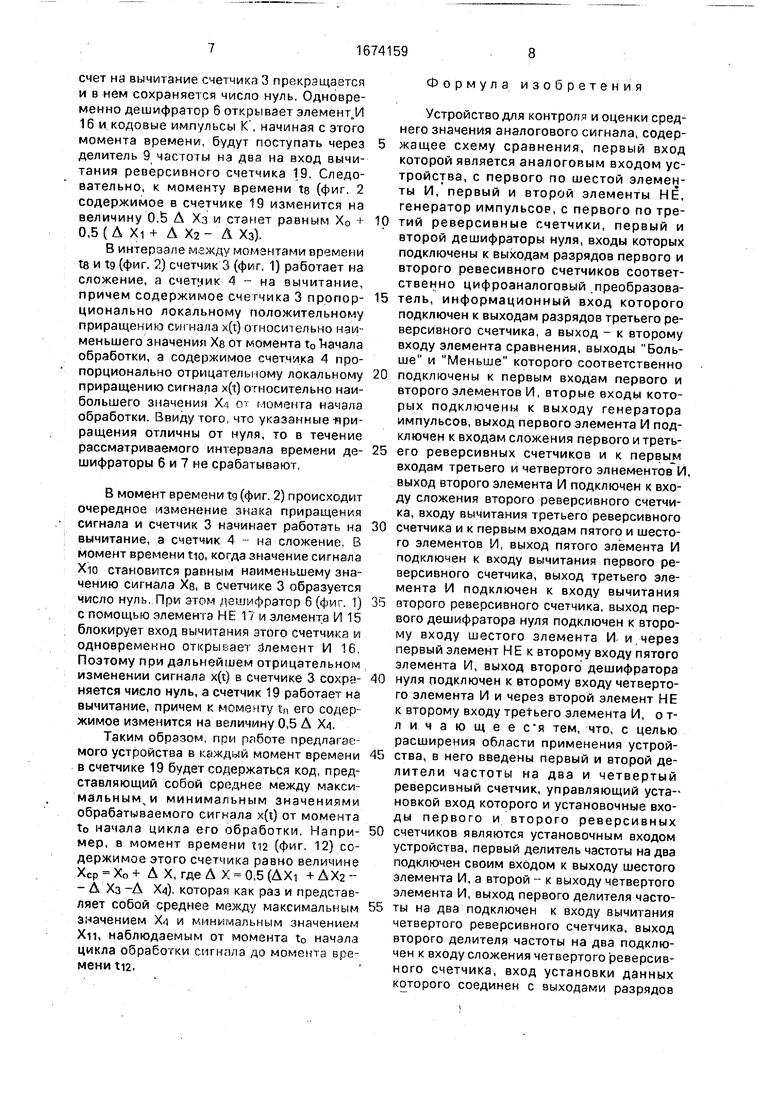

На фиг. 1 представлена схема устройства; на фиг. 2 - временная диаграмма, иллюстрирующая принцип действия устройства.

Устройство содержит схему 1 сравнения, генератор 2 импульсов, первый,второй и третий реверсивные счетчики 3, 4, 5, первый и второй дешифраторы 6, 7 нуля, циф- роаналоговый преобразователь 8, первый и второй делители 9, 10 частоты на два, с первого по шестой элементы И 11-16, первый и второй элементы НЕ 17, 18, четвертый реверсивный счетчик 19, аналоговый 20 и установочный 21 входы и информационный 22 выход устройства.

Устройство работает следующим образом.

Обрабатываемый аналоговый сигнал x(t) поступает на первый вход схемы 1 сравнения. На второй вход этого же элемента поступает компенсирующий аналоговый сигнал хДх) обратной связи с выхода циф- роаналогового преобразователя 8. Если сигнал x(t) больше сигнала xK(t) (режим Не- докомпенсация), то на первом выходе схемы 1 сравнения образуется сигнал логической единицы, который открывает элемент И 11. Импульсы от генератора 2 череа элемент И 11 поступают на вход сложения реверсивного счетчика 3. Содержимое этого счетчика увеличивается, что. в свою очередь, вызывает увеличение компенсирующего аналогового сигнала xK(t) на выходе цифроаналогового преобразователя 8. Как только сигнал хк(х) становится равным сигналу x(t) с точностью до порога нечувствительности д0, схема сравнения 1 закрывает элемент И 11.

Если же обрабатываемый сигнал x(t) меньше компенсирующего сигнала xK(t) (режим Перекомпенсация), то на втором выходе схемы 1 сравнения образуется сигнал логической единицы, который открывает элемент И 12, и импульсы от генератора 2 поступают уже на вход вычитания реверсивного счетчика 5. Содержимое этого счетчика уменьшается, что вызывает умень

шение компенсирующего сигнала xK(t), Как только сигнал xK(t) становится равным сигналу x(t) с точностью до /- о. х -ia сравнения 1 закрывает элемент И 12. I :м самым осуществляется следящее преобразование обрабатываемого сигнала x(t) в цифровую форму, в процессе которого на выходах разрядов реверсивного счетчика 5 образуется параллельный код, пропорциональный те0 кущему значению сигнала x(t), а на выходах элементов И 11 и 12 образуется реверсивныйчислоимпульсный код, представляющий собой последовательность кодовых импульсов К+ и К . образуемых со5 ответственяо при каждом элементарном положительном и отрицательном приращениях сигнала x(t).

Перед началом цикла обработки аналогового сигнала x(t) в момент времени to

0 (фиг. 2) на вход 21 устройства (установочные входы счетчиков 3 и 4 и управляющий вход счетчика 19) с помощью кнопки начальной установки (не показана) либо от какого-либо другого внешнего устройства

5 поступает управляющий сигнал, посредством которого счетчики 3 и 4 обнуляются, а в счетчик 19 по шине параллельной передачи данных из счетчика 5 заносится код величины х0, соответствующий значению аналого0 вого сигнала в этот момент времени.

В процессе следящего преобразования аналогового сигнала x(t) в цифровую форму кодовые импульсы К+, образуемые на выходе элемента И 11, поступают на вход сло5 жения реверсивного счетчика 3 и через элемент И 13 на вход вычитания реверсивного счетчика 4. Кодовые импульсы К, образуемые на выходе элемента И 12, поступают на вход сложения реверсивного счетчика 4

0 и через элемент И 15 на вход вычитания реверсивного счетчика 3. С помощью дешифраторов 6 и 7 осуществляется блокировка счета на вычитание в счетчиках 3 и 4, как только в соответствующем счетчика обраэу5 ется число нуль. Блокировка достигается тем, что при появлении в счетчике 3 числа нуль на выходе дешифратора 6, подключенного к нулевым выходам разрядов счетчика 3, образуется потенциал логической еди0 ницы, который через элемент НЕ 17 блокирует элемент И 15. Аналогичным образом с помощью дешифратора 7 и элементов 18 и 13 осуществляется блокировка входа вычитания счетчика 4.

5 Поскольку в начале цикла обработки сигнала в момент времени t0 (фиг. 2), как уже отмечалось выше, счетчики 3 и 4 обнуляются, то в результате на выходах дешифраторов 6 и 7 образуются потенциалы

логической единицы, которые открывают элементы И 16 и 14 и с помощью элементов НЕ 17, 18 блокируют входы вычитания соответственно счетчиков 3 и 4.

В интервале времени между момента- ми t0 и ti (фиг. 2) сигнал x(t) возрастает, а значит образуются кодовые импульсы К на выходе элемента И 11 (фиг. 1). Эти импульсы поступают на вход сложения реверсивного счетчика 3 и вход элемента И 13, который в данной ситуации заблокирован сигналом от дешифратора 7 нуля. В результате в указанный промежуток времени счетчик 4 будет продолжать оставаться в нулевом состоянии, а счетчик 3 будет считать на сложение, причем содержимое этого счетчика будет пропорционально текущему положительному приращению сигнала x(t) относительно его значения Х0 в момент времени to, a значит к моменту времени ti содержи- мое счетчика 3 станет равным величине ДХ1 Xi - Х0 (фиг. 2).

Кроме того, в указанный промежуток времени кодовые импульсы К+ проходят через открытый элемент И делитель 10 частоты на два на вход сложения реверсивного счетчика 19. Отсюда следует, что к моменту времени ti (фиг. 2) содержимое реверсивного счетчика 19 (фиг. 1) изменится на величину 0,5 Д XL т.е. станет равным Х0 0.5 A XL

В момент времени п (фиг. 2) происходит изменение знака приращения сигнала, а значит на выходе элемента И 12 (фиг. 1) начинают образовываться кодовые импуль- сы К . Эти импульсы поступают на вход сложения реверсивного счетчика 4 (фиг. 1) и на вход элемента И 15. Поскольку в реверсивном счетчике 3 в данной ситуации содержится число Д xi, отличное от нуля, то на выходе дешифратора 6 образуется сигнал логического нуля, который блокирует элемент И 16 и через элемент НЕ 17 открывает элемент И 15. Поэтому в ин гервале между ti и t2 (фиг. 2) кодовые импульсы К будут свободно проходить на вход вычитания счетчика 3 (фиг. 1), уменьшая содержимое последнего. Однако к моменту времени ta содержимое этого счетчика еЩе не достигнет нуля, поскольку значение сигнала Х2 в момент времени t2 больше значения сигнала XT в момент времени ц. Содержимое же реверсивного счетчика 4 будет увеличиваться и к моменту времени t2 окажется пропорциональным отрицательному приращению сигнала x(t) относительно значения Xi - наибольшего локального значения обрабатываемого сигнала от момента to начала цикла его обработки.

Поскольку в интервале между моментами ti и ta элемент И 16 заблокирован, то к моменту времени t2 содержимое счетчика останется равным величине Х0 + 0,5 Д Xi.

В момент времени t2 (фиг. 2) происходит очередное изменение знака приращения сигнала x(t) и снова образуются уже кодовые импульсы К . Эти импульсы поступают на вход сложения реверсивного счетчика 3 и открытый дешифратором 7 вход вычитания реверсивного счетчика 4. Содержимое счетчика 3 постоянно увеличивается, а счетчика 4 - уменьшается до тех пор, пока в момент времени t3 (фиг. 2) не будет выполнено условие Хз Xi и содержимое счетчика 4 не окажется равным нулю. В этот момент времени 1з дешифратор 7 блокирует элемент И

13,предотвращая дальнейший счет на вычитание счетчиком 4, и открывает элемент И

Начиная с момента времени ti (фиг. 4), сигнал x(t) уменьшается, а значит образуются кодовые импульсы К, которые поступают на вход сложения счетчика 4 и вход вычитания счетчика 3. При этом содержимое счетчика 4 в каждый момент времени пропорционально текущему отрицательному приращению сигнала x(t) относительно наибольшего локального значения Х4 в течение цикла обработки сигнала, а содержимое счетчика 3 пропорционально текущему положительному приращению сигнала x(t) относительно наименьшего локального значения Хо в течение цикла обработки сигнала.

В моменты времени ts и te (фиг. 2) происходят очередные изменения знака приращения сигнала x(t), что вызывает изменения направления счета в счетчиках 3 и 4. Однако, поскольку экстремальные значения сигнала Хб и Хб не являются ни наибольшим, ни наименьшим значениями сигнала, то ни в счетчике 3, ни в счетчике 4 числа нуль не образуется, а значит не происходит срабатывания дешифраторов 6 и 7.

В момент времени ty, когда значение сигнала X становится равным наименьшему значению Хо, принятому в момент времени t0, содержимое счетчика 3 становится равным нулю. При этом срабатывает дешифратор 6 и закрывается элемент И 13. В результате, начиная с момента времени t,

счет на вычитание счетчика 3 прекращается и в нем сохраняется число нуль. Одновременно дешифратор б открывает элемент.И 16 и кодовые импульсы К, начиная с этого момента времени, будут поступать через делитель 9 частоты на два на вход вычитания реверсивного счетчика 19. Следовательно, к моменту времени ts (фиг. 2 содержимое в счетчике 19 изменится на величину 0,5 Д Хз и станет равным Х0 - 0,5 ( Д Xi + Д Х2- Д Хз).

В интервале между моментами времени te и tg (фиг. 2) счетчик 3 (фиг. 1) работает на сложение, а счетчик 4 - на вычитание, причем содержимое счетчика 3 пропорционально локальному положительному приращению си нала x(t) относительно наименьшего значения Хв от момента to Начала обработки, а содержимое счетчика 4 пропорционально отрицательному локальному приращению сигнала x(t) относительно наибольшего значения Xi от момента начала обработки. Ввиду того, что указанные -яри- ращения отличны от нуля, то в течение рассматриваемого интервала времени дешифраторы 6 и 7 не срабатывают,

В момент времени tg (фиг. 2) происходит очередное изменение знака приращения сигнала и счетчик 3 начинает работать на вычитание, а счетчик 4 - на сложение. В момент времени tio, когда значение сигнала Хю становится равным наименьшему значению сигнала Хв, в счетчике 3 образуется число нуль. При этом дешифратор 6 (фиг. 1) с помощью элемента НЕ 17 и элемента И 15 блокирует вход вычитания этого счетчика и одновременно открывает Элемент И 16. Поэтому при дальнейшем отрицательном изменении сигнала x(t) в счетчике 3 сохраняется число нуль, а счетчик 19 работает на вычитание, причем к моменту tn его содержимое изменится на величину 0,5 Д .

Таким образом, при работе предлагаемого устройства в каждый момент времени в счетчике 19 будет содержаться код, представляющий собой среднее между макси- мальным и минимальным значениями обрабатываемого сигнала x(t) от момента to начала цикла его обработки. Например, в момент времени ti2 (фиг. 12) содержимое этого счетчика равно величине Хср Х0 + Д X, где Д X 0,5 (AXi + ДХ2 - - Д Хз -Д X/i). которая как раз и представляет собой среднее между максимальным значением X.j и минимальным значением Хп, наблюдаемым от момента to начала цикла обработки сигнала до момента времени t12.

Формула изобретения

Устройство для контроля и оценки среднего значения аналогового сигнала, содержащее схему сравнения, первый вход которой является аналоговым входом устройства, с первого по шестой элементы И, первый и второй элементы НЕ, генератор импульсое, с первого по тре0 тий реверсивные счетчики, первый и второй дешифраторы нуля, входы которых подключены к выходам разрядов первого и второго ревесивного счетчиков соответственно цифроаналоговый преобразова5 тель, информационный вход которого подключен к выходам разрядов третьего реверсивного счетчика, а выход - к второму входу элемента сравнения, выходы Больше и Меньше которого соответственно

0 подключены к первым входам первого и второго элементов И, вторые входы которых подключены к выходу генератора импульсов, выход первого элемента И подключен к входам сложения первого и треть5 его реверсивных счетчиков и к первым входам третьего и четвертого элнементов И, выход второго элемента И подключен к входу сложения второго реверсивного счетчика, входу вычитания третьего реверсивного

0 счетчика и к первым входам пятого и шестого элементов И, выход пятого элемента И подключен к входу вычитания первого реверсивного счетчика, выход третьего элемента И подключен к входу вычитания

5 второго реверсивного счетчика, выход первого дешифратора нуля подключен к второму входу шестого элемента И и через первый элемент НЕ к второму входу пятого элемента И, выход второго дешифратора

0 нуля подключен к второму входу четвертого элемента И и через второй элемент НЕ к второму входу третьего элемента И, о т- личающеес я тем, что, с целью расширения области применения устрой5 ства, в него введены первый и второй делители частоты на два и четвертый реверсивный счетчик, управляющий уста- новкой вход которого и установочные входы первого и второго реверсивных

0 счетчиков являются установочным входом устройства, первый делитель частоты на два подключен своим входом к выходу шестого элемента И, а второй - к выходу четвертого элемента И, выход первого делителя часто5 ты на два подключен к входу вычитания четвертого реверсивного счетчика, выход второго делителя частоты на два подключен к входу сложения четвертого реверсивного счетчика, вход установки данных которого соединен с выходами разрядов

третье1 / pteepctfRnoio счегчика, а выходы пятг«дов четвертого реверсивного счетчика

to it tz tj htsts b htstto ff a

являются информационным выходом устройства

Т

| Патент США N 4246470, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для цифровой обработки аналогового сигнала | 1988 |

|

SU1566370A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-10-24—Подача