Выла дш3 Вьн2 9wf

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножающий цифроаналоговый преобразователь | 1988 |

|

SU1765893A1 |

| Преобразователь код-ток | 1987 |

|

SU1499498A1 |

| Высоковольтный транзисторный переключатель | 1990 |

|

SU1734203A1 |

| Ключевой преобразователь | 1987 |

|

SU1624639A1 |

| Устройство для контроля работоспособности аналоговых блоков радиоэлектронной аппаратуры | 1987 |

|

SU1506403A1 |

| Кольцевой счетчик | 1988 |

|

SU1539998A1 |

| Кольцевой счетчик | 1988 |

|

SU1539997A1 |

| Цифроаналоговый преобразователь | 1973 |

|

SU661778A1 |

| Коммутирующее устройство | 1983 |

|

SU1173546A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU1064453A1 |

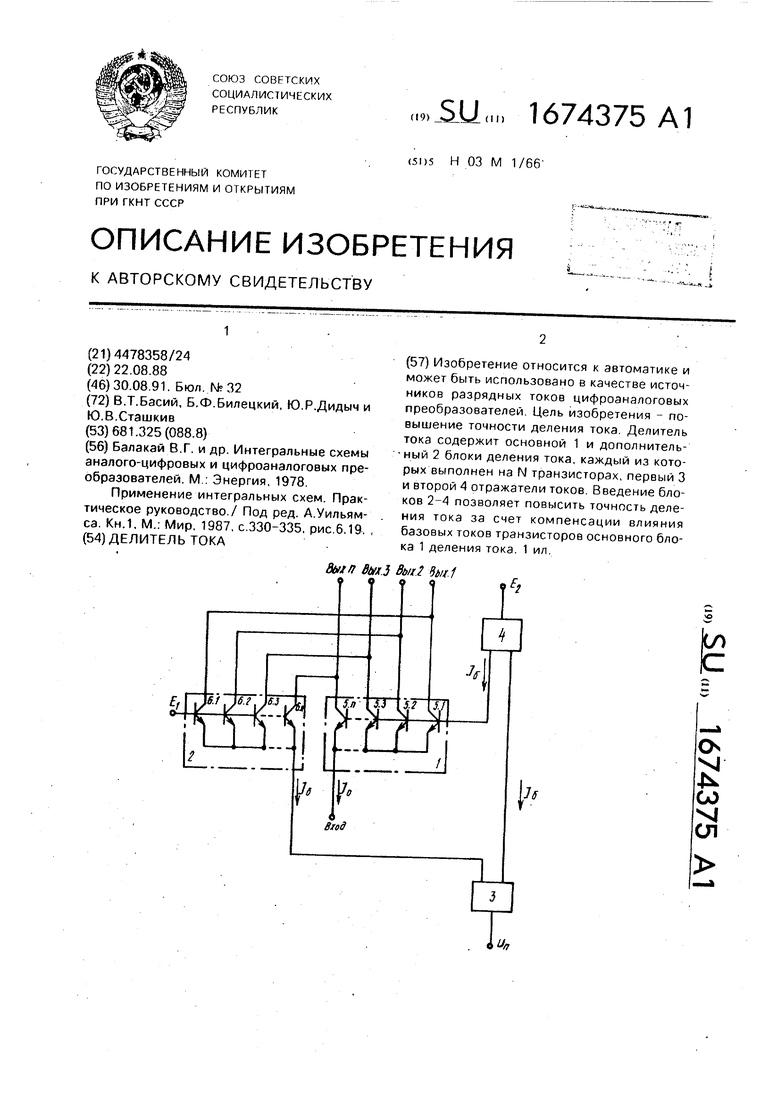

Изобретение относится к области автоматики и может быть использовано в качестве источников разрядных токов цифроаналоговых преобразователей. Цель изобретения - повышение точности деления тока. Делитель тока содержит основной 1 и дополнительный 2 блоки деления тока, каждый из которых выполнен на N транзисторах, первый 3 и второй 4 отражатели токов. Введение блоков 2 - 4 позволило повысить точность деления тока за счет компенсации влияния базовых токов транзисторов основного блока 1 деления тока. 1 ил.

со

с

о

2

со

VJ

ел

Изобретение относится к автоматике и может быть использовано, в частности, в качестве источников разрядных токов циф- роэналоговых преобразователей.

Цель изобретения - повышение точности деления тока.

На чертеже представлена функциональная схема делителя тока.

Делитель тока содержит основной 1 и дополнительный 2 блоки деления тока, пер- вый 3 и второй 4 отражатели токов. Каждый из блоков 1 и 2 деления тока выполнен на п транзисторах 5.1-б.п и 6,1-б.п соответственно.

Делитель тока работает следующим об- разом.

Входной опорный ток 10 поступает на объединенные эмиттеры транзисторов 5.1- 5.п основного блока 1 деления тока, в коллекторах которых формируются разрядные токи, величины которых распределены, например, по двоичному закону и соответствуют соотношению 1:1:2:4:.,.:2 . В этом случае количество эмиттеров транзисторов 5.1-б.п или площади их эмиттерных перехо- дов, или количество одинаковых параллельно соединенных транзисторов в каждом разряде блока 1 изменяются также по двоичному закону.

Сумма базовых токов транзисторов ос- новного блока 1 деления тока протекает по цепи: вход-выход второго отражателя 4 токов, вход-выход первого отражателя 3 токов и эмиттерно-коллекторные переходы транзисторов 6.1-б.п дополнительного блока 2 деления тока. В коллекторах транзисторов 6.1-б.п, в свою очередь, формируются токи, величины которых соотносятся между собой также по двоичному закону. Эти токи суммируются с токами коллекторов соответствую- щих транзисторов 5.1-5.П основного блока 1 деления тока.

Результирующий выходной ток делителя тока отличается от величины входного опорного тока 1о на величину, равную сумме

базовых токов транзисторов 6.1-б.п дополнительного блока 2 деления тока. При коэффициенте усиления потоку ft транзисторов

блоков 1 и 2 эта величина составляет 1//32 часть от входного тока 0 и при / 100 погрешность деления равна 0,01 %.

Таким образом, введение дополнительного блока деления тока и двух отражателей токов позволяет повысить точность деления входного опорного тока 10 за счет компенсации влияния на точность деления базовых токов транзисторов основного блока 1 деления тока.

Формула изобретения Делитель тока, содержащий основной блок деления тока, выполненный в виде п транзисторов, базы которых обьединены, коллекторы являются выходной шиной, а эмиттер первого из п транзисторов объеди- нен с эмиттерами остальных транзисторов и является входной шиной опорного тока, и дополнительный блок деления тока, выполненный на п транзисторах, отличающий- с я тем, что, с целью повышения точности деления, в него введены первый и второй отражатели токов, коллекторы транзисторов дополнительного блока деления тока соединены с коллекторами соответствующих транзисторов основного блока деления тока, а эмиттеры обьединены и подключены к выходу первого отражателя токов, первый вход которого является входной шиной источника питания, а второй вход подключен к выходу второго отражателя токов, первый вход которого является первой входной шиной источника опорного напряжения, а второй вход соединен с базой первого транзистора основного блока деления тока, база первого транзистора дополнительного блока деления тока объединена с базами остальных транзисторов данного блока и является второй входной шиной источника опорного напряжения.

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы аналого-цифровых и цифроаналоговых преобразователей | |||

| М Энергия, 1978 Применение интегральных схем | |||

| Прак тическое руководство / Под ред | |||

| А.Уильям- са | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мир, 1987, с 330-335, рис 6.19 | |||

Авторы

Даты

1991-08-30—Публикация

1988-08-22—Подача