э

3i

VfM.

4

4i

сл

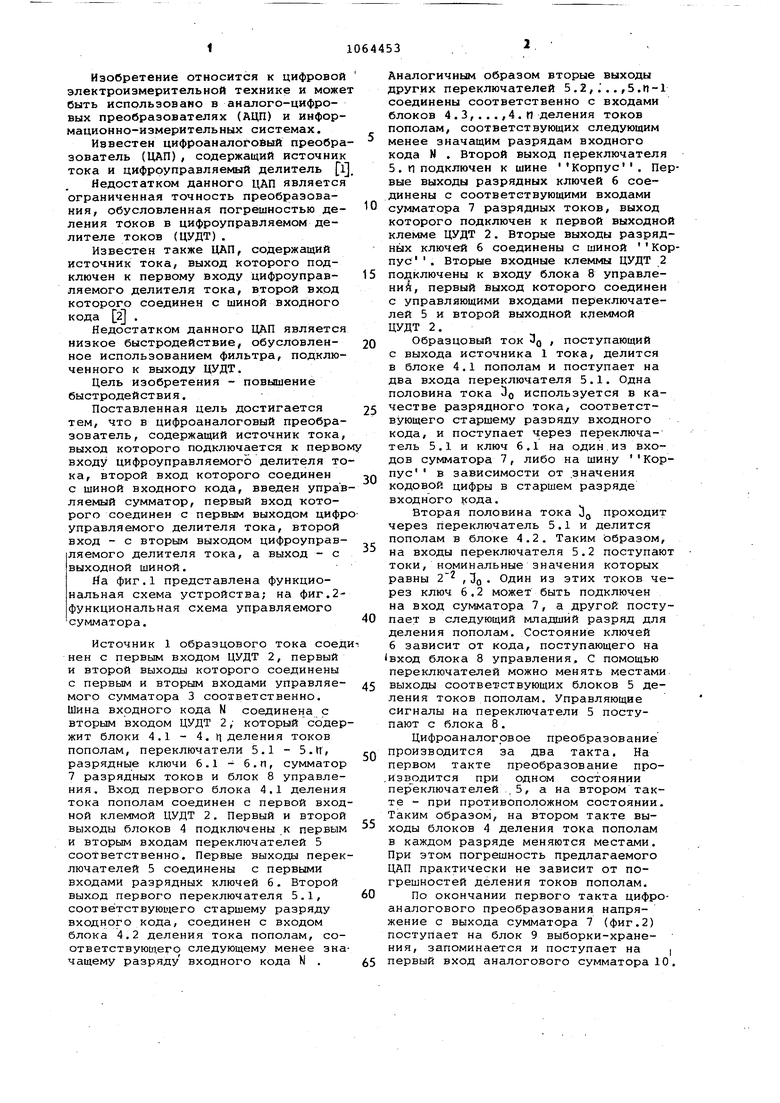

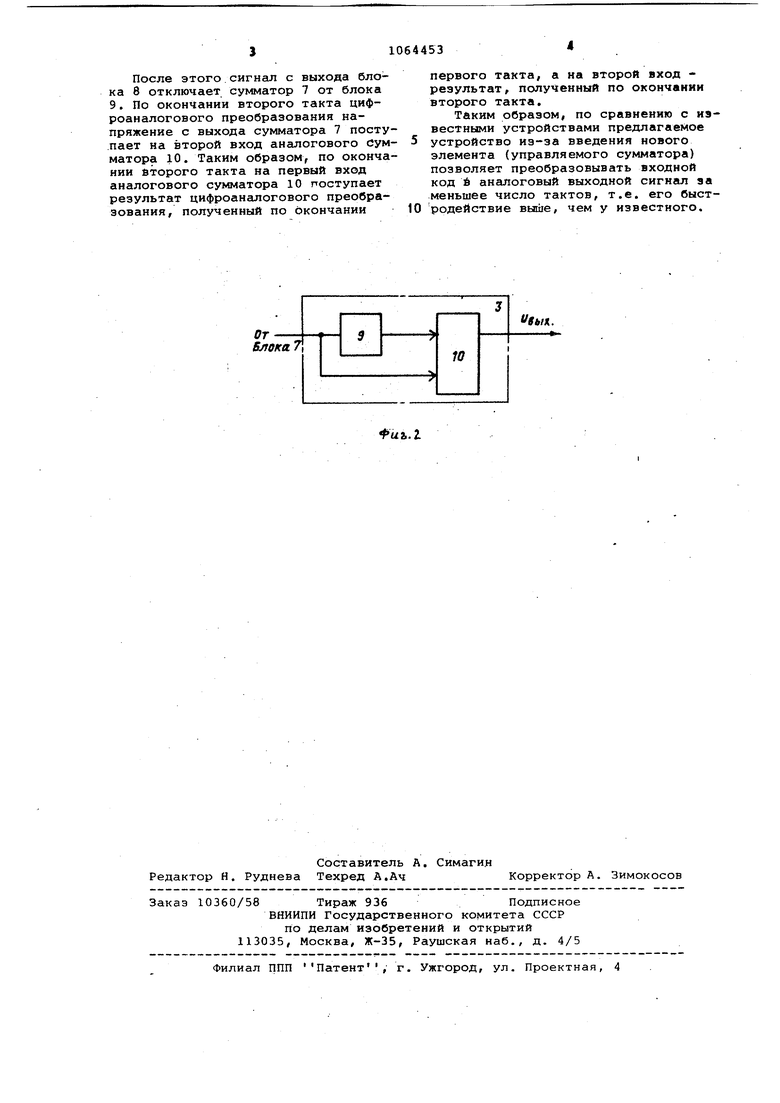

САЭ Изобретение относится к цифровой электроизмерительной технике и може быть использовано в аналого-цифровых преобразователях (АЦП) и информационно-измерительных системах. Известен цифроаналогойый преобра зователь (ЦАП), содержащий источник тока и цифрруправляемый делитель l Недостатком данного ЦАП является ограниченная точность преобразования, обусловленная погрешностью деЛенин токов в цифроуправляемом делителе токов (ЦУДТ). Известен также ЦАП, содержащий источник тока, выход которого подключен к первому входу цифроуправляемого делителя тока, второй вход которого соединен с шиной входного кода 2 . Недостатком данного ЦАП является низкое быстродействие, обусловленное использованием фильтра, подключенного к выходу ЦУДТ. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в цифроаналоговый преобразователь, содержащий источник тока, выход которого подключается к перво входу цифроуправляемого делителя то ка, второй вход которого соединен с шиной входного кода, введен управ ляемый сумматор, первый вход которого соединен с первым выходом цифр управляемого делителя тока, второй вход - с вторым выходом цифроуправляемого делителя тока, а выход - с выходной тиной. ria фиг.1 представлена функциональная схема устройства; на фиг.2функциональная схема управляемого сумматора. Источник 1 образцового тока соед нен с первым входом ЦУДТ 2, первый и второй выходы которого соединены с первым и вторым входами управляемогр сумматора 3 соответственно. Шина входного кода N соединена с вторым входом ЦУДТ 2 , который содер жит блоки 4.1 - 4. п деления токов пополам, переключатели 5.1 - 5.И, разрядные ключи 6.1 - б.п, сумматор 7 разрядных токов и блок 8 управления. Вход первого блока 4.1 деления тока пополам соединен с первой вход ной клеммой ЦУДТ 2. Первый и второй выходы блоков 4 подключены к первым и вторым входам переключателей 5 соответственно. Первые выходы перек лючателей 5 соединены с первыми входами разрядных ключей б. Второй выход первого переключателя 5.1, соответствующего старшему разряду входного кода, соединен с входом блока 4.2 деления тока пополам, соответствующего следующему менее зна чащему разряду входного кода N . Аналогичным образом вторые выходы других переключателей 5.2, ... ,5.0-1 соединены соответственно с входами блоков 4.3,...,4.п деления токов пополам, соответствующих следующим менее значащим разрядам входного кода N . Второй выход переключателя 5. и подключен к шине Корпус . Первые выходы разрядных ключей 6 соединены с соответствующими входами сумматора 7 разрядных токов, выход которого подключен к первой выходной клемме ЦУДТ 2. Вторые выходы разрядных ключей 6 соединены с шиной Корпус . Вторые входные клеммы ЦУДТ 2 по;п(ключены к входу блока 8 управлений, первый выход которого соединен с управляющими входами переключателей 5 и второй выходной клеммой ЦУДТ 2. Образцовый ток Зд , поступающий с выхода источника 1 тока, делится в блоке 4.1 пополам и поступает на два входа переключателя 5.1. Одна половина тока Зд используется в качестве разрядного тока, соответствующего старшему разряду входного кода, и поступает через переключатель 5.1 и ключ 6.1 на один.из входов сумматора 7, либо на шину Корпус в зависимости от .значения кодовой цифры в старшем разряде входного кода. Вторая половина тока проходит через переключатель 5.1 и делится пополам в блоке 4.2. Таким образом, на входы переключателя 5.2 поступают токи, номинальные значения которых равны 2 fUQ Один из этих токов через ключ 6,2 может быть подключен на вход сумматора 7, а другой поступает в следующий младший разряд для деления пополс1М. Состояние ключей 6 зависит от кода, поступающего на вход блока 8 управления, С помощью переключателей можно менять местами выходы соответствующих блоков 5 деления токов пополам. Управляющие сигналы на переключатели 5 поступают с блока 8. Цифроаналогрвое преобразование производится за два такта. На первом такте преобразование прои заводится при одном состоянии переключателей .5, а на втором такте - при противоположном состоянии. Таким образом, на втором такте выходы блоков 4 деления тока пополам в каждом разряде меняются местами. При этом погрешность предлагаемого ЦАП практически не зависит от погрешностей деления токов пополам. По окончании первого такта цифроаналогового преобразования напряжение с выхода сумматора 7 (фиг.2) поступает на блок 9 выборки-хранения, запоминается и поступает на | первый вход аналогового сумматора 10.

После этого.сигнал с выхода блока 8 отключает сумматор 7 от блока 9. По окончании второго такта цифроаналогового преобразования напряжение с выхода сумматора 7 поступает на второй вход аналогового Сумматора 10. Таким образом, по окончании второго такта на первый вход аналогового сумматора 10 поступает результат цифроангшогового преобразования, полученный по окончании

первого такта, а на второй вход результат, полученный по окончании второго такта.

таким образом, по сравнению с иэвестными устройствами предлагаемое

устройство из-за введения нового элемента (управляемого сумматора) позволяет преобразовывать входной код 6 аналоговый выходной сигнал эа меньшее число тактов, т.е. его быстродействие выше, чем у известного.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1691962A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Цифроаналоговый преобразовательС АВТОМАТичЕСКОй КОРРЕКциЕй НЕли-НЕйНОСТи | 1979 |

|

SU809549A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| Цифро-аналоговый множительно- ТРигОНОМЕТРичЕСКий пРЕОбРАзОВАТЕль | 1978 |

|

SU822223A1 |

ЦИФРОАЯАЛОГОВЫЙ ПРЕОВРАЭО-П ВАТЕЛЬ, содеркао ий источйик тока, выход которого подключен к первому входу цифроуправляемого делителя тока, второй вход которого соединен с шиной входного кода, отличающийся тем, что, с целью повышения быстродействия, в него введен управляемый суьелатор, первый вход которого соединен с первым выходом цифроуправляемого делителя тока, второй вход - с вторьил выходом цифроуправляемого делителя тока, а выход - с выходной шиной. S

.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бёшакай В.Г | |||

| и др | |||

| Интегральные схемы, АЦП и ЦАП | |||

| М., Энергия, 1978, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IEEE Jprnal of Solid.-State Circuts, 1976, 6, p | |||

| Способ десульфитации фруктовых и ягодных соков, напитков и т.п. продуктов | 1921 |

|

SU795A1 |

Авторы

Даты

1983-12-30—Публикация

1981-03-12—Подача