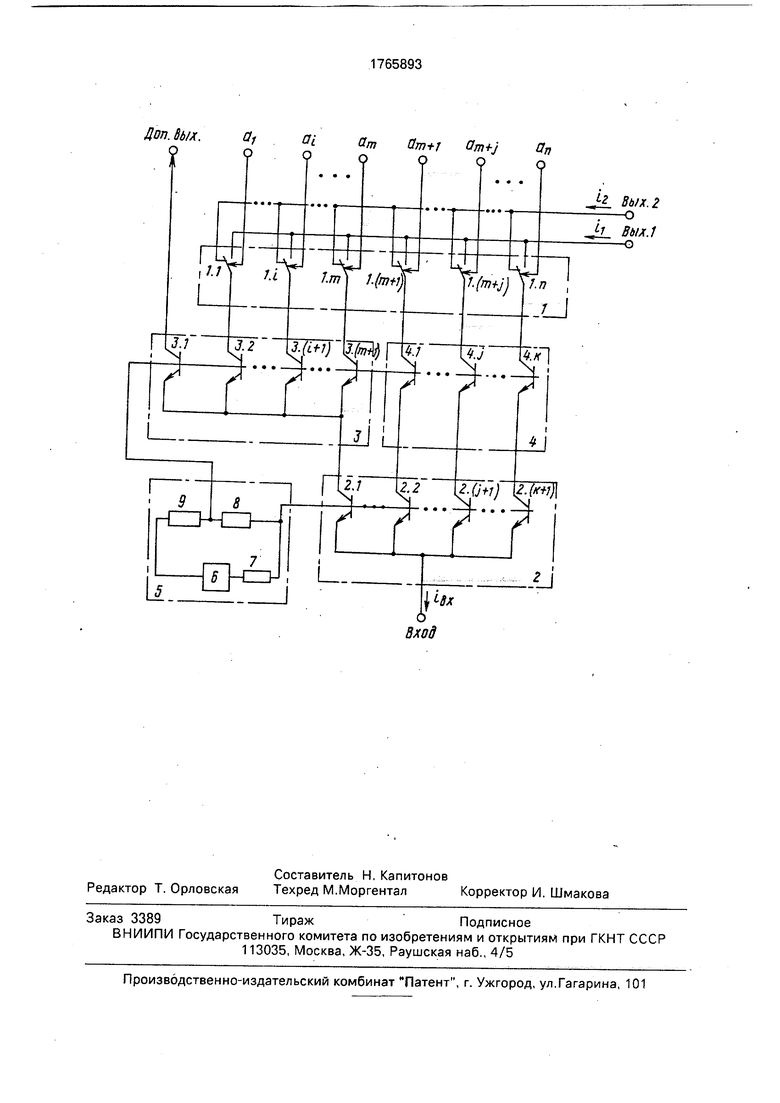

ключатели 1.1-1.m, соответствующие младшим разрядам, поступают в первую либо вторую выходную шину ЦАП.

Коллекторный ток первого транзистора 3.1 второго блока 3 деления тока поступает на дополнительный выход ЦАП и может быть использован для наращивания разрядности ЦАП. Если этого не требуется, то коллектор транзистора 3.1 должен быть соединен с шиной нулевого потенциала.

Режим транзисторов первого 2 и второго 3 блоков деления тока, а также блока 4 транзисторов задается источником 5 опорного напряжения. Напряжения смещения без транзисторов блока 2 и блоков 3 и 4 формируются делением напряжения источника 6 резистивным делителем, выполненным на резисторах 7-9.

На первом выходе ЦАП формируется ток, пропорциональный значению управляющего кода, а на втором выходе - инверсному значению управляющего кода.

Блок 4 транзисторов обеспечивает выравнивание частотных характеристик трактов прохождения сигналов старших разрядов относительно сигналов младших разрядов, что обеспечивает уменьшение линейных искажений выходного сигнала ЦАП.

Формула изобретения Умножающий цифроаналоговый преобразователь, содержащий п разрядных переключателей, управляющие входы которых являются входной шиной управляющего кода, первый выход первого разрядного переключателя объединен с первыми выходами остальных разрядных переключателей и является первой выходной шиной, второй выход первого разрядного переключателя

объединен с вторыми выходами остальных разрядных переключателей и является второй выходной шиной, первый и второй блоки деления токов, выполненные соответственно в виде k+1 и т+1 транзисторов с различными площадями эмиттеров, где k+m п; база первого транзистора первого блока деления тока объединена с базами остальных транзисторов первого блока де0 ления тока и подключена к первому выходу источника опорного напряжения, второй выход которого соединен с базами транзисторов второго блока деления тока, коллектор (i+1)-ro транзистора которого соединен

5 с информационным входом 1-го разрядного

переключателя, где 1 1,2т, коллектор

первого транзистора первого блока деления тока соединен с эмиттерами транзисторов второго блока деления тока, отличаю0 щ и и с я тем, что, с целью повышения точности за счет уменьшения линейных искажений выходного сигнала, в него введен блок из k транзисторов, эмиттер j-ro транзистора которого соединен с коллектором

5 Q+1)-ro транзистора первого блока деления тока, а коллектор соединен с информационным входом (m+j)-ro разрядного переключателя, где j 1, 2 k, база первого

транзистора блока из k транзисторов объе0 динена с базами остальных транзисторов блока из k транзисторов и соединена с вторым выходом источника опорного напряжения, эмиттер первого транзистора первого блока деления тока объединен с

5 эмиттерами остальных транзисторов первого блока деления тока и является входной шиной аналогового сигнала, коллектор первого транзистора второго блока деления тока является дополнительной выходной

0 шиной.

Яол.бь,. a, at aja am+r Oa Qn

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-ток | 1987 |

|

SU1499498A1 |

| Делитель тока | 1988 |

|

SU1674375A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (АЦП) | 1996 |

|

RU2110887C1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1691962A1 |

| Цифроаналоговый преобразователь | 1973 |

|

SU661778A1 |

| Цифро-аналоговый преобразователь | 1979 |

|

SU828398A1 |

| Преобразователь код-ток | 1984 |

|

SU1246378A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1102030A2 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU1019622A1 |

J.m

j.2 ЛТр7Ш)ГЖ ГО-fe l

...4

re/ to

i

l-(m+i.

l.(m+j)

In

..U

N

4- .

/

о Вход

..и

Авторы

Даты

1992-09-30—Публикация

1988-12-30—Подача