О

VI

Os

о ю

ю

Изобретение относится к технике связи, может использоваться в приемной части аппаратуры передачи дискретной информации для формирования корректирующего уровня напряжения и является усовершенствованием изобретения по авт. св. ISfc 1092749.

Цель изобретения - повышение точности формирования путем учета искажений смежных информационных импульсов.

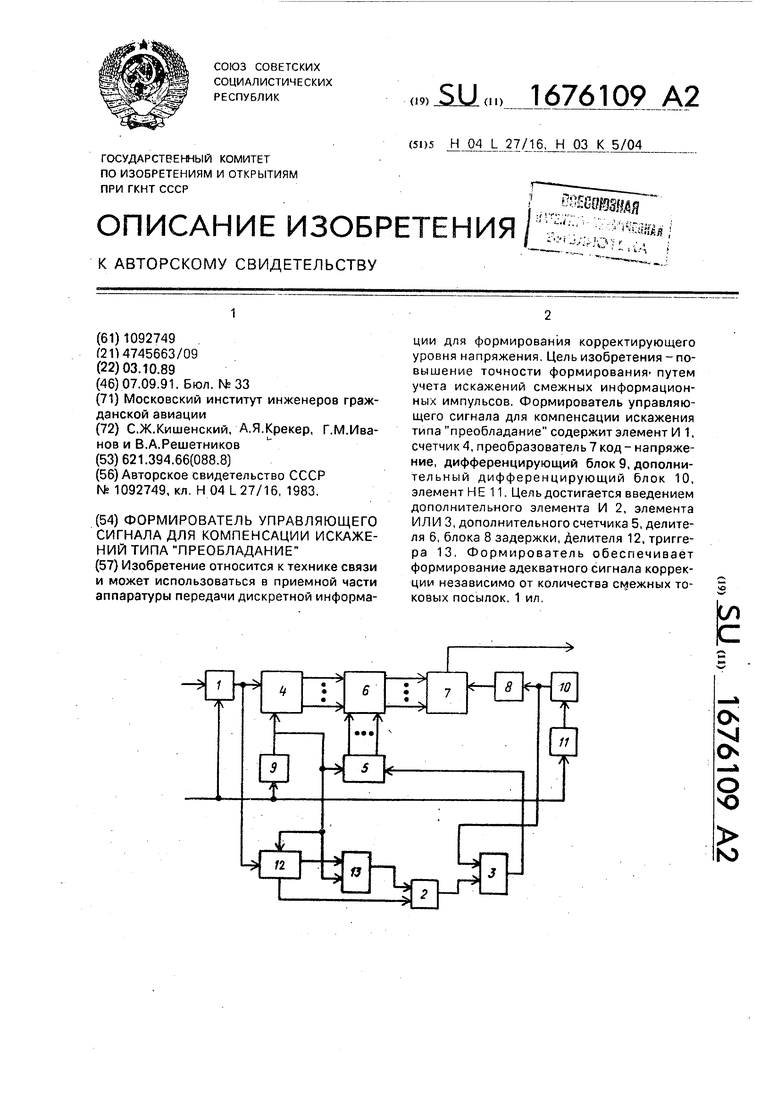

На чертеже изображена структурная электрическая схема предложенного формирователя.

Формирователь содержит элемент И 1, дополнительный элемент И 2, элемент ИЛИ 3, счетчик 4, дополнительный счетчик 5, делитель 6, преобразователь 7 код - напряжение, блок 8-задержки, дифференцирующий блок 9, дополнительный дифференцирую- щий блок 10, элемент НЕ 11, делитель 12 частоты, триггер 13.

Формирователь работает следующим образом.

На тактовый вход формирователя (один вход элемента И 1) поступает последовательность тактовых импульсов высокой частоты. На информационный вход формирователя (второй вход первого элемента И 1, дифференцирующего блока 9 и элемента НЕ 11) поступают информационные импульсы с номинальной длительностью TO , причем г0 N Твч, где N - заранее выбранное отношение (коэффициент). Отклонения номинальной длительно- сти характеризуют величину преобладаний в принимаемых элементах сообщения и значение корректирующего (управляющего) сигнала.

В момент смены на информационном входе уровня напряжения логического О на уровень логической 1 на выходе дифференцирующего блока 9 формируется короткий импульс, устанавливающий в нулевое (исходное) состояние счетчики 4,5, а также делитель 12 и триггер 13. При этом уровень напряжения на выходе преобразователя 7 остается неизменным, так как не изменяется код числа, записанный в него ранее. В течение времени, равного длительности по- ложительного сигнала (совокупности смежных единичных информационных посылок) на информационном входе, элемент И 1 открыт этим сигналом, и импульсы высокой частоты с тактового входа поступают на вы- ход элемента И 1 и далее на входы счета счетчика 4 и делителя 12. Содержимое счетчика 4 после окончания денного интервала пропорционально длительности входного

информационного сигнала положительной полярности.

На выходе элемента НЕ 11 формируется последовательность, инверсная относительно входного информационного сигнала, которая поступает на вход дифференцирующего блока 10, с выхода которого снимается импульс в момент смены на информационном входе формирователя уровня логической 1 на уровень логического О (т.е. в момент окончания положительного информационного импульса). Таким образом, информационная посылка, длительность которой может быть искажена преобладанием, начинается с положительного перепада напряжения (фронта) и заканчивается отрицательным перепадом напряжения. При этом между положительным и отрицательным перепадами могут располагаться не одна, а несколько смежных положительных элементарных посылок. В этом случае необходимо скорректировать величину вычисляемого преобладания и управляющего сигнала в зависимости от количества смежных посылок.

Предположим, что отношение длительности информационной посылки, не искаженной преобладаниями, к периоду тактовых импульсов высокой частоты равно N. Коэффициент деления делителя 12 выбирается равным этому отношению, т.е. N. Сигнал с первого выхода делителя 12 поступает на вход установки в единичное состояние триггера 13 в момент поступления на вход делителя N импульсов (сигнализируя об окончании неискаженной посылки). Сигналы с второго выхода делителя 12 формируются в моменты времени, когда на его вход поступает N+I-N/2 импульсов (I 1.2,...), что соответствует середине (половине) неискаженной посылки. Если неискаженная посылка должна иметь длительность т0, то при поступлении на вход формирователя информационного сигнала длительностью в интервале от О до 1,5г0 принимается решение о поступлении однократной посылки, при интервале длительностей поступившего сигнала от 1,5-ть до 2,5- Т0 принимается решение о приходе двух смежных положительных посылок, и т.д. В общем случае при длительности принятого сигнала в интервале от (1-0,5) То до 0+0,5) -г0 , где 1 1,2

принимается решение о поступлении на информационный вход 1-кратной смежной положительной посылки.

Если длительность принимаемого положительного сигнала меньше Т0 , то при поступлении на информационный вход отрицательного фронта с выхода дифференцирующего блока 10 сигнал поступает на один вход элемента ИЛИ 3 и с его выхода далее на счетный вход счетчика 5, который переходит в состояние 1 (единица в младшем разряде). Этот же импульс с некоторой задержкой, пройдя через блок 8, передним фронтом сбрасывает число, хранящееся в памяти преобразователя 7, а задним фронтом осуществляет гапись в преобразователь 7 нового числа, сформированного к этому моменту на выходе делителя 6. На входы делителя с выходов счетчика 4 поступает код числа импульсов высокой частоты, записанных в интервале положительного входного сигнала на информационном входе формирователя, а на входы делителя 8 со счетчика 5 поступает код числа, представляющего количество смежных положительных посылок. С выхода делителя 6 снимается частное от деления чисел, записанных соответственно в счетчиках 4,5, в виде кода, который и записывается как новый код числа в преобразователь 7. При принятии решения о приходе одиночной посылки информационного сигнала (счетчик 5 содержит код числа 1, как описано выше) формирователь работает аналогично устройству-прототипу.

Если в течение первого т0 не поступил отрицательный фронт информационного сигнала, то сигналом с первого выхода делителя 12 (в момент поступления на вход делителя N-ro импульса такта) устанавливается в единичное состояние триггер 13, подготавливая счет числа смежных посылок при отсутствии в них отрицательного фронта информационного сигнала. В дальнейшем сигналы с второго выхода делителя 12 (формирующиеся, как указано выше, в моменты поступления

N -I-я- импульсов (i 1,2,...), соответствующие серединам очередных посылок - второй, третьей и т.д., проходят через элемент И 2 (на его второй вход теперь поступает разрешающий сигнал с выхода триггера 13) и через элемент ИЛИ 3 на счетный вход счетчика 5. Включение триггера 13 необходимо для того, чтобы не допустить подсчета первого сигнала с выхода (второго) делителя 12 счетчиком 5.

Таким образом, к моменту поступления отрицательного фронта по информационному входу формирователя, знаменующему окончание посылки (или совокупности смеж: нь,хинформационных посылок), в счетчике 4 содержится код длительности этой посылки (или совокупности), а в счетчике 5 - оценка

и числа посылок в совокупности. Делитель 6 осуществляет деление содержимого счетчика 4 на содержимое счетчика 5, и частное от этого деления представляет

собой код, соответствующий искажению длительности, приходящемуся на одну элементарную посылку.

При отсутствии преобладаний на выходе формирователя (а именно преобразователя код - напряжение) устанавливается некоторый неизменный сигнал, не зависящий от количества смежных информационных посылок. В случае поступления на вход фоомирователя импульсов (посылок),

характеризующихся токовыми преобладаниями (удлинение- , положительных интервалов за счет отрицательных), по их окончании на выходе преобразователя 7 устанавливается уровень напряжения, больший по величине, чем для неискаженных посылок. В случае бестоковыл преобладаний на выходе преобразователя 7 устанавливается уровень аналогового сигнала, меньший по величине, чем уровень сигнала для неискаженных посылок. Таким образом, отклонения уровня выходного сигнала от некоторого номинального значения характеризуют знак и величину преобладания, вследствие чего данный сигнал

может служить для коррекции преобладаний при передаче полезной информации по каналам связи.

При этом в отличие от прототипа предлагаемый формирователь обеспечивает

формирование адекватного сигнала коррекции независимо от количества смежных токовых посылок (именно по токовым посылкам и формируется корректирующий сигнал), поскольку в нем осуществляется

приведение выходного сигнала к одной элементарной токовой посылке независимо от их количества, как описано выше.

45

Формула изобретения

Формирователь управг иощего сигнала для компенсации искажений типа преобладание по авт. св. № 1092749, отличающийся тем, что, с целью повыше0 ния точности формирования путем учета искажений смежных информационных импульсов, в него введены делитель, блок задержки, дополнительный счетчик, делитель частоты, триггер, дополнительный эле5 мент И и элемент ИЛИ, причем выходы счетчика соединены с информационными входами преобразователя код - напряжение через делитель, выход дополнительного дифференцирующего блока соединен со сбросовым входом преобразователя код напряжение через блок задержки, выход элемента И соединен с информационным входом делителя частоты, вход сброса которого, вход сброса триггера и счетный вход дополнительного счетчика соединены с выходом дифференцирующего блока, первый выход делителя частоты соединен с установочным входом триггера, выход которого соединен с первым входом дополнительного

элемента И, второй вход и выход которого соединены соответственно с вторым выходом делителя частоты и первым входом элемента ИЛИ, второй вход которого соединен с выходом дополнительного дифференцирующего блока, выход элемента ИЛИ соединен с входом сброса дополнительного счетчика, выходы которого соединены с установочными входами делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями | 1981 |

|

SU1125760A2 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Устройство для компенсации искажений типа "преобладание | 1983 |

|

SU1113899A1 |

| Формирователь управляющего сигнала для компенсации искажений типа "преобладание | 1983 |

|

SU1092749A1 |

| Устройство для измерения краевых искажений двоичных сигналов типа "преобладаний | 1984 |

|

SU1215186A1 |

| УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ ФЛУКТУИРУЮЩИХ ИМПУЛЬСНЫХ СИГНАЛОВ | 1993 |

|

RU2060509C1 |

| Устройство для имитации краевых искажений телеграфных сигналов | 1984 |

|

SU1177934A1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

| Устройство для контроля работы трансмиттера | 1980 |

|

SU926660A1 |

| Устройство для измерения преобладаний дискретных сигналов | 1985 |

|

SU1285611A1 |

Изобретение относится к технике связи и может использоваться в приемной части аппаратуры передачи дискретной информации для формирования корректирующего уровня напряжения Цель изобретения - повышение точности формирования- путем учета искажений смежных информационных импульсов. Формирователь управляющего сигнала для компенсации искажения типа преобладание содержит элемент И 1, счетчик 4, преобразователь 7 код - напряжение, дифференцирующий блок 9, дополни- тельный дифференцирующий блок 10, элемент НЕ 11 Цель достигается введением дополнительного элемента И 2, элемента ИЛИ 3, дополнительного счетчика 5, делителя 6, блока 8 задержки, делителя 12, триггера 13. Формирователь обеспечивает формирование адекватного сигнала коррекции независимо от количества смежных токовых посылок. 1 ил

| Формирователь управляющего сигнала для компенсации искажений типа "преобладание | 1983 |

|

SU1092749A1 |

Авторы

Даты

1991-09-07—Публикация

1989-10-03—Подача