Изобретение относится к измерит тельной технике и может быть использовано в автоматизированных системах для определения максимальных искажений длительностей импульсов в сериях телеграфных посылок.

Цель изобретения - .повышение точности измерения искажения длительности импульсов.

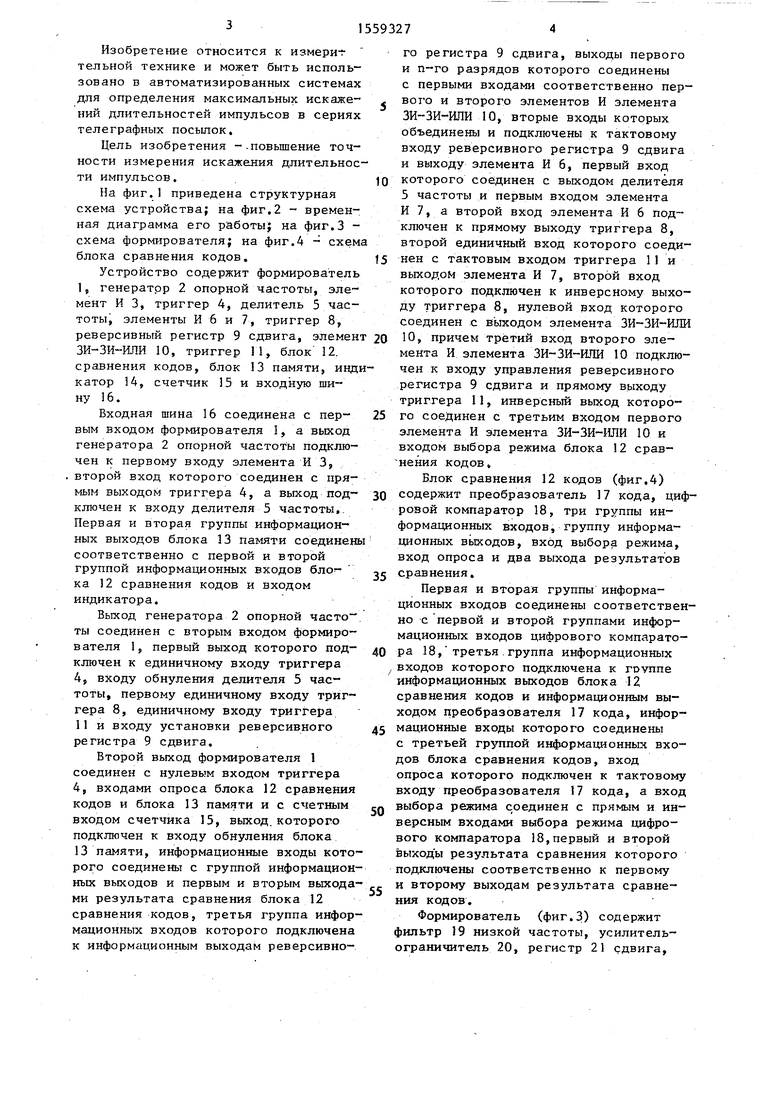

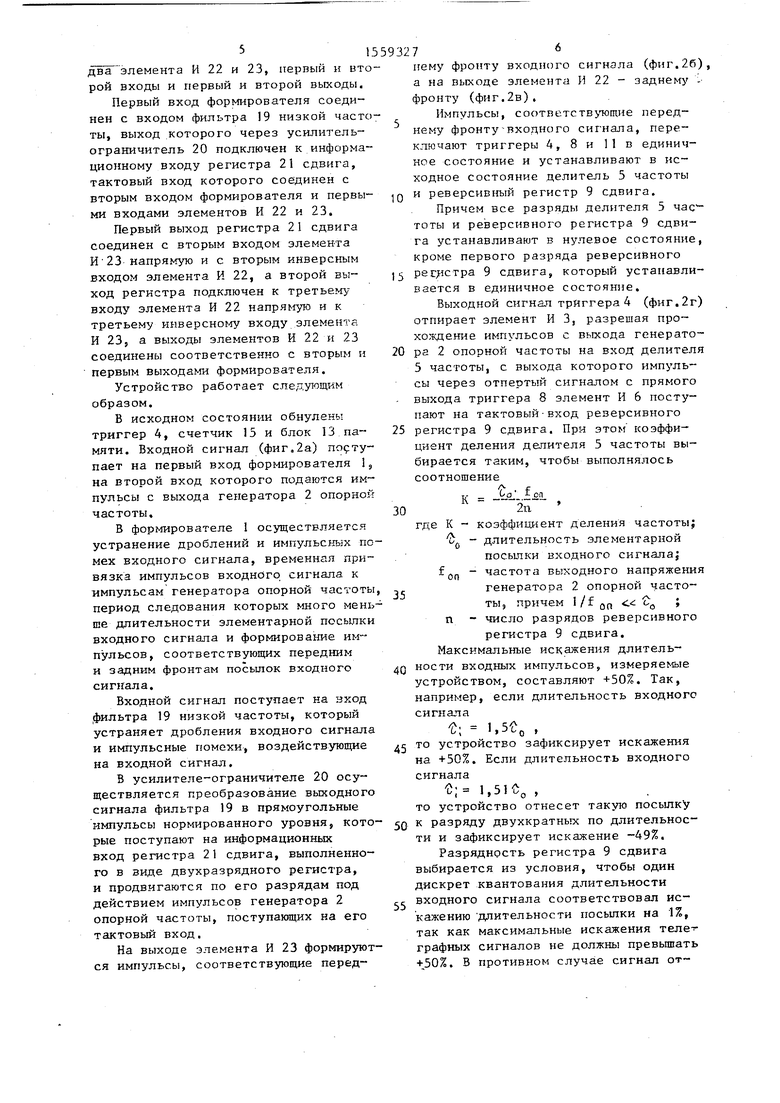

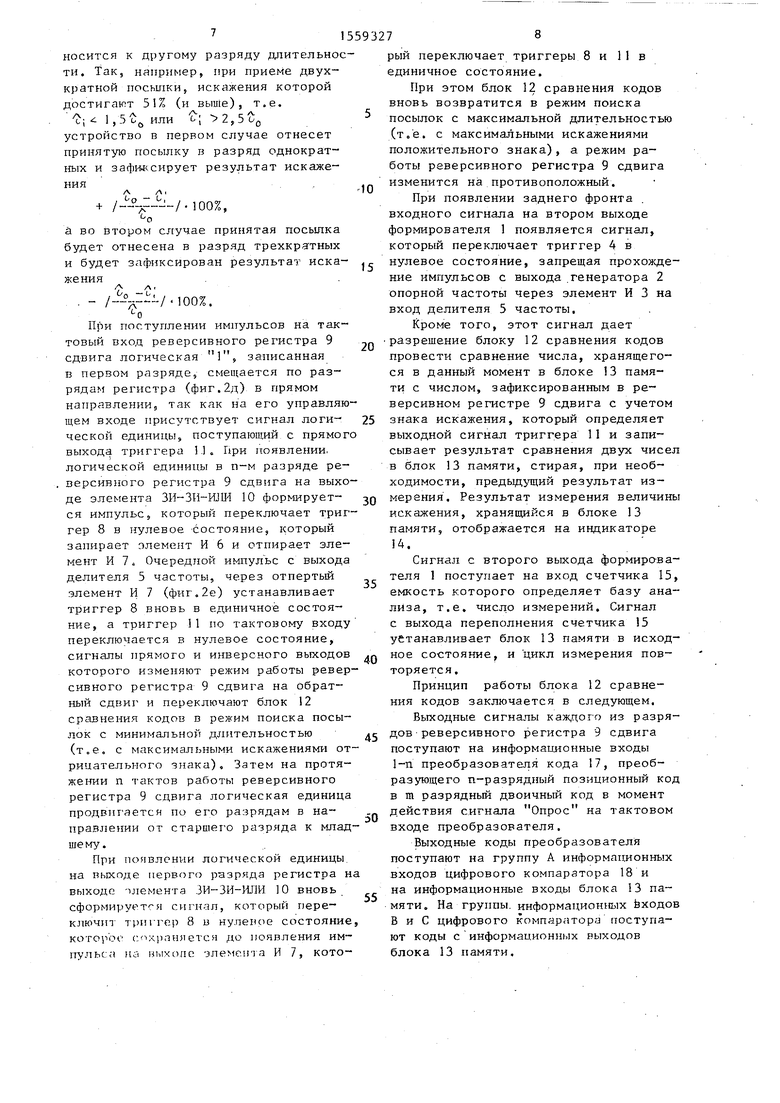

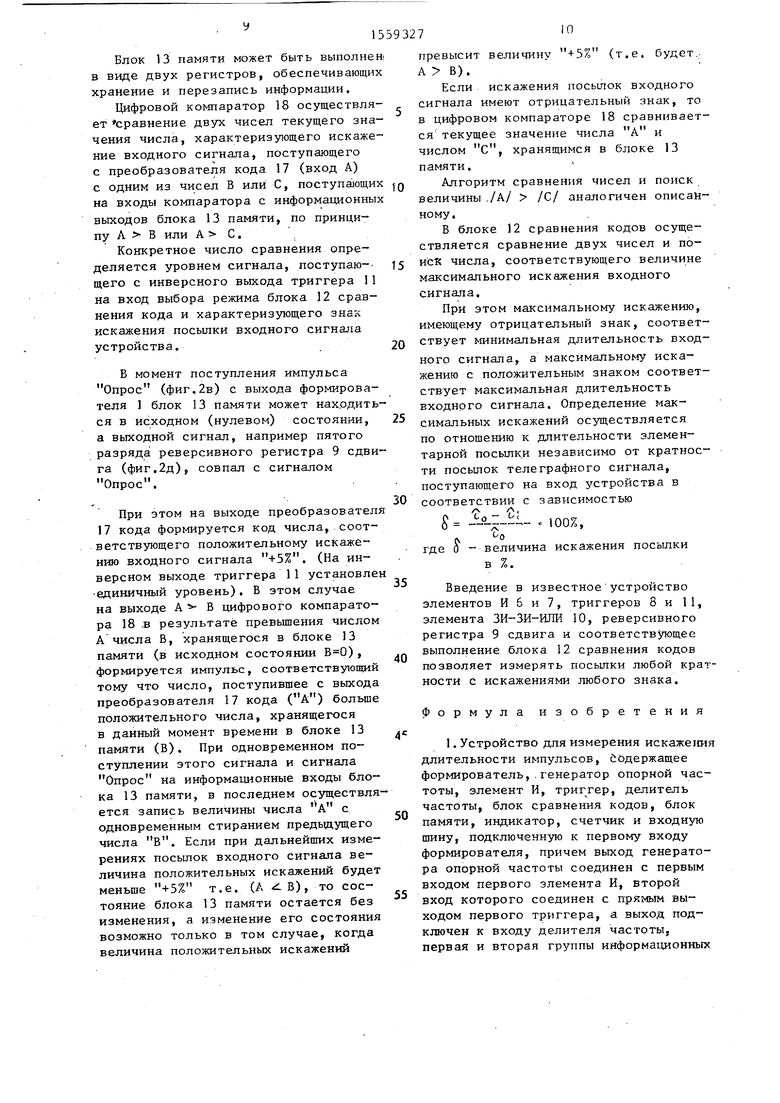

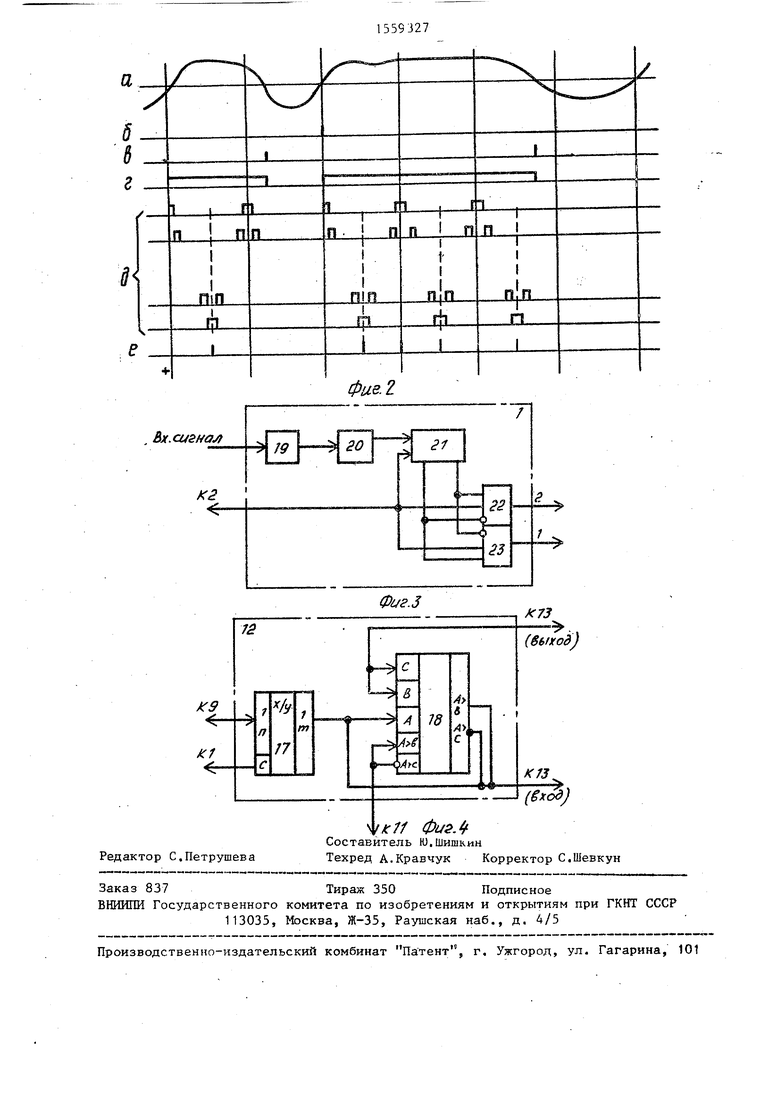

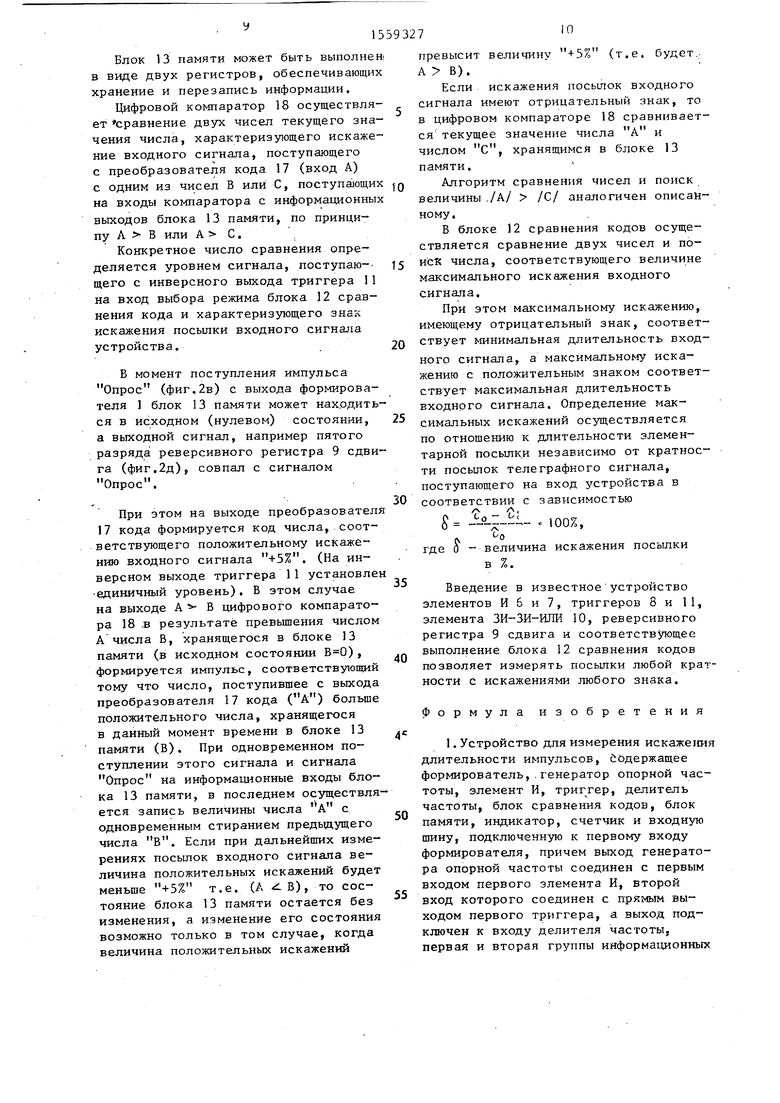

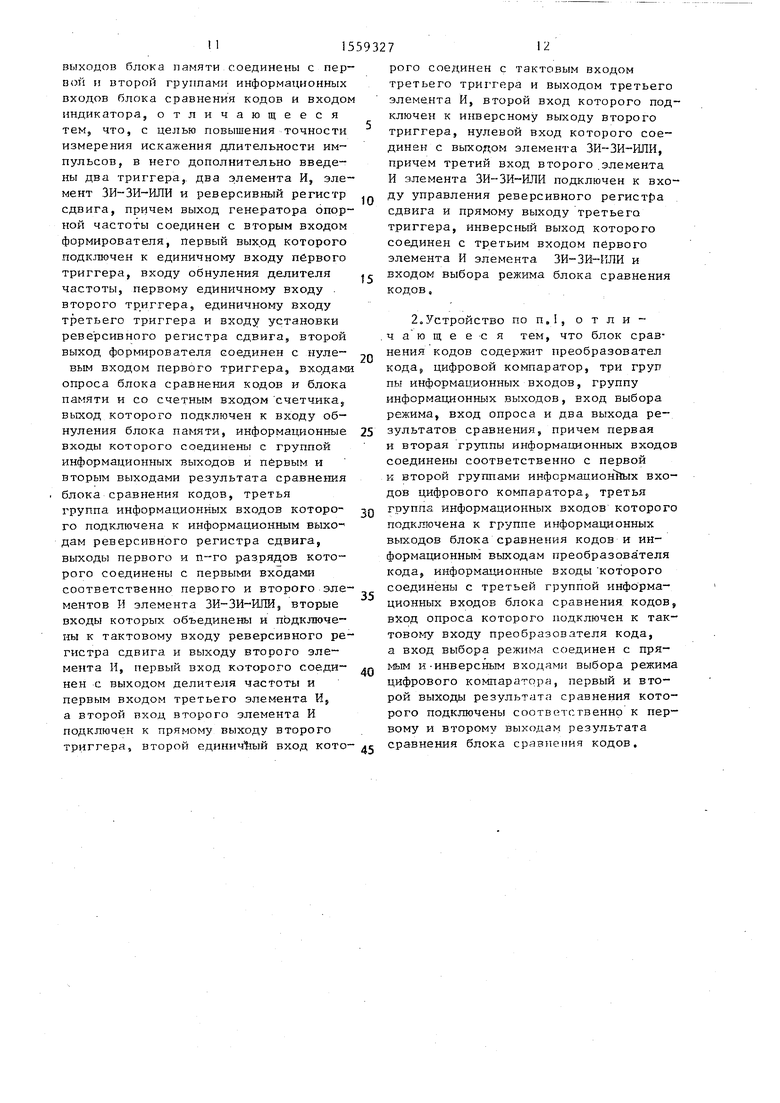

На фиг.1 приведена структурная схема устройства; на фиг.2 - временная диаграмма его работы} на фиг.З - схема формирователя; на фиг.4 - схем блока сравнения кодов.

Устройство содержит формирователь 1, генератор 2 опорной частоты, элемент И 3, триггер 4, делитель 5 частоты, элементы И 6 и 7, триггер 8, реверсивный регистр 9 сдвига, элемен ЗИ-ЗИ-ИЛЙ 10, триггер 11, блок 12. сравнения кодов, блок 13 памяти, индкатор 14, счетчик 15 и входную шину 16.

Входная шина 16 соединена с первым входом формирователя I, а выход генератора 2 опорной частоты подключен к первому входу элемента ИЗ, второй вход которого соединен с прямым выходом триггера 4, а выход подключен к входу делителя 5 частоты. Первая и вторая группы информационных выходов блока 13 памяти соединены соответственно с первой и второй группой информационных входов блока 12 сравнения кодов и входом индикатора.

Выход генератора 2 опорной часто ты соединен с вторым входом формирователя 1, первый выход которого подключен к единичному входу триггера 4, входу обнуления делителя 5 частоты, первому единичному входу триггера 8, единичному входу триггера 11 и входу установки реверсивного регистра 9 сдвига.

Второй выход формирователя 1 соединен с нулевым входом триггера 4, входами опроса блока 12 сравнения кодов и блока 13 памяти и с счетным входом счетчика 35, выход, которого подключен к входу обнуления блока 13 памяти, информационные входы которого соединены с группой информационных выходов и первым и вторым выходами результата сравнения блока 12 сравнения кодов, третья группа информационных входов которого подключена к информационным выходам реверсивного регистра 9 сдвига, выходы первого и п-го разрядов которого соединены с первыми входами соответственно пер-

вого и второго элементов И элемента ЗИ-ЗИ-ИЛИ 10, вторые входы которых объединены и подключены к тактовому входу реверсивного регистра 9 сдвига и выходу элемента И 6, первый вход

которого соединен с выходом делителя 5 частоты и первым входом элемента И 7, а второй вход элемента И 6 подключен к прямому выходу триггера 8, второй единичный вход которого соеди5 нен с тактовым входом триггера 11 и выходом элемента И 7, второй вход которого подключен к инверсному выходу триггера 8, нулевой вход которого соединен с выходом элемента ЗИ-ЗИ-ИЛИ

0 10 причем третий вход второго элемента И элемента ЗИ-ЗИ-ИЛИ 10 подключен к входу управления реверсивного регистра 9 сдвига и прямому выходу триггера 11, инверсный выход которо5 го соединен с третьим входом первого элемента И элемента ЗИ-ЗИ-ИЛИ 10 и входом выбора режима блока 12 сравнения кодов.

Блок сравнения 12 кодов (фиг.4)

0 содержит преобразователь 17 кода, цифровой компаратор 18, три группы информационных входов, группу информационных выходов, вход выбора режима, вход опроса и два выхода результатов

5 сравнения.

Первая и вторая группы информационных входов соединены соответственно с первой и второй группами информационных входов цифрового компарато0 ра 18, третья группа информационных / входов которого подключена к группе информационных выходов блока 12 сравнения кодов и информационным выходом преобразователя 17 кода, инфор5 мационные входы которого соединены с третьей группой информационных входов блока сравнения кодов, вход опроса которого подключен к тактовому входу преобразователя 17 кода, а вход выбора режима соединен с прямым и инверсным входами выбора режима цифрового компаратора 18,первый и второй выходы результата сравнения которого подключены соответственно к первому и второму выходам результата сравне0

5

ния кодов.

Формирователь (фиг.З) содержит фильтр 19 низкой частоты, усилитель- ограничитель 20, регистр 21 сдвига,

5

и 23,

1

два элемента И 22 и 23, первый и второй входы и первый и второй выходы.

Первый вход формирователя соединен с входом фильтра 19 низкой частоты, выход которого через усилитель- ограничитель 20 подключен к информационному входу регистра 21 сдвига, тактовый вход которого соединен с вторым входом формирователя и первыми входами элементов И 22 и 23.

Первый выход регистра 21 сдвига соединен с вторым входом элемента И 23 напрямую и с вторым инверсным входом элемента И 22, а второй выход регистра подключен к третьему входу элемента И 22 напрямую и к третьему инверсному входу элемента И 23, а выходы элементов И 22 и 23 соединены соответственно с вторым и первым выходами формирователя.

Устройство работает следующим образом.

В исходном состоянии обнулены триггер 4, счетчик 15 и блок 13 памяти. Входной сигнал (фиг.2а) поступает на первый вход формирователя ls на второй вход которого подаются импульсы с выхода генератора 2 опорной частоты,

В формирователе 1 осуществляется устранение дроблений и импульсных помех входного сигнала, временная привязка импульсов входного сигнала к импульсам генератора опорной частоты период следования которых много меньше длительности элементарной посылки входного сигнала и формирование импульсов, соответствующих передним и задним фронтам посылок входного сигнала.

Входной сигнал поступает на вход фильтра 19 низкой частоты, который устраняет дробления входного сигнала и импульсные помехи, воздействующие на входной сигнал.

В усилителе-ограничителе 20 осуществляется преобразование выходного сигнала фильтра 19 в прямоугольные импульсы нормированного уровня, которые поступают на информационных вход регистра 21 сдвига, выполненного в виде двухразрядного регистра, и продвигаются по его разрядам под действием импульсов генератора 2 опорной частоты, поступающих на его тактовый вход.

На выходе элемента И 23 формируются импульсы, соответствующие перед-

1559327

0

0

5

нему фронту входного сигнала (фиг.26), а на выходе элемента И 22 - заднему - фронту (фиг.2в).

Импульсы, соответствующие переднему фронту-вхоцного сигнала, переключают триггеры 4, 8 и 11 в единичное состояние и устанавливают в исходное состояние делитель 5 частоты и реверсивный регистр 9 сдвига.

Причем все разряды делителя 5 частоты и реверсивного регистра 9 сдвига устанавливают в нулевое состояние, кроме первого разряда реверсивного регистра 9 сдвига, который устанавливается в единичное состояние.

Выходной сигнал триггера 4 (фнг.2г) отпирает элемент И 3, разрешая прохождение импульсов с выхода генератора 2 опорной частоты на вход делителя 5 частоты, с выхода которого импульсы через отпертый сигналом с прямого выхода триггера 8 элемент И 6 поступают на тактовый-вход реверсивного регистра 9 сдвига. При этом коэффициент деления делителя 5 частоты выбирается таким, чтобы выполнялось соотношение

30

К

JЈP-

2п

5

где К - коэффициент деления частоты; / о

ОП

длительность элементарной посылки входного сигнала; частота выходного напряжения генератора 2 опорной частоты, причем

1/f

on

Сл

п

число разрядов реверсивного

регистра 9 сдвига. Максимальные искажения длительности входных импульсов, измеряемые устройством, составляют +50%. Так, например, если длительность входного сигнала

Ј;

1,5С

о

то устройство зафиксирует искажения на +50%. Если длительность входного

сигнала

«;1,51

о

то устройство отнесет такую посыпку к разряду двухкратных по длительности и зафиксирует искажение -49%. Разрядность регистра 9 сдвига выбирается из условия, чтобы один дискрет квантования длительности входного сигнала соответствовал искажению длительности посылки на 1%, так как максимальные искажения телет графных сигналов не должны превышать +50%. В противном случае сигнал относится к другому разряду длительности. Так, например, при приеме двухкратной посылки, искажения которой достигают 51% (и выше), т.е.

Ъ

,5 с-0 или ь; 2,5 и0

устройство в первом случае отнесет принятую посылку в разряд однократных и зафиксирует результат искажения

+ /

Л

t-o

Л.

с/,

-10

Ъг

/100%,

а во втором случае принятая посыпка будет отнесена в разряд трехкратных и будет зафиксирован результат искажения

15

Л л.

Л

100%.

При поступлении импульсов на тактовый вход реверсивного регистра 9

it 1 ч

20

35

сдвига логическая 1, записанная в первом разряде, смещается по разрядам регистра (фиг.2д) в прямом направлении, так как на его управляющем входе присутствует сигнал логи- 25 ческой единицы, поступающий с прямого выхода триггера 11„ При появлении, логической единицы в п-м разряде реверсивного регистра 9 сдвига на выходе элемента ЗИ-ЗИ-ИЛИ 10 формирует- 0 ся импульс, который переключает триггер 8 в нулевое состояние, который запирает элемент И 6 и отпирает элемент И 7. Очередной импульс с выхода делителя 5 частоты, через отпертый элемент И 7 (фиг.2е) устанавливает триггер 8 вновь в единичное состояние, а триггер 11 по тактовому входу переключается в нулевое состояние, сигналы прямого и инверсного выходов которого изменяют режим работы реверсивного регистра 9 сдвига на обратный сдвиг и переключают блок 12 сравнения кодов в режим поиска посылок с минимальной длительностью (т.е. с максимальными искажениями отрицательного знака), Затем на протяжении п тактов работы реверсивного регистра 9 сдвига логическая единица продвигается по его разрядам в на- .. правлении от старшего разряда к младшему.

При появлении логической единицы на выходе первого разряда регистра на выходе ьчемента ЗИ-ЗИ-ИЛИ 10 вновь сформируется сигнал, который переключит тршгер 8 в нупеное состояние, которое с- 1,р,1няется до появления импульса на пыхопе -элемента И 7, кото15593278

рый переключает триггеры 8 и 11 в единичное состояние.

При этом блок 12 сравнения кодов вновь возвратится в режим поиска посылок с максимальной длительностью (т.е. с максимальными искажениями положительного знака), а режим работы реверсивного регистра 9 сдвига изменится на противоположный.

При появлении заднего фронта входного сигнала на втором выходе формирователя 1 появляется сигнал, который переключает триггер 4 в нулевое состояние, запрещая прохождение импульсов с выхода генератора 2 опорной частоты через элемент И 3 на вход делителя 5 частоты.

Кроме того, этот сигнал дает разрешение блоку 12 сравнения кодов провести сравнение числа, хранящегося в данный момент в блоке 13 памяти с числом, зафиксированным в реверсивном регистре 9 сдвига с учетом знака искажения, который определяет выходной сигнал триггера 11 и записывает результат сравнения двух чисел в блок 13 памяти, стирая, при необходимости, предыдущий результат измерения. Результат измерения величины искажения, хранящийся в блоке 13 памяти, отображается на индикаторе 14.

Сигнал с второго выхода формиро-ва- теля 1 поступает на вход счетчика 15, емкость которого определяет базу анализа, т.е. число измерений. Сигнал с выхода переполнения счетчика 15 устанавливает блок 13 памяти в исходное состояние, и цикл измерения повторяется.

Принцип работы блока 12 сравнения кодов заключается в следующем.

Выходные сигналы каждого из разрядов реверсивного регистра 9 сдвига поступают на информационные входы 1-п преобразователя кода 17, преобразующего n-разрядный позиционный код в m разрядный двоичный код в момент действия сигнала Опрос на тактовом входе преобразователя.

Выходные коды преобразователя поступают на группу А информационных входов цифрового компаратора 18 и на информационные входы блока 13 памяти. На группы информационных входов В и С цифрового компаратора поступают коды с информационных РЫХОДОВ блока 13 памяти.

40

55

Блок 13 памяти может быть выполнен в виде двух регистров, обеспечивающих хранение и перезапись информации.

Цифровой компаратор 18 осуществляет сравнение двух чисел текущего значения числа, характеризующего искажение входного сигнала, поступающего с преобразователя кода 17 (вход А) с одним из чисел В или С, поступающих на входы компаратора с информационных выходов блока 13 памяти, по принципу Л В или А С.

Конкретное число сравнения определяется уровнем сигнала, поступаю-- щего с инверсного выхода триггера 11 на вход выбора режима блока 12 сравнения кода и характеризующего знак искажения посылки входного сигнала устройства.

В момент поступления импульса Опрос (фиг,2в) с выхода формирователя 1 блок 13 памяти может находиться в исходном (нулевом) состоянии, а выходной сигнал, например пятого разряда реверсивного регистра 9 сдвига (фиг.2д), совпал с сигналом Опрос.

При этом на выходе преобразовател 17 кода формируется код числа, соответствующего положительному искажению входного сигнала +5%. (На инверсном выходе триггера 11 установле -единичный уровень), В этом случае на выходе А В цифрового компаратора 18 .в результате превышения числом А числа В, хранящегося в блоке 13 памяти (в исходном состоянии ), формируется импульс, соответствующий тому что число, поступившее с выхода преобразователя 17 кода (А) больше положительного числа, хранящегося в данный момент времени в блоке 13 памяти (В). При одновременном поступлении этого сигнала и сигнала Опрос на информационные входы блока 13 памяти, в последнем осуществляется запись величины числа А с одновременным стиранием предыдущего числа В. Если при дальнейших измерениях посылок входного сигнала величина положительных искажений будет меньше +5% т.е. (А В), то состояние блока 13 памяти остается без изменения, а изменение его состояния возможно только в том случае, когда величина положительных искажений

JQ

15 20

2530

93271П

превысит величину +5% (т.е. будет А В).

Если искажения посылок входного сигнала имеют отрицательный знак, то в цифровом компараторе 18 сравнивается текущее значение числа А и числом С, хранящимся в блоке 13 памяти.

Алгоритм сравнения чисел и поиск величины ./А/ /С/ аналогичен описанному.

В блоке 12 сравнения кодов осуществляется сравнение двух чисел и поиск числа, соответствующего величине максимального искажения входного сигнала.

При этом максимальному искажению, имеющему отрицательный знак, соответствует минимальная длительность входного сигнала, а максимальному искажению с положительным знаком соответствует максимальная длительность входного сигнала. Определение максимальных искажений осуществляется по отношению к длительности элементарной посылки независимо от кратности посылок телеграфного сигнала, поступающего на вход устройства в соответствии с зависимостью

8 «юо%,

ч °°

О - величина искажения посылки

в %.

где

5

0

0

5

Введение в известное устройство элементов И 6 и 7, триггеров 8 и И, элемента ЗИ-ЗИ-ШТИ 10, реверсивного регистра 9 сдвига и соответствующее выполнение блока 12 сравнения кодов позволяет измерять посылки любой кратности с искажениями любого знака.

Формула изобретения

1. Устройство для измерения искажения длительности импульсов, Содержащее формирователь, генератор опорной частоты, элемент И, триггер, делитель частоты, блок сравнения кодов, блок памяти, индикатор, счетчик и входную шину, подключенную к первому входу формирователя, причем выход генератора опорной частоты соединен с первым входом первого элемента И, второй вход которого соединен с прямым выходом первого триггера, а выход подключен к входу делителя частоты, первая и вторая группы информационных

Ч1

выходов блока памяти соединены с первой и второй группами информационных входов блока сравнения кодов и входо индикатора, отличающееся тем, что, с целью повышения точности измерения искажения длительности импульсов, в него дополнительно введены два триггера, два элемента И, элемент ЗИ-ЗИ-ИЛИ и реверсивный регистр сдвига, причем выход генератора опорной частоты соединен с вторым входом формирователя, первый выход которого подключен к единичному входу первого триггера, входу обнуления делителя частоты, первому единичному входу второго триггера, единичному входу третьего триггера и входу установки реверсивного регистра сдвига, второй выход формирователя соеди 1ен с нулевым входом первого триггера, входам опроса блока сравнения кодов и блока памяти и со счетным входом счетчика, выход которого подключен к входу обнуления блока памяти, информационные входы которого соединены с группой информационных выходов и первым и вторым выходами результата сравнения блока сравнения кодов, третья группа информационных входов которого подключена к информационным выхо- дам реверсивного регистра сдвига, выходы первого и п-го разрядов которого соединены с первыми входами соответственно первого и второго элементов И элемента ЗИ-ЗИ-ИЛИ, вторые входы которых объединены и подключены к тактовому входу реверсивного регистра сдвига и выходу второго элемента И, первый вход которого соединен с выходом делителя частоты и первым входом третьего элемента и, а второй вход второго элемента И подключен к прямому выходу второго триггера, второй единичный вход кото

0

5

932

0

5

0

5

0

712

рого соединен с тактовым входом третьего триггера и выходом третьего элемента И, второй вход которого подключен к инверсному выходу второго триггера, нулевой вход которого соединен с выходом элемента ЗИ-ЗИ-ИЛИ, причем третий вход второго элемента И элемента ЗИ-ЗИ-ИЛИ подключен к входу управления реверсивного регистра сдвига и прямому выходу третьего триггера, инверсный выход которого соединен с третьим входом первого элемента И элемента ЗИ-ЗИ-ИЛИ и входом выбора режима блока сравнения кодов,

2.Устройство по п,15 отличающееся тем, что блок сравнения кодов содержит преобразовател кода, цифровой компаратор, три труп пы информационных входов, группу информационных выходов, вход выбора режима, вход опроса и два выхода результатов сравнения, причем первая и вторая группы информационных входов соединены соответственно с первой и второй группами информационных входов цифрового компаратора5 третья гоуппа информационных входов которого подключена к группе информационных выходов блока сравнения кодов и информационным выходам преобразователя кода, информационные входы которого соединены с третьей группой информационных входов блока сравнения кодов, вход опроса которого подключен к тактовому входу преобразователя кода, а вход выбора режима соединен с прямым и-инверсным входами выбора режима цифрового компаратора, первый и второй выходы результата сравнения которого подключены соответственно к первому и второму выходам результата сравнения блока сравнения кодов.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Устройство для выделения маркера кадровой синхронизации | 1983 |

|

SU1095434A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом | 1987 |

|

SU1610600A1 |

| ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ С АВТОМАТИЧЕСКИМ СОГЛАСОВАНИЕМ СКОРОСТЕЙ ПЕРЕДАЧИ И ПРИЕМА | 2003 |

|

RU2249919C2 |

Изобретение относится к измерительной технике и может быть использовано в устройствах для определения искажений телеграфного сигнала. Целью изобретения является расширение функциональных возможностей путем поиска максимальных искажений длительности импульсов. Цель достигается введением в устройство для измерения искажений длительности импульсов элементов И 6,7, триггеров 8,11, элемента ЗИ-ЗИ-ИЛИ 10 и реверсивного регистра 9 сдвига. Устройство содержит также формирователь 1, генератор 2 опорной частоты, элемент И 3, триггер 4, делитель частоты 5, блок 13 сравнения кодов, блок 13 памяти, индикатор 14, счетчик 15 и входную шину 16. 4 ил.

| Устройство для контроля длительностителеграфных посылок | 1973 |

|

SU508953A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство измерения длительности импульсов | 1974 |

|

SU516187A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-23—Публикация

1988-01-07—Подача