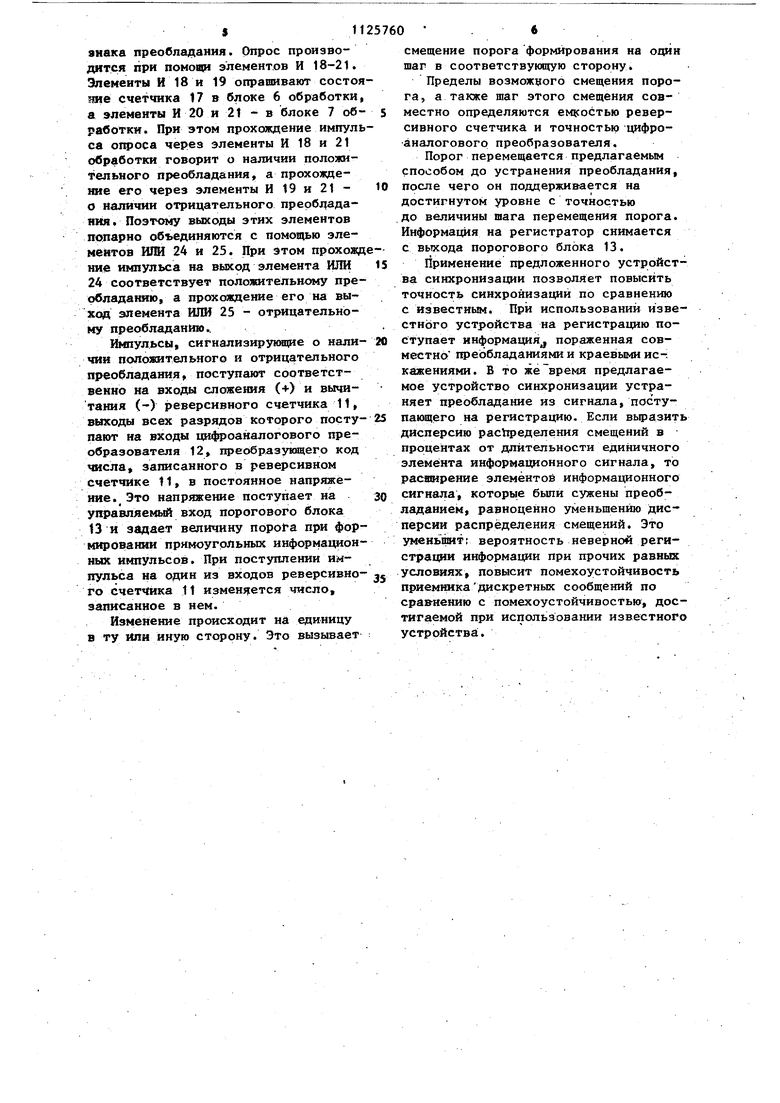

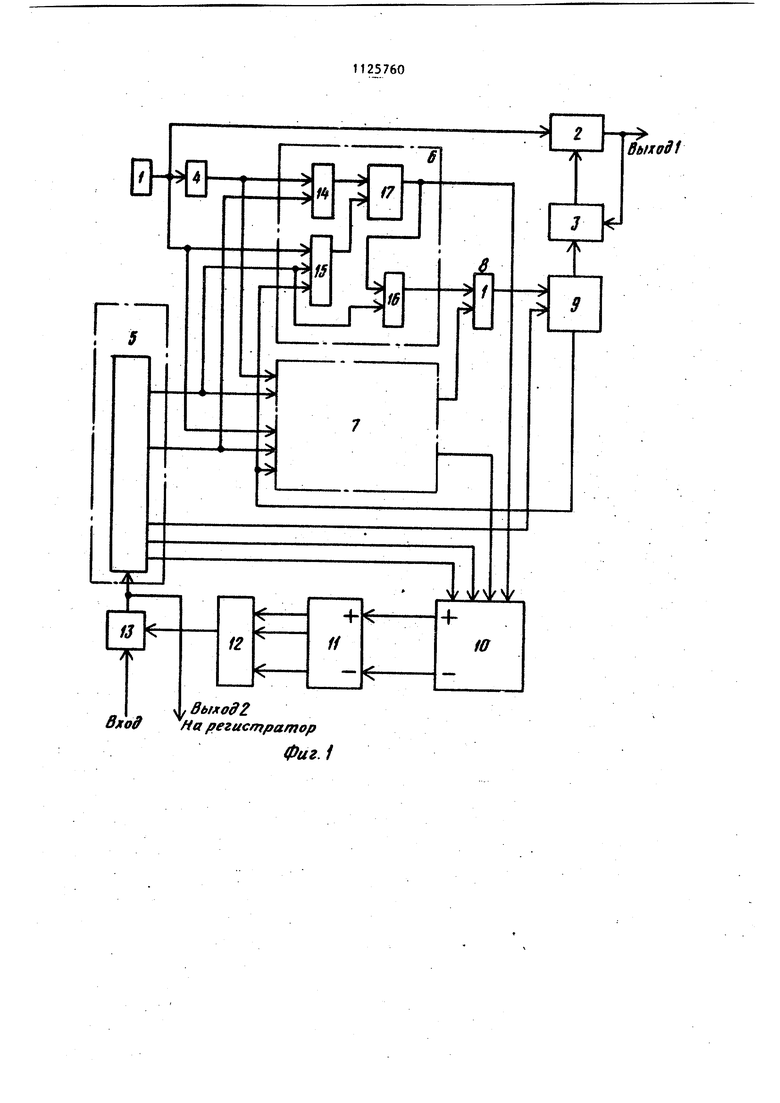

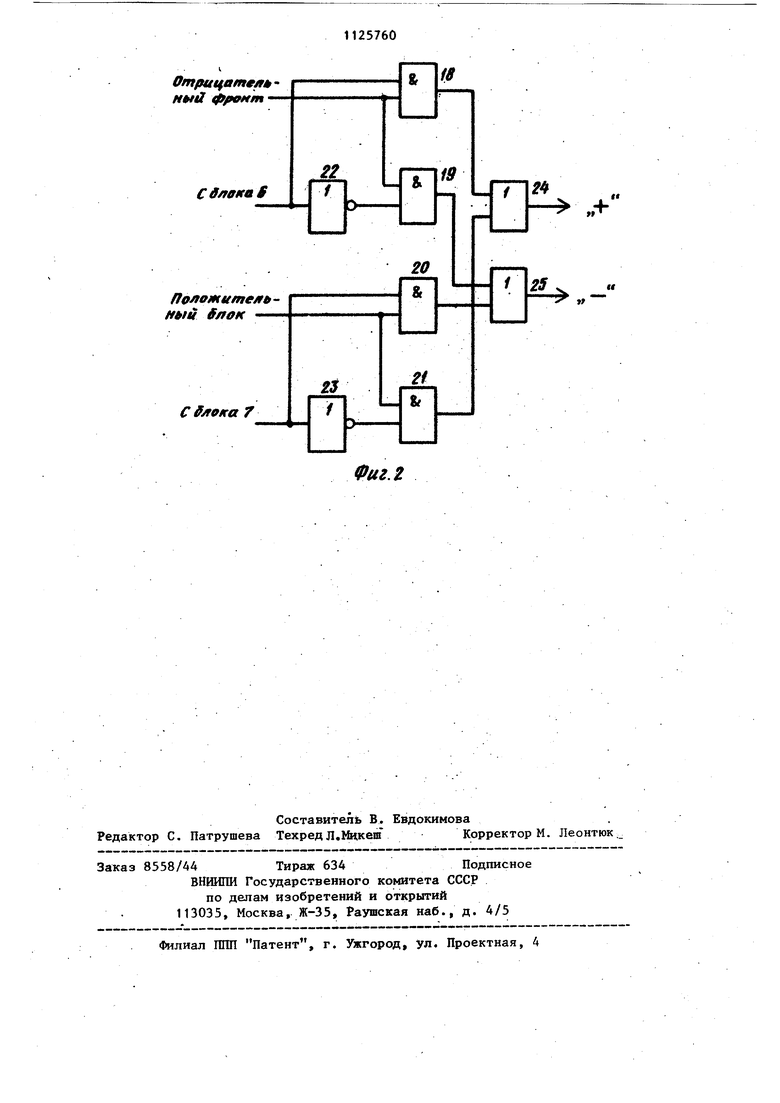

Изобретение относится к радиосвя зи, а именно к синхронизации приемника с передатчиком без .спещ1альных синхропосьток. По основному авт.св. № 743217 известно устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями, содержащее последовательно соединенные опорный генератор, управляемый делитель частоты и фазовый дискриминатор, выход которого подключен к другому входу управляемого делителя частоты, а также делитель частоты, формирователь фронтов, блок обработ ки переднего фронта входного сигнала, блок обработки заднего фронта входного сигнала, элемент ИЛИ и фор мирователь импульсов управления, вы ход опорного генератора непосредст.венно и через делитель частоты подключен к первым и вторым входам бло ков обработки переднего и заднего фронтов входного сигнала, вькоды которых через последовательно соединенные элемент ИЛИ и формировател и шyльGoв управления подключены к другому входу фазового дискриминатора, при этом выходы формирователя фронтов подключены соответственно к третьим и четвертым входам блока обработки переднего и заднего фронтов входного сигнала и к другом входу формирователя импульсов управ ления, другой выход которого подклю чeн к управляющим входам блоков обр ботки переднего и заднего фронтов входного сигнала lj . Недостатком известного устройств является низкая точность синхрониза Цель изобретения - повышение точ ности синхронизации путем обеспечения временной привязки регистрируемых импульсов относительно Импульсов входного двоичного сигнала. Цель достигается тем, что в устройство для синхронизации двоичных сигналов в каналах с постоянными пр обладания ш, содержащее последовательно соединенные опорный генератор, управляемьй делитель частоты и фазовый дискриминатор, выход которого подключен к другому входу упра ляемого делителя частоты, а также д литель частоты, формирователь фронтов,, блок обработки переднего фронт входного сигнала, блок обработки 02 переднего фронтй входного сигнала, блок обработки заднего фронта входного сигнала, элемент ИЛИ и формирователь импульсов управления, выход опорного генератора непосредственно и через делитель частоты подключен к первым.и вторым входам блоков обработки переднего и заднего фронтов входного сигнала, выходы которых через последовательно соединенные элемент ИЛИ и формирователь импульсов Управления подключены к другому входу фазового дискриминатора, при этом выходы формирователя фронтов подключены соответственно к третьим и четвертым входам блоков обработки переднего и заднего фройтов входного сигнала и к другому входу формирователя импульсов управления, другой выход которого подключен к управляющим входам блоков обработки переднего и заднего фронтов входного сигнала, введены последовательно соединенные блок определения знака преобладания, реверсивный счетчик, цифроаналоговый преобразователь и пороговый блок, при этом дополнительные выходы формирователя фронтов и дополнительные выходы блоков обработки переднего и заднего фронтов входного сигнала подключены к соответствующим входам блока определения знака преобладания, а выход порогового блока подключен к входу формирователя фронтов, причем сигнальньй вход порогового блока является входом устройства. На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - вариант выполнения блока определения знака преобладания. . Устройство для синхронизации двоичых сигнвлов в каналах с постоянными реобладаниями содержит опорный генератор 1, управляемый делитель 2 часоты, фазовый дискриминатор 3, делитель 4 частоты, формирователь 5 фронтов, блок 6 обработки переднего ронта входного сигнала, блок 7 обаботки заднего фронта входного сигнала, элемент ИЛИ 8, формирователь 9 мпульсов управления, блок 10 опрееления знака преобладания, реверсивный счетчик 11, цифроаналоговый преобразователь 12 и пороговый блок 13, в состав блока 6(7) обработки ходят ключи 14-16 и счетчик 17, а 31 в состав блока 10 определения знака преобладания входят элементы И 18-21 инверторы 22 и 23 и элементы ИЛИ 24 и 25. Устройство работает следующим образом.. По переднему фронту положительной посылки информации открывается ключ 14 и из делителя 4 частоты и счетчика 17 образуется единый счетг чик, считающий импульсы опорного генератора 1 все время, пока поступает положительная посьшка. Цикл работы этого счетчика равен дли- тельности искаженной элементарной посьтки с точностью до стабильности опорного генератора 1. Поэтому, если информационные посылки искажены преобладанием к моменту окончания положительной посылки, в счетчике хранится некоторый остаток от счета, Ьпределяемый величиной и зна ком преобладания. В момент окончания положительной посылки ключ Ю закры вается и открывается ключ 15, пропускающий импульсы опорного генератора 1 на счетчик 17, минуя делитель .4 частоты. Это эквивалентно де лению на два остатка, хранимого в счетчике 17. . После того, как импульсы опорног генератора 1 заполнят счетчик 17, на его выходе образуется отрицатель ный фронт, использующийся для форми рования управляющих импульсов. Процесс формирования этих импульсов (Зависит от состояния счетчика 17 в момент окончания положительнойпосылки. Если остаток от счета не превышает половины элементарной посьтки, при окончании положительной посылки выход счетчика 17 находится в состоянии О. Импульс отрицательного фройта с выхода формирователя 5 . фронтов записывает 1 в триггер, находящийся в формирователе 9 импул сов управления. Одновременно начина ется заполнение счетчика 17 импульсами опорного генератора . Когда о заполнится на .его выходе возникает отрицательный фронт, поступающий на счетныйвход триггера, находящегося в формирователе 9 импульсов управле ния . Этим фронтом триггер возвращается в состояние О. При этом формируется импульс управления, поступ щий на фазовый дискриминатор 3. 0 Если остаток превьппает половину элементарной посыпки, при окончании положительной посылки выход счетчика 17 находится в состоянии 1. Импульс отрицательного фронта с выхода формирователя 5 фронтов подтверждает состояние О триггера, находящегося в формирователе 9 импульсов управления. Отрицательный фронт, возникающий при заполнении счетчика 17, переводит этот триггерв состояние и только после нового заполнения счетчика триггер перейдет в состояние О. В этот момент сформируется импульс управления, поступакйдий на фазовый дискриминатор 3. Процесс обработки отрицательной посылки аналогичен описанному. Обработка начинается в момент появления переднего фронта этой посылки и вы- , полняется блоком 7 обработки, устройство и принцип работы которого аналогичен блоку 6 обработки. По результатам обработки посылок обоими блоками 6 и 7 обработки блок 10 определения знака преобладания вьшосит решение о знаке преобладания и о направлении, в котором следует смещать порог в пороговом блоке 13. Решение выносится по состоянию счетчиков 17, входящих в состав 1саждого блока 6 и 7 обработки. При обработке положительной посылки и наличии положительного преобладания выход счетчика 17 в блоке 6 обработки находится в состоянии О, а при наличии отрицательного преобладания - состоянии 1. При обработке отрицательной посылки и наличии положительного преобладания выход счетчика 17 в блоке 7 обработки находится в состоянии 1, а при наличии отрицательного преобладания - в состоя-НИИ О. . Чтобы принять верное решение, необходимо опросить состояние соответствующего счетчика еще до начала заполнения его импульсами опорного генератора 1. Для положительной посылки этот момент совпадает с отрицательным фронтам информационного сигнала, а для отрицательной посылки - с положительным фронтом. Эти моменты вьщеляются в виде узких импульсов, поступающих по двум отдельным проводам с формирователя 5 фронтов и выполняющих роль импуль- . саопроса в блоке 10 определения

янака преобладания. Опрос проиэвода1тся при помощи элементов И 18-21. Элементы И 18 и 19 опрашивают состояние счетчика 17 в блоке б обработки, а элементы И 20 и 21 - в блоке 7 обработки. При этом прохождение импульса огфоса через элементы И 18 и 21 обработки говорит о наличии положительного преобладания, а прохождение его череэ элементы И 19 и 21 о наличии отрицательного прербд адания. Поэтому выходы этих элементов попарно объединяются с помощью элементов ШШ 24 и 25. При этом прохождние импульса на выход элемента ИЛИ 24 соответствует положительному преобладанию, а прохождение его на выход элемента ИЛИ 25 - отрицательному преобладанию..

Импульсы, сигнализирукярте о напичии положительного и отрицательного преобладания, поступают соответственно на входы сложения (+) и вычитания (-) реверсивного счетчика 11, выходы всех разрядов которого поступают на входы цифроаналогового преобразователя 12 преобр.азукщего код числа, загшсанного в реверсивном счетчике t1, в постоянное напряжение. Это напряжение поступает на управляемый вход порогового блока 13 и задает величину nopot-a при формировании прямоугольных инфор ационных импульсов. При поступлении импульса на один из входов реверсивного счетчика 11 изменяется число, записанное в нем.

Изменение происходит на единицу в ту или иную сторону. Это вызывает

смещение порога формирования на один шаг в соответствующую сторонуi

Пределы возможного смещения порога, а также шаг этого смещения совместно определяются емкостью реверсивного счетчика н точностью цифроаналогового преобразователя.

Порог перемещается предлагаемым способом до устранения преобладания, после чего он поддерживается на достигнутом уровне с точностью до величины шага перемещения порога. Информация на регистратор снимается с выхода порогового блока 13.

Применение предложенного устройства синхронизации позволяет повысить точность синхронизации по сравнению с известным. При использований известного устройства на регистрацию поступает информация пораженная совместно преобладаниями и краевыми искажениями. В то же время предлагаемое устройство синхронизации устраняет преобладание из сигнала, поступающего На регистрацию. Если выразит дисперсию расйределения смещений в пр эцентах от длительности единичного элемента информационного сигнала, то расширение элементов информационного сигнала, которые были сужены преобладанием, равноценно уменьшению Дисперсии распределения смещений. Это уменьшитг вероятность неверной регистрации информации при прочих равных условиях, повысит помехоустойчивость приемникадискретных сообщений по сравнению с помехоустойчивостью, достигаемой при использовании известного устройства.

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями | 1978 |

|

SU743217A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство для компенсации искажений типа "преобладание | 1987 |

|

SU1506581A1 |

| Устройство компенсации искажений типа "преобладаний" в дискретных сигналах | 1986 |

|

SU1385319A1 |

| Устройство синхронизации импульсных приемников | 1976 |

|

SU605327A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU886290A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

yCTPpfteTBC ДЛЯ СИНХРОНИЗАЦИИ ДВОИЧНЫХ СИГНАЛОВ В КАНАЛАХ С ПОСТОЯННЫМИ ПРЕОБЛАДАНИЯМИ по авт. св. № 743217, о т л и чаю щ е е с я тем, что, с целью повышения точности синхронизации путем обеспечения временной привязки регистрируемых импульсов относительно импульсов входного двоичного сигнала, введены последовательно соединенные блок определения знака преобладания, реверсивный счетчик, цифроаналоговый преобразователь и пороговый блок, при этом дополнительные выходы формирователя фронтов и дополнительные выходы блоков обработки переднего и заднего фронтов входного сигнала подключены к соответствующим входам блока определения знака преобладания, а выход порогового блока подключен к входу формирователя фронтов, причем сигнальный вход порогового S блока является входом устройства.

IS

Г

s I

/j

//

12

BbixodZ

t Ha регистратор

фиг.1

A

I

, P

f

Ш

2

II

2S

It

fftuz.Z

| t | |||

| Устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями | 1978 |

|

SU743217A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-23—Публикация

1981-06-22—Подача