ную шину 2, элемент ИЛИ 3, интегратор 4 со сбросом, коммутирующий элемент 5, дифференцирующие цепи 6, 14, 15 и триггеры 7, 28-33, ключи 8, 10, амплитудный детектор 9, элемент 11 задержки, вычитающий блок 12, пороговый блок 13, блок 16 деления, элементы И 17-20, делитель 21 напряжения, компараторы 22, 23, 24, инверторы 25, 26, 27, выходы 34-40. За счет введения элемента

ИЛИ 3, интегратора 4 со сбросом и элемента 11 задержки обеспечивается исключение сложных элементов формирования эталонного напряжения калибровки по первому каналу и автоматического перезапуска устройства, а также повышение точности контроля за счет сравнения измеряемого параметра с непрерывным эталонным сигналом. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство допускового контроля двухканальных усилителей | 1986 |

|

SU1401588A1 |

| Измеритель нелинейности амплитудной характеристики радиоэлементов | 1986 |

|

SU1370615A1 |

| Измеритель нелинейности радиодеталей | 1984 |

|

SU1195293A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Измеритель шума | 1985 |

|

SU1293669A1 |

| Устройство для определения оптимального периода технического обслуживания изделия | 1990 |

|

SU1767508A1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1348776A1 |

| Устройство автоматического контроля величины показателя тепловой инерции термопар | 1980 |

|

SU939964A1 |

| Устройство для определения оптимального периода технического состояния изделия | 1990 |

|

SU1767510A1 |

| Устройство для учета движущихся объектов | 1985 |

|

SU1305740A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и управления технологическими процессами изготовления двухканальных аналоговых усилителей на интегральных схемах. Цель изобретения - упрощение устройства и повышение точности контроля за счет использования интегратора со сбросом для формирования эталонного напряжения автоматической калибровки. Устройство допускового контроля двухканальных усилителей 1 содержит входzi Ё О 2 Ю CJ 36 38 Фиг.1 40

Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и управления технологическими процессами изготовления двухканальных аналоговых усилителей на интегральных схемах.

Цель изобретения - упрощение устройства и повышение точности контроля за счет использования интегратора со сбросом для формирования эталонного напряжения автоматической калибровки.

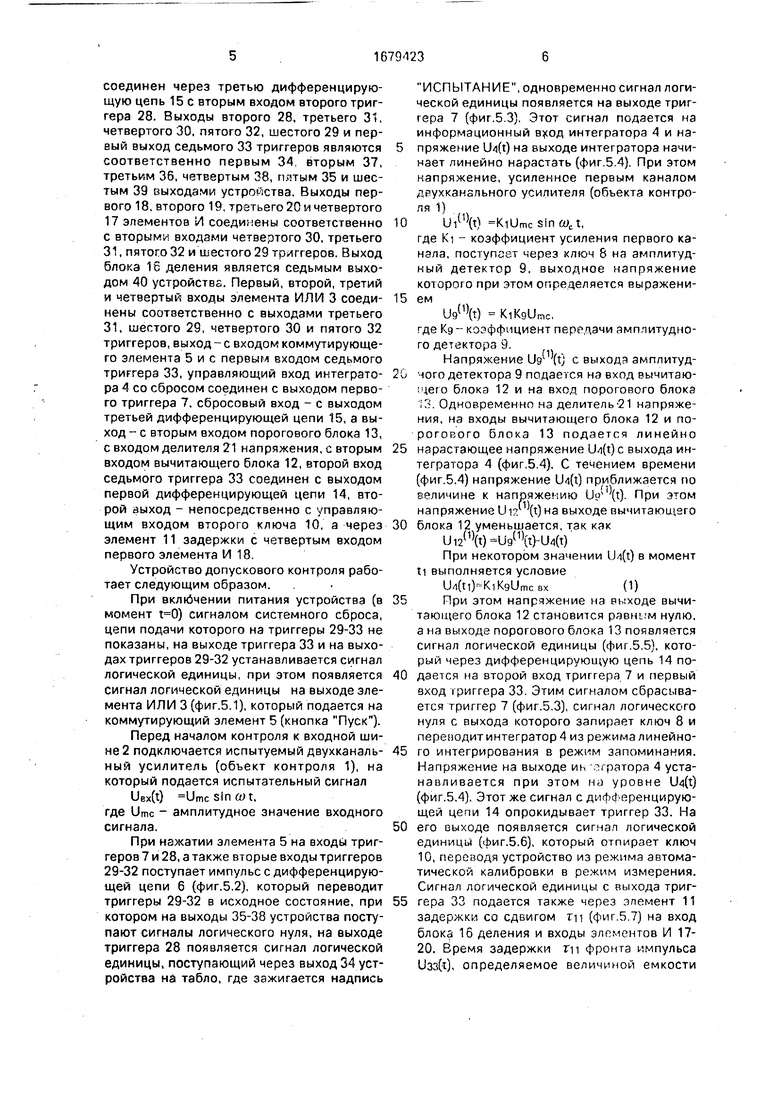

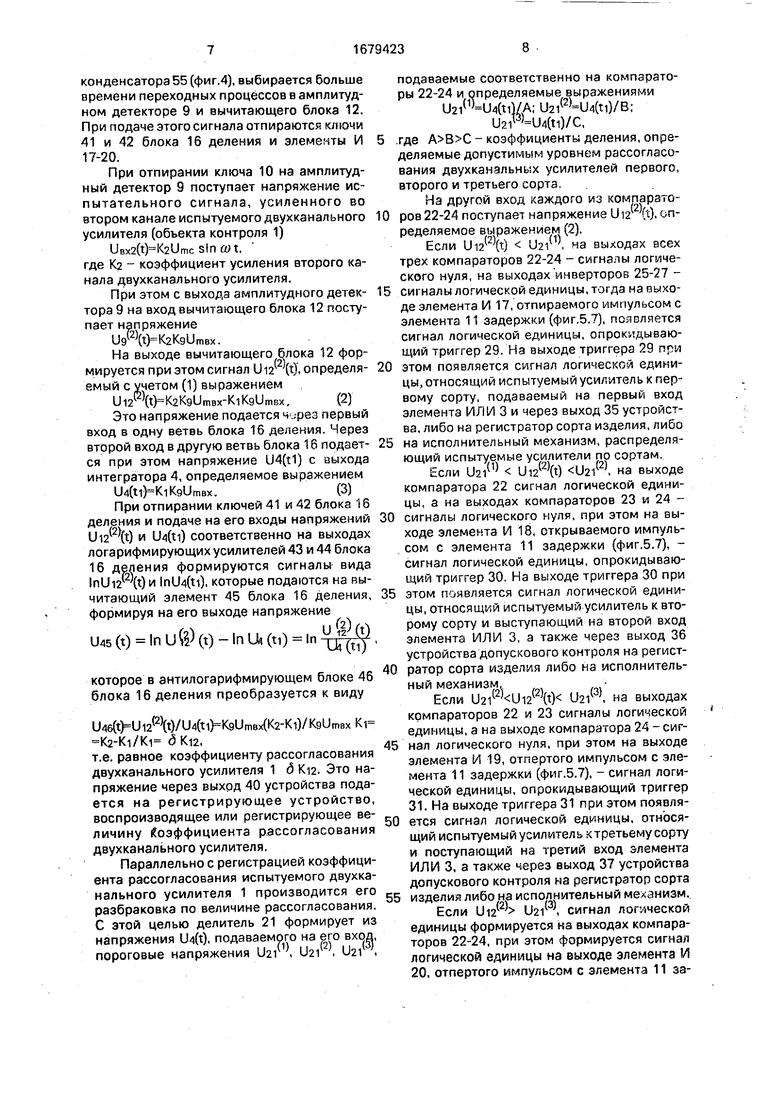

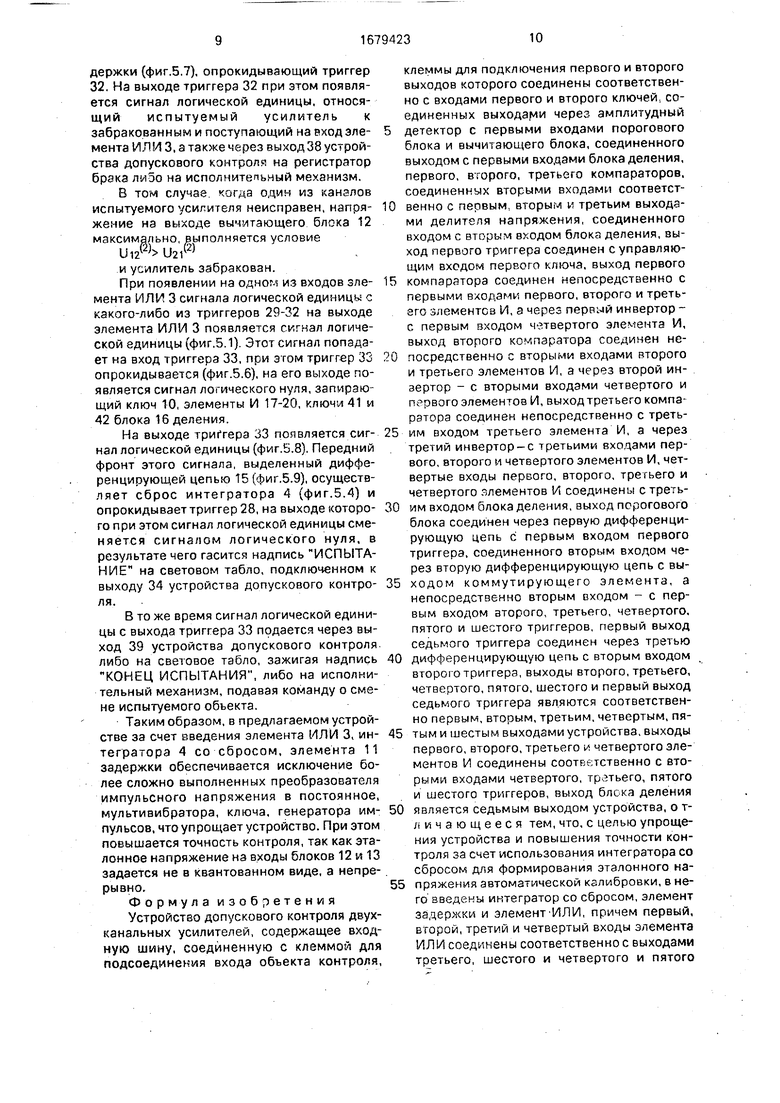

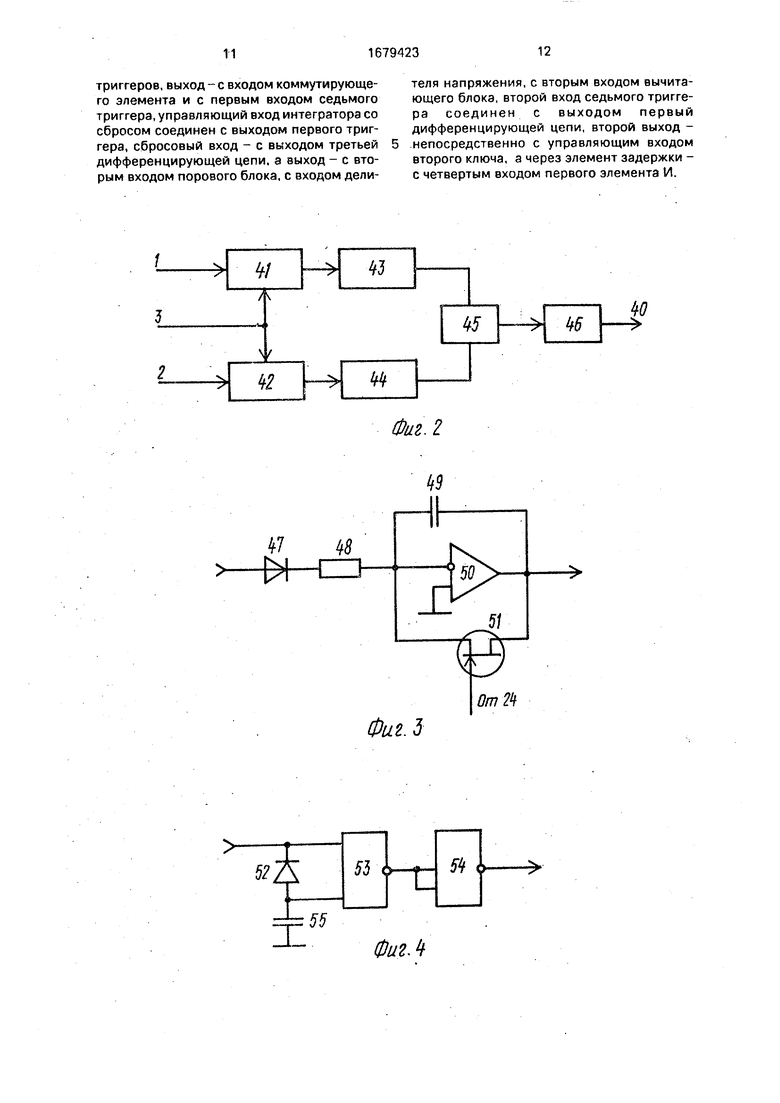

На фиг.1 приведена схема устройства; на фиг.2 - схема блока деления; на фиг.З - схема интегратора со сбросом; на фиг.4 - схема элемента задержки; на фиг.5 - временные диаграммы работы устройства.

Устройство допускового контроля двухканальных усилителей 1 содержит входную шину 2, элемент ИЛИ 3, интегратор 4 со сбросом, коммутирующий элемент 5, вторую дифференцирующую цепь 6, первый триггер 7, первый ключ 8, амплитудный детектор 9, второй ключ 10, элемент 11 задержки, вычитающий блок 12, пороговый блок 13, первую1 14 и третью 15 дифференцирующие цепи, блок 16 деления, четвертый 17, первый 18, второй 19 и третий 20 элементы И, делитель 21 напряжения, первый 22, второй 23 и третий 24 компараторы, первый 25, второй 26 и третий 27 инверторы, второй 28, шестой 29, четвертый 30, третий 31, пятый 32 и седьмой 33 триггеры, первый 34, пятый 35, третий 36, второй 37, четвертый 38, шестой 39 и «седьмой 40 выходы,

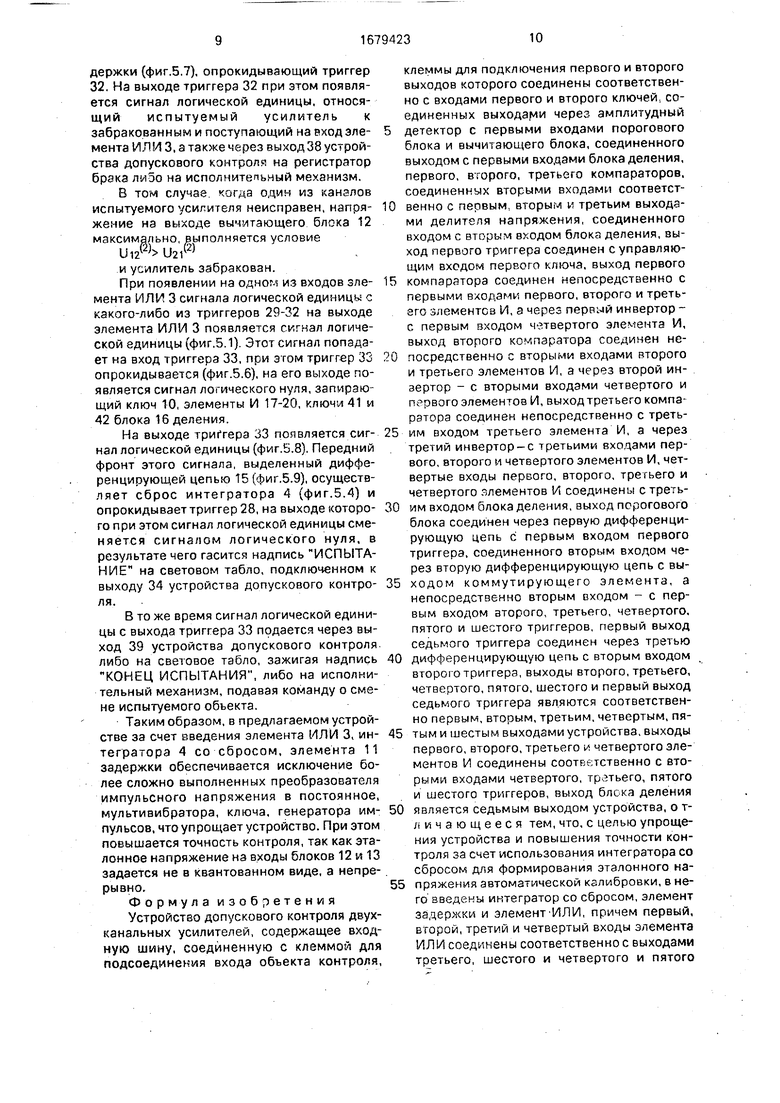

Блок 16 деления (фиг.2) содержит ключи 41 и 42, логарифмирующие усилители 43 и 44, вычитающий элемент 45, антилогариф- мирующий элемент 46.

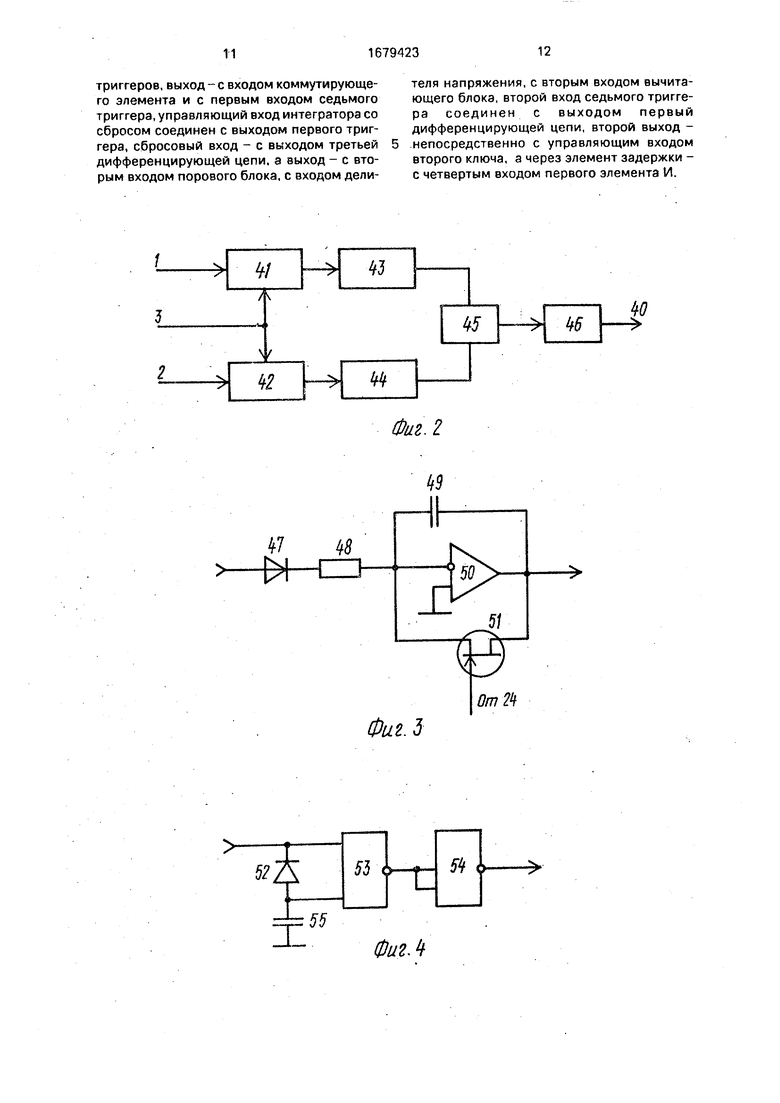

Интегратор 4 со сбросом (фиг.З) содержит диод 47, резистор 48, конденсатор 49, усилитель 50 и транзистор 51.

Элемент 11 задержки (фиг.4) содержит диод 52, элемент И-НЕ 53, элемент НЕ 54 и конденсатор 55.

Входная шина 2 соединена с клеммой для подключения входа объекта контроля (двухканального усилителя 1), клеммы для подключения первого и второго выходов которого соединены соответственно с входами первого 8 и второго 10 ключей, соединенных выходами через амплитудный детектор 9 с первыми входами порогового блока 13 и вычитающего блока 12, соединенного выходом с первыми входами блока 16 деления, первого 22, второго 23, третьего 24 компараторов, соединенных вторыми входами соответственно с первым, вторым и третьим выходами делителя 21 напряжения.

а входом с вторым входом блока 16 деления. Выход первого триггера 7 соединен с управляющим входом первого ключа 8. Выход первого компаратора 22 соединен непосредственно с первыми входами первого 18,

второго 19 и третьего 20 элементов И, а через первый инвертор 25 - с первым входом четвертого элемента И 17. Выход второго компаратора 23 соединен непосредственно с вторыми входами второго 19 и третьего 20 элементов И, а через второй инвертор 26 - с вторыми входами четвертого 17 и первого 18 элементов И, выход третьего компаратора 24 соединен непосредственно с третьим входом третьего элемента И 20, а через третий инвертор 27 - с третьими входами первого 18, второго 19 и четвертого 17 элементов И. Четвертые входы первого 18, второго 19, третьего 20 и четвертого 17 элементов И соединены с

третьим входом блока 16 деления. Выход порогового блока 13 соединен через первую дифференцирующую цепь 14 с первым входом первого триггера 7, соединенного вто- рым входом через вторую

дифференцирующую цепь 6 с выходом коммутирующего элемента 5, соединенным с первым входом второго 28, третьего 31, четвертого 30, пятого 32 и шестого 29 триггеров, первый выход седьмого триггера 33

соединен через третью дифференцирующую цепь 15с вторым входом второго триггера 28. Выходы второго 28, третьего 31, четвертого 30, пятого 32, шестого 29 и первый выход седьмого 33 триггеров являются соответственно первым 34, вторым 37, третьим 36, четвертым 38, пятым 35 и шестым 39 выходами устройства. Выходы первого 18, второго 19, тратьего 20 и четвертого 17 элементов И соединены соответственно с вторыми входами четвертого 30, третьего 31, пятого 32 и шестого 29 триггеров. Выход блока 15 деления является седьмым выходом 40 устройства. Первый, второй, третий и четвертый входы элемента ИЛИ 3 соединены соответственно с выходами третьего 31, шестого 29, четвертого 30 и пятого 32 триггеров, выход - с входом коммутирующего элемента 5 и с первым входом седьмого триггера 33, управляющий вход интегратора 4 со сбросом соединен с выходом первого триггера 7. сбросовый вход - с выходом третьей дифференцирующей цепи 15, а выход - с вторым входом порогового блока 13, с входом делителя 21 напряжения, с вторым входом вычитающего блока 12, второй вход седьмого триггера 33 соединен с выходом первой дифференцирующей цепи 14, второй выход - непосредственно с управляющим входом второго ключа 10, а через элемент 11 задержки с четвертым входом первого элемента И 18.

Устройство допускового контроля работает следующим образом.

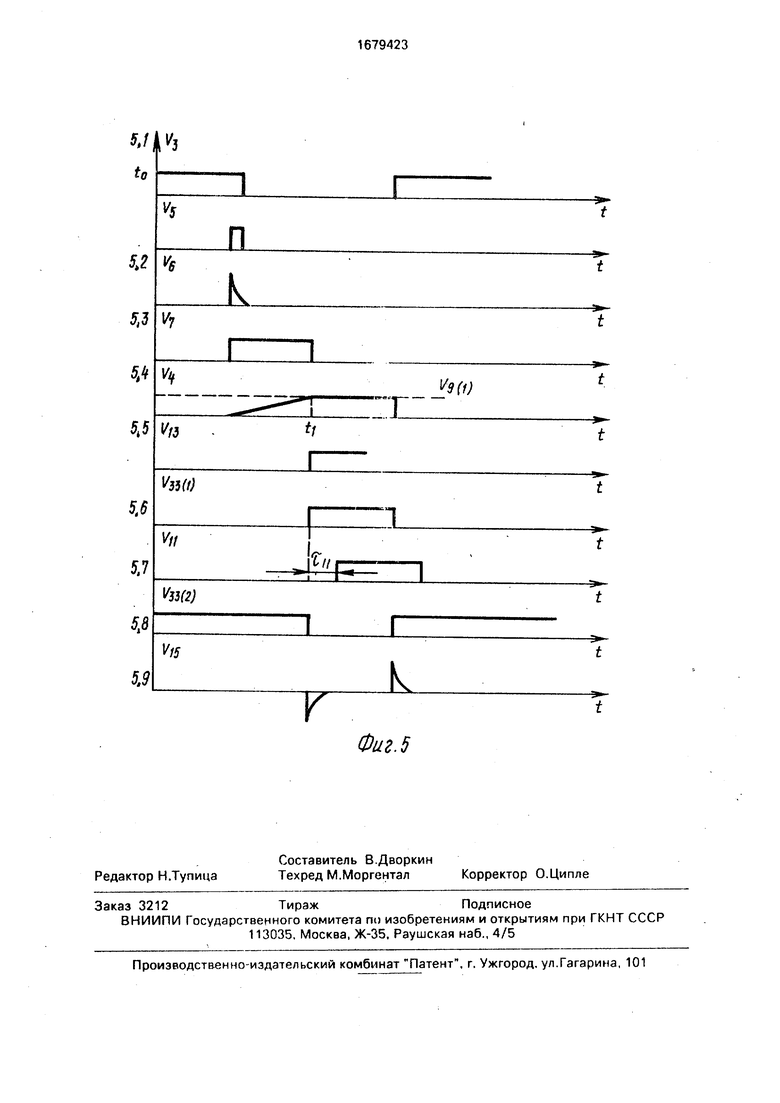

При включении питания устройства (в момент ) сигналом системного сброса, цепи подачи которого на триггеры 29-33 не показаны, на выходе триггера 33 и на выходах триггеров 29-32 устанавливается сигнал логической единицы, при этом появляется сигнал логической единицы на выходе элемента ИЛИ 3 (фиг.5.1), который подается на коммутирующий элемент 5 (кнопка Пуск).

Перед началом контроля к входной шине 2 подключается испытуемый двухканаль- ный усилитель (объект контроля 1), на который подается испытательный сигнал

Uex(t) UmcSinftn,

где Umc - амплитудное значение входного сигнала.

При нажатии элемента 5 на входы триггеров 7 и 28, а также вторые входы триггеров 29-32 поступает импульс с дифференцирующей цепи 6 (фиг.5.2), который переводит триггеры 29-32 в исходное состояние, при котором на выходы 35-38 устройства поступают сигналы логического нуля, на выходе триггера 28 появляется сигнал логической единицы, поступающий через выход 34 устройства на табло, где зажигается надпись

ИСПЫТАНИЕ, одновременно сигнал логической единицы появляется на выходе триггера 7 (фиг.5.3), Этот сигнал подается на информационный вход интегратора 4 и напряжение LM(t) на выходе интегратора начинает линейно нарастать (фиг.5.4). При этом напряжение, усиленное первым каналом друхкан.ального усилителя (объекта контроля 1)

Ui(1)(t) KiUmc ,

где Ki - коэффициент усиления первого канала, поступает через ключ 8 на амплитудный детектор 9, выходное напряжение которого при этом определяется выражением

Ug(1)(t) KiKgUmc,

где Kg- коэффициент передачи амплитудного детектора 9.

Напряжение IV (t) с выхода амплитудчого детектора 9 подается на вход вычитающего блока 12 и на вход порогового блока i3. Одновременно на делитель 21 напряжения, на входы вычитающего блока 12 и порогового блока 13 подается линейно

нарастающее напряжение U(t) с выхода интегратора 4 (фиг,5.4). С течением времени (фиг.5.4) напряжение U-i(t) приближается по величине к напряжению Up (t). При этом напряжение Ui (т.) на выходе вычитающего

блока 12 уменьшается, так как Ui2(1)(t)U9(1)(t)-lMt)

При некотором значении U/i(t) в момент П выполняется условие

U(tihKiK9UmcBx(1)

При этом напряжение на выходе вычитающего блока 12 становится равным нулю, а на выходе порогового блока 13 появляется сигнал логической единицы (фиг.5.5), который через дифференцирующую цепь 14 подается на второй вход триггера 7 и первый вход григгера 33. Этим сигналом сбрасывается триггер 7 (фиг.5.3), сигнал логического нуля с выхода которого запирает ключ 8 и переводит интегратор 4 из режима линейного интегрирования в режим запоминания. Напряжение на выходе иь -лгратора 4 устанавливается при этом на уровне lU(t) (фиг.5.4). Этот же сигнал с дифференцирующей цепи 14 опрокидывает триггер 33. На

его выходе появляется сигнал логической единицы (фиг.5.6), который отпирает ключ 10, переводя устройство из режима автоматической калибровки в режим измерения. Сигнал логической единицы с выхода триггера 33 подается также через элемент 11 задержки со сдвигом тц (фиг.5.7) на вход блока 16 деления и входы элементов И 17- 20. Время задержки Гц фронта импульса LtoCt), определяемое величиной емкости

конденсатора 55 (фиг.4), выбирается больше времени переходных процессов в амплитудном детекторе 9 и вычитающего блока 12. При подаче этого сигнала отпираются ключи 41 и 42 блока 16 деления и элементы И 17-20.

При отпирании ключа 10 на амплитудный детектор 9 поступает напряжение испытательного сигнала, усиленного во втором канале испытуемого двухканального усилителя (объекта контроля 1)

U8x2(t)K2Umc Sin (Wt,

где К2 - коэффициент усиления второго канала двухканального усилителя.

При этом с выхода амплитудного детектора 9 на вход вычитающего блока 12 поступает напряжение

U9(2)(t)K2K9UmBX.

На выходе вычитающего б/юка 12 формируется при этом сигнал (t), определяемый с учетом (1) выражением

Ul2P)(thK2K9UmBx-KlK9UmBX,(2)

Это напряжение подается ч.;рез первый вход в одну ветвь блока 16 деления. Через второй вход в другую ветвь Ьлока 16 подается при этом напряжение U4(t1) с выхода интегратора 4, определяемое выражением

U4(tl)KlK9UmBX.(3)

При отпирании ключей 41 и 42 блока 16 деления и подаче на его входы напряжений U12 (t) и U4ti) соответственно на выходах логарифмирующих усилителей 43 и 44 блока 16 деления формируются сигналы вида lnUi2 (t)n lnU4(ti), которые подаются на вычитающий элемент 45 блока 16 деления, формируя на его выходе напряжение

U45(t) lnU®(t)-lnU(ti) .

которое в антилогарифмирующем блоке 46 блока 16 деления преобразуется к виду

U eW-Utt tJ/U tl KgUmB fc-KiJ/KgUmexKi K2-Ki/Ki dKi2,

т.е. равное коэффициенту рассогласования двухканального усилителя 1 д Ki2. Это напряжение через выход 40 устройства подается на регистрирующее устройство, воспроизводящее или регистрирующее величину Коэффициента рассогласования двухканального усилителя.

Параллельно с регистрацией коэффициента рассогласования испытуемого двухканального усилителя 1 производится его разбраковка по величине рассогласования. С этой целью делитель 21 формирует из напряжения l)4(t), подаваемого на его вход, пороговые напряжения U21 , U21 . U21 ,

подаваемые соответственно на компараторы 22-24 и определяемые выражениями U2i(1)U4(ti)/A;U2i{2)U4(ti)/B; U2iT3)U4(ti)/C,

где А В С-коэффициенты деления, определяемые допустимым уровнем рассогласования двухканальных усилителей первого, второго и третьего сорта,

На другой вход каждого из компарато0 ров 22-24 поступает напряжение Ui2 (t), определяемое выражением (2).

Если U12 (t} 1)21 , на выходах всех трех компараторов 22-24 - сигналы логического нуля, на выходах инверторов 25-27 5 сигналы логической единицы, тогда на выходе элемента И 17, отпираемого импульсом с элемента 11 задержки (фиг.5.7), псяоляется сигнал логической единицы, опрокидывающий триггер 29. На выходе триггера 29 при

0 этом появляется сигнал логической единицы, относящий испытуемый усилитель к первому сорту, подаваемый на первый вход элемента ИЛИ 3 и через выход 35 устройства, либо на регистратор сорта изделия, либо

5 на исполнительный механизм, распределяющий испытуемые усилители по сортам.

Если U21(1) Ui2(2(t) U21(2). на выходе компаратора 22 сигнал логической единицы, а на выходах компараторов 23 и 24 0 сигналы логического нуля, при этом на выходе элемента И 18, открываемого импульсом с элемента 11 задержки (фиг.5.7), - сигнал логической единицы, опрокидывающий триггер 30. На выходе триггера 30 при

5 этом появляется сигнал логической единицы, относящий испытуемый усилитель к второму сорту и выступающий на второй вход элемента ИЛИ 3, а также через выход 36 устройства допускового контроля на регист0 ратор сорта изделия либо на исполнительный механизм.

Если U2i(2)Ui2(2)(t) U21(3), на выходах компараторов 22 и 23 сигналы логической единицы, а на выходе компаратора 24 - сиг5 нал логического нуля, при этом на выходе элемента И 19, отпертого импульсом с элемента 11 задержки (фиг.5.7), - сигнал логической единицы, опрокидывающий триггер 31. На выходе триггера 31 при этом появля0 ется сигнал логической единицы, относящий испытуемый усилитель третьему сорту и поступающий на третий вход элемента ИЛИ 3, а также через выход 37 устройства долускового контроля на регистратор сорта

5 изделия либо на исполнительный механизм. Если Ui2 U21 , сигнал логической единицы формируется на выходах компараторов 22-24, при этом формируется сигнал логической единицы на выходе элемента И 20, отпертого импульсом с элемента 11 задержки (фиг.5.7), опрокидывающий триггер 32. На выходе триггера 32 при этом появляется сигнал логической единицы, относящий испытуемый усилитель к забракованным и поступающий на РХОД элемента ИЛ И 3, а также через выход 38 устройства допускового контроле на регистратор брзка лиэо на исполнительный механизм.

В том случае когда один из каналов испытуемого усилителя неисправен, напряжение на выходе вычитающего блока 12 максимально, выполняется условие

U12(2)U21(2)

и усилитель забракован.

При появлении на одном из входов элемента ИЛИ 3 сигнала логической единицы с какого-либо из триггеров 29-32 на выходе элемента ИЛИ 3 появляется сигнал логической единицы (фиг.5.1). Этот сигнал попадает на вход триггера 33, при эгом триггер 33 опрокидывается (фиг.5.6), на его выходе появляется сигнал логического нуля, запирающий ключ 10, элементы И 17-20, ключи 41 и 42 блока 16 деления.

На выходе триггера 33 появляется сигнал логической единицы (фиг.5.8). Передний фронт этого сигнала, выделенный дифференцирующей цепью 15 (фиг.5.9), осуществляет сброс интегратора 4 (фиг.5.4) и опрокидывает триггер 28, на выходе которого при этом сигнал логической единицы сме- няется сигналом логического нуля, в результате чего гасится надпись ИСПЫТАНИЕ на световом табло, подключенном к выходу 34 устройства допускового контроля.

В то же время сигнал логической единицы с выхода триггера 33 подается через выход 39 устройства допускового контроля либо на световое табло, зажигая надпись КОНЕЦ ИСПЫТАНИЯ, либо на исполнительный механизм, подавая команду о смене испытуемого объекта.

Таким образом, в предлагаемом устройстве за счет введения элемента ИЛИ 3, интегратора 4 со сбросом, элемента 11 задержки обеспечивается исключение более сложно выполненных преобразователя импульсного напряжения в постоянное, мультивибратора, ключа, генератора импульсов, что упрощает устройство. При этом повышается точность контроля, так как эталонное напряжение на входы блоков 12 и 13 задается не в квантованном виде, а непрерывно.

Формула изобретения

Устройство допускового контроля двух- канальных усилителей, содержащее входную шину, соединенную с клеммой для подсоединения входа объекта контроля,

клеммы для подключения первого и второго выходов которого соединены соответственно с входами первого и второго ключей соединенных выходами через амплитудный

детектор с первыми входами порогового блока и вычитающего блока, соединенного выходом с первыми входами блока деления, первого, второго, третьего компараторов, соединенных вторыми входами соответст0 венно с первым вторым и третьим выходами делителя напряжения, соединенного входом с вторым входом блока деления, выход первого триггера соединен с управляющим входом первого ключа, выход первого

5 компаратора соединен непосредственно с первыми входами первого, второго и третьего элементов И, а через первый инвертор - с первым входом четвертого элемента И, выход второго компаратора соединен не0 посредственно с вторыми входами второго и третьего элементов И, а через второй инвертор- - с вторыми входами четвертого и первого элементов И, выход третьего компаратора соединен непосредственно с треть5 им входом третьего элемента И, а через третий инвертор-с третьими входами первого, второго и четвертого элементов И, четвертые входы первого, второго, третьего и четвертого элементов И соединены с треть0 им входом блока деления, выход порогового блока соединен через первую дифференцирующую цепь с первым входом первого триггера, соединенного вторым входом через вторую дифференцирующую цепь с вы5 ходом коммутирующего элемента, а непосредственно вторым входом - с первым входом второго, третьего, четвертого, пятого и шестого триггеров, первый выход седьмого триггера соединен через третью

0 дифференцирующую цепь с вторым входом второго триггера, выходы второго, третьего, четвертого, пятого, шестого и первый выход седьмого триггера являются соответственно первым, вторым, третьим, четвертым, пя5 тым и шестым выходами устройства, выходы первого, второго,третьего и четвертого элементов И соединены соответственно с вторыми входами четвертого, третьего, пятого и шестого триггеров, выход блска деления

0 является седьмым выходом устройства, о т- личающееся тем, что, с целью упрощения устройства и повышения точности контроля за счет использования интегратора со сбросом для формирования эталонного на5 пряжения автоматической калибровки, в него введены интегратор со сбросом, элемент задержки и элемент ИЛ И, причем первый, второй, третий и четвертый входы элемента ИЛ И соединены соответственно с выходами третьего, шестого и четвертого и пятого

триггеров, выход-с входом коммутирующего элемента и с первым входом седьмого триггера, управляющий вход интегратора со сбросом соединен с выходом первого триггера, сбросовый вход - с выходом третьей дифференцирующей цепи, а выход - с вторым входом перового блока, с входом делителя напряжения, с вторым входом вычитающего блока, второй вход седьмого триггера соединен с выходом первый дифференцирующей цепи, второй выход - непосредственно с управляющим входом второго ключа, а через элемент задержки - с четвертым входом первого элемента И.

Фиг. 2

Фиг. 3

М:

to

5,1 5t8 5.9

V

Фиг. 5

| Бортовые системы управления полетом | |||

| /Под ред | |||

| Ю.В.Байбородина | |||

| - М,, Транспорт, 1975, с | |||

| Фотореле для аппарата, служащего для передачи на расстояние изображений | 1920 |

|

SU224A1 |

| Устройство допускового контроля двухканальных усилителей | 1986 |

|

SU1401588A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

Авторы

Даты

1991-09-23—Публикация

1989-10-17—Подача