О

VJ о N XI ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный стабилизатор напряжения постоянного тока | 1989 |

|

SU1707609A1 |

| Способ управления тиристорным преобразователем частоты | 1985 |

|

SU1336176A1 |

| Имитатор химической батареи | 1982 |

|

SU1089593A1 |

| Устройство для газовой резки и сварки | 1989 |

|

SU1699734A1 |

| РЕГУЛЯТОР ТОКА | 2013 |

|

RU2530305C1 |

| СПОСОБ ЗАЩИТЫ ТРАНСФОРМАТОРА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 2004 |

|

RU2264016C1 |

| Передатчик СВЧ миллиметрового диапазона волн повышенной выходной мощности | 2019 |

|

RU2722422C1 |

| Импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1325442A1 |

| Стабилизированный источник постоянного напряжения | 1985 |

|

SU1309012A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1495766A1 |

Изобретение относится к электротехнике, в частности к источникам вторичного электропитания радиоэлектронной аппаратуры. Цель - повышение качества стабилизации, надежности работы и КПД Устройство содержит управляемыйдискретный выпрямитель 1, управляемый компенсационный стабилизатор 8 напряжения, датчик 9 тока, датчик 12 напряжения, шину 13 управления, вычитающий блок 15, селектор 17 минимального сигнала, аналоговый сумматор 20, эадатчик 21 минимального падения напряжения на стабилизаторе 8, блок 23 выделения модуля сигнала, проходной элемент 25 с узкой зо

Фиг.1

ной нечувствительности, управляемый аттенюатор 29. Выпрямитель 1 обеспечивает гк стоянным напряжением стабилизатор 8. Из заданного сигнала на управляющей тине 13 и сигнала обратной связи от датчика 12 напряжения селектор 17 выбирает наименьший. Этот сигнап суммируется с сигналом задэтчика 21 о сумматоре 20, который в установившемся режиме, управляя выпрямителем 1, устанавливает оптимальный режим стабилизатора 8. При увеличении абсолютИзобретение относится к электротехнике и предназначено для использования при реализации вторичного электропитания радиоэлектронной аппаратуры с широким диапазоном изменения напряжения на выводах потребителя

Цель изобретения - повышение качества стабилизации, надежности работы и КПД.

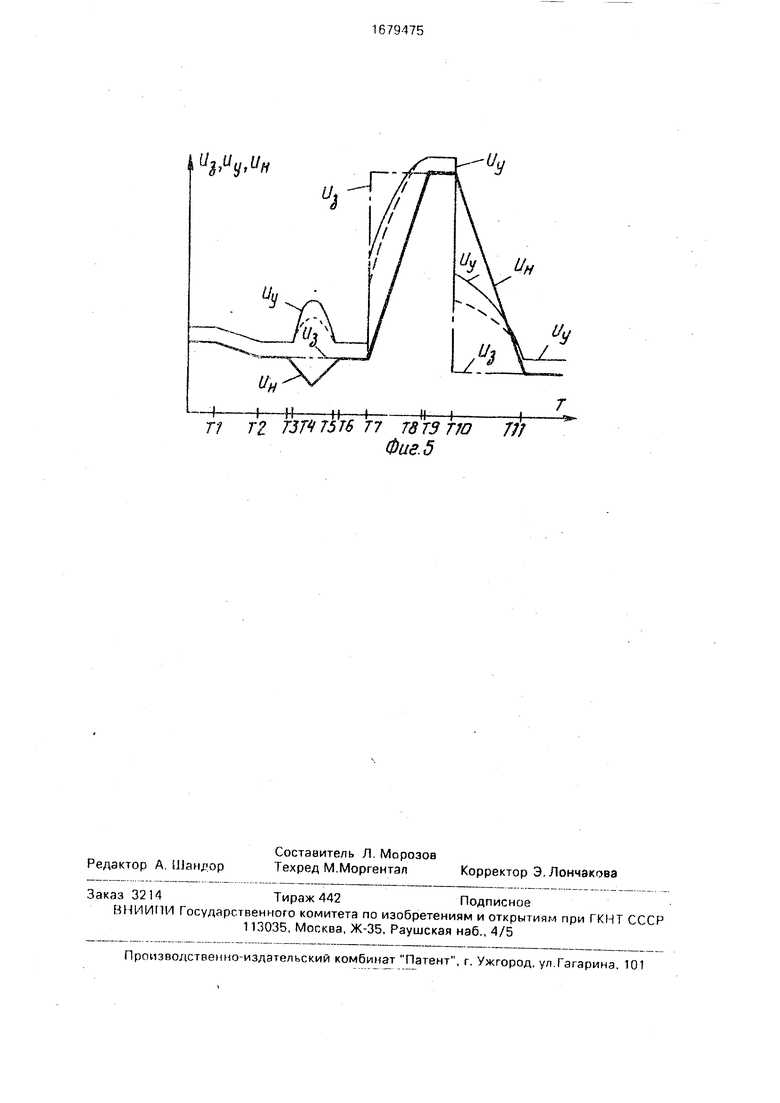

Нафиг.1 представлена функциональная управляемого стабилизирующего ис- ючника напряжения постоянного тока; на фиг.2-4 - принципиальные электрические схемы примененных соответственно селектора минимального сигнала, проходного элемента с узкой зоной нечувствительности и дискретного выпрямителя; на фиг.5 - упрощенный совмещенный график изменения напряжений в отдельных узловых точках устройства.

В управляемом стабилизирующем источнике напряжения постоянного тока (фиг.1) на входе силового канала расположен управляемый дискретный выпрямитель 1, который имеет питающее выводы 2 и 3, соединенные с неотмеченными на схеме сыводами для подключения первичного источника питания, и выходные выводы 4 и 5, подключенные к входным выводам 6 и 7 управляемого компенсационного стабилизатора 8 напряжения через датчик 9 тока. Выходные выводы 10 и 11 стабилизатора 8 напряжения соединены с : смененными на схеме выводами для подключения нагрузки и с входом датчика 12 напряжения. К непокэзанному на схеме источнику управляющего напряжения по шине 13 подключен управляющий вход 14 стабилизатора 8 напряжения, один из входов вычитающего1 блока 15 и вход 16 селектора 17 минимального сигнала. Вход 18 последнего и другой вход вычитающего блока 15 соединены с выходом датчика 12 напряжения. Выход 19 селектора 17 минимального сигнала подключен к одному из входов аналогового сумматора 20, другой вход которого соединен с выходом задатчи- ка 21 минимального падения напряжения

ной величины разности между задающим сигналом и выходным напряжением цепочка из вычитающего блока 15, блока 23 выделения модуля, проходного элемента 25, логарифмирующего блока 27 и аттенюатора 29 обеспечивает добавление напряжения в сумматоре 20 для ускорения переходных процессов. При увеличении нагрузочного тока датчик 9 т ока осуществляет коррекцию сигнала через аттенюатор 2В. 1 з.п. ф-лы, 5 ил.

на стабилизаторе 8 напряжения, а выход - с управляющим входом 22 выпрямителя 1. В состав устройства входят, кроме того, блок 23 выделения модуля сигнала с выходом 24,

проходной элемент 25 с узкой зоной нечувствительности, выполненный с выходом 26, логарифмирующий блок 27. Указанные функциональные узлы 23, 25, 27 включены последовательно между выходом вычитающего

блока 15 и сигнальным входом 28 аттенюатора 29. выход 30 которого соединен с третьим входом сумматора 20, а управляющий вход 31 - с выходом 32 датчика 9 тока.

Селектор 17 минимального сигнала содержит операционный усилитель 33 (фиг.2), неинвертирующий вход которого подключен к входу 16, а инвертирующий вход - к входу 18. Выход операционного усилителя 33 через встречно включенный диод 34 связан

с затвором n-канального полевого транзистора 35, исток которого соединен с входом 16, а сток - с выходом 19. Между истоком и стоком транзистора 35 включен резистор 36. Между входом 18 и выходом 19 включен

р-канальный полевой транзистор 37, затвор

которого через резистор 38 связан с его

истоком и через согласно включенный диод

39 - с выходом операционного усилителя 33.

Проходно гемент 25 с узкой зоной

нечувствительности содержит операционный усилитель 40 (фиг.З), виход которого через диод 41 связан с егс инвертирующим входом и с выходом 26. Выход 24, являющийся одновременно выходом блока 23 выделения модуля сигнала, через резистор 42 связан с неинвертирую %им входом операци онного усилителя 40, который через резистор 43 подключен к источнику 44 отрицательного опорного напряжения.

Дискретный управляемый выпрямитель

1 может быть выполнен по любой из схем, обеспечивающих пропорциональную зависимость (с учетом дискретизации по уровню) выходного выпрямленного напряжения от

5 потенциала на его управляющем входе.

Для обеспечения наилучших энергетических характеристик дискретный управляемый выпрямитель 1 предпочтительно выполнять на основе ключевых элементов. Вместе с тем для исключения импульсных помех и искажений формы входного сетевого напряжения этот выпрямитель не должен быть с фазовой регулировкой среднего значения выпрямленного напряжения. Это так- же необходимо для уменьшения массы и габаритов индуктивно-емкостных фильтров. Обязательным требованием является минимизация дискретности изменения выходного напряжения. Для исключения импульсных помех и искажения формы сетевого напряжения недостаточно отказа от фазовых регулировок, обязательным требованием является также коммутация цепей в моменты прохождения тока нагрузки через нуль.

В наибольшей степени всем этим требованиям удовлетворяет выпрямитель с трансформатором, имеющим коммутируемые обмотки, цифроаналоговым преобразователем и синхронизатором моментов коммута- ции. Один из возможных вариантов такого дискретного управляемого выпрямителя 1 содержит трансформатор 45 (фиг.4), первичная обмотка 46 которого подключена к выводам 2 и 3, а вторичная обмотка выполнена в виде изолированных секций 47.1-47.k с удвоенным числом витков в каждой последующей секции. Число витков наименьшей из секций определяет дискретность изменения выпрямленного напряжения. Число сек- ций k определяется, исходя из требуемого числа дискрет т. для обеспечения наибольшего требуемого от выпрямителя 1 напряжения при максимальной нагрузке и минимальном напряжении сети с необходимым запасом. Величины m и k связаны между собой выражением .

Для коммутации секций 47.1-47.k вторичной обмотки служат двухполюсные переключатели 48.1-48.k, каждый из которых при поступлении потенциала на его управляющий вход должен включать соответствующую секцию в общую цепь, а при отсутствии управляющего потенциала создавать связь для обхода данной секции. Управляющие входы переключателей 48.1-48.k соединены с выходами соответствующих элементов И 49.1-49.k, первые входы которых подключены к соответствующим выходам преобразователя 50 напряжение-код. Вход последнего со- единен с управляющим входом 22. Вторые входы элементов И 49.1-49.k объединены и подключены к выходу генератора 51 импульсов, а их третьи входы также объединены и подключены к выходу порогового элемента 52. Вход порогового элемента 52 соединен

с выводом шунта 53, который включен в цепь связи вторичной обмотки трансформатора 45 с диодным мостом 54. Выходы диодного моста 54 через фильтр 55 нижних частот связаны с выводами 4 и 5. Переключатели 48.1-48.k выполнены в виде пары симисторов с гальванической развязкой (например, оптрон- ной) управляющих электродов. Один из симисторов каждого переключателя управляется прямым потенциалом с выхода соответствующего из элементов И 49.1-49.k, a другой симистор управляется инверсным потенциалом (на схеме не показано).

Управляемый стабилизирующий источник напряжения постоянного тока работает следующим образом.

На управляющую шину 13 подается задающий сигнал V3, (фиг.5) пропорциональный требуемому выходному напряжению устройства на выходах 10 и 11, т.е. напряжение VH на нагрузке. Для удобства и большей наглядности все напряжения здесь и в дальнейшем представлены в нормированном виде. Поэтому можно утверждать, что задачей всего устройства является обеспечение равенства VH V3 при любых изменениях задающего сигнала, при колебаниях тока нагрузки, при изменениях внутренних ЭДС нагрузки.

Ввиду широкого диапазона изменений указанных параметров для обеспечения стабилизации требуемого напряжения с необходимым качеством при высоком КПД и хороших массогабаритных показателях предусмотрены два силовых блока, участвующих в регулировании выходного напряжения.

Дискретный выпрямитель 1 служит для грубого дискретного регулирования напряжения, имеет высокие энергетические характеристики (в том числе и КПД) при минимальных массе и габаритах. Однако он не позволяет получить высокую точность поддержания напряжения на нагрузке, имеет неудовлетворительные динамические характеристики. Поэтому его основной функцией является обеспечение оптимальным напряжением питания компенсационного стабилизатора 8 напряжения. Последний при поддержании на его входных питающих выводах 6 и 7 минимального, но достаточного для качественной стабилизации напряжения на нагрузке также имеет хорошие массогабаритные и энергетические характеристики и обеспечивает точное поддержание требуемого выходного напряжения в соответствии с напряжением на его управляющем входе 14.

Все остальные блоки служат для того, чтобы обеспечить для разных режимов работы устройства при любых изменениях перечисленных выше параметров оптимальное

напряжение на питающем входе стабилизатора 8 путем установления соответствующего коэффициента передачи выпрямителя 1. Устройство в зависимости от характера и величины изменения параметров работает в двух режимах. Первый режим - это основной режим при установившихся значениях всех параметров (входного управляющего сигнала, выходного напряжения, токов нагрузки, внутренних ЭДС нагрузки). В этом же режиме устройство работает при незначительных колебаниях указанных параметров и при их значительных, но плавных изменениях, В указанных условиях необходимо обеспечивать превышение входного питающего напряжения стабилизатора 8 напряжения над напряжением на нагрузке на минимальном уровне, достаточном для обеспечения требуемого качества напряжения на нагрузке. Второй режим - зто режим ускоренной отработки более значительных резких (скачкообразных) изменений упомянутых выше параметров. В этом режиме стабилизатору 8 задастся предельно допустимое, но не опасное для него превышение входного питающего напряжения над меньшим из двух напряжений - над выходным напряжением, поступающим на нагрузку, или над задающим сигналом./

Критерием для перехода из режима в режим является разница между заданным управляющим напряжением и напряжением на нагрузке. Если эта разница не превышает определенного наперед заданного значения 5, то устройство работает в первом режиме. При этом напряжение на выходе выпрямителя 1 (т.е. напряжение на питающем входе стабилизатора 8) превышает напряжение на нагрузке (т.е. напряжение на выходе стабилизатора 8) на минимальную величину , достаточную для получения требуемого качества напряжения на нагрузке. Если же разница между заданным управляющим напряжением и фактическим напряжением на нагрузке достигает и превышает значение д, то устройство переходит во второй режим для быстрейшего завершения переходного процесса. При этом напряжение на выходе выпрямителя 1 возрастает относительно минимальной величины ДУмин пропорционально отклонению выходного напряжения от заданного. Однако это повышение напряжения относительно первого режима осуществляется таким образом, что перепад напряжений на входе и выходе стабилизатора 8 не превышает максимальную для данного тока нагрузки величину AVMaKc, при которой обеспечивается надёжная безопасная работа стабилизатора 8..

Величина д допустимого критического отклонения выходного напряжения от заданного определяет величину зоны нечувствительности проходного элемента 25. Если

разностный сигнал не превышает д , то сигнал, равный его абсолютной величине, не проходит через элемент 25. Поэтому на третий вход аналогового сумматора 20 поступает нулевой потенциал с управляемого аттенюа0 тора 29. В этом режиме выходной потенциал сумматора 20 равен сумме с задатчи- ка 21 и меньшего из двух напряжений, выявляемых селектором 17 минимального сигнала. Если же разница между заданным

5 напряжением и напряжением на нагрузке по модулю превышает величину д зоны нечувствительности (это может быть только в переходных режимах), то разностный сигнал с выхода вычитающего блока 15, приве0 денный блоком 23 выделения модуля сигнала к положительной полярности, проходит через элемент 25, блоки 27 и 29 и добавляется в сумматоре 20 к сумме ДУМин меньшего из напряжений, выделяемых се5 лектором 17.

Выходной сигнал сумматора 20, поступая на управляющий вход выпрямителя 1, устанавливает на его выходе напряжение, превышающее напряжение на нагрузке (или

0 заданное напряжение) на величину в пределах от минимального значения ДУМин до предельно допустимого безопасного для данного тока значения Д /макс.

Благодаря логарифмической характери5 стике блока 27 обеспечивается наибольшее относительное повышение напряжения на входе стабилизатора 8 при малых превышениях величины д по сравнению с большими превышениями этой величины. Поэтому лю0 бые, даже малые отклонения выходного напряжения от заданного устраняются с наибольшей эффективностью. В то же время при больших отклонениях не происходит недопустимого перепада напряжений на

5 стабилизаторе 8. Благодаря плавности логарифмической характеристики создаются наиболее благоприятные условия для затухания переходных процессов по сравнению с ключевой характеристикой, согласно которой

0 при малых напряжениях на стабилизатор 8 подается сразу предельно допустимое напряжение.

Кроме того, датчик 9 тока также вносит коррективы в величину вырабатываемого вы5 прямителем 1 напряжения для стабилизатора 8. При увеличении тока нагрузки неизбежно растет и выделяемая в регулирующем органе стабилизатора 8 мощность. Чтобы стабилизатор 8 не вышел из строя при больших

токах, происходит снижение уровня предельного перепада напряжений между его питающим входом и выходом благодаря действию аттенюатора 29,

На графике (фиг.5) упрощенно показаны изменения основных напряжений в разных режимах в нормализованной форме.

До момента времени Ti первый режим имеет место в установившемся режиме и при незначительных отклонениях напряжения нагрузки от заданного напряжения. При таких незначительных отклонениях стабилизатор 8 способен без повышения его входного питающего напряжения обеспечить требуемое качество стабилизации напряжения. Задающее управляющее напряжение Us изображено штрих-пунктирной линией, напряжение на нагрузке UH - сплошной утолщенной линией, а напряжение на управляющем входе выпрямителя Uy - сплошной тонкой линией. В уста- новившемся режиме напряжение на нагрузке ниже заданного напряжения, но на фиг.5 эти два напряжения показаны одной сплошной утолщенной линией ввиду очень малого их различия. Однако этого различия достаточно для того, чтобы в селекторе 17 минимал ьного сигнала на выходе операционного усилителя 33 с большим коэффициентом усиления вырабатывался положительный сигнал, который через диод 39 открывает полевой транзистор 37, обеспечивающий связь входа 18 с выходом 19 селектора. При этом транзистор 35 закрыт, сигнал заданного напряжения не проходит через селектор 17, а сигнал на первом входе сумматора 20 равен напряжению на нагрузке.

В это время минимальный разностный сигнал с выхода вычитающего блока 15 приводится блоком 23 выделения модуля сигнала к положительной полярности. Этот разностный сигнал меньше зоны нечувствительности элемента 25, поэтому он не проходит через него и не доходит до сумматора 20. В связи с этим сигнал с выхода сумматора 20 в первом режиме равен сумме выходного напряжения на нагрузке и минимального дополняющего напряжения, вырабатываемого задатчиком 21:

Vy VH+ ДУмин.

Выпрямитель 1 обеспечивает установление пропорционального этому сигналу напряжения на выходных выводах 4 и 5. При этом управляющий сигнал преобразуется преобразователем 50 в пропорциональный двоичный код. При низких уровнях тока через шунт 53 (практически при прохождении тока через нуль) пороговый элемент 52 вырабатывает разрешающий потенциал на третьих (верхних по схеме) входах элементов И 49.1-49.k. Импульсы генератора 51

вызывают срабатывание переключателей 48.1-48.k в соответствии с кодом преобразователя 50. При этом включаются секции, суммарное число витков которых пропорци- 5 опально требуемому напряжению. На выходах 6 и 7 стабилизатора 8 устанавливается напряжение, превышающее напряжение на выводах 10 и 11 на минимальную величину ДУмин, достаточную для осуществления ка0 чественной стабилизации напряжения на нагрузке при максимальном КПД.

При плавных изменениях управляющего напряжения с момента TI до Т2 выпрямитель 1 обеспечивает все то же минимально

5 необходимое превышение входного питающего напряжения стабилизатора 8 над плавно изменяемым напряжением нагрузки, достаточное для осуществления качественной стабилизации напряжения на нагрузке.

0 В момент Тз вследствие значительного повышения нагрузочного тока или возникновения внутренних противоЭДС в нагрузке начинается спад выходного напряжения, который стабилизатор 8 не в состоянии

5 скомпенсировать при минимальном превышении напряжения на его питающем входе над требуемым напряжением (именно над требуемым напряжением, которое выше фактического напряжения на нагрузке). В

0 момент Тз, когда разница между задаваемым и фактическим напряжениями на нагрузке превышает допустимую критическую величину, т.е. когда (VH - V3) д , абсолютная величина разностного напряжения превы5 шает зону нечувствительности элемента 25. Сигнал, прошедший через элемент 25, имеет малый уровень и поэтому в наибольшей степени усиливается логарифмирующим блоком 27. Усиленный сигнал проходит че-

0 рез аттенюатор 29 и в сумматоре 20 добав- - ляется к сумме напряжения на нагрузке и ДУмин, т.е. устройство плавно переходит во второй режим. По мере увеличения отклонения напряжения на нагрузке от заданного

5 напряжения происходит увеличение управляющего напряжения на выходе сумматора 20 и увеличение превышения входного питающего напряжения стабилизатора 8 над его выходным напряжением. Однако благодаря

0 логарифмической характеристике блока 27 нарастание этого превышения происходит не прямо пропорционально. С ростом отклонения нарастание уменьшается все в большей степени. При неограниченном росте откло5 нения напряжения на нагрузке от заданного напряжения перепад напряжений между входом и выходом компенсационного стабилизатора 8 стемится к максимально допустимой величине ДУмакс, при которой еще

не происходит выход стабилизатора 8 из строя, Однако а период спад напряжения на нагрузке не столь значителен, чтобы вызвать максимальное превышение напряжения на питающем входе стабилизатора 8 по отношению к выходному напряжению.

Если снижение напряжения на нагрузке вызывается значительным ростом нагрузочного тока, то происходит увеличение сигнала, поступающего с датчика 9 тока нз управляющий вход 31 аттенюатора 29.

Это может происходить и без снижения напряжения на нагрузке. Рост сигнала вызывает увеличение ослабления, вносимого аттенюатором 29, что ведет к меньшему нарастанию сигналь на третьем аходе сумматора 20 по срапнению с его нарастанием при малых токах нагрузки. По названной причине превышение входного питающего напряжения стабилизатора 8 также меньше (штриховая линия на фиг.5). Благодаря этому исключается выход из строя стабилизатора 8 мз-за одновременного повышения падения напряжения на его регулирующем элементе (не показан) и увеличения тока через него.

В момент ТБ, ко да разница-между задаваемым и фактическим напряжениями на нагрузке уменьшается до уровня критической, потребность в максимальном превышении напряжения на питающем входе стабилизатора 8 над напряжением нагрузки отпадает и устройство переходит в первый режим.

В момент Т происходит резкое многократное увеличение задающего напряжения на управляющей шине 13 устройства. Казалось бы для максимального ускорения переходных процессов следовало немедленно увеличить напряжение на питающем входе стабилизатора 8. Однако это привело бы к отказу последнего. Кроме того, резкий переходный процесс вызвал бы перерегулирование, затягивающее установление требуемого напряжения,

Наиболее оптимальным в таких условиях является переход устройства во второй режим работы, когда превышение напряжения на питающем входе стабилизатора 8 над напряжением на нагрузке составляет величину ДУмакс. причем превышение именно над фактическим напряжением нагрузки.

Это исключает выход стабилизатора 8 из строя. Между тем по мере роста напряжения на нагрузке с максимально возможной скоростью происходит увеличение напряжения на питающем входе стабилизатора 8 при его безопасном режиме,

В момент Те имеет место постепенный плавный переход а первый режим и стабилизатор 8 вновь работает в наиболее экономичном режиме, достаточном однако для осуществления качественной стабилизации выходного напряжения.

Если в момент Т го происходит резкое

скачкообразное снижение задающего напряжения, то немедленно возникают резкий сброс напряжения на выходе управляющего комплексного стабилизатора 8 до уровня Vy2 ° V3 + Л /МЕХС и изменение режима рабо0 ты. Теперь до момента Т11 стабилизатор 8 полностью закрыт и не выдает энергию в нагрузку.

Однако по мере уменьшения отклонения напряжения на нагрузке от заданного

5 напряжения происходит плавное уменьшение превышения входного питающего напряжения стабилизатора 8 над заданным напряжением. К моменту Тп устройство плавно переходит в первый наиболее экономичный

0 режим работы и стабилизатор 8 постепенно начинает передавать энергию в нагрузку и стабилизировать выходное напряжение.

Таким образом обеспечивается сочетание высоких динамических характеристик

5 устройства при значительных скачкообразных изменениях задающего напряжения, тока нагрузки, внутренних ЭДС нагрузки с высокой надежностью, с высокими энергетическими и массогабаритными показагеля0 ми, с высоким качеством стабилизируемого выходного напряжения в установившихся режимах.

Формула изобретения

1, Управляемый стабилизирующий ис5 точник напряжения постоянного тока, содержащий дискретный выпрямитель и компенсационный стабилизатор напряжения, включенные в силовой канал между выводами для подключения первичного

0 источника питания и нагрузки, источник управляющего напряжения, выход которого соединен с опорным входом стабилизатора напряжения, датчик напряжения, вход которого подключен к выходу стабилизатора напря5 женин, аналоговый сумматор, первый вход которого соединен с выходом, задатчика минимального падения напряжения на стабилизаторе напряжения, отличающийся тем, что, с целью повышения качества ста0 билизации, надежности работы и КПД, в него введены датчик тока, селектор минимального сигнала, вычитающий блок, блок выделения модуля сигнала, проходной элемент с узкой зоной нечувствительности, логариф5 мирующий блок и аттенюатор, причем датчик тока включен в цепь между выходом выпрямителя и питающим входом стабилизатора напряжения, первые входы селектора минимального сигнала и вычитающего блока соединены с выходом источника уп:

равняющего напряжения, а их вторые входы - с выходом датчика напряжения, выход селектора минимального сигнала подключен к второму входу сумматора, блок выделения модуля сигнала, проходной элемент и логарифмический блок включены последовательно между выходом вычитающего блока и сигнальным входом аттенюатора, управляющий вход аттенюатора соединен с выходом датчика тока, а выход - с третьим входом сумматора, выход которого подключен к управляющему входу выпрямителя.

fiff

т

472

С-4Ще-432

0

5

неинвертирующий и инвертирующий входы которого использованы в качестве соответственно первого и второго входов данного функционального узла, п- и р-канальные полевые транзисторы, истоки которых соединены с потенциальными выводами соответственно неинвертирующего и инвертирующего входов операционного усилителя, затворы через разнонаправленные диоды - с выходным потенциальным выводом последнего, а стоки объединены между собой и использованы в качестве выходного потенциального вывода данного функционального узла, два резистора, включенных между затворами и истоками соответствующих полевых транзисторов.

36i

11

35

19

фие.1

фие.З

К-55

± 5

50

43

Фие.Ь

22

77 ТI T3W75T6 77 7879 ПО ///

Фие.5

| Авторское свидетельство СССР № 1228680, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1422879, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-09-23—Публикация

1989-10-23—Подача