О СО 00

00

оо

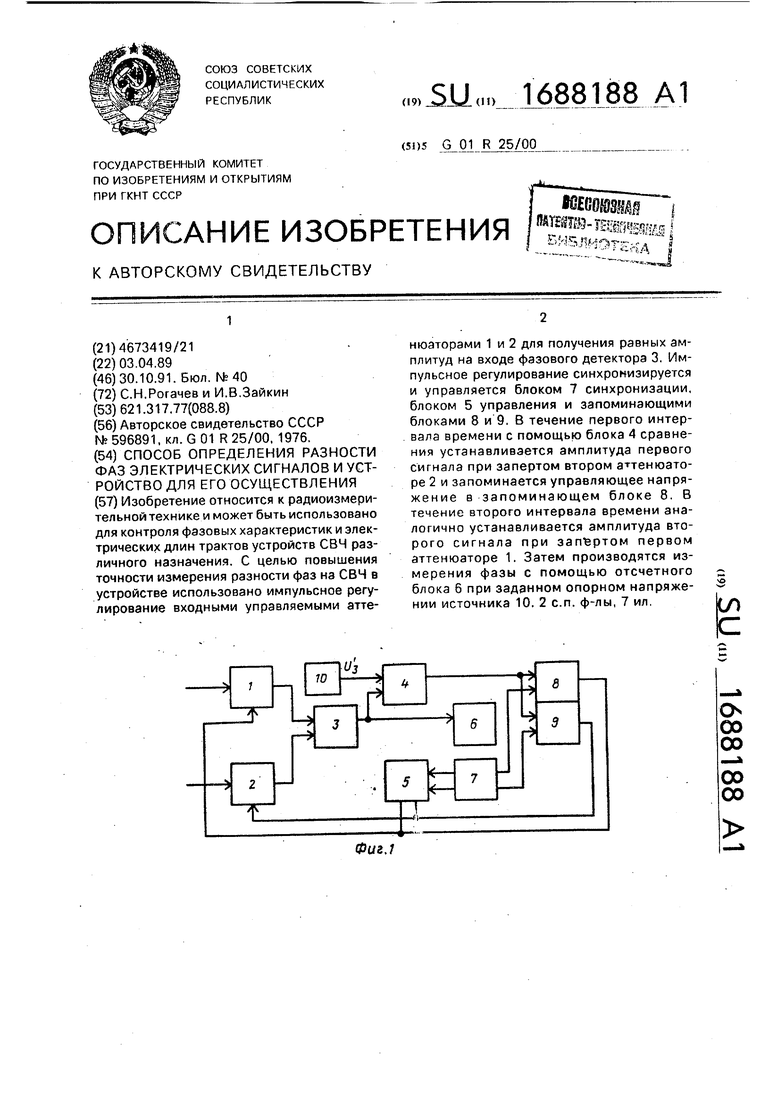

Изобретение относится к радиоизмерительной технике, предназначено для определения разности фаз сигналов в широком диапазоне частот и может быть использовано в технике СВЧ для контроля фазовых характеристик и электрических длин различных устройств.

Цель изобретения - повышение точности измерения разности фаз при работе на сверхвысоких частотах.

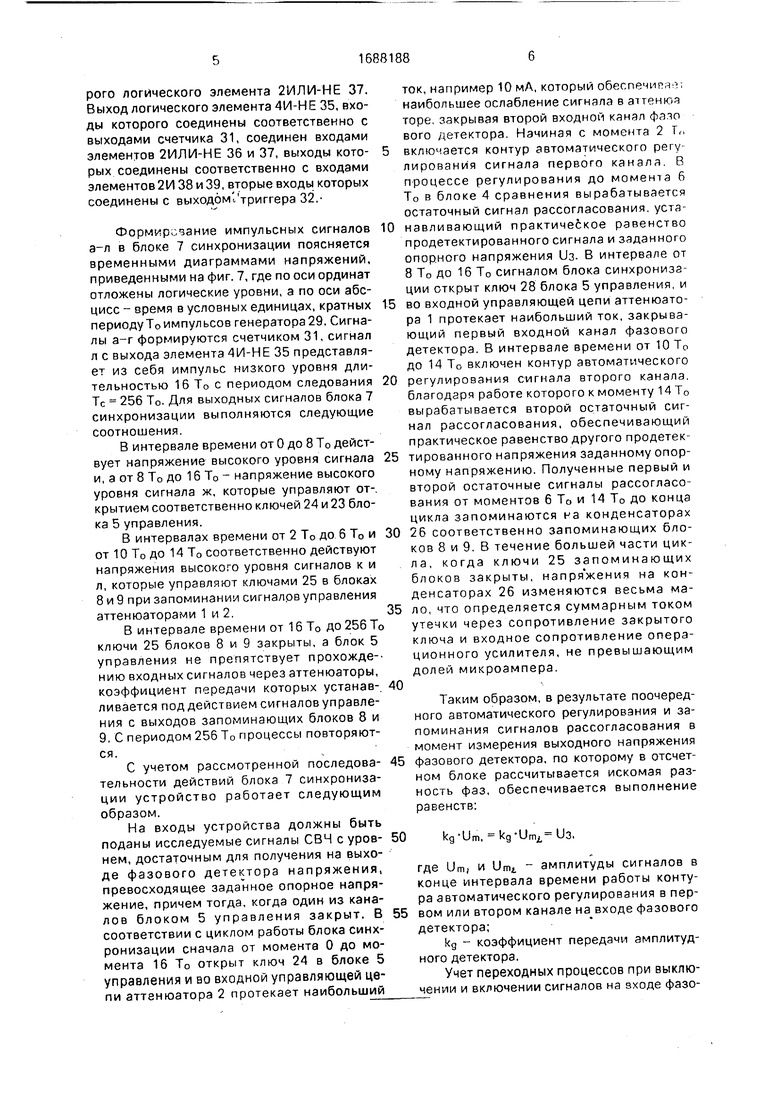

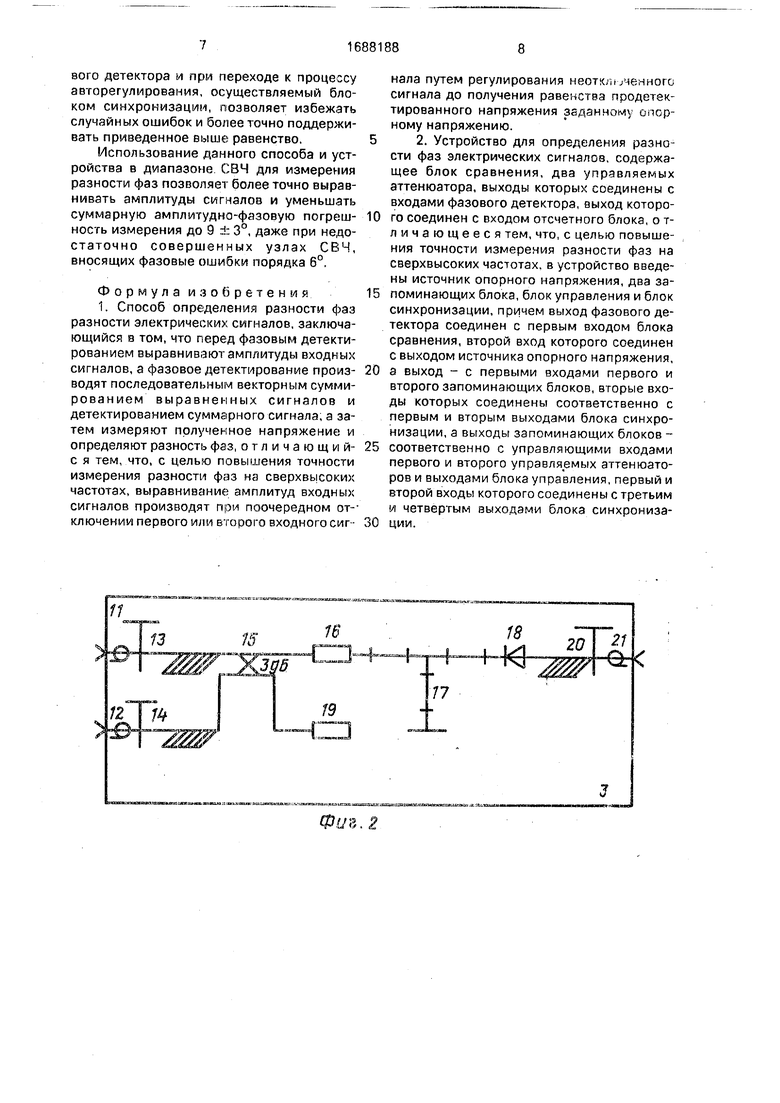

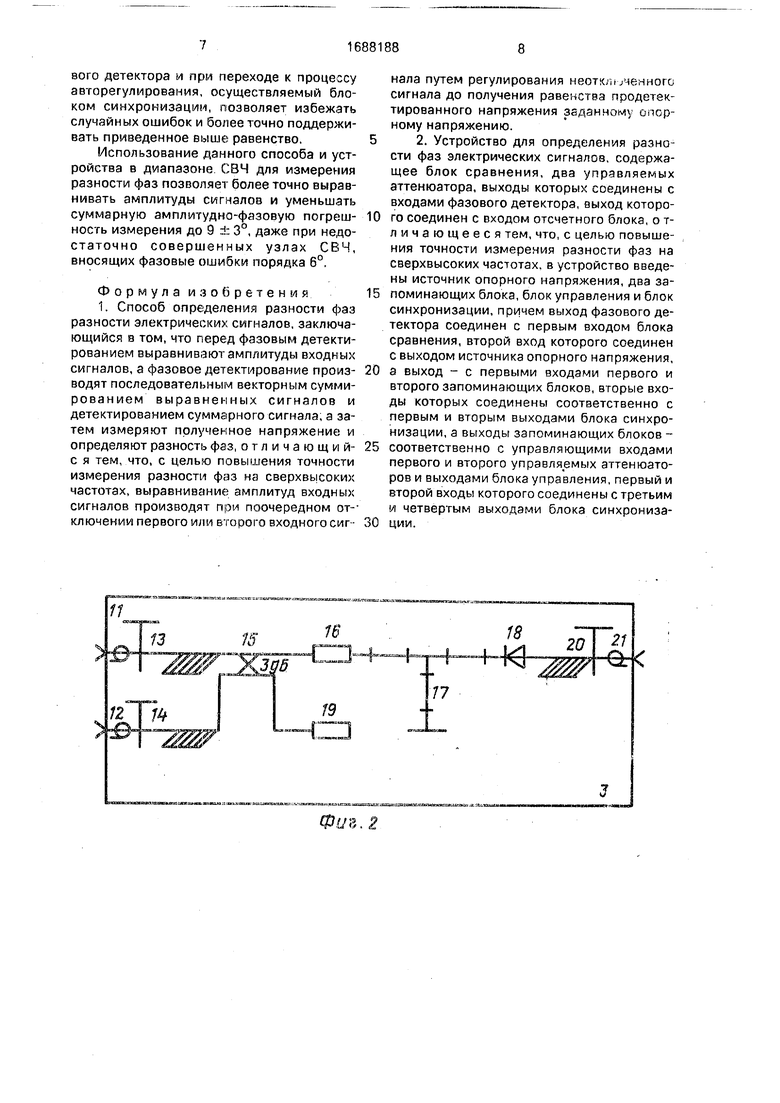

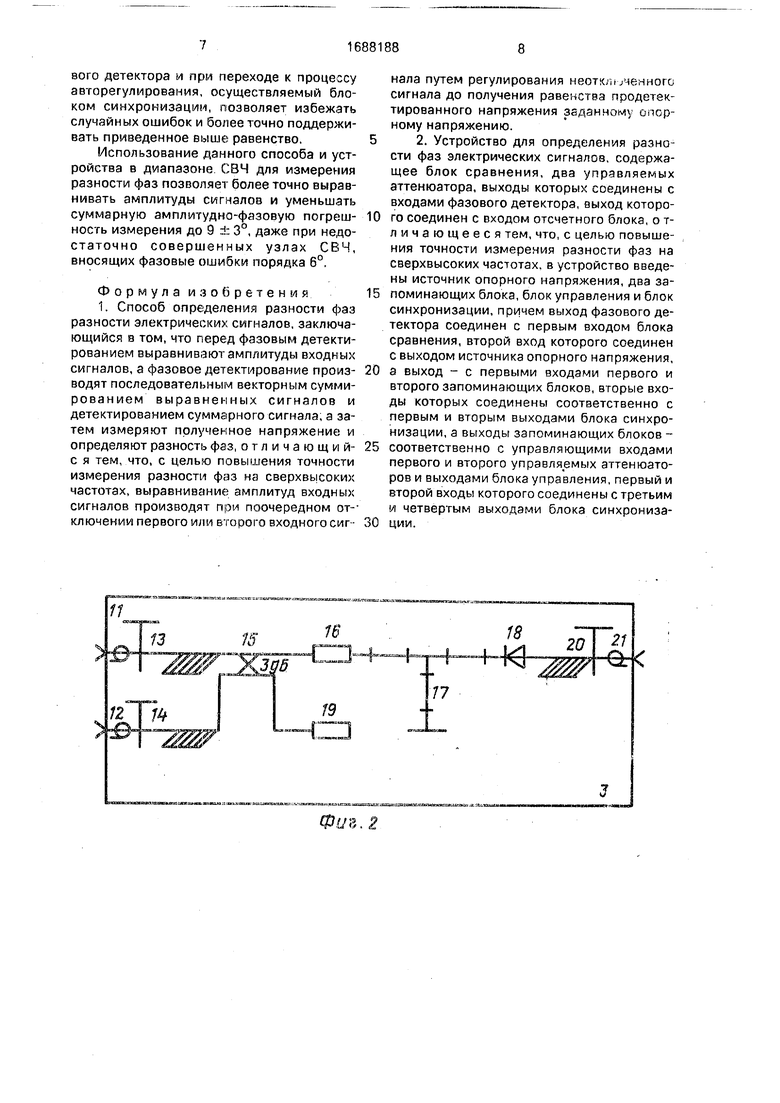

На фиг. 1 приведена структурная схема устройства, реализующего способ измерения разности фаз электрических сигналов; на фиг. 2 приведена схема фазового детектора СВЧ, для которого применим данный способ; на фиг, 3 представлена схема блока сравнения; на фиг. А - схема блока управления; на фиг. 5 - схема запоминающего блока; на фиг. 6 - схема блока синхронизации; на фиг. 7 даны временные диаграммы напряжений в цепях блока синхронизации.

Способ применим в том случае, когда фазовое детектирование осуществляется путем векторного суммирования сигналов с последующим амплитудным детектированием суммарного сигнала. Для более точного выравнивания сигналов на входе их поочередно отключают, а неотключенный сигнал регулируют, добиваясь равенства продетектированного напряжения с заданным опорным напряжением. Затем измеряют продетектированное напряжение при подаче на вход обоих входных сигналов и определяют разность фаз р, используя формулу

E(p) U3

1 ± cos р

где Е (р) - выходное продетектированное напряжение;

Уз заданное опорное напряжение.

Способ реализован в устройстве, схема которого приведена на фиг. 1.

Устройство содержит управляемые аттенюаторы 1, 2, фазовый детектор 3, блок 4 сравнения, блок 5 управления, отсчетный блок 6, блок 7 синхронизации, два запоминающих блока 8 и 9, источник 10 опорного напряжения.

Выходы управляемых аттенюаторов 1 и 2 соединены с входами фазового детектора 3, выход которого соединен с входом отсчет ного блока 6 и первым входом блока 4 сравнения, второй вход которого соединен с выходом источника 10 опорного напряжения, управляющие входы управляемых аттенюаторов 1 и 2 соединены с выходами блока 5 управления и соответствующими выходами запоминающих блоков 8 и 9, первые входы которых подсоединены к выходу блока 4 сравнения, а вторые входы - соответственно к первому и второму выходам блока 7 синхронизации, третий и четвертый выходы

которого соединены с первым и вторым входами блока 5 управления.

Фазовый детектор, применяемый в диапазоне СВЧ, содержит входные соединители 11 и 12, которые через переходы и 14 и

0 полосковые линии передачи соединены с входами направленного ответвителя15. Один из выходов направленного ответвите- пя 15 через резистор 16 и согласующий шлейф 17 соединен с амплитудным детекто5 ром 18, диодом СВЧ. Второй выход направленного ответви.теля 15 соединен с согласованной нагрузкой 19. Выход амплитудного детектора 18 через переход 20 соединен с выходным соединителем 21.

0Блок 4 сравнения, показанный на фиг.

3, содержит операционный усилитель 22, для повышения устойчивости которого в цепи обратной связи используется резисторы и конденсаторы. Блок 4 сравнения

5 вырабатывает сигнал рассогласования, управляющий коэффициентом передачи аттенюаторов 1 и 2.

Блок 5 управления, предназначенный для поочередного закрывания вход0 ных каналов фазового детектора на время регулирования амплитуды сигнала в неотключенном канале, содержит, как показано ча фиг. 4, два электрбнных ключа 23 и 24 и резисторы, подключенные к выводам

5 Х1, Х2 ключей и ограничивающие ток управляющего сигнала. Ключи открыты при подаче на их управляющие входы Y1 и Y2 напряжений высокого уровня.

Запоминающие блоки 8 и 9, выполнен0 ные по схеме фиг. 5, состоят из ключа 25, запоминающего конденсатора 26, операционного усилителя 27, включенного по схеме повторителя напряжения, и резистора 28, ограничивающего ток нагрузки.

5Блок7 синхронизации, выполненный по

схеме фиг. 6. содержит генератор 29 импульсов, частота следования которых стабилизирована кварцем 30, восьмиразрядный двоичный счетчик 31, D-триггер 32. два ин0 вертора 33, 34, четырехвходовый элемент 4И-НЕ 35, два элемента 2ИЛИ-НЕ 36 и 37 и два элемента 2И 38 и 39. Выход генератора 29 соединен со счетнкм входом двоичного счетчика 31, выход второго разряда которо5 го соединен с входом С синхронизации триггера 32, выход третьего разряда через инвертор 33 - с входом D триггера 32. а выход четвертого разряда - с одним из входов логического элемента 2ИЛИ-НЕ 36 и через инвертор 34 - с одним из входов второго логического элемента 2ИЛИ-НЕ 37. Выход логического элемента 4М-НЕ 35. входы которого соединены соответственно с выходами счетчика 31, соединен входами элементов 2ИЛИ-НЕ 36 и 37, выходы кото- рых соединены соответственно с входами элементов 2И 38 и 39, вторые входы которых соединены с выходом триггерэ 32.

Формир тание импульсных сигналов а-л в блоке 7 синхронизации поясняется временными диаграммами напряжений, приведенными на фиг. 7, где по оси ординат отложены логические уровни, а по оси абсцисс - время в условных единицах, кратных периоду Т0 импульсов генератора 29. Сигналы а-г формируются счетчиком 31, сигнал л с выхода элемента 4И-НЕ 35 представля- ет из себя импульс низкого уровня длительностью 16 Т0 с периодом следования Тс 256 Т0. Для выходных сигналов блока 7 синхронизации выполняются следующие соотношения.

В интервале времени от 0 до 8 Т0 действует напряжение высокого уровня сигнала и, а от 8 Т0 до 16 Т0 - напряжение высокого уровня сигнала ж, которые управляют открытием соответственно ключей 24 и 23 блока 5 управления.

В интервалах времени от 2 Т0 до 6 Т0 и от 10 Т0 до 14 Т0 соответственно действуют напряжения высокого уровня сигналов к и л, которые управляют ключами 25 в блоках

8и 9 при запоминании сигналов управления аттенюаторами 1 и 2

В интервале времени от 1 6 Т0 до 256 Т ключи 25 блоков 8 и 9 закрыты, а блок 5 управления не препятствует прохождению входных сигналов через аттенюаторы коэффициент передачи которых устанав- ливается под действием сигналов управления с выходов запоминающих блоков 8 и

9С периодом 256 Т0 процессы повторяются.

С учетом рассмотренной последова- тельности действий блока 7 синхронизации устройство работает следующим образом.

На входы устройства должны быть поданы исследуемые сигналы СВЧ с уров- нем, достаточным для получения на выходе фазового детектора напряжения, превосходящее заданное опорное напряжение, причем тогда, когда один из каналов блоком 5 управления закрыт. В соответствии с циклом работы блока синхронизации сначала от момента 0 до момента 16 То открыт ключ 24 в блоке 5 управления и во входной управляющей цепи аттенюатора 2 протекает наибольший

ток, например 10 мЛ, который об гпрчи 1 н наибольшее ослабление сигнала в горе закрывая второй входной канал фтп вого детектора Начиная с момента 2 1, включается контур автоматического регулирования сигнала первого канала Р процессе регулирования до момента 6 Т0 в блоке 4 сравнения вырабатывается остаточный сигнал рассогласования ycia навливающий практическое равенство продетектированного сигнала и заданного опорного напряжения 11з. В интервале от 8 То до 16 То сигналом блока синхронная ции открыт ключ 28 блока 5 управления, и во входной управляющей цепи аттенюато ра 1 протекает наибольший ток, закрывающий первый входной канал фазового детектора В интервале времени от 10 Тс, до 14 Т0 включен контур автоматического регулирования сигнала второго каната благодаря работе которого кмомрнту 14 Т 0 вырабатывается второй остаточный сиг нал рассогласования, обеспечивающий практическое равенство другого продетек тированного напряжения заданному опор ному напряжению. Полученные первый и второй остаточные сигналы рассогласо вания от моментов 6 Т0 и 14 Т0 до конца цикла запоминаются на конденсаторах 26 соответственно запоминающих блоков 8 и 9 В течение большей части цикла, когда ключи 25 запоминающих блоков закрыты, напря жения на конденсаторах 26 изменяются весьма мало, чго определяется суммарным током утечки через сопротивление закрытого ключа и входное сопротивление операционного усилителя, не превышающим долей микроампера.

Таким образом, в результате поочередного автоматического регулирования и запоминания сигналов рассогласования в момент измерения выходного напряжения фазового детектора, по которому в отсчет- ном блоке рассчитывается искомая разность фаз, обеспечивается выполнение равенств:

kg-Dm, kg-Umi Do.

где Um, и итл амплитуды сигналов в конце интервала времени работы контура автоматического регулирования в первом или втором канале на входе фазового детектора;

kg - коэффициент передачи амплитудного детектора.

Учет переходных процессов при выключении и включении сигналов на входе фазового детектора и при переходе к процессу авторегулирования, осуществляемый блоком синхронизации, позволяет избежать случайных ошибок и более точно поддерживать приведенное выше равенство.

Использование данного способа и устройства в диапазоне СВЧ для измерения разности фаз позволяет более точно выравнивать амплитуды сигналов и уменьшать суммарную амплитудно-фазовую погреш- ность измерения до 9 ± 3°, даже при недостаточно совершенных узлах СВЧ, вносящих фазовые ошибки порядка 6°.

Ф о р м у л а и з о б р е т е н и я

1. Способ определения разности фаз разности электрических сигналов, заключающийся в том, что перед фазовым детектированием выравнивают амплитуды входных сигналов, а фазовое детектирование произ- водят последовательным векторным сумми- рованием выравненных сигналов и детектированием суммарного сигнала, а затем измеряют полученное напряжение и определяют разность фаз, отличающий- с я тем, что, с целью повышения точности измерения разности фаз на сверхвысоких частотах, выравнивание амплитуд входных сигналов производят при поочередном отключении первого или второго входного сиг-

нала путем регулирования неотюь.ченного сигнала до получения равенства продетек- тированного напряжения заданному опорному напряжению.

2. Устройство для определения разности фаз электрических сигналов, содержащее блок сравнения, два управляемых аттенюатора, выходы которых соединены с входами фазового детектора, выход которого соединен с входом отсчетного блока, о т- личающееся тем, что, с целью повышения точности измерения разности фаз на сверхвысоких частотах, в устройство введены источник опорного напряжения, два запоминающих блока, блок управления и блок синхронизации, причем выход фазового детектора соединен с первым входом блока сравнения, второй вход которого соединен с выходом источника опорного напряжения, а выход - с первыми входами первого и второго запоминающих блоков, вторые входы которых соединены соответственно с первым и вторым выходами блока синхронизации, а выходы запоминающих блоков - соответственно с управляющими входами первого и второго управляемых аттенюаторов и выходами блока управления, первый и второй входы которого соединены с третьим и четвертым выходами блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения ослабления СВЧ-четырехполюсников | 1982 |

|

SU1140059A2 |

| Устройство для измерения фазового сдвига СВЧ-четырехполюсников | 1982 |

|

SU1092426A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| Устройство для определения влажности | 1986 |

|

SU1425556A1 |

| Устройство для измерения ослабления СВЧ четырехполюсников | 1981 |

|

SU1010575A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство для измерения амплитудно-частотных и фазочастотных характеристик четырехполюсников с преобразователем частоты | 1989 |

|

SU1709242A1 |

| ИЗМЕРИТЕЛЬ ХАРАКТЕРИСТИК ФАЗОВЫХ ФЛУКТУАЦИЙ | 1992 |

|

RU2041469C1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Устройство для измерения влажности | 1987 |

|

SU1478107A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано для контроля фазовых характеристик и электрических длин трактов устройств СВЧ различного назначения. С целью повышения точности измерения разности фаз на СВЧ в устройстве использовано импульсное регулирование входными управляемыми аттенюаторами 1 и 2 для получения равных амплитуд на входе фазового детектора 3. Импульсное регулирование синхронизируется и управляется блоком 7 синхронизации, блоком 5 управления и запоминающими блоками 8 и 9. В течение первого интервала времени с помощью блока 4 сравнения устанавливается амплитуда первого сигнала при запертом втором аттенюаторе 2 и запоминается управляющее напряжение в запоминающем блоке 8. В течение второго интервала времени аналогично устанавливается амплитуда второго сигнала при запертом первом аттенюаторе 1. Затем производятся измерения фазы с помощью отсчетного блока 6 при заданном опорном напряжении источника 10. 2 с.п. ф-лы, 7 ил. Ё

Фиг. 2

L-czHh-L-czHH

С мф

goxg

д-гщ

1

8818891

| Двухканальный фазометр | 1976 |

|

SU596891A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-10-30—Публикация

1989-04-03—Подача