Изобретение относится к цифровой электронике и может использоваться в системах фазовой автоподстройки частоты (ФАПЧ).

Известен частотно-фазовый компаратор, содержащий две схемы И-НЕ, два блокирующих триггера и фазовый триггер, входы которого подключены к клеммам источников контролируемой и эталонной частоты, при этом инверсный выход первого из блокирующих триггеров подключен к первому входу первой схемы И-НЕ, второй вход которой подключен к инверсному выходу фазового триггера, а выход подключен к первому входу второй схемы И-НЕ, второй вход которой подключен к инверсному выходу второго блокирующего триггера, а выход является γ выходом частотно-фазового компаратора, две схемы И, схема ИЛИ, элемент задержки, два одновибратора и два триггера, синхро-входы которых подключены соответственно к источникам контролируемой и эталонной частоты, D входы которых подключены соответственно к прямому и инверсному выходу фазового триггера, а выходы подключены соответственно к входам первого и второго одновибраторов, при этом выход первого одновибратора подключен к первому входу первой схемы И, к первому входу схемы ИЛИ, к входу R первого триггера и является 2/2 выходом частотно-фазового компаратора, а выход второго одновибратора является 0/2 выходом частотно-фазового компаратора, подключен к первому входу второй схемы И, к входу R второго триггера, к второму входу схемы ИЛИ, выход которой через элемент задержки подключен к синхро-входам блокирующих триггеров, D вход первого из блокирующих триггеров подключен к выходу первой схемы И, второй вход которой подключен к инверсному выходу второго блокирующего триггера, вход D которого подключен к выходу второй схемы И, второй вход которой подключен к инверсному выходу первого блокирующего триггера, прямой выход которого является Т выходом частотно-фазового компаратора, Р выходом которого является прямой выход второго блокирующего триггера [Патент России № 2469461, МПК H03D 13/00, опубл. . 2012. Бюл. №341].

Недостатком указанного частотно-фазового детектора является низкая отказоустойчивость, наличие в устройстве схем одновибраторов, которые могут привезти к нестабильным состояниям схемы в режиме детектирования частоты. Схема имеет риски сбоя в режиме детектирования частоты, что понижает общую надежность устройства при использовании в системах автоматического регулирования частот.

Известен импульсный частотно-фазовый детектор, имеющий первый и второй входы; первый, второй и третий выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы; первый и второй логические элементы; тактовые входы первого, третьего и шестого запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены ко второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; установочные входы первого и третьего запоминающих элементов соединены между собой; информационный вход второго запоминающего элемента подключен к уровню логической единицы; информационный выход второго запоминающего элемента и второй вход первого логического элемента соединены между собой; установочный вход второго запоминающего элемента и выход первого логического элемента соединены между собой; информационный вход шестого запоминающего элемента и первый вход второго логического элемента соединены между собой; информационный выход шестого запоминающего элемента и второй вход второго логического элемента соединены между собой, третий, четвертый, пятый, шестой и седьмой логические элементы; выход третьего логического элемента подключен ко второму выходу устройства; выход четвертого логического элемента подключен к третьему выходу устройства; информационный вход первого запоминающего элемента подключен к уровню логической единицы; инвертированный информационный выход первого запоминающего элемента и первый вход пятого логического элемента соединены между собой; установочный вход первого запоминающего элемента и выход шестого логического элемента соединены между собой; первые входы третьего и седьмого логических элементов соединены между собой и подключены к информационному выходу второго запоминающего элемента; информационный выход третьего и информационный вход пятого запоминающих элементов и первый вход четвертого логического элемента соединены между собой; информационный вход четвертого запоминающего элемента и выход седьмого логического элемента соединены между собой; вторые входы третьего, четвертого и седьмого логических элементов и информационный выход четвертого запоминающего элемента соединены между собой; инвертированный информационный выход четвертого запоминающего элемента и второй вход пятого логического элемента соединены между собой; установочный вход четвертого запоминающего элемента, выход пятого и первый вход шестого логических элементов соединены между собой; третий вход пятого и второй вход шестого логических элементов соединены между собой и подключены к выходу первого логического элемента; информационный выход пятого запоминающего элемента, первый вход второго, третьи входы четвертого и шестого логических элементов соединены между собой; установочные входы пятого и шестого запоминающих элементов и выход второго логического элемента соединены между собой; тактовый вход пятого запоминающего элемента подключен к второму входу устройства [Патент России № 2530248, МПК H03D 13/00, опубл. 10.10.2014 г.].

Недостатком указанного импульсного частотно-фазового детектора является наличие рисков сбоя в режиме детектирования частоты, что понижает общую надежность устройства при использовании в системах автоматического регулирования частот.

Наиболее близким техническим решением к заявляемому изобретению является частотно-фазовый детектор, имеющий первый и второй входы; первый, второй, третий и четвертый выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы и первый логический элемент; тактовые входы первого и третьего запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены к второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; информационный выход второго и информационный вход четвертого запоминающих элементов и второй вход первого логического элемента соединены между собой и подключены ко второму выходу устройства; установочные входы первого и второго запоминающих элементов соединены между собой и подключены к выходу первого логического элемента; информационный вход второго запоминающего элемента подключен к уровню логической единицы, второй логический элемент; тактовые входы пятого и шестого запоминающих элементов соединены между собой и подключены к первому входу устройства; информационный выход третьего запоминающего элемента подключен к третьему выходу устройства; выход второго логического элемента подключен к четвертому выходу устройства; информационный вход первого и установочный вход пятого запоминающих элементов соединены между собой и подключены к инвертированному информационному выходу четвертого запоминающего элемента; установочные входы третьего и шестого запоминающих элементов соединены между собой и подключены к выходу первого логического элемента; установочный вход четвертого и информационный выход пятого запоминающих элементов соединены между собой; первый вход второго логического элемента и информационный вход шестого запоминающего элемента соединены между собой и подключены к информационному выходу четвертого запоминающего элемента; второй вход второго логического элемента и информационный выход шестого запоминающего элемента соединены между собой; информационный вход пятого запоминающего элемента подключен к уровню логической единицы [Патент России №2483434, МПК H03D 13/00, опубл. 27.05.2013 г.].

Недостатком выше указанного частотно-фазового детектора является наличие рисков сбоя (паразитных импульсов) в режиме детектирования частоты при отставании опорного сигнала в два и более раз. Данный частотно-фазовый детектор при использовании в составе контуре ФАПЧ, может произвести настройку выходной частоты на когерентные или кратные частоты опорного сигнала, что приведет к сбою системы.

Технической проблемой, решаемой созданием заявленного изобретения, является создание частотно-фазового детектора для использования в контуре фазовой автоподстройки частоты, который исключит возможность рисков сбоя в режиме частотного детектирования.

Технический результатам, обеспечиваемый изобретением, заключается в исключении возможности «захвата» когерентных и кратных частот опорного сигнала, что позволит избежать рисков сбоя в режиме частотного детектирования, увеличение стабильности работы системы контура ФАПЧ, повышение надежности частотно-фазового детектора, снижение энергопотребления и уменьшение занимаемой площади на кристалле.

Для достижения вышеуказанного технического результата частотно-фазовый детектор для контура фазовой автоподстройки частоты, выполнен содержащим шесть КМОП-ключей, два Т-триггера, JK-триггер, логический элемент 2ИЛИ-НЕ и логический элемент 2ИЛИ; причем первый вход устройства соединен с объединенными входами первого, третьего и пятого КМОП-ключей; второй вход устройства соединен с объединенными входами второго, четвертого и шестого КМОП ключей; С-вход первого Т-триггера соединен с объединенными выходы первого и второго КМОП-ключей; С-вход JK-триггера соединен с объединенными выходами третьего и четвертого КМОП-ключей; С-вход второго Т-триггера соединен с объединенными выходами пятого и шестого КМОП-ключей; второй выход устройства соединен с объединенными Т-входом первого Т-триггера, Q-выходом JK-триггера и С-входом третьего КМОП-ключа; второй вход логического элемента 2ИЛИ-НЕ соединен с объединенными J-входом JK-триггера, nQ-выходом второго Т-триггера и С-входом шестого КМОП-ключа; первый вход логического элемента 2ИЛИ-НЕ соединен с объединенными K-входом JK-триггера, nQ-выходом первого Т-триггера и С-входом второго КМОП-ключа; С-вход четвертого КМОП-ключа соединен с объединенными Т-входом второго Т-триггера, nQ-выходом JK-триггера; первый выход устройства соединен с объединенными Q-выходом первого T-триггера и С-входом первого КМОП-ключа; второй выход устройства соединен с объединенными Q-выходом второго триггера и С-входом пятого КМОП-ключа; первый вход логического элемента 2ИЛИ соединен с выходом логического элемента 2ИЛИ-НЕ; третий вход устройства соединен с объединенными вторым входом логического элемента 2ИЛИ и R-входом JK-триггера.

От прототипа предлагаемое устройство отличается тем, что используются входные КМОП-ключи, что позволяет избежать рисков сбоя в режиме частотного детектирования при использовании частотно-фазового детектора в составе контура ФАПЧ. Снижение энергопотребления и уменьшение занимаемой площади на кристалле обусловлено реализацией решения с наименьшим количеством элементов. Благодаря обратной связи управления КМОП-ключами, реализованной объединением выходов триггеров и управляющих С-входов КМОП-ключей, исключается возможность возникновения рисков сбоя (паразитных импульсов) в режиме детектирования частоты, а также повышается стабильность работы системы контура ФАПЧ.

Изобретение поясняется следующими материалами:

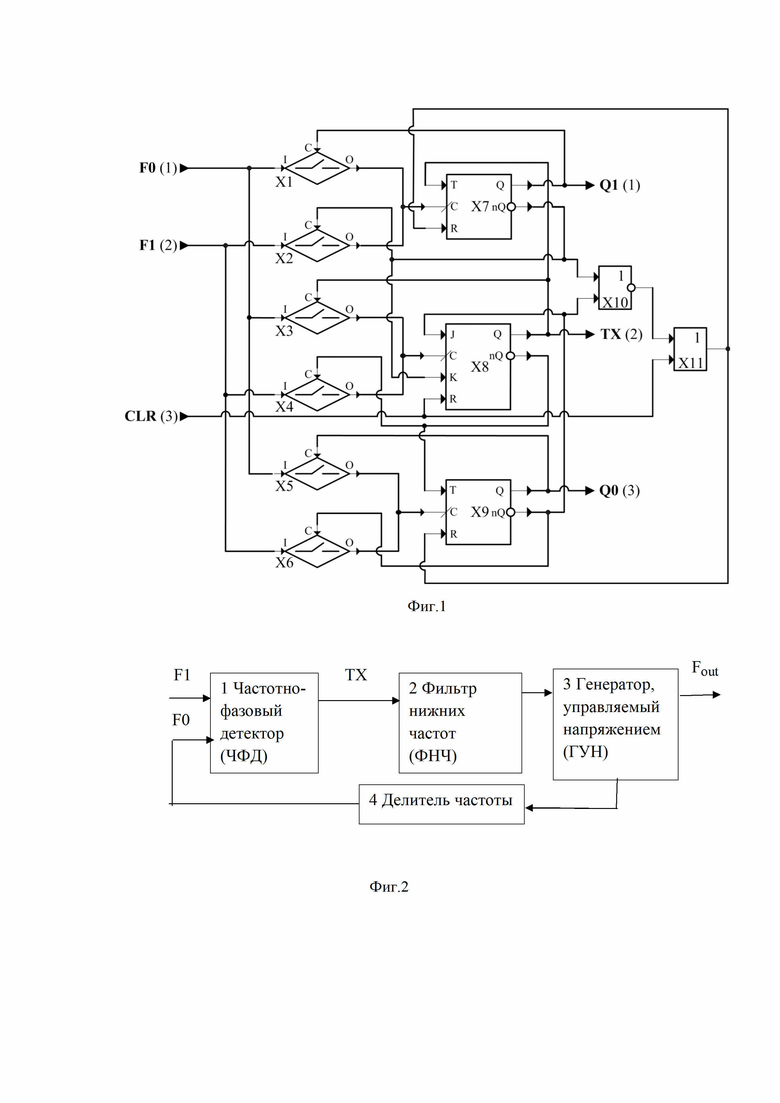

Фиг. 1 - Электрическая схема частотно-фазового детектора.

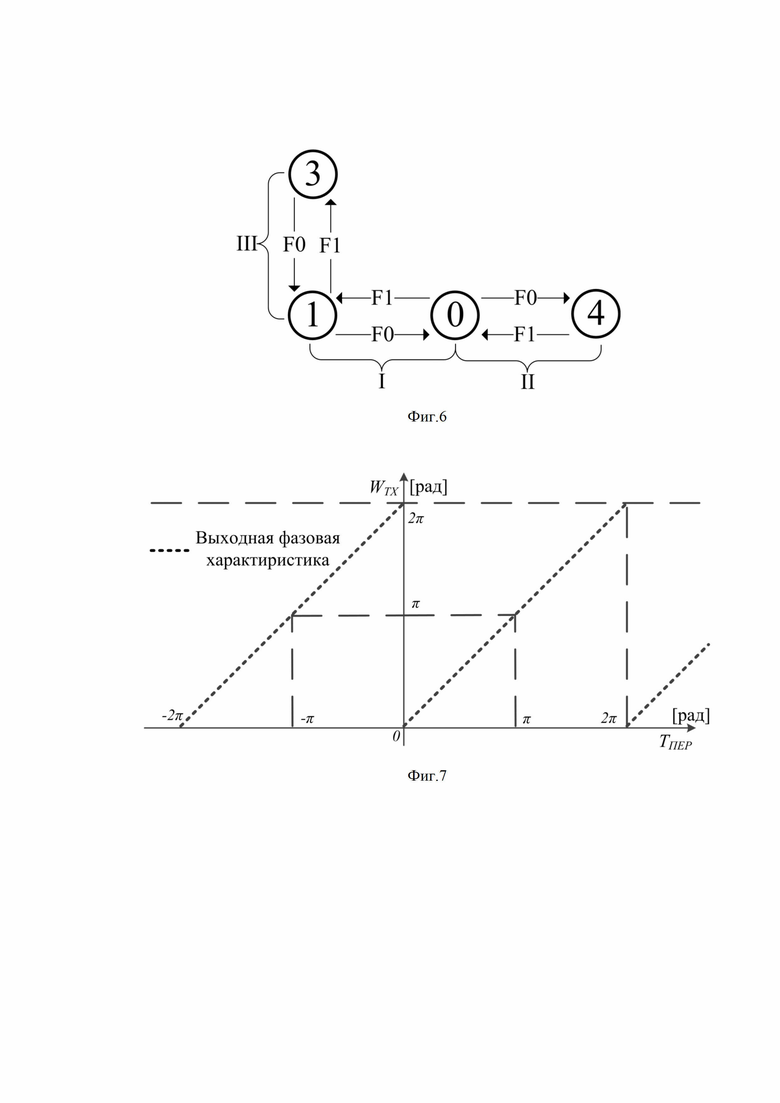

Фиг. 2 - Блок схема контура ФАПЧ.

Фиг. 3 - График работы частотно-фазового детектора.

Фиг. 4 - Таблица истинности заявляемого частотно-фазового детектора.

Фиг. 5 - Таблица состояний и режимов работы частотно-фазового детектора.

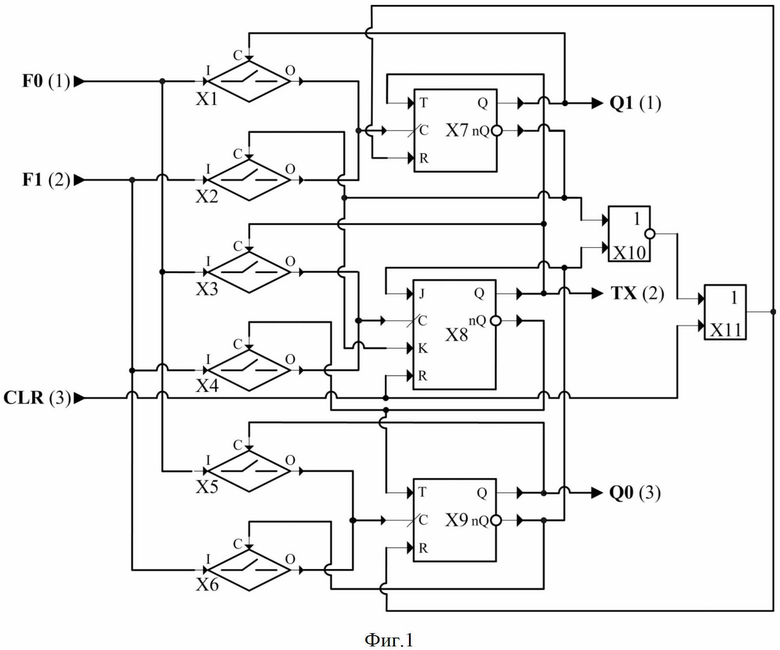

Фиг. 6 - Граф состояний частотно-фазового детектора.

Фиг. 7 - Выходная фазовая характеристика частотно-фазового детектора.

Частотно-фазовый детектор (ЧФД) - устройство импульсного типа, преобразующее фазовый сдвиг в длительность импульса. В основе схемотехнической реализации лежит использование синхронных динамических триггеров. Частотно-фазовый детектор, входит в состав контура фазовой автоподстройки частоты и состоит из: 6 КМОП ключей, на вход которых поступают сигналы сравниваемых фаз и частот F1 и F0; 2 Т-триггеров; JK-триггера, выходы которых соединены с КМОП ключами, образую при этом обратную связь.

Устройство содержит: X1, X2, X3, X4, X5, X6 - КМОП-ключи; X7, X9 - Т-триггера, X8 - JK-триггер, X10 - логический элемент 2ИЛИ-НЕ, X11 - логический элемент 2ИЛИ; F1, F0 - входы для опорного и детектируемого сигналов соответственно; CLR - вход для перевода схемы в начальное состояние (сброс схемы осуществляется логической «1»); TX - выходной сигнал разности фаз сигналов F1, F0; Q1 - выходной сигнал, формирующий логическую «1» при опережении частоты опорного сигнала F1 относительно детектируемого сигнала F0; Q0 - выходной сигнал, формирующий логическую «1» при опережение частоты детектируемого сигнала F0 относительного частоты опорного сигнала F1 (фиг. 1).

Фазовый детектор имеет три основных входа: F0, F1, CLR и три выхода: TX, Q0, Q1. Выбор индексов 0 и 1, при обозначении входов F0, F1 связан с логикой работы ЧФД. Передний фронт сигнала F1 устанавливает на выходе TX логическую «1», а передний фронт сигнала F0 устанавливает на выходе TX логический «0». Сигналы F1 и F0 имеют прямоугольную форму напряжений, для обеспечения работы ЧФД импульсного типа. ЧФД определяет временной интервал между передними фронтами импульсов F1 и F0 в режиме сравнения фаз входных сигналов.

Входы F1 и F0 являются выводами для опорного и детектируемого сигнала соответственно, вход CLR является выводом сброса, который переводит устройство в начальное состояние (TX=0, Q0=0, Q1=0). TX - выход, формирующий логическую «1» длительность которой равняется разности фаз F1 и F0. Q0 - выходной сигнал, формирующий логическую «1» если частота F0 > F1. Q1 - выходной сигнал, формирующий логическую «1» если частота F1 > F0.

В начальном состоянии после сброса схемы на выходах частотно-фазового детектора Q1, TX, Q0 сформирован логический «0». КМОП-ключи Х2, Х4, Х6 находятся в открытом состоянии, так как управляющие С-входы объединены с инверсными выходами триггеров Х7, Х8, Х9 и в начальном состоянии находятся в логической «1».

Устройство имеет два режима работы: режим детектирование частот входных сигналов F0, F1 и режим детектирование фаз входных сигналов F0, F1.

В режиме детектирования частот происходит отслеживание частоты детектируемого сигнала F0 относительно опорного сигнала F1. Если частота опорного сигнала F1 больше детектируемого сигнала F0, то на выходе Q1 и TX формируется логическая «1», а на выходе Q0 логический «0», если частота опорного сигнала F1 меньше частоты детектируемого сигнала F0, то на выходе Q0 формируется логическая «1», а на выходе Q1 и TX логический «0». Это происходит благодаря использованию счетных триггеров Х7, Х9 с асинхронным сбросом и с синхронизацией по переднему фронту, а также триггера JK-типа Х8 с асинхронным сбросом и записью по переднему фронту (Фиг. 1).

На фиг. 2 изображена блок схема контура ФАПЧ, где: F1,F0 - входы частотно-фазового детектора 1 (ЧФД), TX - выход; ФНЧ - фильтр нижних частот 2; ГУН - генератор, управляемый напряжением 3; FOUT - выходной сигнал контура ФАПЧ; делитель частоты 4.

Если в начальный момент времени частота опорного сигнала F1 превысить частоту детектируемого сигнала F0 в 2 и более раз, то на выходах Q1 и TX будет сформирована логическая «1» - ЧФД 1 находится в режиме детектирования фаз. Сравнение фаз произойдет только после детектирования двух передних фронтов сигнала F0. Первый передний фронт сигнала F0, сформирует на выходе Q1 логический «0», второй передний фронт сигнала F0 сформирует на выходе TX логический «0», что приведет к режиму детектирования фаз входных сигналов F0 и F1.

Если в начальный момент времени частота детектируемого сигнала F0 превысит частоту детектируемого сигнала в 2 и более раз, то на выходе ТХ и Q1 будет логический «0», а на выходе Q0 логическая «1» - ЧФД 1 находится в режиме детектирования частот. Для перехода в режим сравнения фаз необходимо детектирование двух передних фронтов сигнала F1. Первый фронт сигнала F1 сформирует на выходе Q0 логический «0», второй фронт сигнала F1 сформирует выходе TX логическую «1», что приведет к режиму детектирования фаз входных сигналов F0 и F1.

В режиме детектирования частоты частотно-фазовый детектор 1 работает по принципу реверсивного счетчика на основе кода Грея. Схема детектирует только передние фронты входных сигналов F0, F1. Одновременное детектирование передних фронтов сигналов F1 и F0 исключено, так как F0 - сигнал обратной связи контура фазовой автоподстройки частоты, а F1 сигнал опорный частоты.

На фиг. 3 приведен график работы частотно-фазового детектора, где F1,F0 - входные сигналы, TX, Q0, Q1 - выходные сигналы частотно-фазового детектора. Стрелками на диаграмме отмечена зависимость переключения выходных сигналов, от детектирования передних фронтов входных сигналов F0, F1.

В режиме детектирования фаз, частоты входных сигналов F1, F0 равны между собой. Схема ЧФД формирует на выходе ТX дискретные импульсы прямоугольной формы с частотой сигнала F1, длительность которых равна фазовому сдвигу между передними фронтами сигналов F1 и F0. При этом выходы Q0 и Q1 равны логическому «0». Выходная характеристика ЧФД в режиме сравнения фаз имеет периодический характер и обеспечивает детектирование фаз сигналов F1 и F0 в диапазоне от 0 до 2π (Фиг. 7). Фиг. 7 выходная фазовая характеристика частотно-фазового детектора, где пунктирной линией изображена выходная фазовая характеристика заявляемого детектора в режиме сравнения фаз; WTX - ширина импульса логической «1» выходного сигнала TX.

Режимы работы устройства представлены в таблице на Фиг. 4, 5. На фиг. 6 в форме направленного графа представлен алгоритм работы частотно-фазового детектора в зависимости от детектирования передних фронтов входных сигналов F1, F0 .

Фиг. 4 - таблица истинности заявляемого частотно-фазового детектора, где F1, F0 - входные сигналы детектора; TX - выходной сигнал разницы фаз сигналов F1, F0; Q1 - выходной сигнал детектирующий опережение частоты сигнала F1 в 2 и более раз; Q0 - выходной сигнал детектирующий опережение частоты сигнала F0 в 2 и более раз.

Фиг. 5 - таблица состояний и режимов работы частотно-фазового детектора, где BIN [Q0, Q1, TX] объединенная шина в двоичном коде; DEC [Q0, Q1, TX] объединенная шина в десятичном коде, использованная в основаниях графа состояний частотно-фазового детектора (Фиг. 6);

Фиг. 6 - граф состояний частотно-фазового детектора, где: 0 - начальное состояние схемы; 1 - детектирование первого переднего фронта сигнала F1 (I - режим детектирования фаз, при последующем сигнале переднего фронта F0); 3 - формирование логической «1» на выходе Q1 после повторного детектирования переднего фронта сигнала F1 (III - режим частотного детектирование - опережение частоты сигнала F1 относительно частоты F0); 4 - переход в состояние логической «1» выходного сигнала Q0 при детектировании переднего фронта сигнала F0 в исходном состоянии частотно-фазового детектора (II - режим частотного детектирования - опережение частоты сигнала F0 относительно опорного сигнала F1).

Применение предлагаемой схемотехнической реализации устройств а позволяет сравнивать фазы входных сигналов, только в случае если их частоты равны между собой. В случае опережения входного сигнала от опорного или отставания, фазовый детектор формирует логическую единицу на соответствующем выходе Q0, Q1.

Предлагаемое устройство может использоваться в качестве частотно-фазового детектора, которое может применяться как в составе контура ФАПЧ, так и отдельно, представляя собой пороговое устройство (компаратор) контроля разности фаз и частот входных сигналов F1, F0.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РЕЗОНАТОРА ТВЕРДОТЕЛЬНОГО ВОЛНОВОГО ГИРОСКОПА ЛУЧОМ ЛАЗЕРА | 1993 |

|

RU2079107C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2296420C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Способ определения разности фаз электрических сигналов и устройство для его осуществления | 1989 |

|

SU1688188A1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Цифровой частотный детектор | 1984 |

|

SU1307534A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

Изобретение относится к цифровой электронике и может использоваться в системах фазовой автоподстройки частоты (ФАПЧ). Технический результат заключается в исключении возможности «захвата» когерентных и кратных частот опорного сигнала, что позволит избежать рисков сбоя в режиме частотного детектирования, увеличении стабильности работы системы контура ФАПЧ, повышении надежности, снижении энергопотребления. Детектор содержит шесть КМОП-ключей, два Т-триггера, JK-триггер, логический элемент 2ИЛИ-НЕ и логический элемент 2ИЛИ; причем первый вход устройства соединен с объединенными входами первого, третьего и пятого КМОП-ключей; второй вход устройства соединен с объединенными входами второго, четвертого и шестого КМОП ключей; С-вход первого Т-триггера соединен с объединенными выходами первого и второго КМОП-ключей; С-вход JK-триггера соединен с объединенными выходами третьего и четвертого КМОП-ключей; С-вход второго Т-триггера соединен с объединенными выходами пятого и шестого КМОП-ключей; второй выход устройства соединен с объединенными Т-входом первого Т-триггера, Q-выходом JK-триггера и С-входом третьего КМОП-ключа; второй вход логического элемента 2ИЛИ-НЕ соединен с объединенными J-входом JK-триггера, nQ-выходом второго Т-триггера и С-входом шестого КМОП-ключа; первый вход логического элемента 2ИЛИ-НЕ соединен с объединенными K-входом JK-триггера, nQ-выходом первого Т-триггера и С-входом второго КМОП-ключа; С-вход четвертого КМОП-ключа соединен с объединенными Т-входом второго Т-триггера, nQ-выходом JK-триггера; первый выход устройства соединен с объединенными Q-выходом первого T-триггера и С-входом первого КМОП-ключа; третий выход устройства соединен с объединенными Q-выходом второго триггера и С-входом пятого КМОП-ключа; первый вход логического элемента 2ИЛИ соединен с выходом логического элемента 2ИЛИ-НЕ; третий вход устройства соединен с объединенными вторым входом логического элемента 2ИЛИ и R-входом JK-триггера. 7 ил.

Частотно-фазовый детектор, содержащий шесть КМОП-ключей, два Т-триггера, JK-триггер, логический элемент 2ИЛИ-НЕ и логический элемент 2ИЛИ; причем первый вход устройства соединен с объединенными входами первого, третьего и пятого КМОП-ключей; второй вход устройства соединен с объединенными входами второго, четвертого и шестого КМОП ключей; С-вход первого Т-триггера соединен с объединенными выходами первого и второго КМОП-ключей; С-вход JK-триггера соединен с объединенными выходами третьего и четвертого КМОП-ключей; С-вход второго Т-триггера соединен с объединенными выходами пятого и шестого КМОП-ключей; второй выход устройства соединен с объединенными Т-входом первого Т-триггера, Q-выходом JK-триггера и С-входом третьего КМОП-ключа; второй вход логического элемента 2ИЛИ-НЕ соединен с объединенными J-входом JK-триггера, nQ-выходом второго Т-триггера и С-входом шестого КМОП-ключа; первый вход логического элемента 2ИЛИ-НЕ соединен с объединенными K-входом JK-триггера, nQ-выходом первого Т-триггера и С-входом второго КМОП-ключа; С-вход четвертого КМОП-ключа соединен с объединенными Т-входом второго Т-триггера, nQ-выходом JK-триггера; первый выход устройства соединен с объединенными Q-выходом первого T-триггера и С-входом первого КМОП-ключа; третий выход устройства соединен с объединенными Q-выходом второго триггера и С-входом пятого КМОП-ключа; первый вход логического элемента 2ИЛИ соединен с выходом логического элемента 2ИЛИ-НЕ; третий вход устройства соединен с объединенными вторым входом логического элемента 2ИЛИ и R-входом JK-триггера.

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2483434C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2013 |

|

RU2530248C1 |

| JPH 10276044 A, 13.10.1998 | |||

| JPH 10336024 A, 18.12.1998 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2020-05-19—Публикация

2019-02-25—Подача