Изобретение относится к радиоизмерительной технике и может использоваться для определения частоты сигналов при наличии помех.

Целью изобретения является уменьшение времени измерения частоты.

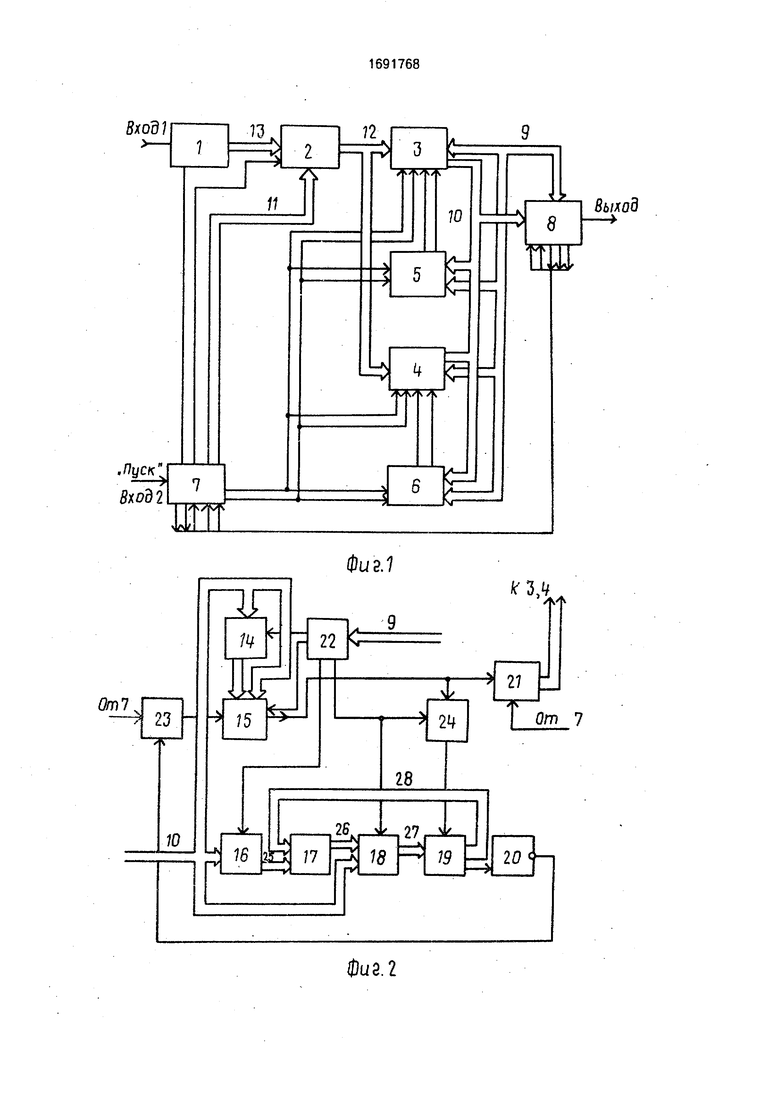

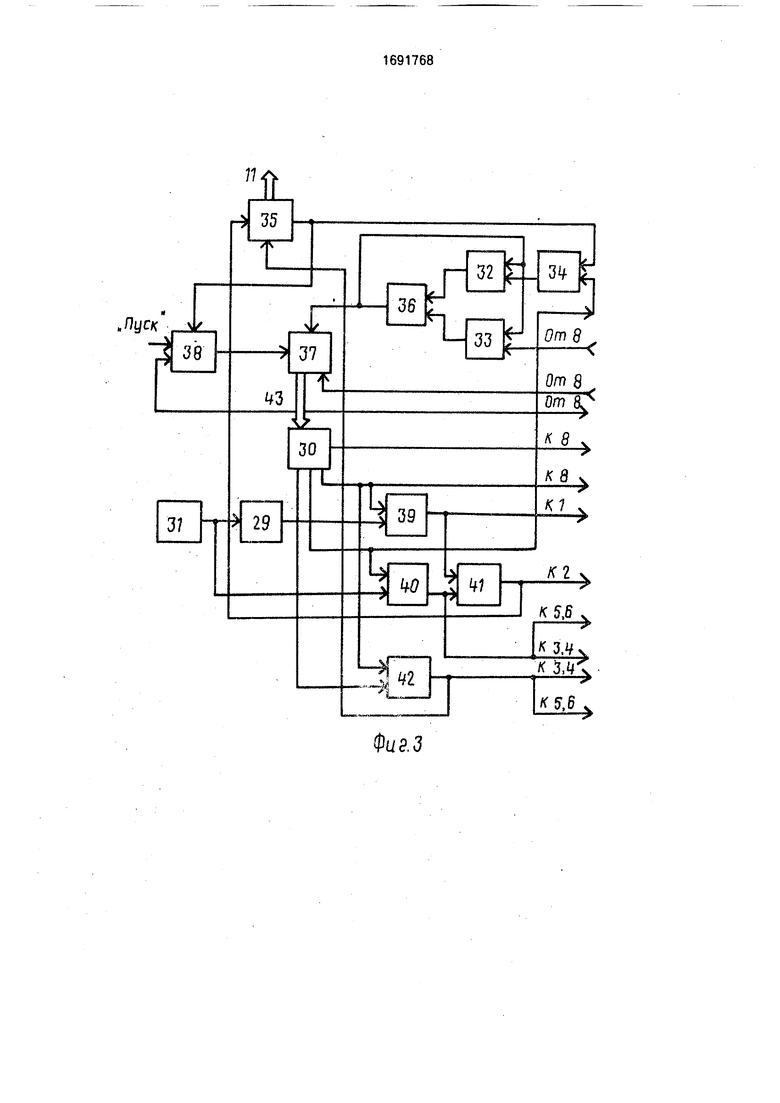

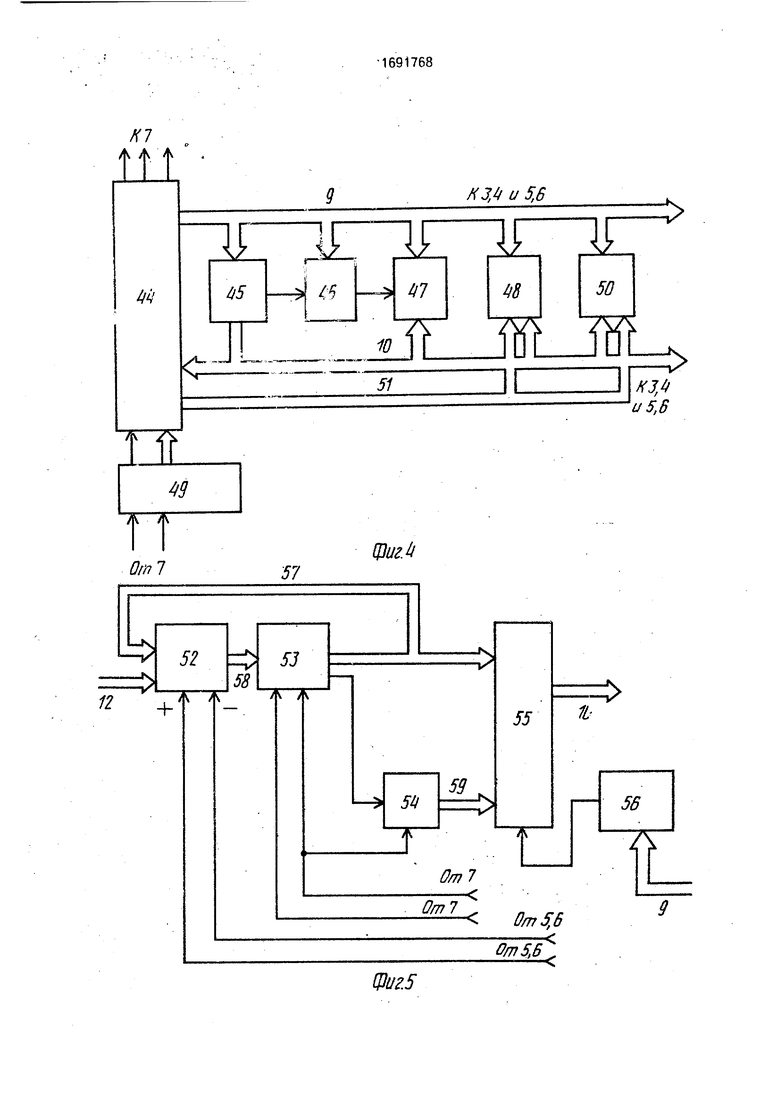

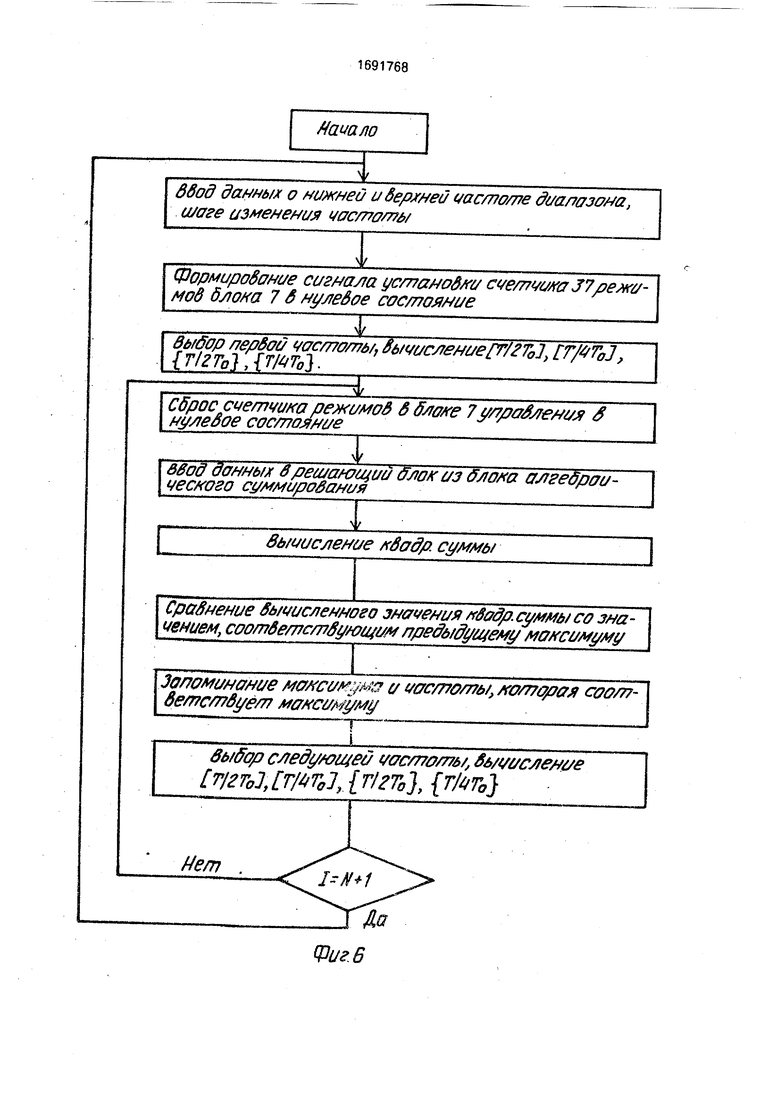

На фиг.1 приведена структурная схема измерителя частоты; на фиг.2-5 - структурные схемы входящих в измеритель блоков; на фиг.б - алгоритм работы измерителя; на фиг.7 - вид частотной характеристики.

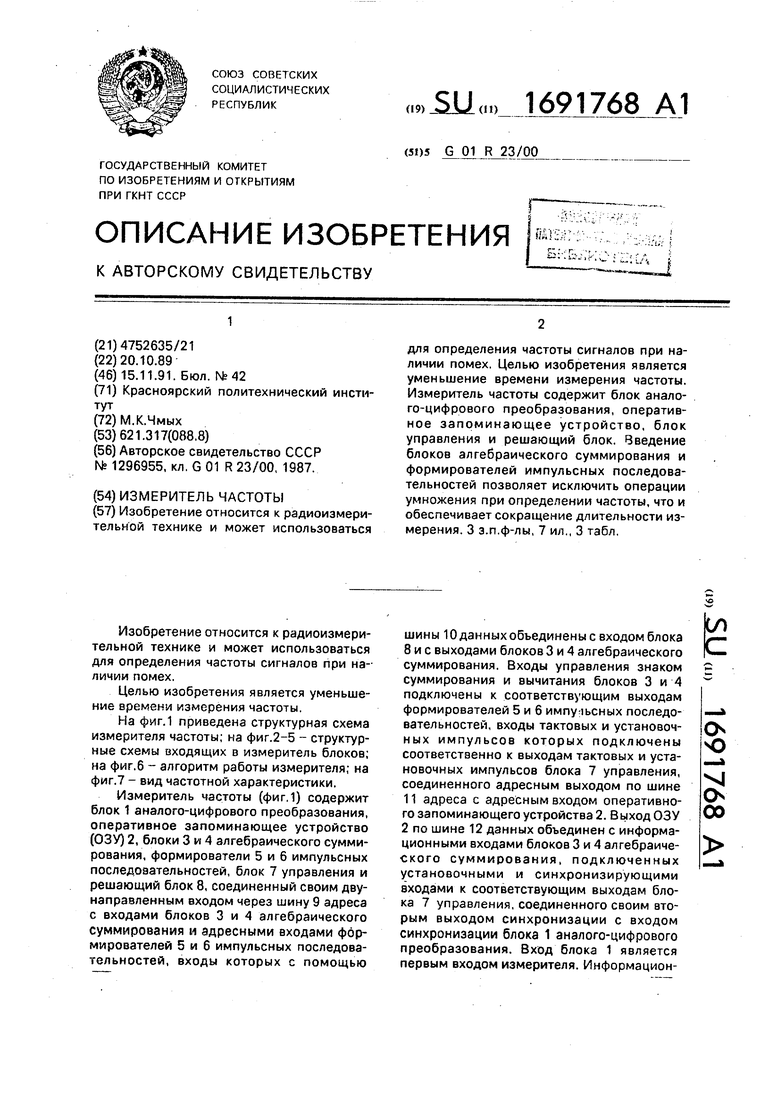

Измеритель частоты (фиг.1) содержит блок 1 аналого-цифрового преобразования, оперативное запоминающее устройство (ОЗУ) 2, блоки 3 и 4 алгебраического суммирования, формирователи 5 и 6 импульсных последовательностей, блок 7 управления и решающий блок 8, соединенный своим двунаправленным входом через шину 9 адреса с входами блоков 3 и 4 алгебраического суммирования и адресными входами формирователей 5 и 6 импульсных последовательностей, входы которых с помощью

шины Юданныхобьединены с входом блока Вис выходами блоков 3 и 4 алгебраического суммирования. Входы управления знаком суммирования и вычитания блоков 3 и 4 подключены к соответствующим выходам формирователей 5 и 6 импульсных последовательностей, входы тактовых и установочных импульсов которых подключены соответственно к выходам тактовых и установочных импульсов блока 7 управления, соединенного адресным выходом по шине 11 адреса с адресным входом оперативного запоминающего устройства 2. Выход ОЗУ 2 по шине 12 данных объединен с информационными входами блоков 3 и 4 алгебраического суммирования, подключенных установочными и синхронизирующими входами к соответствующим выходам блока 7 управления, соединенного своим вторым выходом синхронизации с входом синхронизации блока 1 аналого-цифрового преобразования. Вход блока 1 является первым входом измерителя. Информациейсо

с

о ю

VJ сь

00

ный вход ОЗУ 2 соединен по шине 13 данных с выходом блока 1 аналого-цифрового преобразования. Выходы и входы управляющих сигналов решающего блока 8 подсоединены к соответствующим входам и выходам блока 7 управления, вход Пуск которого является вторым входом измерителя.

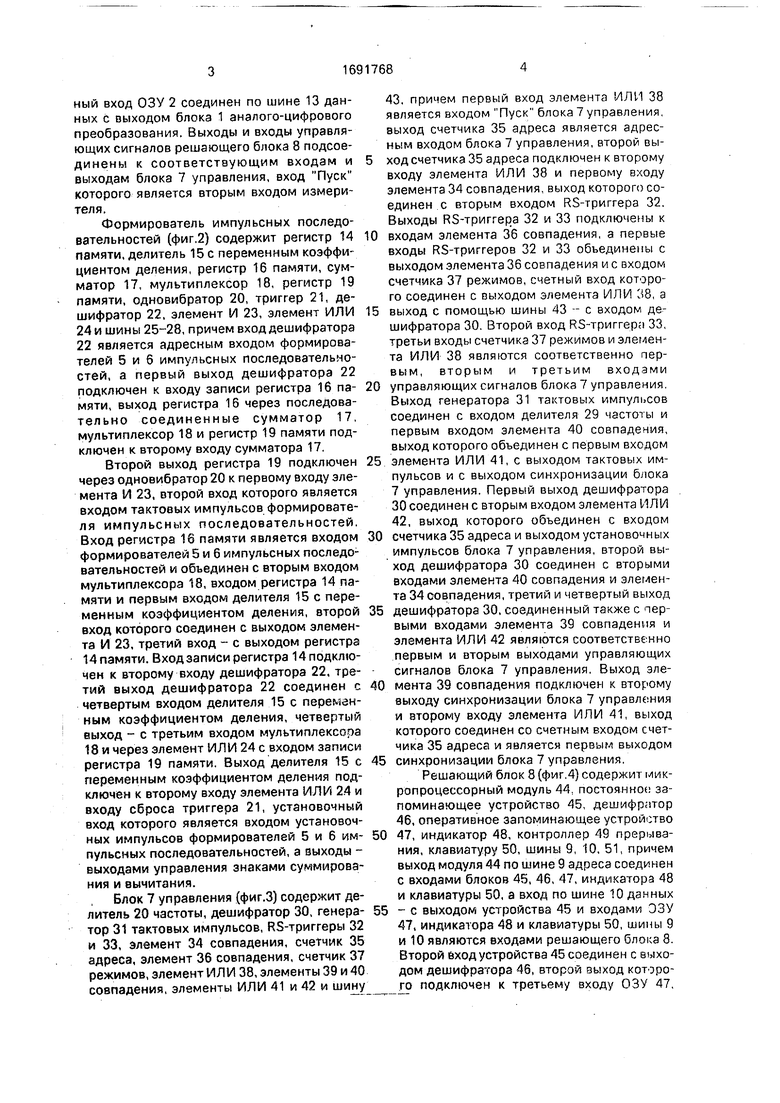

Формирователь импульсных последовательностей (фиг.2) содержит регистр 14 памяти, делитель 15с переменным коэффициентом деления, регистр 16 памяти, сумматор 17, мультиплексор 18, регистр 19 памяти, одновибратор 20, триггер 21, дешифратор 22, элемент И 23, элемент ИЛИ 24 и шины 25-28, причем вход дешифратора 22 является адресным входом формирователей 5 и б импульсных последовательностей, а первый выход дешифратора 22 подключен к входу записи регистра 16 памяти, выход регистра 16 через последовательно соединенные сумматор 17, мультиплексор 18 и регистр 19 памяти подключен к второму входу сумматора 17.

Второй выход регистра 19 подключен через одновибратор 20 к первому входу элемента И 23, второй вход которого является входом тактовых импульсов формирователя импульсных последовательностей. Вход регистра 16 памяти является входом формирователей 5 и 6 импульсных последовательностей и объединен с вторым входом мультиплексора 18, входом регистра 14 памяти и первым входом делителя 15 с переменным коэффициентом деления, второй вход которого соединен с выходом элемента И 23, третий вход - с выходом регистра Нпамяти. Вход записи регистра Нподклю- чен к второму входу дешифратора 22, третий выход дешифратора 22 соединен с четвертым входом делителя 15 с переменным коэффициентом деления, четвертый выход - с третьим входом мультиплексора 18 и через элемент ИЛИ 24 с входом записи регистра 19 памяти. Выход делителя 15 с переменным коэффициентом деления подключен к второму входу элемента ИЛИ 24 и входу сброса триггера 21, установочный вход которого является входом установочных импульсов формирователей 5 и 6 импульсных последовательностей, а выходы - выходами управления знаками суммирования и вычитания.

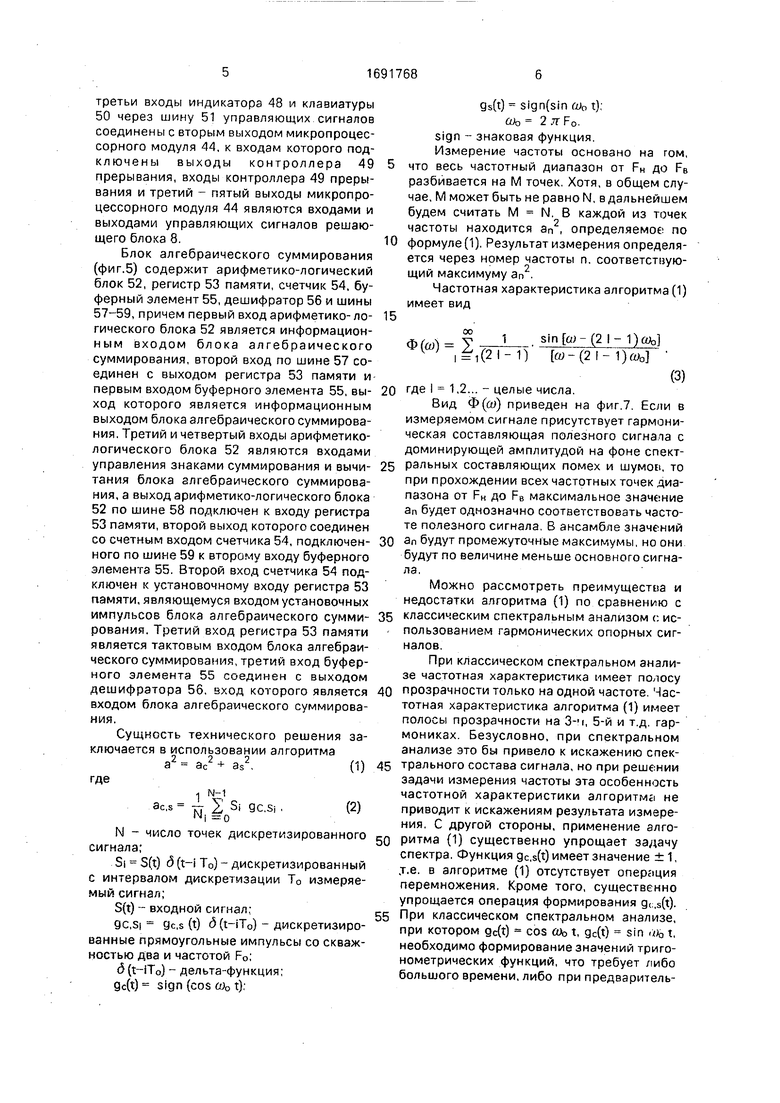

Блок 7 управления (фиг.З) содержит делитель 20 частоты, дешифратор 30, генератор 31 тактовых импульсов, RS-триггеры 32 и 33, элемент 34 совпадения, счетчик 35 адреса, элемент 36 совпадения, счетчик 37 режимов, элемент ИЛИ 38, элементы 39 и 40 совпадения, элементы ИЛИ 41 и 42 и шину

43, причем первый вход элемента ИЛИ 38 является входом Пуск блока 7 управления, выход счетчика 35 адреса является адресным входом блока 7 управления, второй выход счетчика 35 адреса подключен к второму входу элемента ИЛИ 38 и первому входу элемента 34 совпадения, выход которого соединен с вторым входом RS-триггера 32. Выходы RS-триггера 32 и 33 подключены к

0 входам элемента 36 совпадения, а первые входы RS-триггеров 32 и 33 объединены с выходом элемента 36 совпадения и с входом счетчика 37 режимов, счетный вход которого соединен с выходом элемента ИЛИ 38, а

5 выход с помощью шины 43 - с входом дешифратора 30. Второй вход RS-триггерп 33, третьи входы счетчика 37 режимов и элемента ИЛИ 38 являются соответственно первым, вторым и третьим входами

0 управляющих сигналов блока 7 управления. Выход генератора 31 тактовых импульсов соединен с входом делителя 29 частоты и первым входом элемента 40 совпадения, выход которого объединен с первым входом

5 элемента ИЛИ 41, с выходом тактовых импульсов и с выходом синхронизации блока 7 управления. Первый выход дешифратора 30 соединен с вторым входом элемента ИЛИ 42, выход которого объединен с входом

0 счетчика 35 адреса и выходом установочных импульсов блока 7 управления, второй выход дешифратора 30 соединен с вторыми входами элемента 40 совпадения и элемента 34 совпадения, третий и четвертый выход

5 дешифратора 30, соединенный также с первыми входами элемента 39 совпадения и элемента ИЛИ 42 являются соответственно первым и вторым выходами управляющих сигналов блока 7 управления. Выход эле0 мента 39 совпадения подключен к второму выходу синхронизации блока 7 управления и второму входу элемента ИЛИ 41, выход которого соединен со счетным входом счетчика 35 адреса и является первым выходом

5 синхронизации блока 7 управления.

Решающий блок 8 (фиг.4) содержит микропроцессорный модуль 44 постоянное запоминающее устройство 45, дешифратор

46,оперативное запоминающее устройство 0 47, индикатор 48, контроллер 49 прерывания, клавиатуру 50, шины 9, 10, 51, причем выход модуля 44 по шине 9 адреса соединен с входами блоков 45, 46, 47, индикатора 48 и клавиатуры 50, а вход по шине 10 данных

5 - с выходом устройства 45 и входами ОЗУ

47,индикатора 48 и клавиатуры 50, шины 9 и 10 являются входами решающего блока 8. Второй вход устройства 45 соединен с выходом дешифратора 46, второй выход которого подключен к третьему входу ОЗУ 47,

третьи входы индикатора 48 и клавиатуры 50 через шину 51 управляющих сигналов соединены с вторым выходом микропроцессорного модуля 44, к входам которого подключены выходы контроллера 49 прерывания, входы контроллера 49 прерывания и третий - пятый выходы микропроцессорного модуля 44 являются входами и выходами управляющих сигналов решающего блока 8.

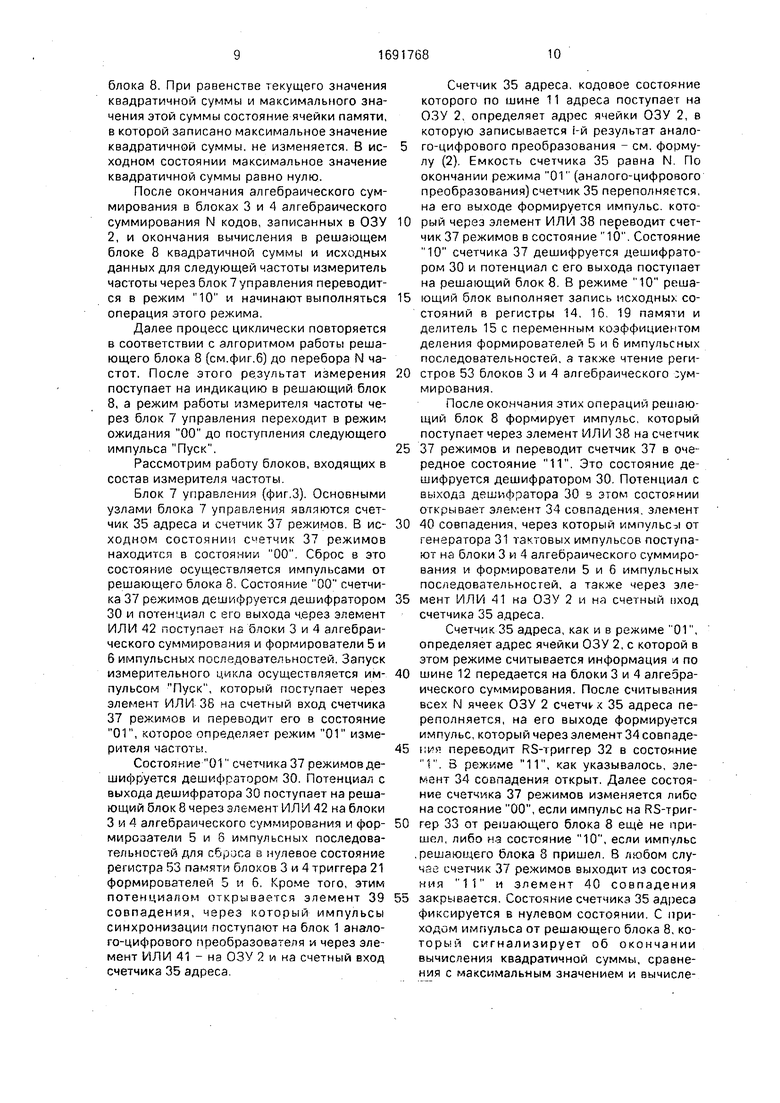

Блок алгебраического суммирования (фиг.5) содержит арифметико-логический блок 52, регистр 53 памяти, счетчик 54, буферный элемент 55, дешифратор 56 и шины 57-59, причем первый вход арифметико-логического блока 52 является информационным входом блока алгебраического суммирования, второй вход по шине 57 соединен с выходом регистра 53 памяти и первым входом буферного элемента 55, выход которого является информационным выходом блока алгебраического суммирования. Третий и четвертый входы арифметико- логического блока 52 являются входами управления знаками суммирования и вычитания блока алгебраического суммирования, а выход арифметико-логического блока

52по шине 58 подключен к входу регистра

53памяти, второй выход которого соединен со счетным входом счетчика 54, подключенного по шине 59 к второму входу буферного элемента 55. Второй вход счетчика 54 подключен к установочному входу регистра 53 памяти, являющемуся входом установочных импульсов блока алгебраического суммирования. Третий вход регистра 53 памяти является тактовым входом блока алгебраического суммирования, третий вход буферного элемента 55 соединен с выходом дешифратора 56, вход которого является входом блока алгебраического суммирования.

Сущность технического решения заключается в использовании алгоритма

а2 ас2 + as2,(1)

где

1 N-1

а« ТГ 2 Si 9C.S, ,(2)

N| 0

N - число точек дискретизированного сигнала;

Si S(t) д (t-i TO) - дискретизированный с интервалом дискретизации Т0 измеряемый сигнал;

S(t) - входной сигнал;

9c,Si Qc.s (t) б (t-iTo) - дискретизиро- ванные прямоугольные импульсы со скважностью два и частотой F0;

5 (t-iTo) - дельта-функция;

9c(t) sign (cos Wo t)

9s(t) sign(sin (DO t)

WQ 2 Л Fo

sign - знаковая функция.

Измерение частоты основано на гом, что весь частотный диапазон от FH до FB разбивается на М точек. Хотя, в общем случае, М может быть не равно N, в дальнейшем будем считать М N. В каждой из точек частоты находится ап , определяемое по формуле (1). Результат измерения определяется через номер частоты п. соответствующий максимуму an .

Частотная характеристика алгоритма (1) имеет вид

00

1

ФГлЛ Т (2-1)Qbl (а) ,Ј,(21-1) ю-(21-1)од,

(3)

0 где I 1,2... - целые числа.

Вид Ф(й) приведен на фиг.7. Если в измеряемом сигнале присутствует гармоническая составляющая полезного сигнапа с доминирующей амплитудой на фоне спект5 ральных составляющих помех и шумов, то при прохождении всех частотных точек диапазона от FH до FB максимальное значение ап будет однозначно соответствовать частоте полезного сигнала. В ансамбле значений

0 Зп будут промежуточные максимумы, но они будут по величине меньше основного сигнала.

Можно рассмотреть преимущества и недостатки алгоритма (1) по сравнению с

5 классическим спектральным анализом с использованием гармонических опорных сигналов.

При классическом спектральном анализе частотная характеристика имеет полосу

0 прозрачности только на одной частоте. Частотная характеристика алгоритма (1) имеет полосы прозрачности на З- i, 5-й и т.д. гармониках. Безусловно, при спектральном анализе это бы привело к искажению спек5 трального состава сигнала, но при решении задачи измерения частоты эта особенность частотной характеристики алгоритма не приводит к искажениям результата измерения. С другой стороны, применение алго0 ритма (1) существенно упрощает задачу спектра. Функция gc,s(t) имеет значение ± 1, .т.е. в алгоритме (1) отсутствует операция перемножения. Кроме того, существенно упрощается операция формирования g(|S(t).

5 При классическом спектральном анализе, при котором gc(t) cos C0o t, gc(t) sin n)o t, необходимо формирование значений тригонометрических функций, что требует либо большого времени, либо при предварит ельном формировании требует памяти большой емкости.

Измеритель частоты работает следующим образом,

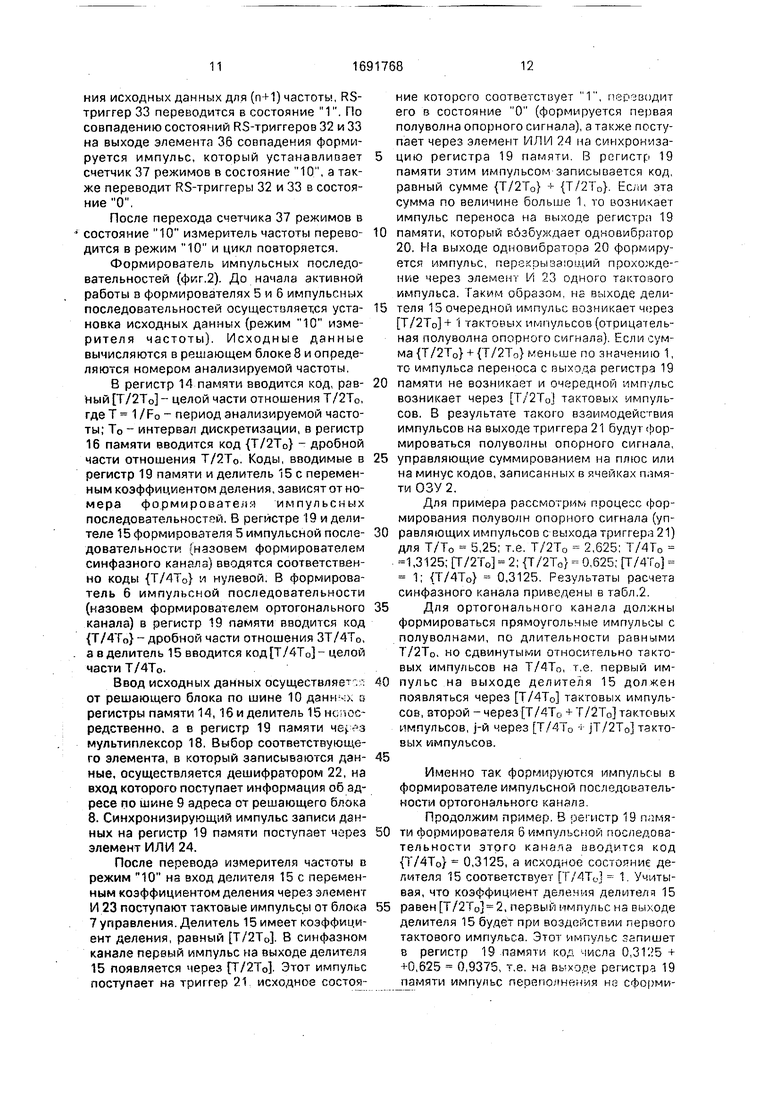

В процессе работы измеритель может находиться в нескольких режимах, определяемых состоянием счетчика 37 режимов блока 7 управления. Режимы измерителя показаны в табл.1. Для простоты будем обозначать эти режимы по двоичному состоянию счетчика 37 режимов: состояния ОО11. 01, 10, 11,

Исходное состояние 00. В этом случае измеритель частоты находится в состоянии ожидания. По приходу импульса Пуск на блок 7 управления измеритель частоты переводится в режим 01. В этом режиме блок аналого-цифрового преобразования осуществляет преобразование входного сигнала с интервалом дискретизации Т0. Интервал дискретизации выбирается исходя из верхней частоты FB частотного диапазона измеряемого сигнала. Результат аналого-цифрового преобразования из блока 1 по шине 13 подается в ОЗУ 2 и запоминается в его ячейках, адрес которых задается по шине 11 блоком 7 управления. В блоке 7 управления также формируются импульсы синхронизации ОЗУ 2.

В ОЗУ 2 накапливается N точек измеряемого сигнала. Число точек N выбирается исходя из разрешающей способности, связанной с погрешностью измерения частоты. Общее время дискретизации сигнала (время накопления) равно:

Тн - МТо.(4)

Разрешающая способность Afp связана с временем накопления соотношением AfP«1/TH.(5)

Отсюда можно получить ориентировочное значение N:

N TH/To 1/Afp -To.(6)

Интервал дискретизации связан с вахней частотой измеряемого частотного диапазона соотношением

To 1/2FB.(7)

После записи в ОЗУ 2 N дискретизиро- ванных точек сигнала процесс накопления заканчивается, Далее начинается процесс обработки полученной информации, Обработка сигнала, основанная на алгоритме (1) происходит в блоках 3 и. 4 алгебраического суммирования. Термин алгебраическое суммирование обусловлен тем, что сумми- рование в этом блоке осуществляется со знаком плюс или минус.

Знак при суммировании в блоке 3, 4 определяется управляющими сигналами,

поступающими от блоков 5 и 6 - Формирователей импульсных последовательностей. Прежде чем начнется процесс алгебраического суммирования, блоком 7 упрэвления формируется режим 10, в котором осуществляется предварительная установка начальных состояний регионов памяти 14, 16, 19 и делителя 15 с переменным коэффициентом деления формирователей 5 и 6.

0Коды начальных состояний вычисляются в решающем блоке 8, причем коды для первой частоты вычисляются заранее и течение времени, пока осуществляется аналого-цифровое преобразование сигнала. В

5 этом же режиме осуществляется сброс и нулевое состояние регистров 53 памяти блоков 3, 4 алгебраического суммирования и триггеров 21 формирователей 5, 6 импульсных последовательностей. Кроме того, в

0 этом режиме осуществляется ч гение регистров 53 памяти блоков 3 и 4 алгебраичес ого суммирования (запись информации из регистров 53 памяти блоков 3 и 4 алгебраического суммирования в ОЗУ 47 решающего

5 блока 8).

После выполнения указанных операций сигналом с решающего блока 8 измеритель частоты через блок 7 управления переводят в режим 11, в котором формирователи 5 и

0 6 импульсных последовательностей начинают формировать импульсы управления знаком суммирования и вычитания в блоках 3 и 4 алгебраического суммирования.

Синхронизирующие импульсы на блоки

5 3 и 4 алгебраического суммирования и формирователи 5 и 6 импульсных последовательностей формируются в блоке 7 управления. Одновременно с тактом суммирования в блоках 3 и 4 происходит измэне0 ние адреса ОЗУ 2.

В этом же режиме 11 в течение времени, пока в блоках 3 и 4 алгебраического суммирования выполняются операции суммирования, в решающем блоке 8 вы5 полняются операции квадратичного суммирования кодов результатов предыдущей операции алгебраического суммирования, а также вычисление исходных данных для следующей частоты. На первом такте

0 вычисление квадратичной суммы осуществляется формально, так как предыдущее- состояние регистров 53 памяти блоков 3 и 4 алгебраического суммирования равно нулю. Но для формализации выполнения режимов

5 такая операция целесообразна В этом же режиме 11 осуществляется сравнение полученного значения квадратичной суммы с максимальным значением этой суммы. Максимальное значение этой суммы хранится в одной из ячеек РЗУ 47 решающего

блока 8. При равенстве текущего значения квадратичной суммы и максимального значения этой суммы состояние ячейки памяти, в которой записано максимальное значение квадратичной суммы, не изменяется. В исходном состоянии максимальное значение квадратичной суммы равно нулю.

После окончания алгебраического суммирования в блоках 3 и 4 алгебраического суммирования N кодов, записанных в ОЗУ 2, и окончания вычисления в решающем блоке 8 квадратичной суммы и исходных данных для следующей частоты измеритель частоты через блок 7 управления переводится в режим 10 и начинают выполняться операция этого режима.

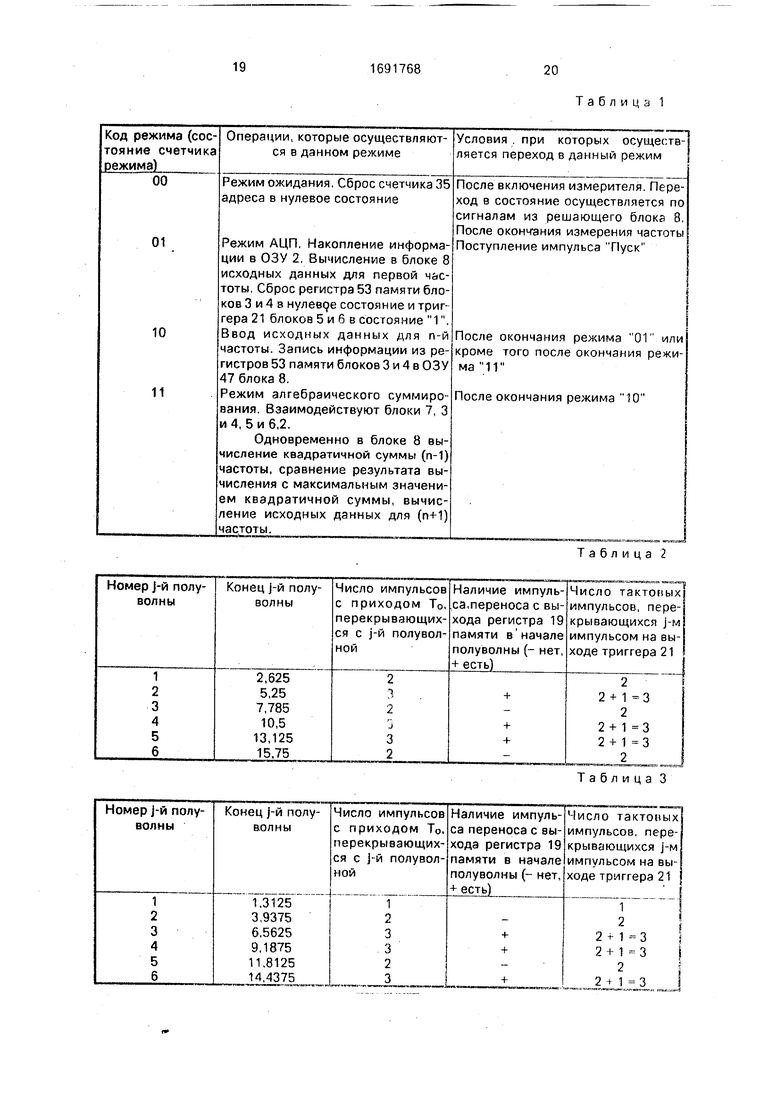

Далее процесс циклически повторяется в соответствии с алгоритмом работы решающего блока 8 (см.фиг.6) до перебора N частот. После этого результат измерения поступает на индикацию в решающий блок 8, а режим работы измерителя частоты через блок 7 управления переходит в режим ожидания 00 до поступления следующего импульса Пуск.

Рассмотрим работу блоков, входящих в состав измерителя частоты.

Блок 7 управления (фиг.З). Основными узлами блока 7 управления являются счетчик 35 адреса и счетчик 37 режимов. В исходном состоянии сиетчик 37 режимов находится в состоянии 00. Сброс в это состояние осуществляется импульсами от решающего блока 8. Состояние 00 счетчика 37 режимов дешифруется дешифратором 30 и потенциал с его выхода ч.ерез элемент ИЛИ 42 поступает на блоки 3 и 4 алгебраического суммирования и формирователи 5 и 6 импульсных последовательностей. Запуск измерительного цикла осуществляется импульсом Пуск, который поступает через элемент ИЛИ 38 на счетный вход счетчика 37 режимов и переводит его в состояние 01, которое определяет режим 01 измерителя частоты.

Состояние 01 счетчика 37 режимов дешифруется дешифратором 30. Потенциал с выхода дешифратора 30 поступает на решающий блок 8 через элемент ИЛИ 42 на блоки 3 и 4 алгебраического суммирования и фор- мирозатели 5 и 8 импульсных последовательностей для сброса в нулевое состояние регистра 53 памяти блоков 3 и 4 триггера 21 формирователей 5 и 6. Кроме того, этим потенциалом открывается элемент 39 совпадения, через который импульсы синхронизации поступают на блок 1 аналого-цифрового преобразователя и через элемент ИЛИ 41 - на ОЗУ 2 и на счетный вход счетчика 35 адреса.

Счетчик 35 адреса, кодовое состояние которого по шине 11 адреса поступает на ОЗУ 2, определяет адрес ячейки ОЗУ 2, в которую записывается i-й результат анало- го-цифрового преобразования - см. формулу (2). Емкость счетчика 35 равна N. По окончании режима 01 (аналого-цифрового преобразования) счетчик 35 переполняется, на его выходе формируется импульс, кото0 рый через элемент ИЛИ 38 переводит счетчик 37 режимов в состояние 10. Состояние 10 счетчика 37 дешифруется дешифратором 30 и потенциал с его выхода поступает на решающий блок 8. В режиме 10 реша5 ющий блок выполняет запись исходных состояний в регистры 14, 16. 19 памяти и делитель 15 с переменным коэффициентом деления формирователей 5 и 6 импульсных последовательностей, а также чтение реги0 стров 53 блоков 3 и 4 алгебраического суммирования.

После окончания этих операций решающий блок 8 формирует импульс, который поступает через элемент ИЛИ 38 на счегчик

5 37 режимов и переводит счетчик 37 в очередное состояние 11. Это состояние дешифруется дешифратором 30. Потенциал с выхода дешифратора 30 з этом состоянии открывает элемент 34 совпадения, элемент

0 40 совпадения, через который импульса от генератора 31 тактовых импульсов поступают на блоки 3 и 4 алгебраического суммирования и формирователи 5 и 6 импульсных последовательностей, а также через эпе5 мент ИЛИ 41 на ОЗУ 2 и на счетный иход счетчика 35 адреса.

Счетчик 35 адреса, как и в режиме 01, определяет адрес ячейки ОЗУ 2, с которой в этом режиме считывается информация и по

0 шине 12 передается на блоки 3 и 4 алгебраического суммирования. После считывания всех N ячеек ОЗУ 2 счетч1 . 35 адреса переполняется, на его выходе формируется импульс, который через элемент 34 совпаде5 пия переводит RS-триггер 32 в состояние 1. В режиме 11, как указывалось, элемент 34 совпадения открыт. Далее состояние счетчика 37 режимов изменяется либо на состояние 00, если импульс на RS-триг0 rep 33 от решающего блока 8 ещё не пришел, либо на состояние 10, если импульс .решающего блока 8 пришел. В любом случае счатчик 37 режимов выходит из состояния 11 и элемент 40 совпадения

5 закрывается. Состояние счетчикз 35 адреса фиксируется в нулевом состоянии. С приходом импульса от решающего блока 8, ко- торый сигнализирует об окончании вычисления квадратичной суммы, сравнения с максимальным значением и вычисления исходных данных для (п+1) частоты, RS- триггер 33 переводится в состояние 1. По совпадению состояний RS-триггеров 32 и 33 на выходе элемента 36 совпадения формируется импульс, который устанавлиоает счетчик 37 режимов в состояние 10, а также переводит RS-триггеры 32 и 33 в состояние О.

После перехода счетчика 37 режимов в состояние 10 измеритель частоты переводится в режим 10 и цикл повторяется.

Формирователь импульсных последовательностей (фиг.2). До начала активной работы в формирователях 5 и 6 импульсных последовательностей осуществляется установка исходных данных (режим 10 измерителя частоты). Исходные данные вычисляются в решающем блоке 8 и определяются номером анализируемой частоты.

В регистр 14 памяти вводится код, равный Т/2Т0 - целой части отношения Т/2Т0, где Т 1 /Fo - период анализируемой частоты; То - интервал дискретизации, в регистр 16 памяти вводится код {Т/2Т0} - дробной части отношения Т/2Т0. Коды, вводимые в регистр 19 памяти и делитель 15 с переменным коэффициентом деления, зависят от но- мера формирователя импульсных последовательностей. В регистре 19 и делителе 15 формирователи 5 импульсной последовательности (назовем формирователем синфазного канала) вводятся соответственно коды {Т/4Т0} и нулевой. В формирователь 6 импульсной последовательности (назовем формирователем ортогонального канала) в регистр 19 памяти вводится код {Т/4Т0} - дробной части отношения ЗТ/4Т0, а в делитель 15 вводится код Т/4Т0 - целой части Т/4Т0.

Ввод исходных данных осуществляет-,-. от решающего блока по шине 10 данных о регистры памяти 14,16 и делитель 15 непосредственно, а в регистр 19 памяти мультиплексор 18. Выбор соответствующего элемента, в который записываются данные, осуществляется дешифратором 22, на вход которого поступает информация об адресе по шине 9 адреса от решающего блока 8. Синхронизирующий импульс записи данных на регистр 19 памяти поступает через элемент ИЛИ 24.

После перевода измерителя частоты в режим 10 нз вход делителя 15 с переменным коэффициентом деления через элемент И 23 поступают тактовые импульсы от блока 7 управления. Делитель 15 имеет коэффициент деления, равный Т/2Т0. В синфазном канале первый импульс на выходе делителя 15 появляется через Т/2Т0. Этот импульс поступает на триггер 21 исходное состояние которого соответствует 1, переводит его в состояние О (формируется первая полуволна опорного сигнала), а также поступает через элемент ИЛИ 24 на синхронизацию регистра 19 памяти. В регистр 19 памяти этим импульсом записывается код, равный сумме {Т/2Т0} + {Т/2Т0}. Если эта сумма по величине больше 1, то возникает импульс переноса на выходе регистр;) 19

0 памяти, который вбзбуждает одновибратор 20. На выходе одновибратора 20 формируется импульс, пергкрыззющий прохожде-- ние через элемент И 23 одного тактового импульса. Таким образом, на выходе дели5 теля 15 очередной импульс возникает через Т/2То + 1 тактовых импульсов (отрицательная полуволна опорного сигнала). Если сумма {Т/2Т0} + {Т/2Т0} меньше по значению 1, то импульса переноса с выхода регистра 19

0 памяти не возникает и очередной импульс возникает через T/2T0j тактовых импульсов. В результате такого взаимодействия импульсов на выходе триггера 21 будут формироваться полуволны опорного сигнала,

5 управляющие суммированием на плюс или на минус кодов, записанных в ячейках п.эмя- ти ОЗУ 2.

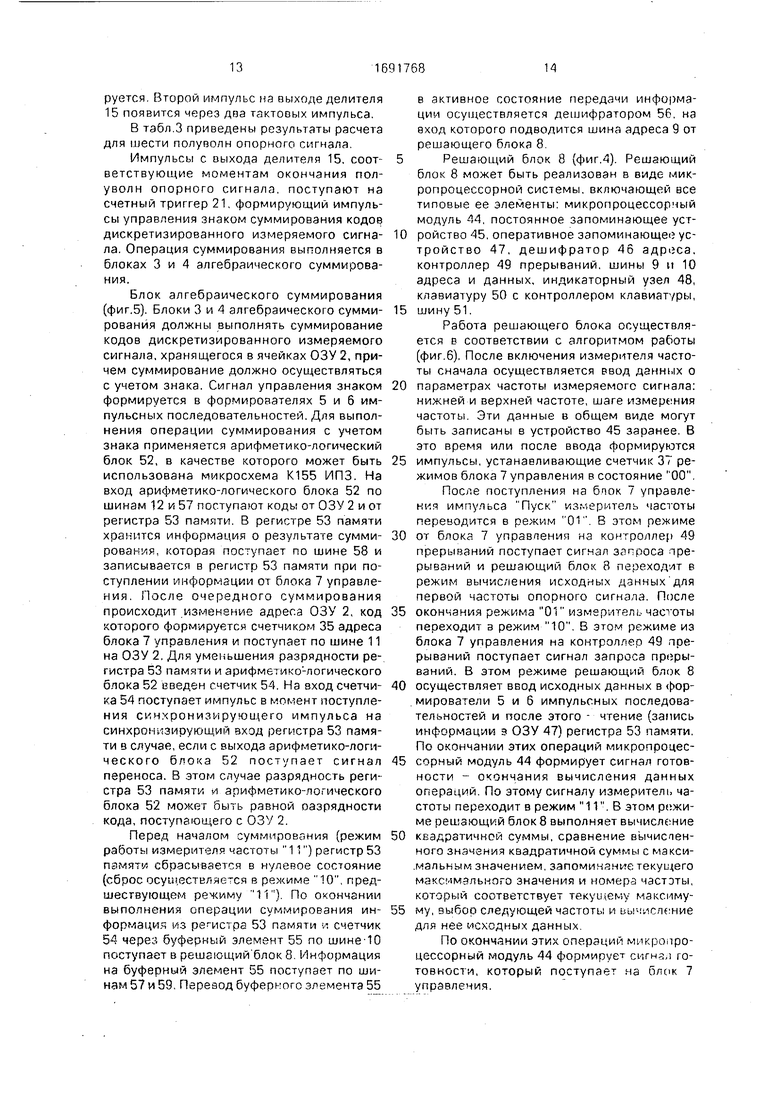

Для примера рассмотрим процесс формирования полуволн опорного сигнала (уп0 равляющих импульсов с выхода триггера 21) для Т/То 5,25; т.е. Т/2Т0 2,625: Т/4Т0 1,3125; Т/2Т0 2; {Т/2Т0} 0,625; Т/4Т0 1; Ш4Т0} 0,3125. Результаты расчета синфазного канала приведены в табл.2.

5 Для ортогонального канала должны формироваться прямоугольные импульсы с полуволнами, по длительности равными Т/2Т0, но сдвинутыми относительно тактовых импульсов на Т/4Т0, т.е. первый им0 пульс на выходе делителя 15 должен появляться через Т/4Т0 тактовых импульсов, второй - через Т/4Т0 + Т/2Т0 тактовых импульсов, j-й через Т/4Т0 - jT/2T0 тактовых импульсов.

5

Именно так формируются импульсы в формирователе импульсной последовательности ортогонального канала.

Продолжим пример. В регистр 19 ламя0 ти формирователя 6 импульсной последовательности этого канала вводится код {Т/4Т0} 0,3125, а исходное состояние делителя 15 соответствует Т/4Т0 1. Учитывая, что коэффициент деления делителя 15

5 равен Т/2Т0 2, первый импульс нз выходе делителя 15 будет при воздействии первого тактового импульса. Этот импульс запишет в регистр 19 памяти код числа 0,3125 + +0,625 0,9375, т.е. на выходе регистра 19 памяти импульс переполнения но сФормируется. Второй импульс на выходе делителя 15 появится через два тактовых импульса.

В табл.3 приведены результаты расчета для шести полуволн опорного сигнала.

Импульсы с выхода делителя 15. соответствующие моментам окончания полуволн опорного сигнала, поступают на счетный триггер 21, формирующий импульсы управления знаком суммирования кодое дискретизированного измеряемого сигнала. Операция суммирования выполняется в блоках 3 и 4 алгебраического суммирования.

Блок алгебраического суммирования (фиг.5). Блоки 3 и 4 алгебраического суммирования должны выполнять суммирование кодов дискретизированного измеряемого сигнала, хранящегося в ячейках ОЗУ 2, причем суммирование должно осуществляться с учетом знака. Сигнал управления знаком формируется в формирователях 5 и 6 импульсных последовательностей. Для выполнения операции суммирования с учетом знака применяется арифметико-логический блок 52, в качестве которого может быть использована микросхема К155 ИПЗ. На вход арифметико-логического блока 52 по шинам 12 и 57 поступают коды от ОЗУ 2 и от регистра 53 памяти. В регистре 53 памяти хранится информация о результате суммирования, которая поступает по шине 58 и записывается в регистр 53 памяти при поступлении информации от блока 7 управления. После очередного суммирования происходит изменение адреса ОЗУ 2, код которого формируется счетчиком 35 адреса блока 7 управления и поступает по шине 11 на ОЗУ 2. Для уменьшения разрядности регистра 53 памяти и арифметико-логического блока 52 введен счетчик 54. На вход счетчика 54 поступает импульс в момент поступления синхронизирующего импульса на синхронизирующий вход регистра 53 памяти в случае, если с выхода арифметико-логи- ческого блока 52 поступает сигнал переноса. В этом случае разрядность регистра 53 памяти и арифметико-логического блока 52 можег быть равной оазрядности кода, поступающего с ОЗУ 2.

Перед началом суммирования (режим работы измерителя частоты 11) регистр 53 памяти сбрасывается в нулевое состояние (сброс осуществляемся в режиме 10, предшествующем режиму 11). По окончании выполнения операции суммирования информация из регистра 53 памяти и счетчик 54 через буферный элемент 55 по шине-10 поступает в решающий блок 8. Информация на буферный элемент 55 поступает по шинам 57 и 59, Перезод буферного элемента 55

в активное состояние передачи информации осуществляется дешифратором 56. на вход которого подводится шина адреса 9 от решающего блока 8.

Решающий блок 8 (фиг.4). Решающий

блок 8 может быть реализован в виде микропроцессорной системы, включающей все типовые ее элементы: микропроцессорный модуль 44, постоянное запоминающее уст0 ройство 45, оперативное запоминающее устройство 47, дешифратор 46 адреса, контроллер 49 прерываний, шины 9 и 10 адреса и данных, индикаторный узел 48, клавиатуру 50 с контроллером клавиатуры,

5 шину 51.

Работа решающего блока осуществляется в соответствии с алгоритмом работы (фиг.6). После включения измерителя частоты сначала осуществляется ввод данных о

0 параметрах частоты измеряемого сигнала: нижней и верхней частоте, шаге измерения частоты. Эти данные в общем виде могут быть записаны в устройство 45 заранее. В это время или после ввода формируются

5 импульсы, устанавливающие счетчик 37 режимов блока 7 управления в состояние 00. После поступления на бпок 7 управления импульса Пуск измеритель частоты переводится в режим 01. В этом режиме

0 от блока 7 управпения на контроллер 49 прерываний поступает сигнал запроса прерываний и решающий блок 8 переходит в режим вычисления исходных данных для первой частоты опорного сигнала. После

5 окончания режима 01 измеритель частоты переходит з режим 10. В этом режиме из блока 7 управления на контроллер 49 прерываний поступает сигнал запроса прерываний. В этом режиме решающий блок 8

0 осуществляет ввод исходных данных в формирователи 5 и 6 импульсных последовательностей и после этого - чтение (запись информации з ОЗУ 47) регистра 53 памяти. По окончании этих операций микропроцес5 сорный модуль 44 формирует сигнал готовности - окончания вычисления данных операций. По этому сигналу измеритель частоты переходит в режим 11. В этом режиме решающий блок 8 выполняет вычисление

0 квадратичной суммы, сравнение вычисленного значения квадратичной суммы с макси- .мальным значением, запоминание текущего максимального значения и номера частоты, который соответствует текущему мэксмму5 му, выбор следующей часто ты и вычисление для нее исходных данных.

По окончании этих операций микропроцессорный модуль 44 формирует сигнал готовности, который поступает на блок 7 управления.

По окончании перебора всех N частотных точек микропроцессорный модуль 44 отправляет полученный результат измерения значения частоты, соответствующий максимуму квадратичной суммы, на индикацию в решающий блок 8 и формирует сигнал окончания измерения частоты. Этот сигнал поступает на блок 7 управления и срабатывает счетчик 37 режимов в состояние 00,

Точность измерения частоты определяется шагом- измерения частоты и шумовой составляющей. Если шумовая составляющая меньше шага измерения частоты, то точность измерения частоты может быть повышена алгоритмическим путем без изменения структурной схемы измерителя. Точность измерения может быть повышена, например, путем вычисления разностей квадратичных сумм или корней из квадратичных сумм с последующим использованием интерполяции.

Продолжим сравнение времени измерения известного способа, основанного на классическом спектральном анализе,и способа, по которому реализован предложенный измеритель.

Пусть N 103. При анализе одной частоты требуется выполнить N умножений и суммирований. С учетом анализа N частот при использовании БПФ время увеличивается в IgN раз. При использовании для выполнения вычисленных операций и операций формирования функций синуса и косинуса микропроцессоров серии К580 операция умножения и суммирования будет составлять 200 мкс, Тогда на измерение частоты в этом случае потребуется время Тизм

9ПП N InM 1ГГ6 «9ПП 1П3 1П 1ГУ6

N ЧдМ «200 10° -.10

200 2, с.

В описанном устройстве время измере ния определяется операцией суммирования. Время на выполнение этой опера ими при использовании БИС серии 155 состазяя- етО,1 мкс. На выполнение измерения частоты в этом случае требуется время порядка N2 0,1 0,1, с, что более чем на порядок меньше времени измерения при использовании классического спектрального анализа.

Таким образом, измеритель частоты позволяет уменьшить время измерения за счет исключения операций умножения при определении частоты.

Формула изобретения

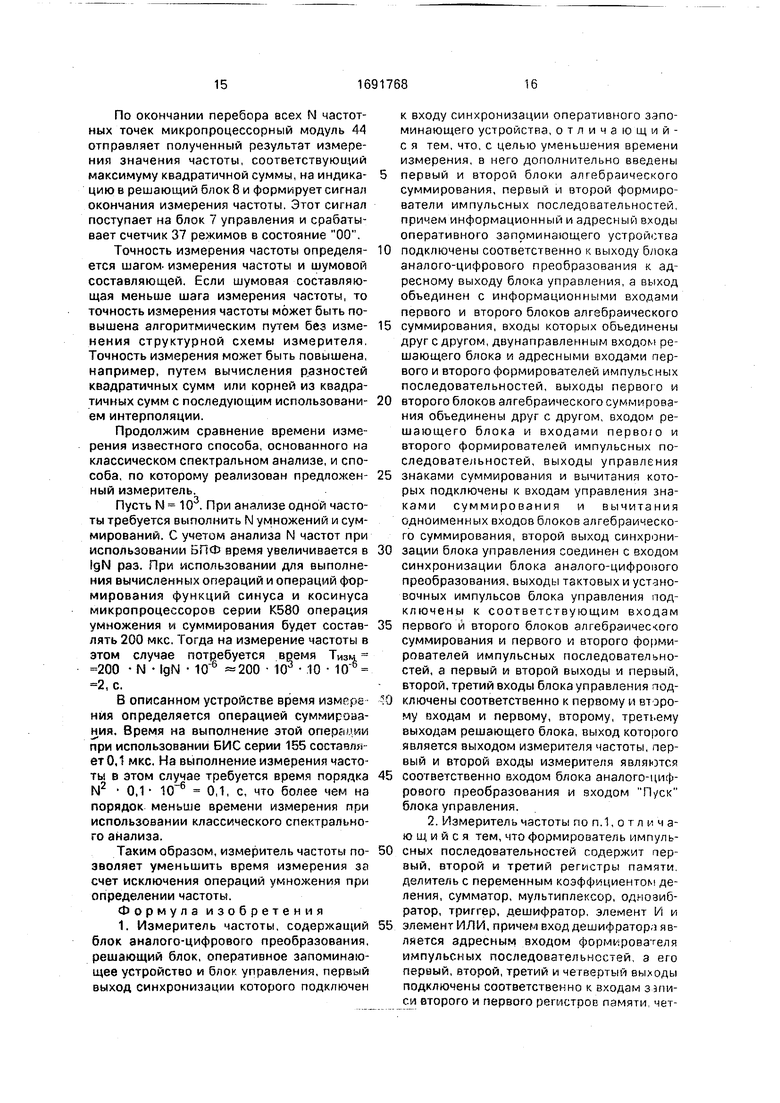

1. Измеритель частоты, содержащий блок аналого-цифрового преобразования, решающий блок, оперативное запоминающее устройство и блок управления, первый выход синхронизации которого подключен

к входу синхронизации оперативного запоминающего устройства, отличаю щий- с я тем, что, с целью уменьшения времени измерения, в него дополнительно введены

первый и второй блоки алгебраического суммирования, первый и второй формирователи импульсных последовательностей, причем информационный и адресный входы оперативного запоминающего устройства

0 подключены соответственно к выходу блока аналого-цифрового преобразования к адресному выходу блока управления, а выход объединен с информационными входами первого и второго блоков алгебраического

5 суммирования, входы которых объединены друг с другом, двунаправленным входом решающего блока и адресными входами первого и второго формирователей импульсных последовательностей, выходы первого и

0 второго блоков алгебраического суммирования объединены друг с другом, входом решающего блока и входами первого и второго формирователей импульсных последовательностей, выходы управления

5 знаками суммирования и вычитания которых подключены к входам управления знаками суммирования и вычитания одноименных входов блоков алгебраического суммирования, второй выход синхрони0 зации блока управления соединен с входом синхронизации блока аналого-цифрового преобразования, выходы тактовых и установочных импульсов блока управления подключены к соответствующим входам

5 первого и второго блоков алгебраического суммирования и первого и второго формирователей импульсных последовательностей, а первый и второй выходы и первый, второй, третий входы блока управления под0 ключены соответственно к первому и второму входам и первому, второму, третьему выходам решающего блока, выход которого является выходом измерителя частоты, первый и второй входы измерителя являются

5 соответственно входом блока аналого-цифрового преобразования и входом Пуск блока управления.

2. Измеритель частоты по п. 1, о т л и ч а- ю щ и и с я тем, что формирователь импуль0 сных последовательностей содержит первый, второй и третий регистры памяти. делитель с переменным коэффициентом деления, сумматор, мультиплексор, однозиб- ратор, триггер, дешифратор, элемент И и

5 элемент ИЛИ, причем вход дешифратора является адресным входом формирователя импульсных последовательностей, а его первый, второй, третий и четвертый выходы подключены соответственно к входам записи второго и первого регистров памяти четвертому входу делителя с переменным коэффициентом деления и третьему входу мультиплексора, выход второго регистра памяти через последовательно соединенные сумматор, мультиплексор и третий регистр памяти подключен к второму входу сумматора, вход второго регистра памяти является входом формирователя импульсных последовательностей и объединен с вторым входом мультиплексора, первым входом делителя с переменным коэффициентом деления и входом первого регистра памяти, выход которого подключен к третьему входу делителя с переменным коэффициентом деления, второй выход третьего регистра памяти через одновибратор соединен с первым входом элемента И, второй вход которого является входом тактовых импульсов формирователя импульсных последовательностей, а выход подключен к второму входу делителя с переменным коэффициентом деления, выход которого объединен со счетным входом триггера и вторым входом элемента ИЛИ, вход установки триггера является входом установочных импульсов формирователя импульсных последовательностей, а выходы триггера - выходами управления знаками суммирования и вычитания формирователя импульсных последовательностей, выход элемента ИЛИ соединен с входом записи третьего регистра памяти.

3. Измеритель частоты поп.1,отлича- ю щ и и с я тем, что блок управления содержит делитель частоты, дешифратор, генератор тактовых импульсов, первый и второй RS-триггеры, первый, второй, третий и четвертый элементы совпадения, счетчик адреса, первый, второй и третий элементы ИЛИ и счетчик режимов, причем выходы первого и второго RS-триггеров соединены с входами второго элемента совпадения, а первые входы объединены с выходом второго элемента совпадений и первым входом счетчика режимов, выход которого подключен к входу дешифратора, выход генератора тактовых импульсов через последовательно соединенные четвертый элемент совпадения и второй элемент ИЛИ подключен к счетному входу счетчика адреса, являющемуся первым выходом синхронизации блока управления, четвертый выход дешифратора, являющийся вторым выходом управляющих сигналов блока управления, объединен с первым входом третьего элемента ИЛИ и через третий элемент совпадения подключен к второму входу второго элемента ИЛИ,

который является вторым выходом синхронизации блока управления, первый выход дешифратора подключен к второму входу третьего элемента ИЛИ, выход которого соединен с входом счетчика адреса и является выходом установочных импульсов блока управления, выход генератора тактовых импульсов через делитель частоты подключен к второму входу третьего элемента совпадения, второй выход дешифратора объединен с вторым входом четвертого элемента совпадения и вторым входом первого элемента совпадения, выход которого соединен с вторым входом первого RS-триггера, а первый

вход объединен с вторым выходом счетчика адреса и вторым входом первого элемента ИЛИ, третий выход дешифратора является первым выходом управляющих сигналов блока управления, а второй вход второго

RS-триггера, третий вход счетчика режимов и третий вход первого элемента ИЛИ являются соответственно первым, вторым и третьим управляющими входами блоке управления, первый вход первого элемента

ИЛИ является входом Пуск блока управления, а выход подключен к счетному входу счетчика режимов, выход четвертого элемента совпадения является выходом тактовых импульсов блока управления.

4. Измеритель частоты по п. 1, о т л и ч а- ю щ и и с я тем, что блок алгебраического суммирования содержит последовательно соединенные арифметико-логический блок

и регистр памяти, выход которого объединен с первым входом буферного элемента и вторым входом арифметико-логического блока, счетчик, дешифратор, причем первый вход арифметико-логического блока является информационным входом блока алгебраического суммирования, выходом которого является выход буферного элемента, третий и четвертый входы арифметико-логического блока являются входами управления знаками суммирования и вычитания блока алгебраического суммирования, входы тактовых и установочных импульсов которого служат соответствующими входами регистра памяти, второй выход регистра памяти подключен к счетному входу счетчика, вход установочных импульсов которого объединен с одноименным входом регистра п.эмя- ти, а выход соединен с вторым входом буферного элемента, выход дешифратора

подключен к третьему входу буферного элемента, а вход является входом блока алгебраического суммирования.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

| Автоматический измеритель импульсной мощности СВЧ - радиосигналов | 1989 |

|

SU1704102A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Генератор функций | 1990 |

|

SU1809432A1 |

| Устройство компенсации сигнала царапин кинопленки | 1986 |

|

SU1392635A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЗВЕНЬЕВ ДИНАМИЧЕСКИХ СИСТЕМ | 1990 |

|

RU2068576C1 |

Изобретение относится к радиоизмерительной технике и может использоваться для определения частоты сигналов при наличии помех. Целью изобретения является уменьшение времени измерения частоты. Измеритель частоты содержит блок аналого-цифрового преобразования, оперативное запоминающее устройство, блок управления и решающий блок. Введение блоков алгебраического суммирования и формирователей импульсных последовательностей позволяет исключить операции умножения при определении частоты, что и обеспечивает сокращение длительности измерения. 3 з.п.ф-лы, 7 ил., 3 табл.

Код режима (состояние счетчика режима

Операции, которые осуществляются в данном режиме

00

Режим ожидания. Сброс счетчика 35 адреса в нулевое состояние

1

0

1

Режим АЦП. Накопление информации в ОЗУ 2. Вычисление в блоке 8 исходных данных для первой частоты. Сброс регистра 53 памяти блоков 3 и 4 в Hyneeqe состояние и триггера 21 блоков 5 и 6 в состояние 1, Ввод исходных данных для п-й частоты. Запись информации из регистров 53 памяти блоков 3 и 4 в ОЗУ 47 блока 8.

Режим алгебраического суммирования. Взаимодействуют блоки 7, 3 и 4, 5 и 6,2.

Одновременно в блоке 8 вычисление квадратичной суммы (п-1) частоты, сравнение результата вычисления с максимальным значением квадратичной суммы, вычисление исходных данных для (п-Н) частоты.

Условия при которых осуществляется переход в данный режим

После включения измерителя. Переход в состояние осуществляется по сигналам из решающего блока 8. После окончания измерения частоты Поступление импульса Пуск

После окончания режима 01 или кроме того после окончания режима 11

После окончания режима 10

Таблица 2

Таблица 3

Bxodl

,ПуСК

Вход 2

Фиг.

фиа.2

Выход

П

ft

фцё.З

Kl

tit

ЩигМ

55

1L

59

56

J

От7

Oml

От 5,6 От 5,6

Фи.5

Начало

ввод данных о нижней и верхней час/по/ле диапазона, шаге изменения час/яа/пы

Формирование сигнала установки сче/лчиш режг/- мов блока 7 S нулевое сос/лояние

выбор первой /0с/77о/т7Ал S6t4UC/feHuefr/ To t Г/4Т0, {Г/гГо},{Г#Ъ.

Сброс счетчика режимов б йла/се 7у/7раЈлемя Ј нулевое coe/лоянуе

ввод данных в решающий олокиз 6 /io#a алгеброй- ческого су/ мироЈания

вь/иисленае хвадр. суммы

Сравнение вычисленного значения кЗадр. суммы со значением, соответствующимлредб/дущему максимуму

Запоминание маясиг я с/ юс/тго/яь/, хо/порая соо/я- ветс/явуе/т махси/ /уму

выбор следующей уас/пя/пы, вб/щмеме

r/гго, , {г/гто1 {т1ито}

Hem .

Фиг. 6

/iW

5f0

| Цифровой панорамный измеритель частоты | 1985 |

|

SU1296955A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-11-15—Публикация

1989-10-20—Подача