оь

О5

о

Изобретение относится к автоматике и вычислительной технике и может быть использовано для одновременного измерения, запоминания и анализа различных параметров объекта.

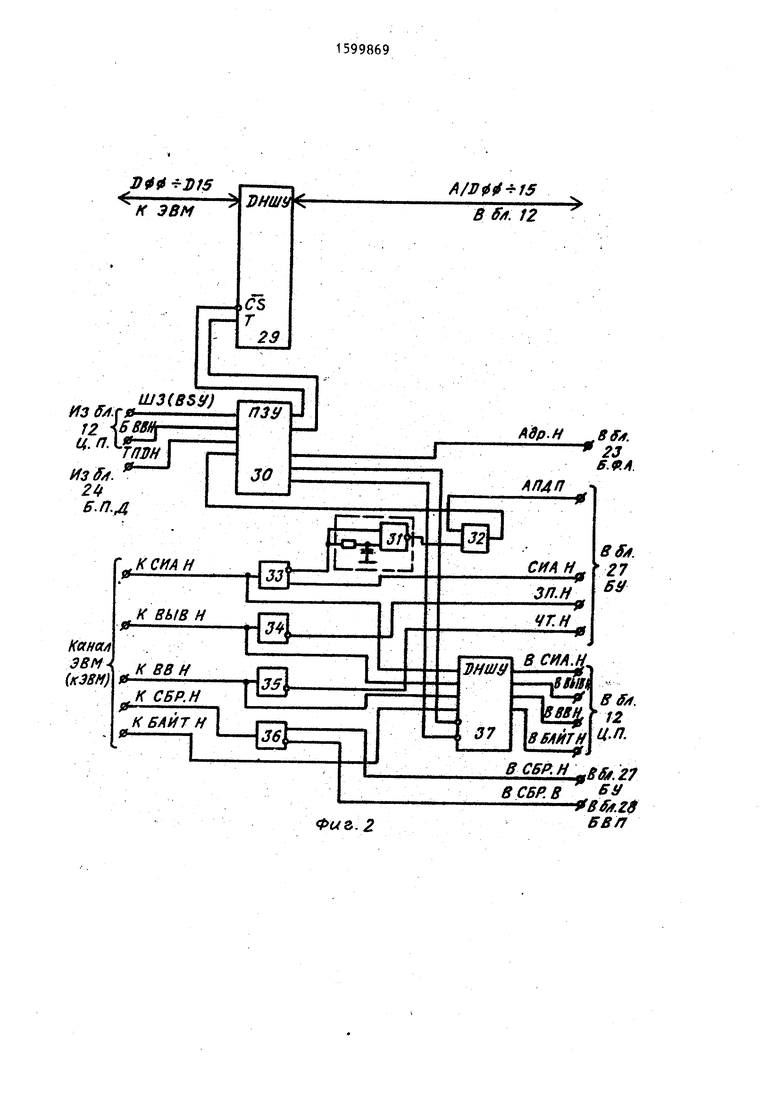

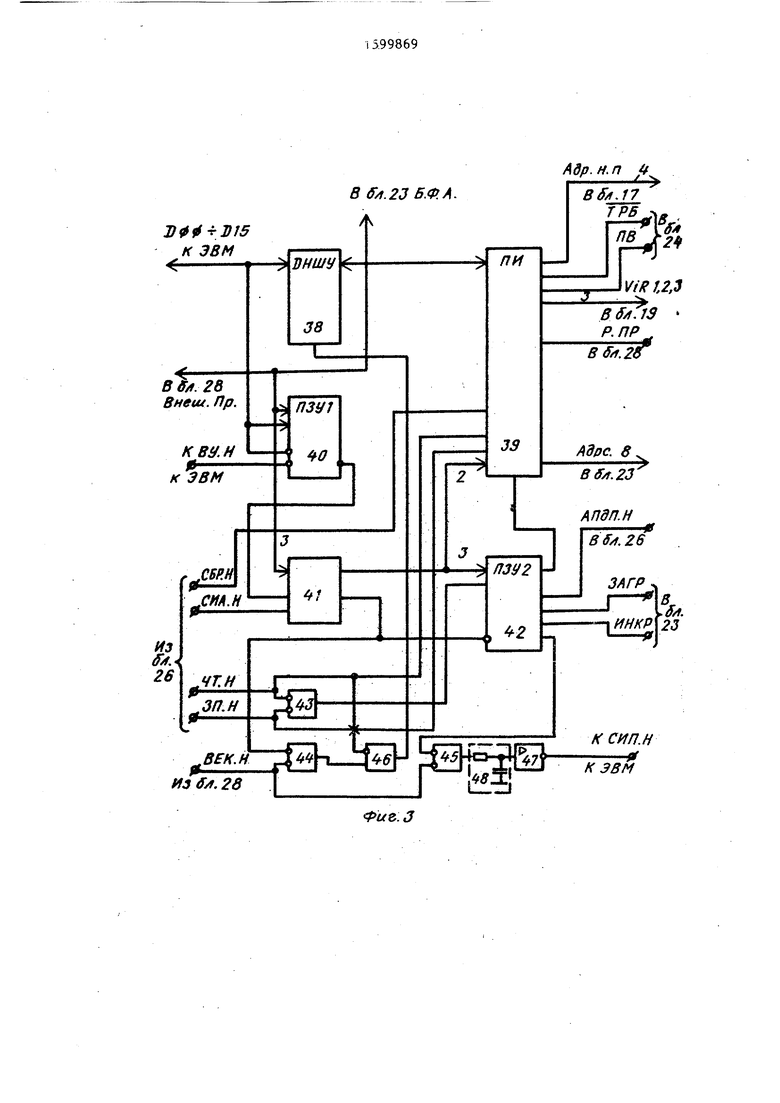

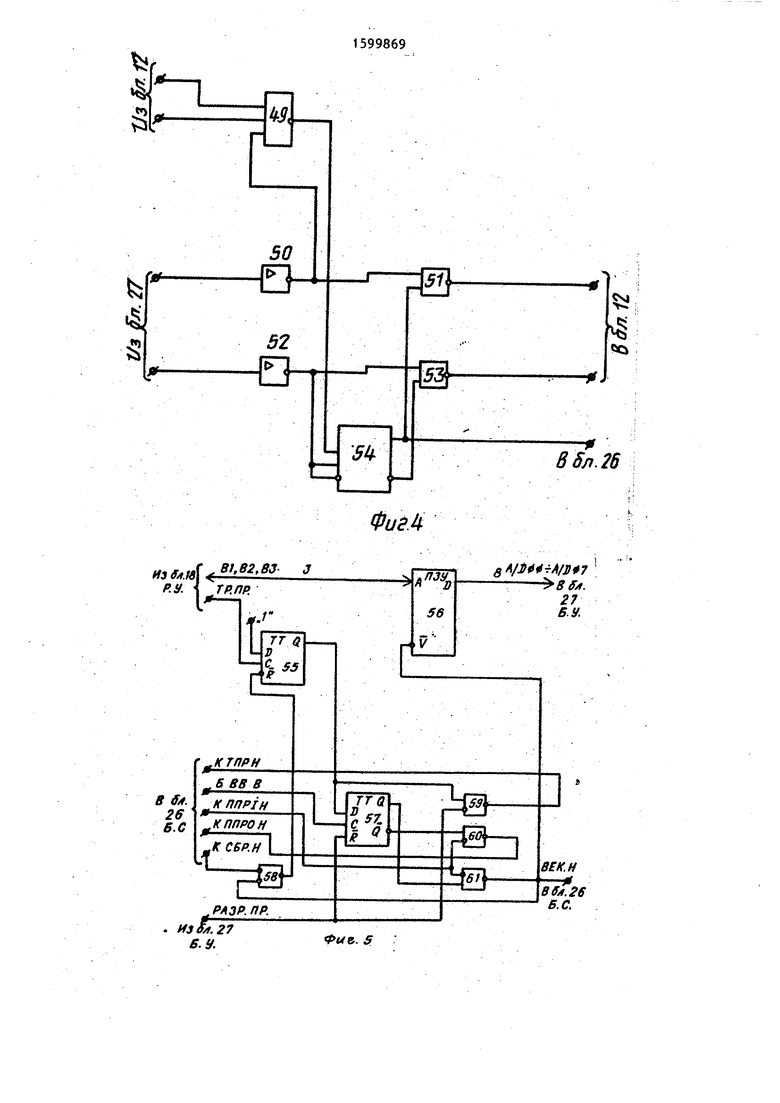

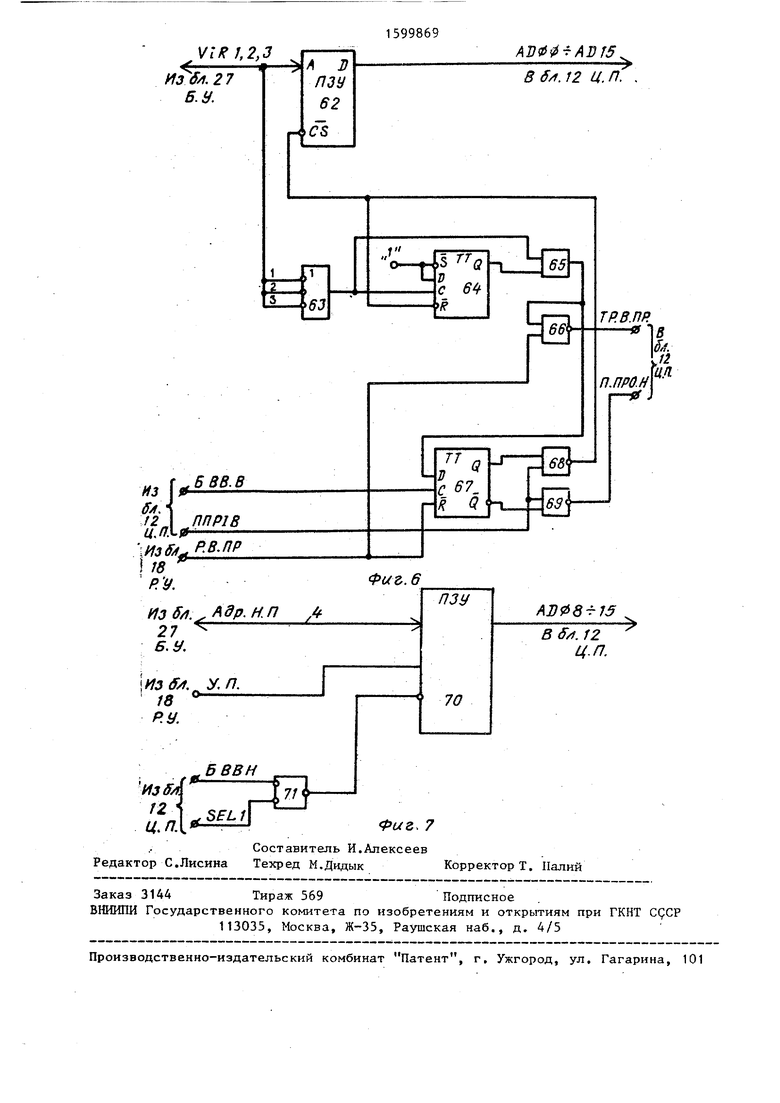

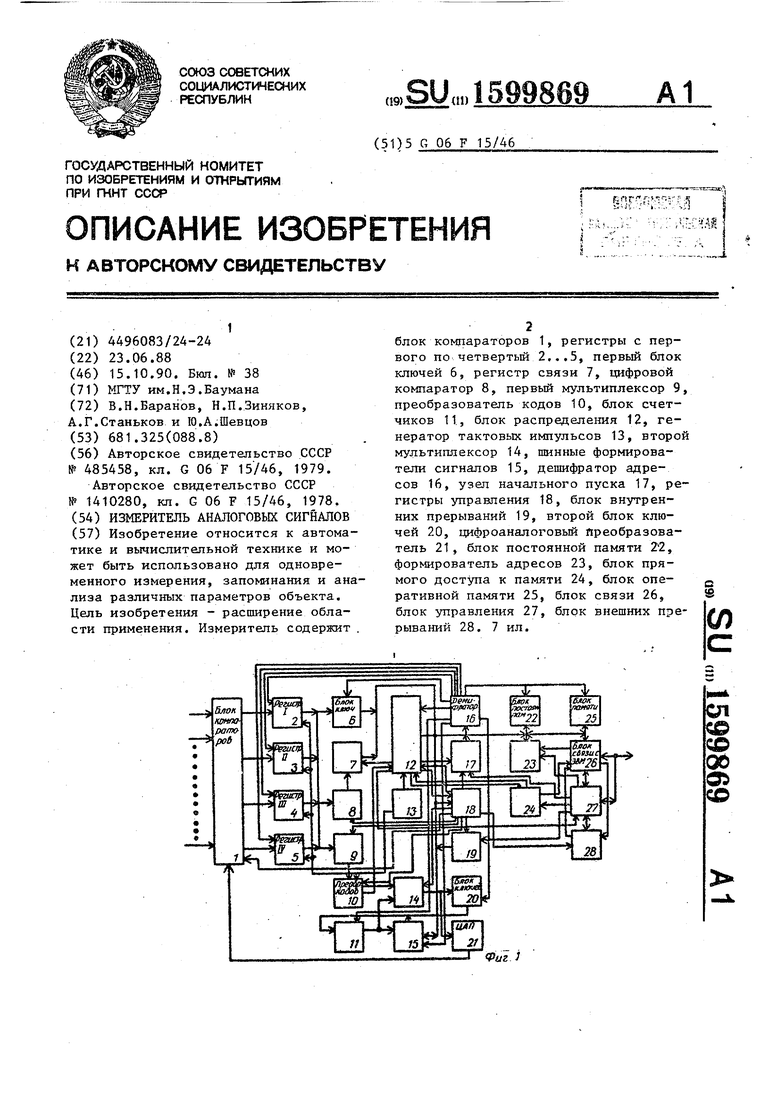

Цель изобретения - расширение области применения устройства за счет произвольного порядка опроса аналоговых сигналов, изменения спос ба измерения и обеспечения прогнозирования состояния объекта контроля. На фиг.1 приведена схема устройства; на фиг.2 - схема блока связи на фиг.З - схема блока управления; на фиг.4 - схема блока прямого достпа; на фиг.З - схема блока внешних прерываний; на фиг.6 - схема блока внутренних прерьшаний; на фиг.7 - схема блока начального пуска.

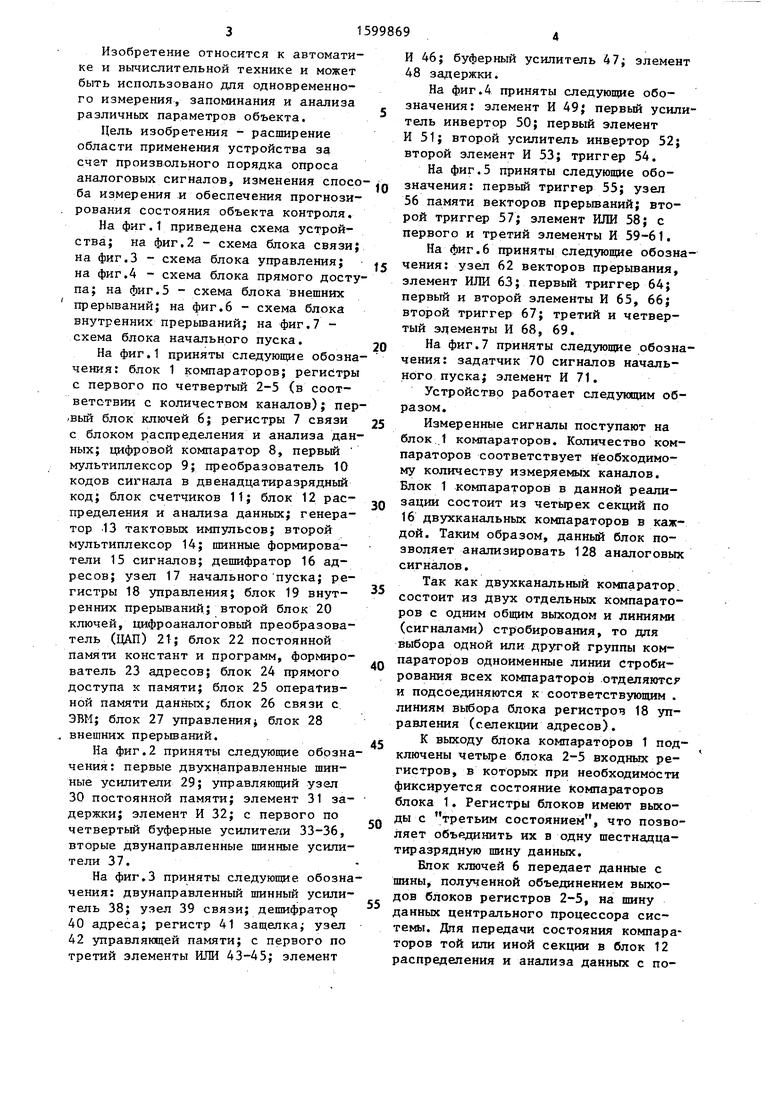

На фиг.1 приняты следующие обозна чения: блок 1 компараторов; регистры с первого по четвертый 2-5 (в соответствии с количеством каналов); пер Вый блок ключей 6; регистры 7 связи с блоком распределения и анализа данных; цифровой компаратор 8, первый мультиплексор 9; преобразователь 10 кодов сигнала в двенадцатиразрядный код; блок счетчиков 11; блок 12 распределения и анализа данных; генератор .13 тактовых импульсов; второй мультиплексор 14; шинные формирователи 15 сигналов; дешифратор 16 адресов; узел 17 начального пуска; регистры 18 управления; блок 19 внутренних прерываний; второй блок 20 ключей, цифроаналоговый преобразователь (ЦАП) 2t; блок 22 постоянной памяти констант и программ, формирователь 23 адресов; блок 24 прямого доступа к памяти; блок 25 оперативной памяти данных,- блок 26 связи с. ЭВМ; блок 27 управленияj блок 28 внешних прерьшаний.

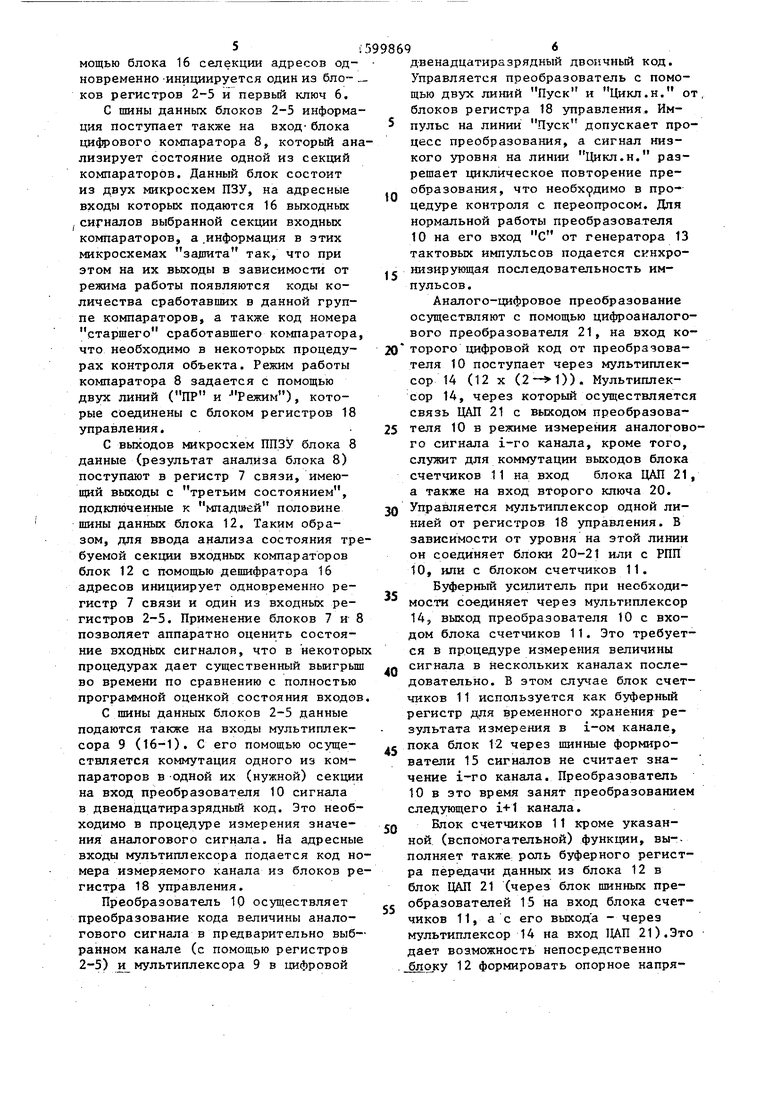

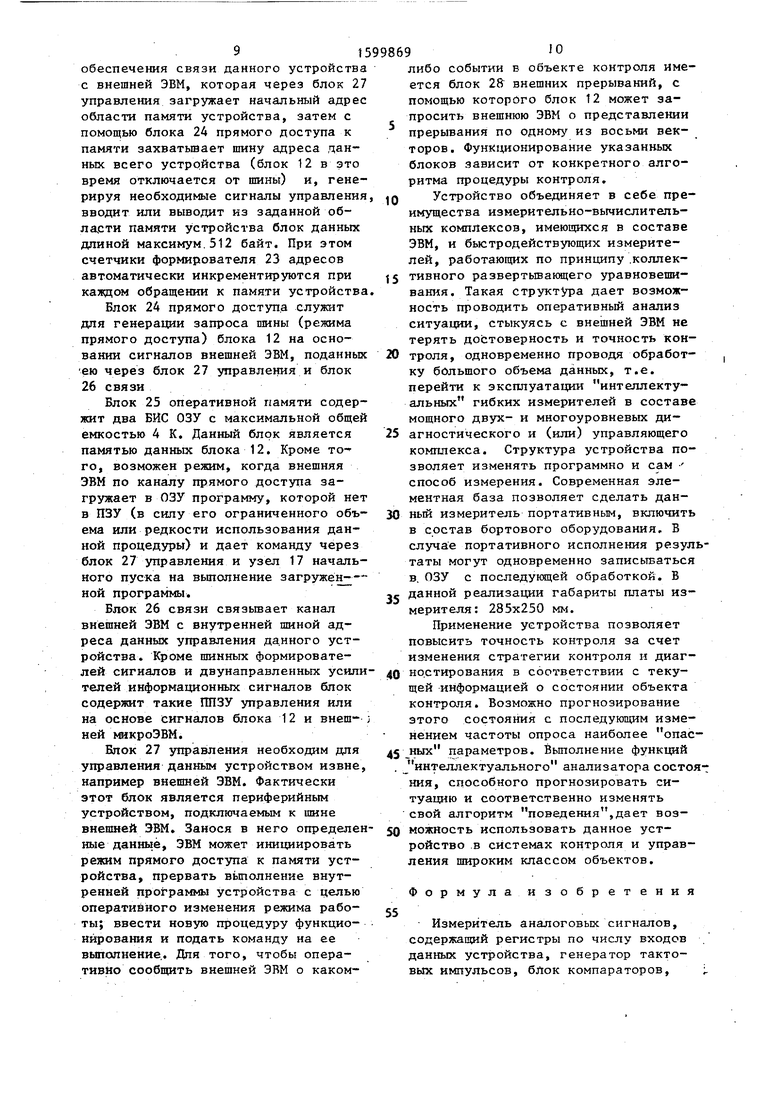

На фиг.2 приняты следующие обозначения: первые двухнаправленные шинные усилители 29; управляющий узел 30 постоянной памяти; элемент 31 задержки; элемент И 32; с первого по четвертый буферные усилитехш 33-36, вторые двунаправленные шинные усилители 37.

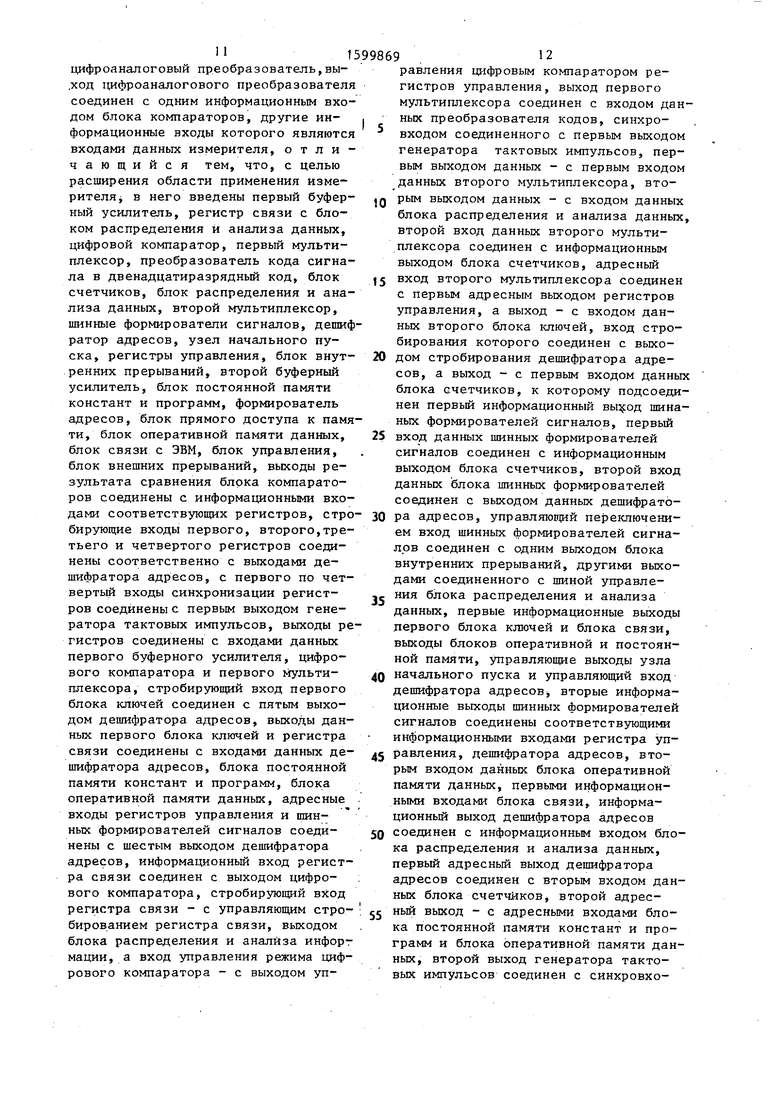

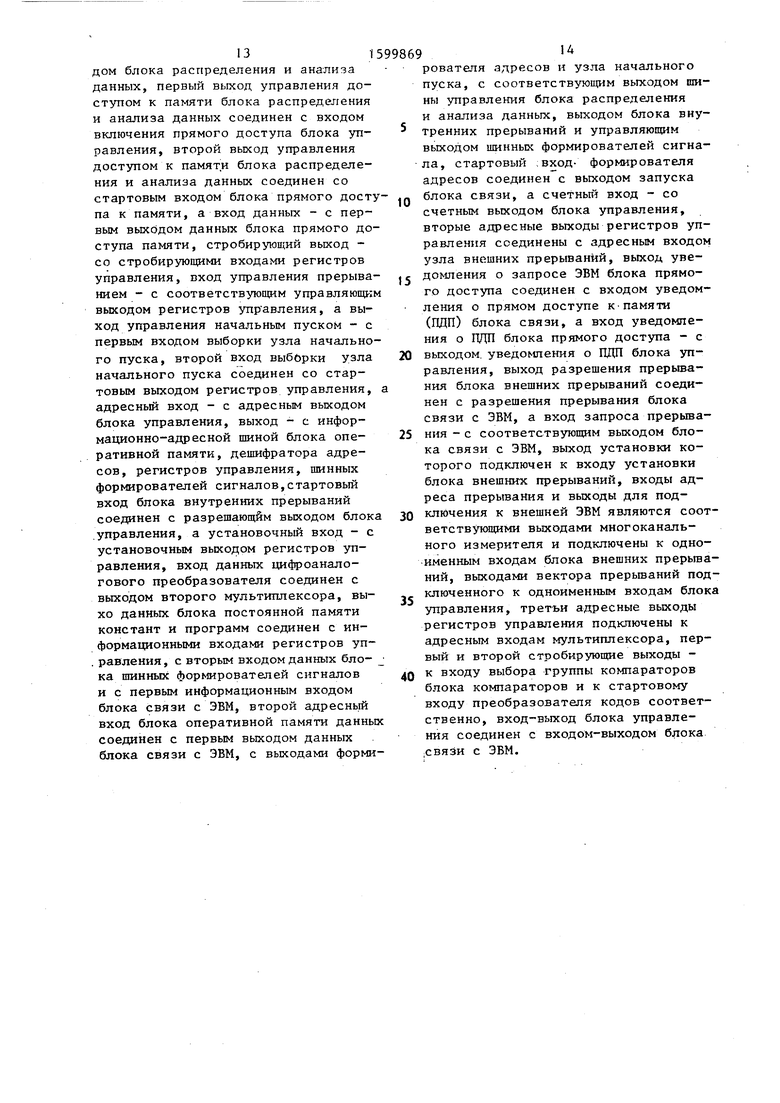

На фиг.З приняты следующие обозначения: двунаправленный шинный усилитель 38; узел 39 связи; дешифратор 40 адреса; регистр 41 защелкаj узел 42 управляющей памяти; с первого по третий элементы ИЛИ 43-45; элемент

,,. .-

55

30

35

40

45

0

И 46; буферный усилитель 47; элемент 48 задержки.

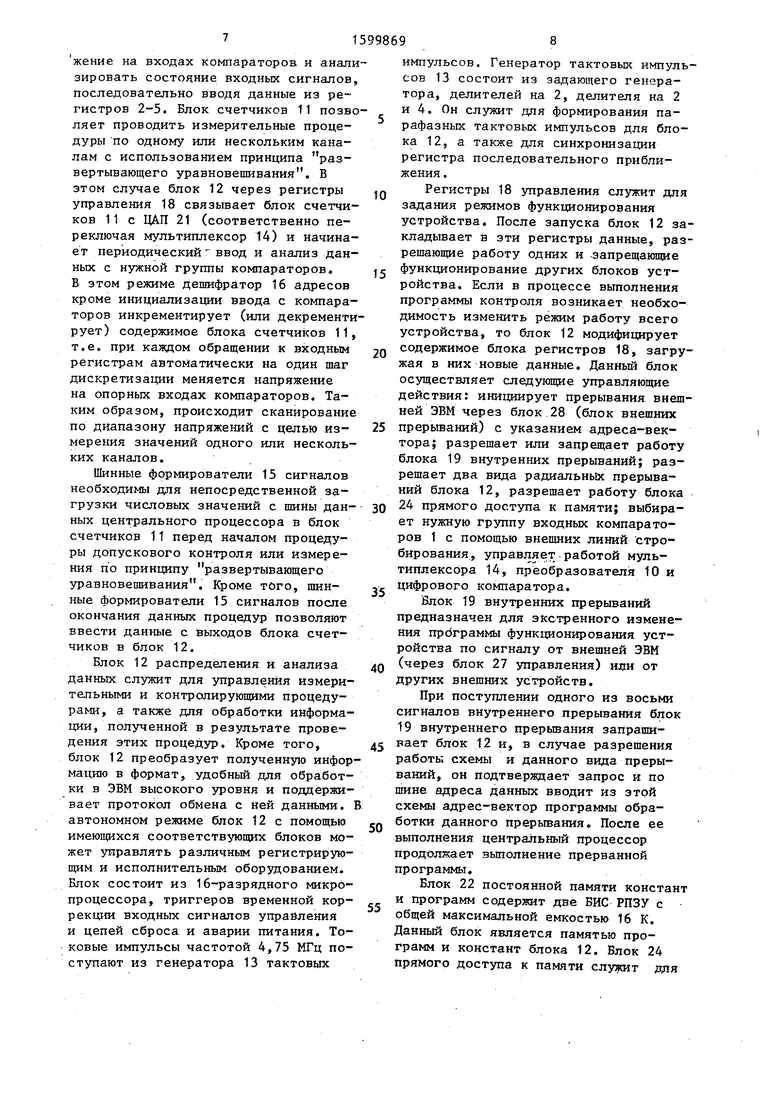

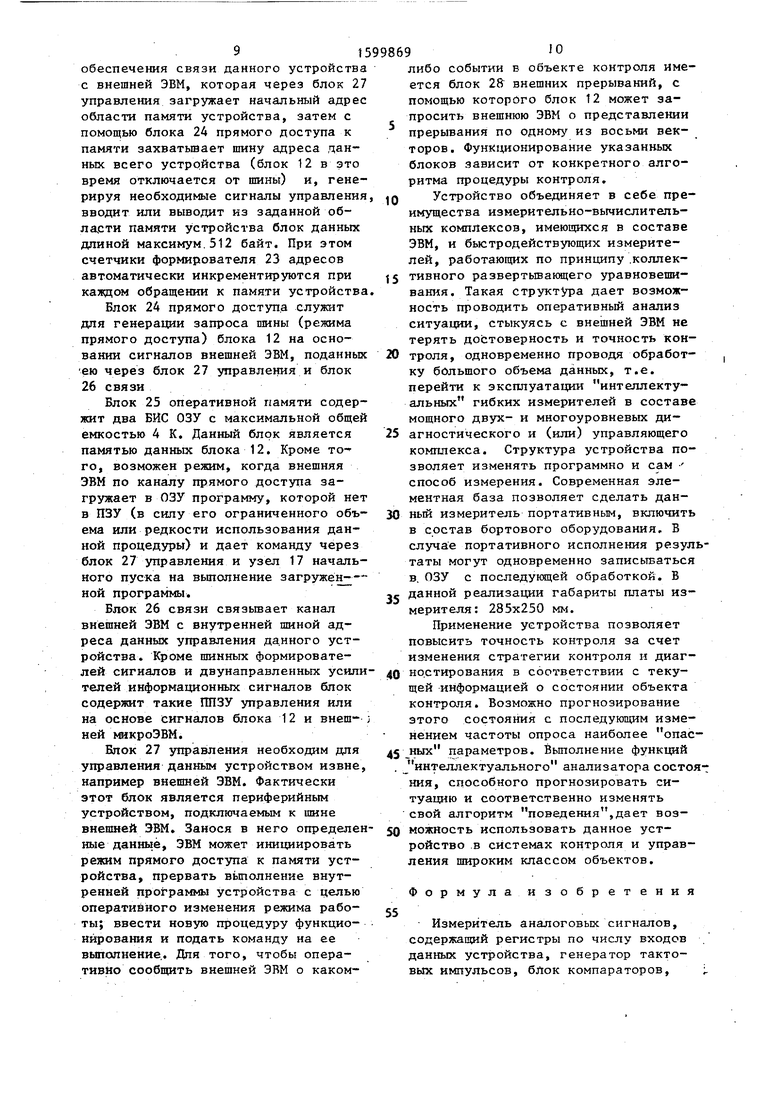

На фиг.4 приняты следующие обозначения: элемент И 49} первый усилитель инвертор 50; первый элемент И 51; второй усилитель инвертор 52; второй элемент И 53; триггер 54.

На фиг.5 приняты следующие обозначения: первый триггер 55; узел 56 памяти векторов прерываний; второй триггер 57; элемент ИЛИ 58; с первого и третий элементы И 59-61.

На фиг.6 приняты следующие обозначения: узел 62 векторов прерывания, элемент ИЛИ 63; первый триггер 64; первый и второй элементы И 65, 66; второй триггер 67; третий и четвертый элементы И 68, 69.

На фиг.7 приняты следующие обозначения: задатчик 70 сигналов начального пуска; элемент И 71.

Устройство работает следующим образом.

Измеренные сигналы поступают на блок 1 компараторов. Количество компараторов соответствует необходимому количеству измеряемых каналов. Блок 1 компараторов в данной реализации состоит из четырех секций по 16 двухканальных компараторов в каждой. Таким образом, данный блок позволяет анализировать 128 аналоговых сигналов.

Так как двухканальный компаратор, состоит из двух отдельных компараторов с одним общим выходом и линиями (сигналами) стробирования, то для выбора одной или другой группы компараторов одноименные линии стробирования всех компараторов отделяются И подсоединяются к соответствующим . линиям выбора блока регистров 18 управления (селекции адресов).

К выходу блока компараторов 1 подключены четыре блока 2-5 входных ре- гистров, в которых при необходимости фиксируется состояние компараторов блока 1. Регистры блоков имеют выходы с третьим состоянием, что позволяет объединить их в одну шестнадцатиразрядную шину данных.

Блок ключей 6 передает данные с шины, полученной объединением выходов блоков регистров 2-5, на шину данных центрального процессора системы. Для передачи состояния компараторов той или иной секции в блок 12 распределения и анализа данных с попеII

имею- 11

половине

состоянием t

мощью блока 16 селекции адресов од- новременно -инициируется один из бло . ков регистров 2-5 и первый ключ 6,

С шины данньпс блоков 2-5 информация постзшает также на вход-блока цифрового компаратора 8, который анализирует состояние одной из секций компараторов. Данный блок состоит из двух микросхем ПЗУ, на адресные входы которых подаются 16 выходных I сигналов выбранной секции входных компараторов, а .информация в зтих микросхемах задгита так, что при этом на их выходы в зависимости от режима работы появляются коды количества сработавших в данной групкомпараторов, а также код номера старшего сработавшего компаратора что необходимо в некоторых процедурах контроля объекта. Режим работы компаратора 8 задается с помощью двух линий (ПР и - Режим), которые соединены с блоком регистров 18 управления.

С выходов микросхем ППЗУ блока 8 данные (результат анализа блока 8) поступают в регистр 7 связи, щий выходы с трет подключенные к мпадшей шины данных блока 12. Таким образом, для ввода анализа состояния требуемой секции входных компараторов блок 12 с помощью дешифратора 16 адресов инициирует одновременно регистр 7 связи и один из входных регистров 2-5. Применение блоков 7 и 8 позволяет аппаратно оценить состояние входных сигналов, что в некоторы процедурах дает существенный выигрьж во времени по сравнению с полностью программной оценкой состояния входов

С шины данных блоков 2-5 данные подаются также на входы мультиплексора 9 (16-1). С его помощью осуществляется коммутация одного из компараторов в одной их (нужной) секции на вход преобразователя 10 сигнала в двенадцатиразрядный код. Это необходимо в процедуре измерения значения аналогового сигнала. На адресные входы мультиплексора подается код номера измеряемого канала из блоков регистра 18 управления.

Преобразователь 10 осуществляет преобразование кода величины аналогового сигнала в предварительно выбранном канале (с помощью регистров 2-5) и мультиплексора 9 в цифровой

o

5

0

5

0

5

0

5

0

5

д-венадцатиразрядный двоичный код. Управляется преобразователь с помощью двух линий Пуск и Цикп.н. от, блоков регистра 18 управления. Импульс на линии Пуск допускает процесс преобразования, а сигнал низкого уровня на лишда Цикл.н. разрешает циклическое повторение преобразования, что необхсрдимо в процедуре контроля с переопросом. Для нормальной работы преобразователя 10 на его вход G от генератора 13 тактовых импульсов подается синхронизирующая последовательность импульсов.

Аналого-цифровое преобразование осуществляют с помощью цифроаналого- вого преобразователя 21, на вход ко- торого цифровой код от преобра-зова- теля 10 поступает через мультиплексор 14 (12 X ()). Мультиплексор 14, через который осуществляется связь ЦАП 21 с выходом преобразователя 10 в режиме измерения аналогового сигнала i-ro канала, кроме того, служит для коммутации выходов блока счетчиков 11 на вход блока ЦАП 21, а также на вход второго ключа 20. Управляется мультиплексор одной линией от регистров 18 управления. В зависимости от уровня на этой линии он соединяет блоки 20-21 или с РПП 10, или с блоком счетчиков 11.

Буферный усилитель при необходимости соединяет через мультиплексор 14, выход преобразователя 10 с входом блока счетчиков 11. Это требуется в процедуре измерения величины сигнала в нескольких каналах последовательно. В этом случае блок счетчиков 11 используется как буферный регистр для временного хранения результата измерения в i-ом канале, пока блок 12 через шинные формирователи 15 сигналов не считает значение i-ro канала. Преобразователь 10 в это время занят преобразованием следующего i+1 канала.

Блок счетчиков 11 кроме указанной (вспомогательной) функции, вы-- полняет также; роль буферного регистра передачи данных из блока 12 в блок ЦАП 21 (через блок шинных преобразователей 15 на вход блока счетчиков 11, ас его выхода - через мультиплексор 14 на вход ЦАП 21),Это дает возможность непосредственно блоку 12 формировать опорное напряжение на входах компараторов и аналзировать состояние входных сигналов последовательно вводя данные из регистров 2-5. Блок счетчиков 11 позвляет проводить измерительные процедуры по одному или нескольким каналам с использованием принципа развертывающего уравновешивания. В этом случае блок 12 через регистры управления 18 связывает блок счетчиков 11 с ЦАП 21 (соответственно переключая мультиплексор 14) и начинает периодический ввод и анализ данных с нужной группы компараторов, В этом режиме дешифратор 16 адресов кроме инициализации ввода с компараторов инкрементирует (или декремент рует) содержимое блока счетчиков 11 т.е. при каждом обращении к входным регистрам автоматически на один шаг дискретизации меняется напряжение на опорных входах компараторов. Таким образом, происходит сканировани по диапазону напряжений с целью из- мерения значений одного или нескольких каналов.

Шинные формирователи 15 сигналов необходимы для непосредственной загрузки числовых значений с шины дан- ных центрального процессора в блок счетчиков 11 перед началом процедуры допускового контроля или измерения по принципу развертывающего уравновешивания. Кроме того, шин- ные формирователи 15 сигналов после окончания данных процедур позволяют ввести данные с выходов блока счетчиков в блок 12.

Блок 12 распределения и анализа данных служит для управления измерительными и контролирующими процедурами, а также для обработки информации, полученной в результате проведения этих процедур. Кроме того, блок 12 преобразует полученную информацию в формат, удобный для обработки в ЭВМ высокого уровня и поддерживает протокол обмена с ней данными. автономном режиме блок 12 с помощью имеющихся соответствующих блоков может управлять различным регистрирующим и исполнительным оборудованием. Блок состоит из 16-разрядного микропроцессора, триггеров временной кор- рекции входньпс сигналов управления и цепей сброса и аварии питания. Токовые импульсы частотой 4,75 МГц поступают из генератора 13 тактовых

импульсов. Генератор тактовых импульсов 13 состоит из задающего генератора, делителей на 2, делителя на 2 и 4. Он служит для формирования па- рафазных тактовых импульсов для блока 12, а также для синхронизации регистра последовательного приближения .

Регистры 18 управления служит для задания режимов функционирования устройства. После запуска блок 12 закладывает в эти регистры данные, разрешающие работу одних и запрещающие функционирование других блоков устройства. Если в процессе вьтолнения программы контроля возникает необходимость изменить режим работу всего устройства, то блок 12 модифицирует содержимое блока регистров 18, загружая в них новые данные. Данньй блок осуществляет следующие управляющие действия: инициирует прерывания внешней ЭВМ через блок 28 (блок внешних прерываний) с указанием адреса-вектора; разрешает или запрещает работу блока 19 внутренних прерываний; раз- рещает два вида радиальных прерываний блока 12, разрешает работу блока 24 прямого доступа к памяти; выбирает нужную группу входных компараторов 1 с помощью внешних линий стро- бирования, управляет работой мультиплексора 14, преобразователя 10 и цифрового компаратора.

Влок 19 внутренних прерываний предназначен для экстренного изменения прбграммы функционирования устройства по сигналу от внешней ЭВМ (через блок 27 управления) или от других внешних устройств.

При поступлении одного из восьми сигналов внутреннего прерывания блок 19 внутреннего прерывания запрашивает блок 12 и, в случае разрешения работы схемы и данного вида прерываний, он подтверждает запрос и по шине адреса данньк вводит из этой схемы адрес-вектор программы обработки данного прерывания. После ее выполнения центральный процессор продолжает выполнение прерванной программы.

Блок 22 постоянной памяти констант и программ содержит две БИС РПЗУ с общей максимальной емкостью 16 К. Данный блок является памятью программ и констант блока 12, Блок 24 прямого доступа к памяти служит для

обеспечения связи данного устройства с внешней ЭВМ, которая через блок 27 управления загружает начальный адрес области памяти устройства, затем с помощью блока 24 прямого доступа к памяти захватьшает шину адреса данных всего устройства (блок 12 в это время отключается от шины) и, генерируя необходимые сигналы управления вводит или выводит из заданной области памяти устройства блок данных длиной максимум.512 байт. При этом счетчики формирователя 23 адресов автоматически инкрементируются при каждом обращении к памяти устройства

Блок 24 прямого доступа служит для генерации запроса шины (режима прямого доступа) блока 12 на основании сигналов внешней ЭВМ, поданных ею через блок 27 управления и блок 26 связи

Блок 25 оперативной памяти содержит два БИС ОЗУ с максимальной общей емкостью 4 К. Данный блок является памятью данных блока 12. Кроме того, возможен режим, когда внешняя ЭВМ по каналу прямого доступа загружает в ОЗУ программу, которой нет в ПЗУ (в силу его ограниченного объема или редкости использования данной процедуры) и дает команду через блок 27 управления и узел 17 начального пуска на выполнение загружён-- ной программы.

Блок 26 связи связьшает канал внешней ЭВМ с внутренней шиной адреса данных управления да.нного устройства. Кроме шинных формирователей сигналов и двунаправленных усилителей информационных сигналов блок содержит такие ППЗУ управления или на основе сигналов блока 12 и внеш- ней ьикроЭВМ.

Блок 27 управления необходим для управления данным устройством извне, например внешней ЭВМ. Фактически этот блок является периферийным устройством, подключаемым к шине внешней ЭВМ. Занося в него определенные данные, ЭВМ может инициировать режим прямого доступа к памяти устройства, прервать вьтолнение внутренней программы устройства с цепью оперативного изменения режима работы; ввести новую процедуру функционирования и подать команду на ее вьтолнение.. Дпя того, чтобы оперативно сообщить внешней ЭВМ о какомлибо событии Б объекте контроля имеется блок 28 внешних прерываний, с помощью которого блок 12 может запросить внешнюю ЭВМ о представлении прерывания по одному из восьми векторов. ФунК1щонирование указанных блоков зависит от конкретного алгоритма процедуры контроля.

Устройство объединяет в себе преимущества измерительно-вычислительных комплексов, имеющихся в составе ЭВМ, и быстродействующих измерителей, работающих по принципу .коллек5 тинного развертьшающего уравновешивания. Такая структура дает возможность проводить оперативный анализ ситуации, стыкуясь с внешней ЭВМ не терять достоверность и точность контроля, одновременно проводя обработку большого объема данных, т.е. перейти к эксплуатахщи интеллектуальных гибких измерителей в составе мощного двух- и многоуровневых ди5 агностического и (или) управляющего комплекса. Структура устройства позволяет изменять программно и сам способ измерения. Современная элементная база позволяет сделать дан0 ный измеритель портативным, включить в состав бортового оборудования. В случае портативного исполнения результаты могут одновременно записываться в. ОЗУ с последукщей обработкой. В

с данной реализации габариты платы измерителя: 285x250 мм.

Применение устройства позволяет повысить точность контроля за счет изменения стратегии контроля и диаг0 ностирования в соответствии с текущей информацией о состоянии объекта контроля. Возможно прогнозирование этого состояния с последующим изме- опроса наиболее опасS

0

5

нением частоты ных параметров. Вьшолнение функций интеллектуального анализатора состояния, способного прогнозировать ситуацию и соответственно изменять свой алгоритм поведения,дает возможность использовать данное устройство .в системах контроля и управления широким классом объектов.

Формулам зобретения

Измеритель аналоговых сигналов, содерзкащий регистры по числу входов данных устройства, генератор тактовых импульсов, блок компараторов, ;.

11

цифроаналоговый преобразователь,вы- .ход цифроаналогового преобразовател соединен с одним информационным входом блока компараторов, другие ин- формационные входы которого являютс входами данных измерителя, отличающийся тем, что, с целью расширения области применения измерителя в него введены первый буферный усилитель, регистр связи с блоком распределения и анализа данных, цифровой компаратор, первьш мультиплексор, преобразователь кода сигнала в двенадцатиразрядный код, блок счетчиков, блок распределения и анализа данных, второй мультиплексор, шинные формирователи сигналов, деширатор адресов, узел начального пуска, регистры управления, блок внутренних прерываний, второй буферный усилитель, блок постоянной памяти констант и программ, формирователь адресов, блок прямого доступа к памти, блок оперативной памяти данных, блок связи с ЭВМ, блок управления, блок внешних прерываний, выходы результата сравнения блока компараторов соединены с информационными входами соответствующих регистров, стр бирующие входы первого, второго,третьего и четвертого регистров соединены соответственно с выходами дешифратора адресов, с первого по четвертый входы синхронизации регистров соединены с первым выходом генератора тактовых импульсов, вьпсоды ргистров соединены с входами данных первого буферного усилителя, цифрового компаратора и первого мультиплексора, стробирующий вход первого блока ключей соединен с пятым выходом дешифратора адресов, вькоды данных первого блока ключей и регистра связи соединены с входами данных дешифратора адресов, блока постоянной памяти констант и программ, блока оперативной памяти данных, адресные входы регистров управления и шинных формирователей сигналов соединены с шестым выходом дешифратора адресов, информационный вход регистра связи соединен с выходом цифро- вого компаратора, стробирующий вход регистра связи - с управляющим стро бированием регистра связи, выходом блока распределения и анализа инфор мации, а вход управления режима цифрового компаратора - с выходом уп

12

o

5

5

0

равления цифровым компаратором регистров управления, выход первого мультиплексора соединен с входом данных преобразователя кодов, синхро- входом соединенного с первым выходом генератора тактовых импульсов, первым выходом данных - с первым входом данных второго мультиплексора, вторым выходом данных - с входом данных блока распределения и анализа данных, второй вход данных второго мультиплексора соединен с информационным выходом блока счетчиков, адресный вход второго мультиплексора соединен с первым адресным выходом регистров управления, а выход - с входом данных второго блока ключей, вход стро- бирования которого соединен с выхо- 0 дом стробирования дешифратора адресов, а выход - с первым входом данных блока счетчиков, к которому подсоединен первьй информационный шина- ных формирователей сигналов, первый вход данных шинных формирователей сигналов соединен с информационным выходом блока счетчиков, второй вход данных блока шинных формирователей соединен с выходом данных дешифратора адресов, управляюп(ий переключением вход шинных формирователей сигналов соединен с одним выходом блока внутренних прерываний, другими выходами соединенного с шиной управления блока распределения и анализа данных, первые информационные выходы лервого блока ключей и блока связи, выходы блоков оперативной и постоянной памяти, управляющие выходы узла начального пуска и управляющий вход дешифратора адресов вторые информационные выходы шинных формирователей сигналов соединены соответствующими информационными входами регистра управления, дешифратора адресов, вторым входом данных блока оперативной памяти данных, первыми информационными входами блока связи, информационный выход дешифратора адресов соединен с информационным входом блока распределения и анализа данных, первый адресный выход дешифратора адресов соединен с вторым входом данных блока счетчиков, второй адресный выход - с адресными входами блока постоянной памяти констант и программ и блока оперативной памяти данных, второй выход генератора тактовых импульсов соединен с синхровхо5

0

5

0

13

дом блока распределения и анализа данных, первый выход управления доступом к памяти блока распределения и анализа данных соединен с входом включения прямого доступа блока управления, второй выход управления доступом к памяти блока распределения и анализа данных соединен со стартовым входом блока прямого дост па к памяти, а вход данных - с первым выходом данных блока прямого доступа памяти, стробирующий выход - со стробирующими входами регистров управления, вход управления прерыванием - с соответствующим управляющи выходом регистров упр авления, а выход управления начальным пуском - с первым входом выборки узла начального пуска, второй вход выборки узла начального пуска соединен со стартовым выходом регистров управления, адресный вход - с адресным выходом блока управления, выход - с информационно-адресной шиной блока оперативной памяти, дешифратора адресов, регистров управления, шинных формирователей сигналон,стартовый вход блока внутренних прерываний соединен с разрешающим выходом блок .управления, а установочный вход - с установочным выходом регистров управления, вход данных цифроанало- гового преобразователя соединен с выходом второго мультиплексора, вы- хо данных блока постоянной памяти констант и программ соединен с информационными входами регистров уп- . равления, с вторым входом данных бло- ка шинных формирователей сигналов и с первым информационным входом блока связи с ЭВМ, второй адресный вход блока оперативной памяти данны соединен с первым выходом данных блока связи с ЭВМ, с выходами форми

15

20

- д а 30 jj j 40 х 25

А

рователя адресов и узла начального пуска, с соответствующим выходом щи- ны управления блока распределения и анализа данньпс, выходом блока внутренних прерываний и управляющим выходом шинных формирователей сигнала, стартовый :вход- формирователя адресов соединен с выходом запуска блока связи, а счетньш вход - со счетным выходом блока управления, вторые адресные выходы регистров управления соединены с адресным входом узла внешних прерываний, выход уведомления о запросе ЭВМ блока прямого доступа соединен с входом уведомления о прямом доступе к-памяти (ГЩП) блока связи, а вход уведомления о ДДП блока прямого доступа - с выходом, уведомления о ПДП блока управления, выход разрешения прерьгоа- ния блока внешних прерываний соединен с разрешения прерывания блока связи с ЭВМ, а вход запроса прерывания - с соответствующим выходом блока связи с ЭВМ, выход установки которого подключен к входу установки блока внешних прерываний, входы адреса прерывания и выходы для подключения к внешней ЭВМ являются соответствующими выходами многоканального измерителя и подключены к одноименным входам блока внешних прерьгаа- ний, выходами вектора прерьшаний подключенного к одноименным входам блока управления, третьи адресные выходы регистров управления подключены к адресным входам мультиплексора, первый и второй стробирующие выходы - к входу выбора группы компараторов блока компараторов и к стартовому входу преобразователя кодов соответственно, вход-выход блока управления соединен с входом-выходом блока связи с ЭВМ.

Канал ЭВМ (кЭВМ)

Фие. 2

ВСБР,.9ч

8 СВР. В У ffSff.Z$ БВЛ

В ff.23 Б.Ф.А. /К

УИШУ

38

В e/i 26

Вмеие. Пр.

ИЗ ff. 26

Адр.н.п /f

Bf.n

ТРВ

пв

f.

2it

ViR 12.3 -rВ .13 P. ПР

Bffi.25

К ЭВМ

Ll-±l

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1990 |

|

SU1753467A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для одновременного измерения, запоминания и анализа различных параметров объекта. Цель изобретения - расширение области применения. Измеритель содержит блок компараторов 1, регистры с первого по четвертый 2...5, первый блок ключей 6, регистр связи 7, цифровой компаратор 8, первый мультиплексор 9, преобразователь кодов 10, блок счетчиков 11, блок распределения 12, генератор тактовых импульсов 13, второй мультиплексор 14, шинные формирователи сигналов 15, дешифратор адресов 16, узел начального пуска 17, регистры управления 18, блок внутренних прерываний 19, второй блок ключей 20, цифроаналоговый преобразователь 21, блок постоянной памяти 22, формирователь адресов 23, блок прямого доступа к памяти 24, блок оперативной памяти 25, блок связи 26, блок управления 27, блок внешних прерываний 28. 7 ил.

Фие.З

...,.BJ.B2.e3 J ЛУ.

В SA. 26 Б.С

РАЭР. пр. ИзУл.27

е.у.

Фиъ. 5

ФигЛ

д

.

27 Б. У.

BffA.26 б. С.

«

VIK J,

H3ff/i,27 Б.У,

Р В.ПР

I 18

p.y.

Аи0Ф- А1)Г5.

Фиг,. 6

| Многоканальный измеритель | 1973 |

|

SU485458A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный измеритель аналоговых сигналов | 1987 |

|

SU1410280A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-15—Публикация

1988-06-23—Подача