Изобретение относится к вычислительной технике и может быть использовано для ускоренного преобразования частично развернутой формы Р 1 кода Фибоначчи в минимальную форму при одновременном контроле исходного кода на соответствие признакам частично развернутой формы Р 1 кода Фибоначчи.

Цель изобретения - повышение быстродействия преобразования.

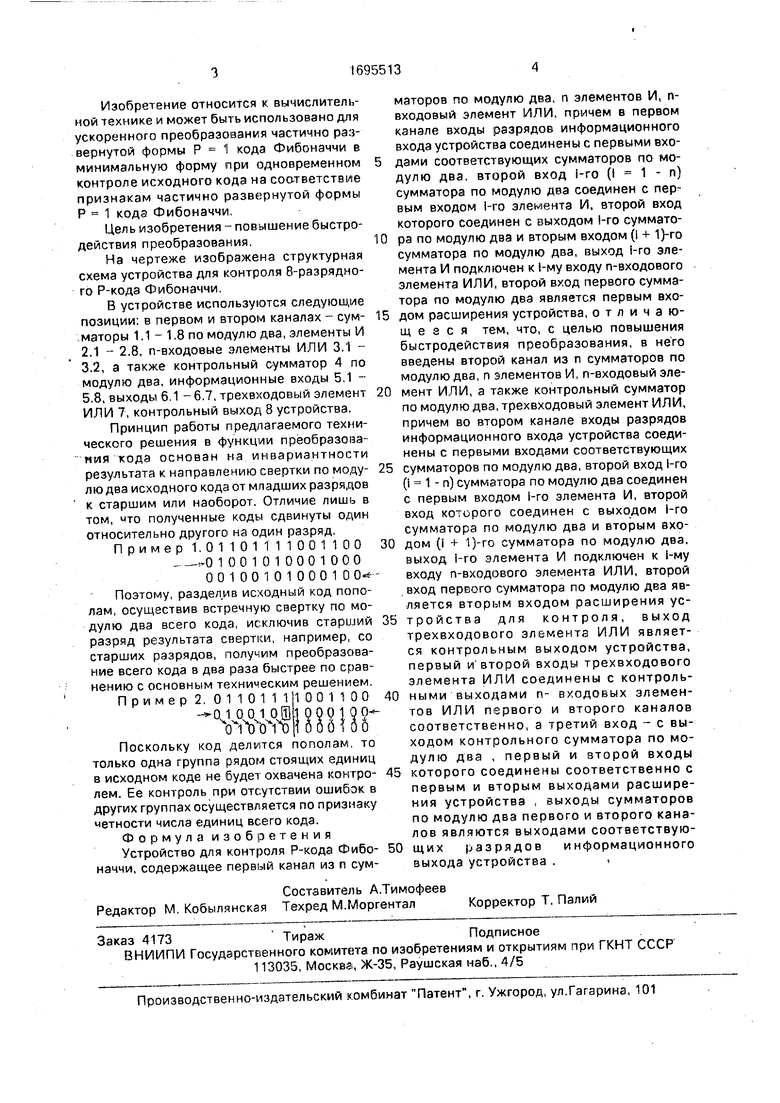

На чертеже изображена структурная схема устройства для контроля 8-разрядного Р-кода Фибоначчи.

В устройстве используются следующие позиции: в первом и втором каналах - сум- чматоры 1.1 - 1.8 по модулю два, элементы И 2.1 - 2.8, n-входовые элементы ИЛИ 3,1 - 3.2, а также контрольный сумматор 4 по модулю два, информационные входы 5.1 - 5.8, выходы 6.1 - 6.7, трехвходовый элемент ИЛИ 7, контрольный выход 8 устройства.

Принцип работы предлагаемого технического решения в функции преобразования кода основан на инвариантности результата к направлению свертки по модулю два исходного кода от младших разрядов к старшим или наоборот. Отличие лишь в том, что полученные коды сдвинуты один относительно другого на один разряд,

Пример 1.0 1 1 0 1 1 1 1 001 1 00 --О 1001010001000 00100101000100

Поэтому, раздел.ив исходный код пополам, осуществив встречную свертку по модулю два всего кода, исключив старший разряд результата свертки, например, со старших разрядов, получим преобразование всего кода в два раза быстрее по сравнению с основным техническим решением.

Пример 2. 01101111001100

01 001 ОШ VlWffi

Поскольку код делится пополам, то только одна группа рядом стоящих единиц в исходном коде не будет охвачена контролем. Ее контроль при отсутствии ошибок в других группах осуществляется по признаку четности числа единиц всего кода. Формула изобретения Устройство для контроля Р-кода Фибоначчи, содержащее первый канал из п сумматоров по модулю два, п элементов И, п- входовый элемент ИЛИ, причем в первом канале входы разрядов информационного входа устройства соединены с первыми входами соответствующих сумматоров по модулю два, второй вход i-ro (I 1 - п) сумматора по модулю два соединен с первым входом 1-го элемента И, второй вход которого соединен с выходом 1-го сумматора по модулю два и вторым входом (I + 1)-го сумматора по модулю два, выход i-ro элемента И подключен к -му входу п-входового элемента ИЛИ, второй вход первого сумматора по модулю два является первым входом расширения устройства, отличающееся тем, что, с целью повышения быстродействия преобразования, в него введены второй канал из п сумматоров по модулю два, п элементов И, n-входовый элемент ИЛИ, а также контрольный сумматор по модулю два, трехвходовый элемент ИЛИ, причем во втором канале входы разрядов информационного входа устройства соединены с первыми входами соответствующих

сумматоров по модулю два, второй вход 1-го (I 1 - п) сумматора по модулю два соединен с первым входом 1-го элемента И, второй вход которого соединен с выходом 1-го сумматора по модулю два и вторым входом (i + 1)-го сумматора по модулю два, выход i-ro элемента И подключен к i-му входу n-входового элемента ИЛИ, второй вход первого сумматора по модулю два является вторым входом расширения устройства для контроля, выход трехвходового элемента ИЛИ является контрольным выходом устройства, первый и второй входы трехвходового элемента ИЛИ соединены с контрольными выходами п- входовых элементов ИЛИ первого и второго каналов соответственно, а третий вход - с выходом контрольного сумматора по модулю два , первый и второй входы

которого соединены соответственно с первым и вторым выходами расширения устройства , выходы сумматоров по модулю два первого и второго каналов являются выходами соответствующих разрядов информационного выхода устройства ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Устройство для контроля Р-кодов Фибоначчи | 1988 |

|

SU1533007A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU907548A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

Изобретение относится к вычислительной технике, может быть использовано в качестве преобразователя частично-развернутой формы Р - кода Фибоначчи в минимальную форму кода. Цель изобретения - повышение быстродействия преобразования. Устройство содержит в первом и втором каналах сумматоры 1.1 - 1.8 по модулю два, элементы И 2.1 - 2.8 n-входовые элеме- ты ИЛИ 3.1 - 3.2, а также контрольный сумматор 4 по модулю два, информационные входы 5.1 -5,8, выходы Ј.1 - 6.7, трехвходо- вый элемент ИЛИ 7, контрольный выход 8 устройства. Повышение быстродействия в два раза достигается за счет одновременного преобразования двух групп разрядов исходного кода. 1 ил.

| Авторское свидетельство СССР Мг1608805. |

Авторы

Даты

1991-11-30—Публикация

1989-06-19—Подача