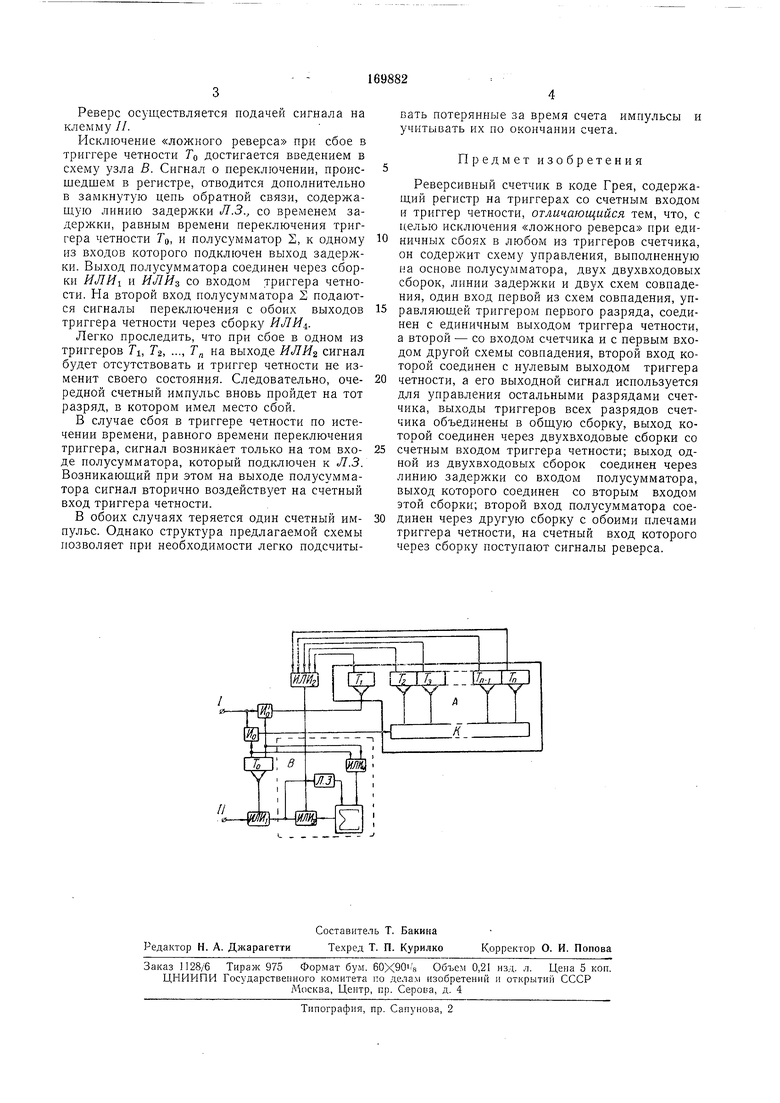

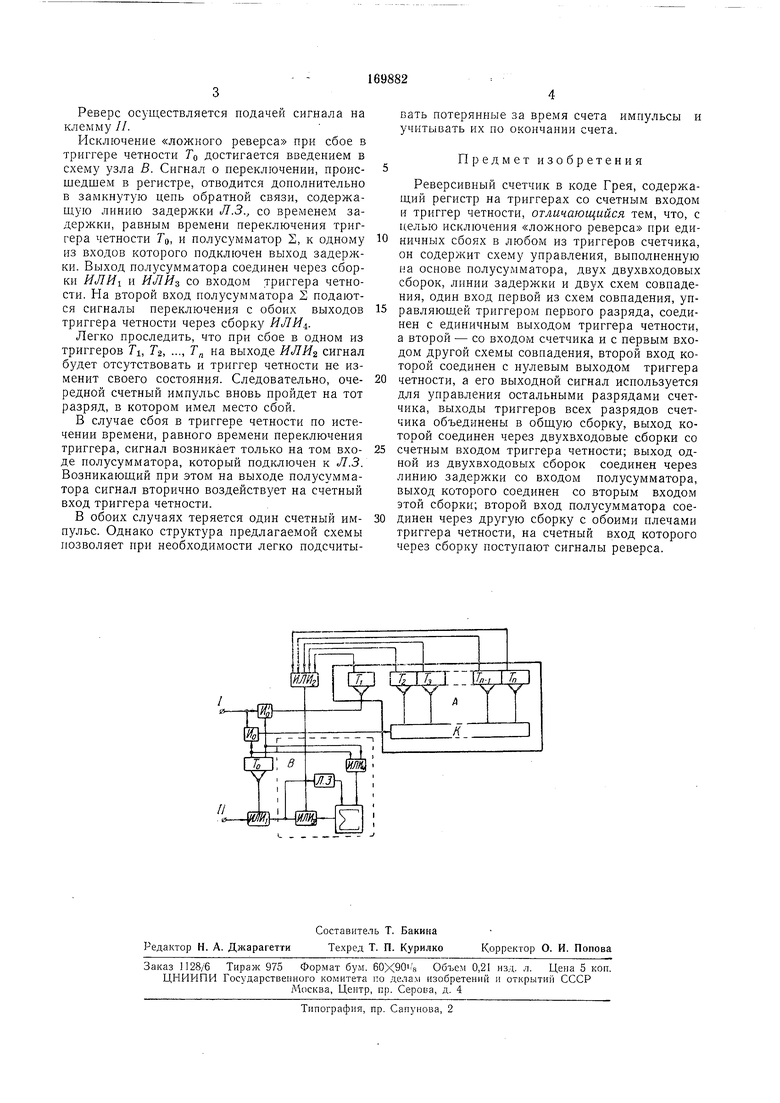

Известны реверсивные счетчики в коде Грея, содержащие регистр на триггерах со счетным входом и триггер четности. Недостаток таких счетчиков заключается в том, что случайный сбой (несрабатывание) в любом из разрядов счетчика, включая триггер четности, приводит к ошибке «ложный реверс. Предложенный счетчик отличается от известных тем, что для исключения «ложного реверса нри единичных .сбоях в любом из триггеров счетчика он содержит схему управления, выполненную на основе полусумматора, двух двухвходовых сборок, линии задержки и двух схем совпадения. Один вход нервой из схем совпадения, управляющей триггером первого разряда, соединен с единичным выходом триггера четности, а другой - со входом счетчика и с первым входом другой схемы совпадения. Второй вход схемы соединен с нулевым выходом триггера четности, а его выходной сигнал используется для управления остальными разрядами счетчика. Выходы триггеров всех разрядов счетчика объединены в сбщую сборку, выход которой соединен через двухвходовые сборки со счетным входом триггера четности. Выход одной из двухвхохаовых сборок соединен через линию задержки со входом полусумматора, его выход - со вторым входом этой сборки, второй же вход полусумматора - через другую сборку с обоими плечами триггера четности, на счетный вход которого.через сборку поступают сигналы реверса. На чертеже приведена схема счетчика, где блок А - счетный регистр, содержащий триггеры TI - Т „ функциональный коммутатор К, используемый для управления записью в разрядах счетчика от 2-го и выше, триггер четности 7о, а блок В - схема управления, содержащая две двухвходовые сборки ИЛИ и MJIHi, линию задержки Л.З. и полусумматор. Автоматическое исключение «ложного реверса нри единичных сбоях в любом из разрядов счетчика достигается за счет того, что триггер четности управляется не счетными импульсами, а сигналами, образующимися при правильных переключениях в триггерах регистра и подаваемыми на вход триггера четности 7(1 через сборки ИЛИ, ИЛ И 2, ИЛИ. При. этом счетные импульсы поступают с клеммы / на входы схем совпадения Яо и ЯоЧ управляемых сигналами с единичного и нулевого выходов триггера четности Го, и коммутируются в зависимости от режима работы (сложение или выч тание) и четности входных импульсов или на вход триггера TI первого разряда регистра, или на один из его остальных разрядов.

Реверс осуществляется подачей сигнала на клемму //.

Исключение «ложного реверса при сбое в триггере четности Го достигается введением в схему узла В. Сигнал о переключении, происшедшем в регистре, отводится дополнительно в замкнутую цепь обратной связи, содержашую линию задержки Л.З., со временем задержки, равным времени переключения триггера четности TO, и полусумматор 2, к одному из входов которого подключен выход задержки. Выход полусумматора соединен через сборки ИЛИ и ИЛИз со входом триггера четности. На второй вход полусумматора Е подаются сигналы переключения с обоих выходов триггера четности через сборку ИЛИ.

Легко проследить, что при сбое в одном из триггеров Ti, Т.2, ..., Г„ на выходе ИЛИ2 сигнал будет отсутствовать и триггер четности не изменит своего состояния. Следовательно, очередной счетный импульс вновь пройдет на тот разряд, в котором имел место сбой.

В случае сбоя в триггере четности по истечении времени, равного времени переключения триггера, сигнал возникает только на том входе полусумматора, который подключен к Л.З. Возникающий при этом на выходе полусумматора сигнал вторично воздействует на счетный вход триггера четности.

В обоих случаях теряется один счетный импульс. Однако структура предлагаемой схемы позволяет при необходимости легко подсчитывать потерянные за время счета импульсы и учитывать их по окончании счета.

Предмет изобретения

Реверсивный счетчик в коде Грея, содержащий регистр на триггерах со счетным входом и триггер четности, отличающийся тем, что, с целью исключения «ложного реверса при единичных сбоях в любом из триггеров счетчика, он содержит схему управления, выполненную на основе полусумматора, двух двухвходовых сборок, линии задержки и двух схем совпадения, один вход первой из схем совпадения, управляюш,ей триггером первого разряда, соединен с единичным выходом триггера четности, а второй - со входом счетчика и с первым входом другой схемы совпадения, второй вход которой соединен с нулевым выходом триггера четности, а его выходной сигнал используется для управления остальными разрядами счетчика, выходы триггеров всех разрядов счетчика объединены в обшую сборку, выход которой соединен через двухвходовые сборки со счетным входом триггера четности; выход одной из двухвходовых сборок соединен через линию задержки со входом полусумматора, выход которого соединен со вторым входом этой сборки; второй вход полусумматора соединен через другую сборку с обоими плечами триггера четности, на счетный вход которого через сборку поступают сигналы реверса.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU293256A1 |

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| Й СЧЕТЧИК В КОДЕ ГРЕЯ | 1965 |

|

SU167365A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК В КОДЕ ГРЕЯ | 1967 |

|

SU190662A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ЧИСЛОВЫХ ВЕЛИЧИН | 1965 |

|

SU167366A1 |

| УСТРОЙСТВО для ЭКСПРЕСС-ОЦЕНКИ СРЕДНЕГО ЗНАЧЕНИЯ ПЕРИОДОВ СЛУЧАЙНОГО ПРОЦЕССА | 1969 |

|

SU252732A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| ДВОИЧНЫЙ СЧЕТЧИК С КОНТРОЛЕМ ОШИБОК | 1973 |

|

SU363215A1 |

| Счетчик с контролем | 1983 |

|

SU1123106A1 |

| Генератор псевдослучайной последовательности | 1979 |

|

SU857984A1 |

Авторы

Даты

1965-01-01—Публикация