Известны (:уг.1маторы в коде Грея, содержащие регистры исходных чисел и регистр результата, 1 которых перед онерацией сложения определяется четкость младших разрядо слагаемых.

Предлагяеми сумматор отличается от известных тем, что пи содержит линии о феделеиии меглосгсй, состоящие из двух групп схем «И. Один из входов схемы «И первой rpynni.i соедипон нулевым выходом триггера данно1о |)а:1)1яда и с шлходом схемы «И второй группы со-ссдиего старшего разряда, другой вход с 1;ыходом схемы «И, подключенной к единичному выходу триггера данного разряд.- и к выходу схем-ы «И первой группы сосед.пего старшего разряда. Один из входов схемы «И второй группы соединен с нулевым выходом триггера данного разряда и с выходом схемы «И первой группы соседнего старшего разряда, другой вход - с единичным выходом трпг4-ера данного разряда и с выходом схемы «И второй группы соседнего старшего разряда, счётный вход каждого триггера регистра результата соединен выходом полусумматора соответственных разрядов слагаемых с выходом схемы «И, ijjnKCMpyioiueft сочетание признаког «нечетнечет, и с в,1ходом схемы «И, один вход которой подключен к единич{ ому выходу триггера pei-истра результата соседнего младн1его разряда, другой - к выходу схемы «И предыдущего разряда линии параллельного переноса. Один из входов схемы «И данного разряда линии параллельного переноса через

линию задержки соединен с выходом схемы «И, фиксирующей сочетание признаков. «нечет-нечет в данном разряде, другой - с выходом схемы «И линии параллельного переноса предыдущего разряда, выход схемы

«И параллельного переноса от старшего разря.аа регистра результата подключен к единичному входу триггера младшего разряда. Это позволяет повысить быстродействие сумматора.

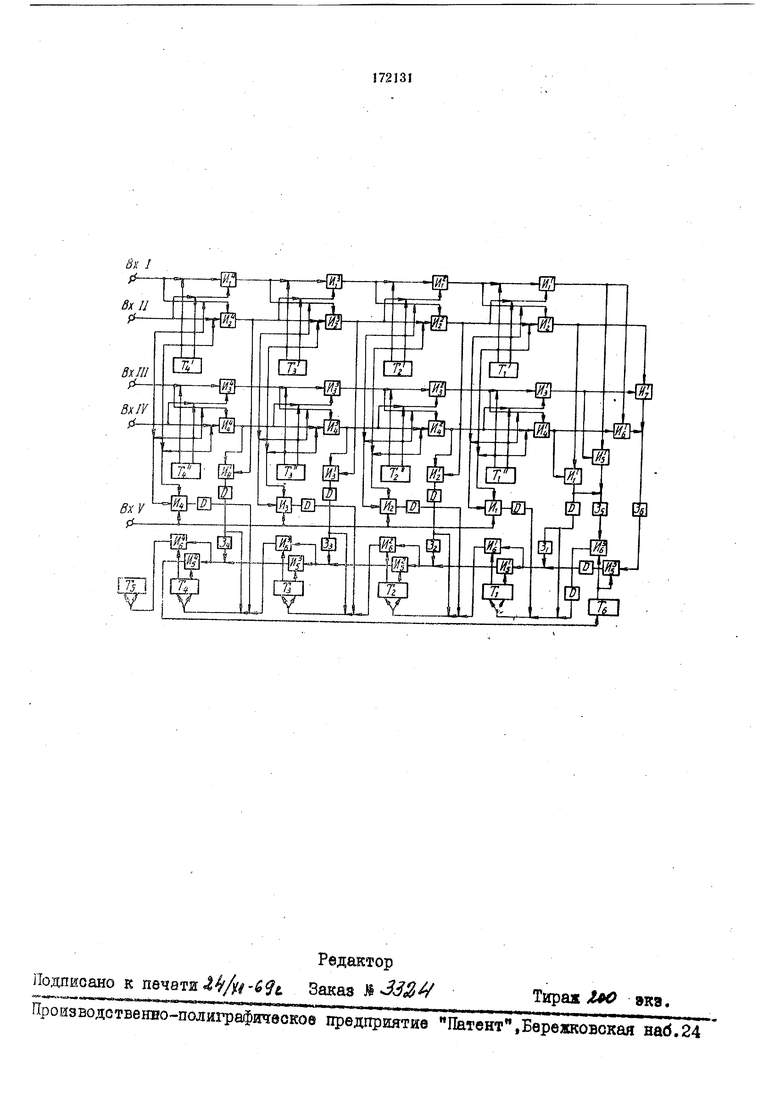

Принципиальная схема предлагаемого сумматора приведена на чертеже.

Сумматор выполнен на четыре разряда (число разрядов может бытьлюбым) и включает регистр исходного числа А, содержащий

триггеры , регистр исходного числа В, содержащий триггеры Г/-7, и регистр результата, содерл ащнй триггеры TI-TSДве группы вентилей MI-MI и ,, подключенные к выходам триггеров регистра исходного числа А, образуют .линию определения четпостеЛ разрядов таким образом, что четность данного разряда устанавливается по значению сигналов }га выходе вентиля данного ра.чряда группы //г-Яа.

Работа линии определения четиостей ра,;рядов числа А описывается следующими логическими выражениями;

группа

P:.(,)(Pi,.)rpviina //ii-Я -

p..(P,,(P(.,iVa,)

(Pj -iiCTKocTb данного разряда числа Л; (Pi + 1 - четность соседнего старшего разряда; uf -значение 1-го разряда числа). .

Две группы вентилей и , подключенные к выходам триггера регистра исходного числа В, образуют линию определения четностей разрядов таким образом, что четность данного разряда устанавливается по значению сигнала на выходе вентиля данного разряда групны .

Работа лил ИИ определения четностей разрядов числа -и описывается следующими логическ1;ми выражениями:

группа Я,41-Я,

: ,)()группа

(а:.., 11/6,) (gi + i Vb)

(qi -четность данного разряда числа; (//+ 1-четность соседнего старшего разряда; ft, -значение /-го разряда числа В).

Схемьг группы //j--И/ определяют поразрядпое сукмированне по модулю «два согласпо логике:

a,i)b,{a b -iaybj).

Pf езультат поразрядного суммирования вводится в регистр результата при подаче высокого потенциала на вход 1/.

Ячейки каждой линии определения четностей, -хемы поразрядного суммирования по модул-) «два, а также схемы совпадений группь , фиксирующие сочетания признакоз «нечет-нечет, - потенциального типа.

Вентили , подключенные к нулевым В1:,;ходам триггеров регистра результата, последовательно соединены между собой и образуют цепь параллельного переноса.

Вентил;: подключены к единичным выходам триггеров регистра результата и осуЕцсствляют прохождение импульсов перенос в соседний старший разряд.

Сигяэл от признака « ечет-нечет на выходе каждой ячейки Hii-И дифференцируется и поступает на счетный вход триггера данного ра:зряда регистра результата, а также чере:; o/uiy из задержек группы ,; - н цепь .. переиоса.

Схемь Mf,--Я- в управляются с единичных г,ых)Д()15 тригчероо jjerncTpa результата таким o6|;a30M, что импульс, ноступивьшй в цеги, параллельного переноса, проходит до той грушпл Я«1---Я,-, которой соотретcTiiyoT Tpnrjep, находящийся в состоянии «1.

носа соедипеп со входом установки единицы триггера Г«, Запоминающим появление единицы циклического переноса. Схемы И и Яз фиксируют однопменные сочетания индексов четности младших разрядов слагаемых, схемы Я;) и Ят - разноименные сочетания индексов четности младших разрядов слагаемых, необходимых для внесения коррекции в результат в случае появления едипицы циклического переноса.

Задержки 3 и 5е обеспечивают появление импульсов коррекции в цени параллельного переноса после срабатывания триггера младшего разряда от возможного сочетания признаков «нечет-нечет при наличии единиць циклического переиоса. Поэтому время задержек ЗЕ и 5а - t задержки переключения триггера.

В случае операции вычитания высокий потенциал подается либо на входы / и IV, либо на входы // и ///.

При подаче сигналов на входы / и iV инвертируется четность всех старших нулевых разрядов, предшеств ющих самому старшему зпачащему разря7-1;у числа В. При подаче сигнала на входы II и /// инвертируется четность всех старших нулевых разрядов, предшествующих самому старшему значащему разряду числа /1.

Работу всего устройства можно проследить яа следуюпдих примерах.

Г1 р и м ер i.

54321

-- +

А 0 I } О 9,

- + -f-f--f (); 15

00101 результат суммы слагаемых по модулю 2;

Г 1корректирующие переносы;

11101 первый промежуточный результат;

i1 корректирующие переносы;

-1 О О --окончательный результат.

Операция сложения начинается с нодачи Командного сигнала (высокий нотенциал) на вход V, в результате чего и регистр результата вводится результат поразрядного суммирования по модулю «два. В рассматриваемом примере в регистр резу,/п/гата вводится запись 00101.

По окончании этой операции па входы / и III подается высокий потенциал, озпачаюпиш операцию сложения, в результате чего мачипают работу липни определе.чия четноCTeii разрядо) с.пагаемых.

ii):c.)Kiin {ютенциал с единичного выхода ({)a 7V и наличие сигнала на входе / ):/;. ловливзют ноянлеиие сигнала на выходе с -vii.i 1-1-) (на пыхрде схемы Яа сигнал отсутстпуот); высокий потенциал с единичного иыхола триггера Т./ и наличие высокого потеьи.иала па пходе /// --появление сигнала пй выходе схемы Я.Н, так что на обоих входах /-/4 имеем сигналы (оба разряда - «нечетные).

Продифференцированный сигнал на выходе , Яд поступает на счетный вход триггера регистра результата и перебрасывает его из состояния «О, установленного поразрядным суммированием по модулю «два, в состояние «Т. Одновременно с этим импульс от сочетания «нечет-нечет поступает в цепи нараллельного переноса. Так как на нулевом выходе триггера Tt к этому моменту времени устанавливается низкий потенциал, то схема H-,-i оказывается запертой, и импульс через схему Я,;- поступает на счетный вход триггера регистра результата, устанавливая в ifCM зйнись «Ь, Получаем первый промежуточным результат-- 11101.

Сигнал с выхода Яз поступает на вход Яг , управляемого единичным выходом триггера T-ji, таге что на выходе имеем высокий потенциал, сигнала же нет (данный разряд четный). Сигнал с выхода Я4 поступает на вход И.y, управляемого нулевым выходом триггера Г;,. Так как в Г., записан «О, на выходе; Я4 появляется сигнал (Яд заперт), фиксиругогций нечетгость данного разряда. Вгледстпгте того, что на один из входов схе,, H;i приложен высокий потенциал, а на Л|;уголг кет, то нет сигнала и на выходе схем;, Я; и результат суммирования по модулю «два в данном разряде остается без измсиегия.

шлсокого потегщиала с нулевого иыхода триггера обеспечивает прохожде уне сиг)1ала через схему /,2 (Яа заперт}, так что RTopoi разряд числа А также будет четпым. Rf.rcoKini потеггциал с пулевого выхода триггера /U обеспечивает прохождение сигнала через схему Я. (Яд2 заперт). На выходе схем1, //о1 нет сигнала, и ре зультат сумлп1ро аиия по модулю «два в данном разряде остается без изменения.

Высокий потенциал единичного выхода триггера Т, обеспечивает прохождение сигнала через схему И-. так что первый разряд регистра /1 оказ1,1пается нечетным; вместе с -)гим пысокпй потенциал с нулевого выхода триперл Г|1 отпирает схему И.,. Первый разряд регистпа В также нечетнг,1Й и па выходе слем,г Я|1 возникает сигнал сочетания мризиакои «-нечет-нечет, который через дифiieieiiui pvir)mvio цепочку ггоступает на счетin, нход Т, триггера результата п перебрае,1пает его из состояния «1, устапоплепного поразрядным суммированием по модулю цпа. Г) состоицие «О.

Вслед за этим через линию задержки 3i импульс от сочетания признаков «нечет-нечет поступает в линию параллельного переноса, а затем, последовательно пройдя схемы И

и Яб- - на вход схемы Яв«, которая оказывается отпертой (триггер Гз в состоянии «1). Одновременно с этим дальнейшее распространение импульса в цепи параллельного переноса прекращается, так как схема Яв заперта.

Импульс на выходе схемы Яо поступает на счетный вход триггера Т регистра ре- зультата и перебрасывает его нз состояния «1 в состояние «О.

Окончательная запись в регистре результата - 10100(24), что соответствует истине.

Пример 2.

Вычитание

54321

+ -ь--+

1 1 1-10,

+ + +

В.-0 1 о 1

: О О О 1 -окончательный результат.

Операция вычитания также начинается с

подачи командного сигнала {высокий потенциал) на вход V введением в регистр результата поразрядного суммирования по модулю «два. В данном случае в регистр результата вводится запись 00100.

К моменту окончания этой операции на входы // и /Я подается .высокий потенциал операции вычитания, при этом инвертируется четность всех старших нулевых разрядов, предшествующих самому старщему значащему разряду числа А.

Высокий потенциал с единичного выхода триггера fi регистра А отпирает схему HI, и сигнал со входа // проходит через схему Я). Сигнал на выходе схемы HZ отсутствует,

поэтому четвертый разряд числа 4 оказывается четпым. Высокий потенциал с единичного выхода триггера 4 и наличие сигнала на входе Я/ обусловливают появление сигнала на выходе схемы И. Так как на выходе схена выходе схемы , позтому результат суммирования по модулю «два в данном разряде остается без изменения. Далее сигнал на выходе схемы Яг проходит через схему Яа, а сигнал на выходе схемы Й4 - через схему И, так что сигналы присутствуют на обоих входах схемы Яз (оба разряда -- нечетные). Продифференцированный сигнал на выходе схемы Яз поступает на счетный рход триггера Т и перебрасывает его КЗ состояния «1, установленного поразрядным суммированием по модулю «два, в состояние «О. Одновременно с этим импульс от сочетания признаков «нечет-нечет через линию задержки Зз поступает в цепь параллельного переноса и, последовательно пройдя через схемы Яз и , - на вход установки «1 триггера Ге, запоминающего появление единицы циклического переноса. Получаем первый промежуточный результат - ООООО-ьединица циклического переноса. Во втором разряде сигналы появляются на в ходах схем И и Яз и результат суммирования по модулю «два в данном разряде регистра результата остается без изменения. В нервом разряде сигналы появляются на выходах схем HI и Я, что соответствует сочетании.; признаков «нечет-нечет. Импульс от сочетания признаков «нечет-нечет в рассматриваемом разряде на счетный вход триггера А регистра результата (триггер перебрасывается в состояние «1), а затем через схему Я((1 - на счетный вход триггера Гв, в ре::у. чего в Т записывается единица. Одновременно с этим сигнал с выхода схемы //ji, пройдя через задержку 35, поступает на одич из входов схемы Яцо. Так как триггер Те находится в состоянии «I, го сигнал проходит ссему J/fiK, дифференцируется на его выходе и поступает на счетный вход триггера Ti, еноиа леребрасывая его в состояние «О, Оконнате.1гьиая запись в регистре результата- 00010 (3), что соответствует истине. Предмет изобретения Сумматор в коде Грея, содержащий регистры исходных чисел и регистр результата, отличающийся тем, что, с целью повышения быстродействия, он содержит линии определения четностей, состоящие из двух групп схем «И, один из входов схемы «И первой группы соединен с нулевым выходом триггера данного разряда и ,с выходом схемы «И второй группы соседнего старшего разряда, другой вход - с выходом схемы «И, подключенной к единичному выходу триггера данного разряда и к выходу схемы «И первой группы соседнего старшего разряда, один из входов схемы «И второй группы соединен с нулевым выходом триггера данного разряда и с выходом схемы «И первой группы соседнего старшего разряда другой вход - с единичным выходом триггера данного разряда ,и с выходом схемы «И второй грунны соседнего старшегоразряда, счетный вход каждого триггера регистра результата соединен выходом полусумматора соответственных разрядов cjiaraeMbix с выходом схемы «И, фиксирующей сочетание признаков «нечет-нечет, и с выходом схемы «И, один вход которой подключен к единичному выходу триггера регистра результата соседнего младшего разряда, другой - к выхо.г5,у схемы «И предыдущего разряда линии параллельного переноса, один из входов схемы «И данного разряда л.чй1-;и параллельною переноса через линию задержки соединен с выходом схемы «И, фиксирующей сочетание признаков «нечет-нечет в данном разряде, другой - с выходом схемы «И линия параллельного переноса предыдущего разряда, выход схемы «И параллельного переноса от старшего разряда регистра результата подключен к единичному входу триггера младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР С ФИКСАЦИЕЙ ОШИБКИПЕРЕНОСА | 1968 |

|

SU208338A1 |

| Устройство для сложения | 1974 |

|

SU525088A1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1966 |

|

SU223462A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Двоичный счетчик с контролем ошибок | 1972 |

|

SU448469A1 |

Даты

1965-01-01—Публикация