1

(21)4754921/09 (22)30.10.89 (46)15.12.91. Бюл. №46

(71)Рязанский радиотехнический институт

(72)В.В.Авдеев, Э.В.Будин, И.Ю.Садомский и Б.И.Филимонов (53)621.396.82(088.8)

(56)Авторское свидетельство СССР № 1494225, кл, Н 04 В 1/10, 1987.

(54) УСТРОЙСТВО ПОДАВЛЕНИЯ РА- ДИОИМПУЛЬСНЫХ ПОМЕХ

(57)Изобретение относится к радиотехнике и может быть использовано для обеспечения помехоустойчивого приема в радиоприемных устройствах различного назначения. Цель изобретения - уменьшение некомпенсированных остатков радиоимпульсных помех с протяженными фронтами и внутриимпульсными скачкообразными изменениями огибающей. Устройство подавления .радиоимпульсных помех содержит амплитудный детектор 1. второй элемент 2 задержки, первый блок 3 выборки и хранения, первый вычмтатель 4. сглаживающий фильтр 5, модулятор 6, коммутатор 7, первый элемент 8 задержки, пороговый блок 9 формирования импульса управления коммутатором, подстраиваемый по частоте и фазе генератор 10, блоки tl.t-II.N ,гискретного формирования уровня компенсирующего напряжения, аторые элементы 12.1-12.N задержки, мультиплексор 53, первый компаратор 14, ёлок 15 автоматического выбора рабочего канала. Формирование уровня компенсирующего напряжения в устройстве осуществляется адаптивной многоканальной схемой,, позволяющей исключить возможность подзвленхч полезного сигнала на выходе устройства. 2 э.п.ф-лы, 5 ил.

(Л

С

Вход

Os

чэ

00

чэ ю

vg

Выход

Изобретение относится к радиотехнике и может быть использовано для обеспечения помехоустойчивого приема в радиоприемных устройствах различного назначения. Цель изобретения - уменьшение нескомпенсированных остатков радиоимпульсных помех с протяженными фронтами и внутриимпульсными скачкообразными изменениями огибающей.

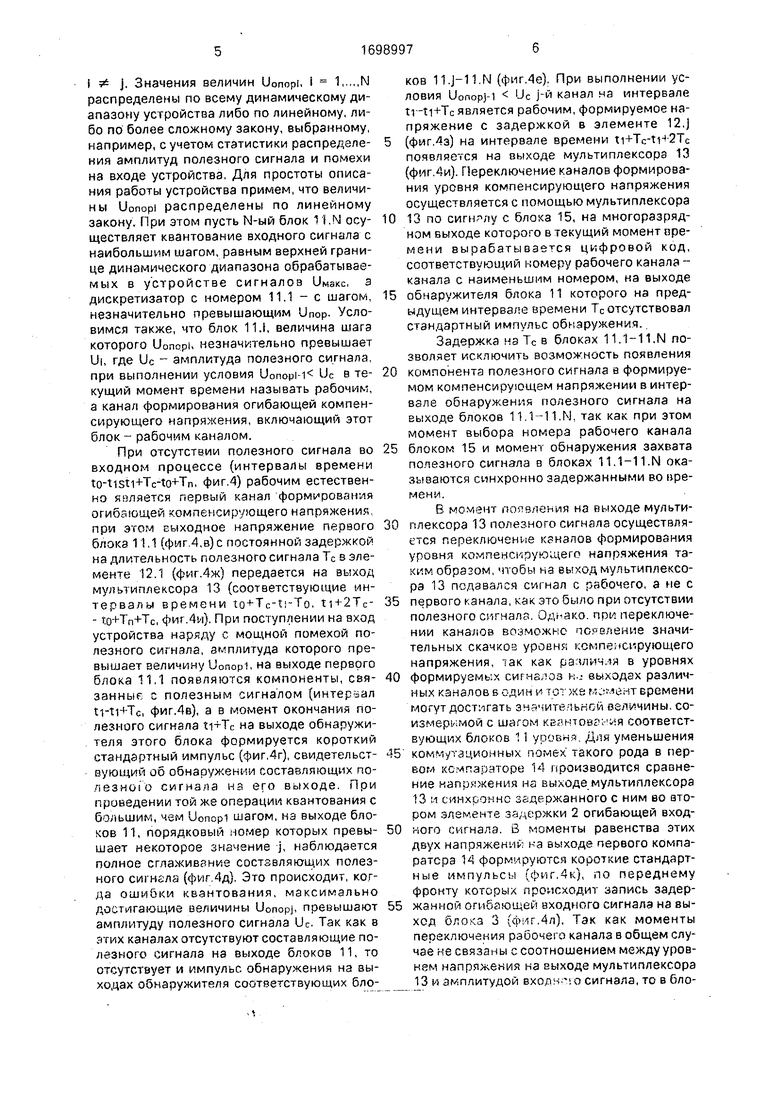

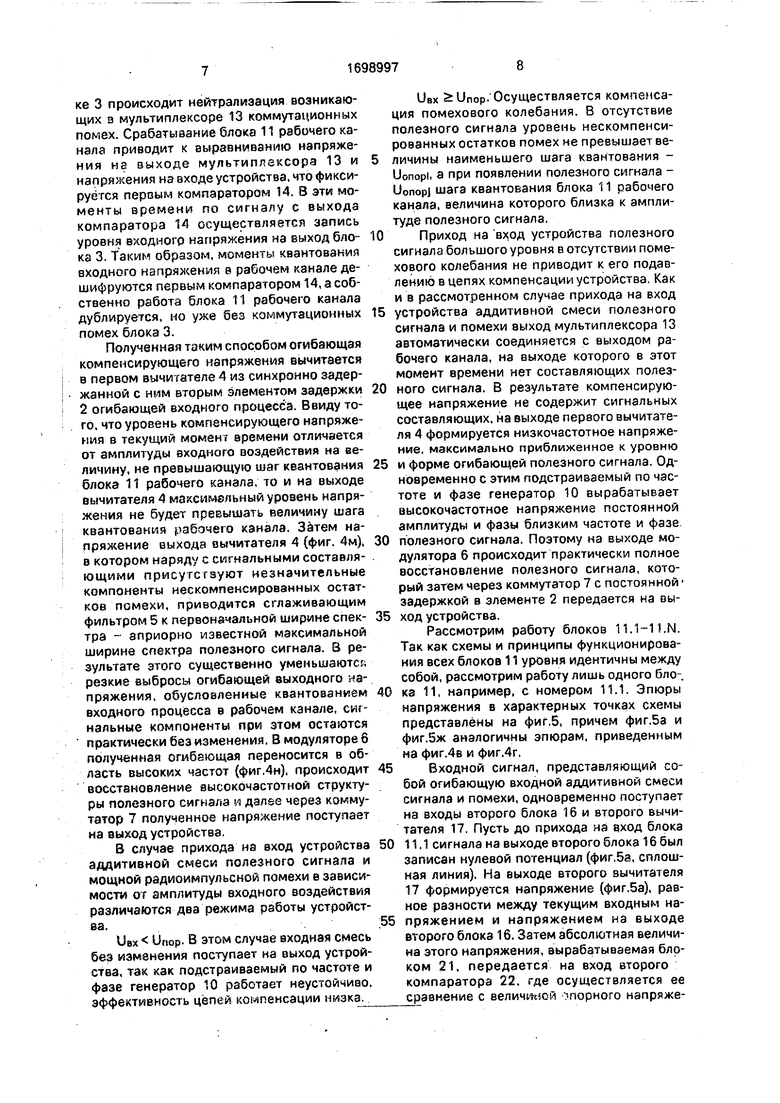

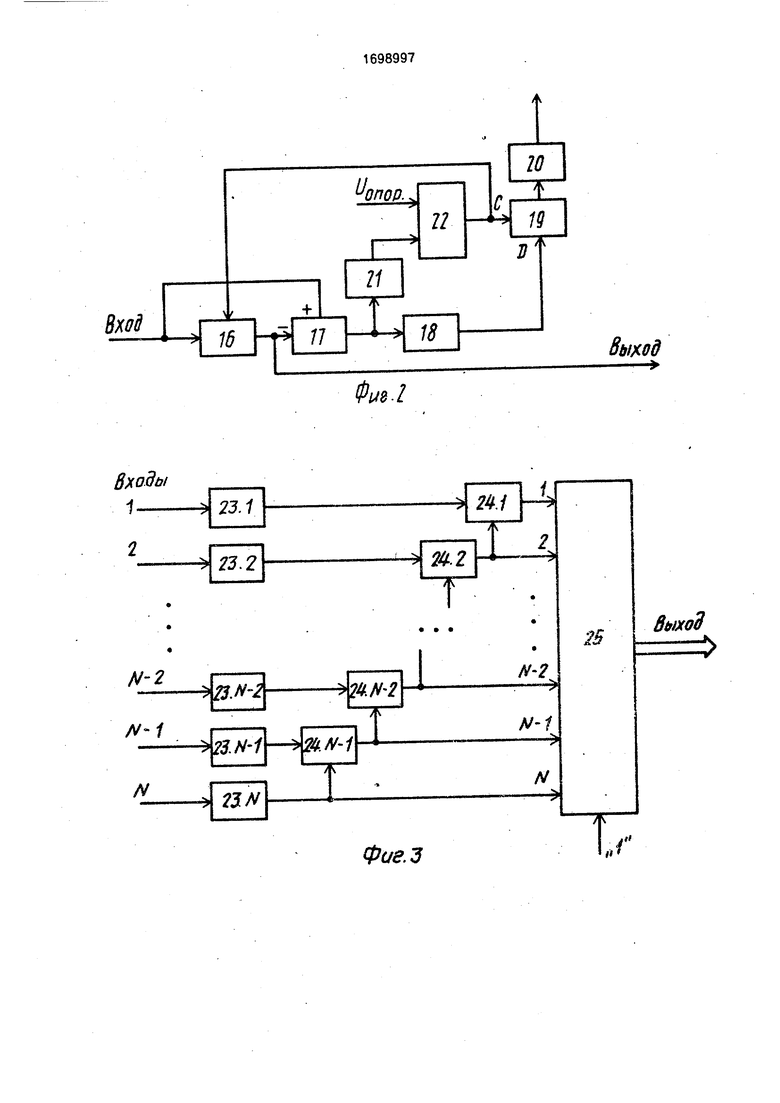

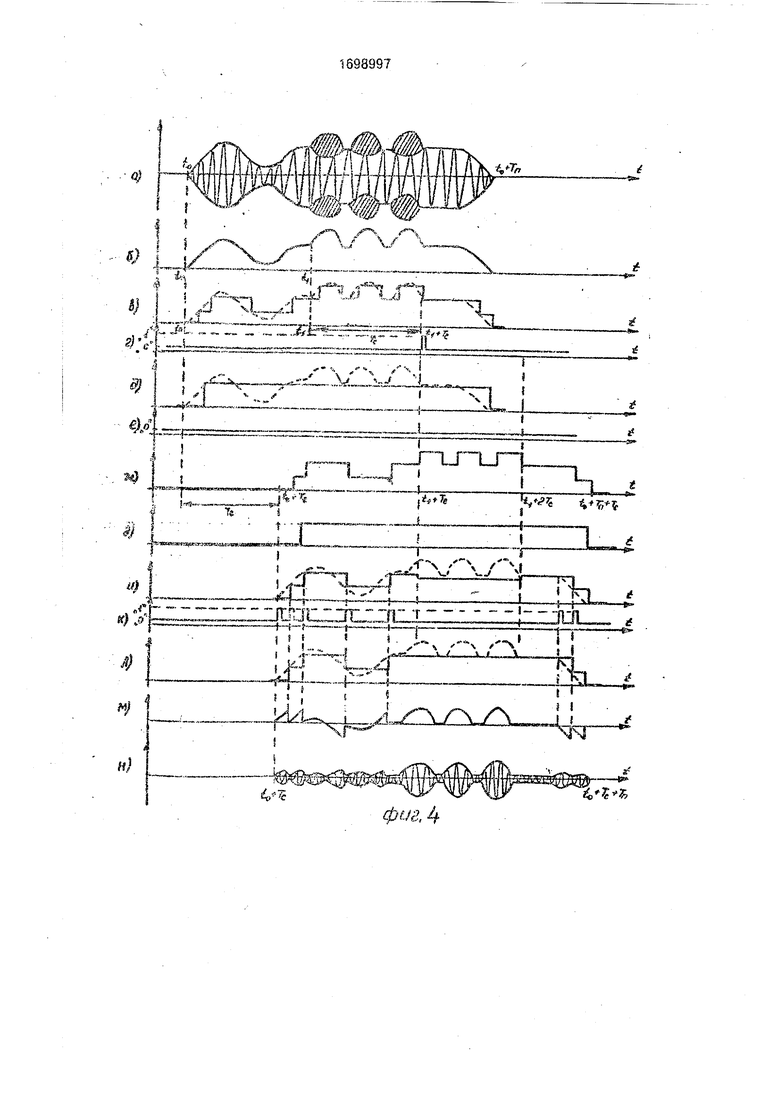

На фиг.1 представлена структурная электрическая схема устройства подавления радиоимпульсных помех; на фиг.2 - структурная электрическая схема блока дискретного формирования уровня компенсирующего напряжения; на фиг.З - структурная электрическая схема блока автоматического выбора рабочего канала; на фиг.4 - эпюры напряжений, поясняющие работу устройства.

Устройство подавления рздиоимпульс- ных помех содержит амплитудный детектор 1 второй элемент 2 задержки, первый блок 3 выборки и хранения, первый вычитатель 4, сглаживающий фильтр 5, модулятор 6, коммутатор 7, первый элемент 8 задержки, пороговый блок 9 формирования импульса управления коммутатором, подстраиваемый по частоте и фазе генератор 10, блоки 11. t-11 .N дискретного формирования уровня компенсирующего напряжения, вторые элементы 12.1-12.fsi задержки, мультиплексор 13, первый компаратор 14, блок 15 автоматического выбора рабочего канала.

Блок 11 дискретного формирования уровня компенсирующего напряжения содержит второй блох 16 выборки и хранения. Второй вычитатель 17, детектор 18 знака, D-триггер 19, обнаружитель 20 полезного сигнала, блок 21 формирования модуля сигнала, второй компаратор 22.

Блок 15 автоматического выбора рабочего канала содержит N расширителей 23.1-23.N сигнала, N-1 ключей 24.1-24.N-1, параллельный сумматор 25.

Устройство работает следующим образом.

Пусть на вход устройства поступает аддитивная смесь полезного сигнала некоррелированной с ним помехи и шума. Сигнал представляет собой амплитудоманипулиро- ванную последовательность радиоимпульсов длительностью Тс с внутриимпульсной модуляцией по частоте и (или) фазе. Помеха представляет собой радиоимпульс длительности Тп с постоянной несущей частотой, либо радиоимпульс с внутриимпульсной модуляцией по частоте и (или) фазе, либо квазигармоническое колебание, модулированное по амплитуде и фазе (частоте) по случайному закону. Предполагается, что шумы ввиду своей малости не вызывают срабатывания порогового блока 9, поэтому не оказывается влияния на принцип действия устройства и в дальнейшем изложении не

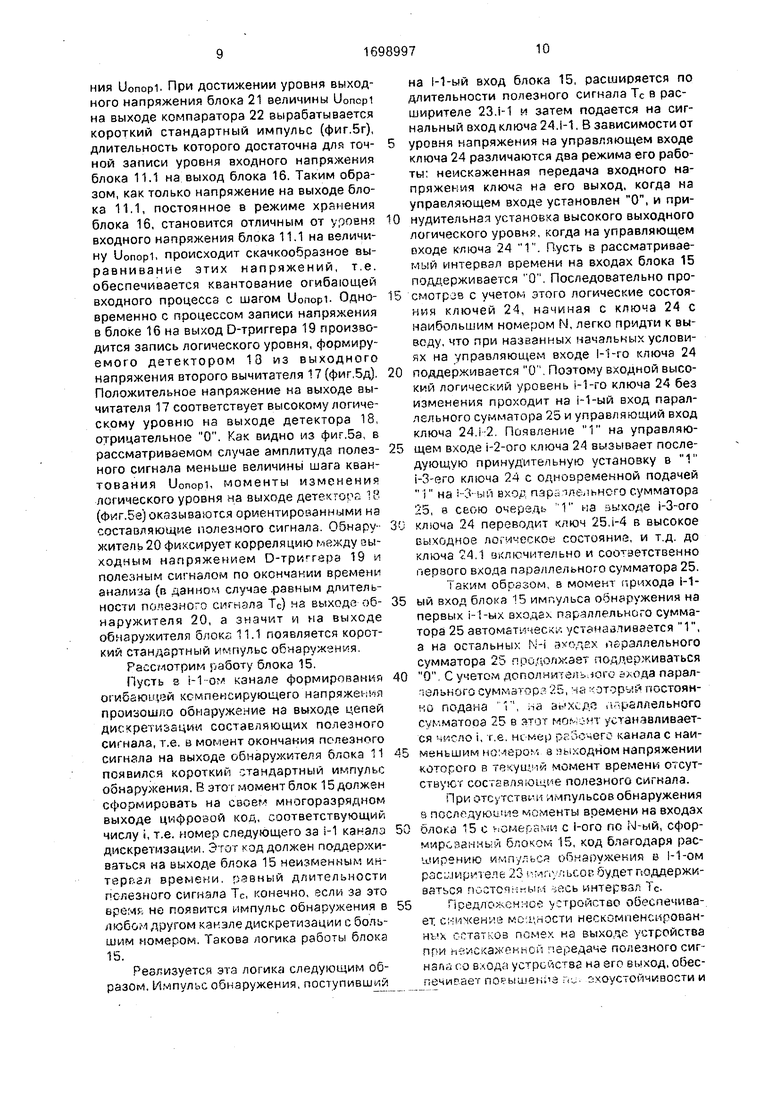

учитываются. Параметры сигнала и помехи: задержка во времени, амплитуда (мощность), начальная фаза полагаются неизвестными (случайными) величинами. Входное воздействие без учета шумовых составляющих представлено на фиг.4а. Штриховкой условно показано возникновение биений на участках, где полезный сигнал и помеха перекрываются во времени. На выходе элемента 8 это напряжение повторяется

практически без искажений с задержкой времени на Т3ад. Пока напряжение на выходе элемента 8 11Вых не превышает Unop - уровня входного сигнала, необходимого для устойчивой работы подстраиваемого по частоте и фазе генератора 10 - пороговый блок 9 поддерживает на своем выходе низкий логический уровень. О на выходе порогового блока 9 соответствует устойчивому состоянию коммутатора 7, при котором выход коммутатора 7 соединен с его нижним по схеме (фиг.1) входом. Таким образом, пока Uex Unop, входной сигнал без изменений с постоянной задержкой в первом элементе 8 через коммутатор 7 передается на выход

устройства. При превышении входным напряжением порогового уровня Unop пороговый блок 9 формирует на своем выходе высокий логический уровень, при котором выход коммутатора 7 оказывается соединенным с его верхним по схеме (фиг.1) входом, а входной сигнал с постоянной задержкой в элементе 8 через соединенные последовательно подстраиваемый по частоте и фазе генератор 10, модулятор 6 и ком-.

мутатор 7 поступает на выход устройства. В этом режиме работы устройства подстраиваемый по частоте и фазе генератор 10 вырабатывает квазигармоническое колебание постоянной амплитуды с частотой и фазой, близкими к частоте и фазе доминирующей компоненты задержанного в элементе 8 входного процесса, а модулятор 6 осуществляет перенос напряжения - свободной от помеховых составляющих огибающей входного сигнала - в область высоких частот.

Амплитудный детектор 1 выделяет огибающую входной аддитивной смеси полез- ного сигнала и помехи (фиг.4б), которая затем квантуется по уровню в N параллельно работающих блоках 1.11-11.IM. Каждый -ый блок 11.1 осуществляет квантование входного сигнала с постоянным шагом Uonopi. причем Uonopi - Uonopj. где i.j 1N;

i j. Значения величин Uonopi, i 1N

распределены по всему динамическому диапазону устройства либо по линейному, либо по более сложному закону, выбранному, например, с учетом статистики распределе- ния амплитуд полезного сигнала и помехи на входе устройства. Для простоты описания работы устройства примем, что величи- ны Uonopi распределены по линейному закону. При этом пусть N-ый блок 11.N осу- ществляет квантование входного сигнала с наибольшим шагом, равным верхней границе динамического диапазона обрабзтывае- мых в устройстве сигналов Умакс, э дискретизатор с номером 11.1 - с шагом, незначительно превышающим Упор. Условимся также, что блок 11.1, величина шага которого Uonopi, незначительно превышает Ui, где Uc амплитуда полезного сигнала, при выполнении условия U0nopi-i Uc в те- кущий момент времени называть рабочим, а канал формирования огибающей компенсирующего напряжения, включающий этот блок - рабочим каналом.

При отсутствии полезного сигнала во входном процессе (интервалы времени to-tisti+Tc-to+Tn, фиг.4) рабочим естественно является первый канал формирования огибающей компенсирующего напряжения, при этом выходное напряжение первого блока 11.1 (фиг.4,а)с постоянной задержкой на длительность полезного сигнала Тс в элементе 12.1 (фиг.4ж) передается на выход мультиплексора 13 (соответствующие интервалы времени to + Tc-t:-To, ti + 2Tc- - to+Tn+Tc, фиг.4и). При поступлении на вход устройства наряду с мощной помехой полезного сигнала, амплитуда которого превышает величину Uonopi, на выходе первого блока 11.1 появляются компоненты, свя- занные с полезным сигналом (интервал ti-ti- -Tc, фиг.4в), а в момент окончания полезного сигнала ti+Tc на выходе обнаружителя этого блока формируется короткий стандартный импульс (фиг.4г), свидетельст- вующий об обнаружении составляющих по- лезно О сигнала из его выходе. При проведении той же операции квантования с большим, чем Uonopi шагом, на выходе блоков 11, порядковый номер которых превы- шает некоторое значение , наблюдается полное сглаживание составляющих полезного сигнала (фиг.4д). Это происходит, когда ошибки квантования, максимально достигающие величины Uonopj, превышают амплитуду полезного сигнала Uc. Так как в этих каналах отсутствуют составляющие полезного сигнала на выходе блоков 11, то отсутствует и импульс обнаружения на выходах обнаружителя соответствующих блоков 11.J-11.N (фиг.4е), При выполнении условия Uonopj-i Uc j-й канал на интервале ti ti+Tc является рабочим, формируемое напряжение с задержкой в элементе 12.j (фиг.4з) на интервале времени ti+Tc-ti-i-2Tc появляется на выходе мультиплексора 13 (фиг.4и). Переключение каналов формирования уровня компенсирующего напряжения осуществляется с помощью мультиплексора 13 по сигналу с блока 15, на многоразрядном выходе которого в текущий момент вре- мени вырабатывается цифровой код, соответствующий номеру рабочего канала - канала с наименьшим номером, на выходе обнаружителя блока 11 которого на предыдущем интервале времени Тс отсутствовал стандартный импульс обнаружения.

Задержка на Тс в блоках 11.1-11.N позволяет исключить возможность появления компонента полезного сигнала а формируемом компенсирующем напряжении в интервале обнаружения полезного сигнала на выходе блоков 11.1-11.N, так как при этом момент выбора номера рабочего канала блоком 15 и момент обнаружения захвата полезного сигнала в блоках 11.1-11.N оказываются синхронно задержанными во времени.

В момент появления на выходе мультиплексора 13 полезного сигнала осуществляется переключение каналов формирования уровня компенсирующего напряжения таким образом, чтобы на выход мультиплексора 13 подавался сигнал с рабочего, а не с первого канала, как это было при отсутствии полезного сигнала. Однако, при переключении каналов возможно появление значительных скачков уровня шмпе; сирующего напряжения, так как раплич.чя в уровнях формируемых сигналов к- выходах различных каналов в один и тег же г- -мент времени могут достигать значительней величины, соизмеримой с шагом квантов ;- ия соответствующих блоков 11 уровня. Для уменьшения коммутационных помех такого рода в первом компараторе 14 производится сравнение напряжения на выходе мультиплексора 13 и синхронно задержанного с ним во втором элементе задержки 2 огибающей входного сигнала. В моменты равенства этих двух напряжений на выходе первого компа- ратсра 14 формируются короткие стандартные импульсы (фиг.4к), ло переднему фронту которых происходит запись задержанной огибающей входного сигнала на выход блока 3 (фиг.4л), Так как моменты переключения рабочего канала в общем случае не связаны с соотношением между уровнем напряжения на выходе мультиплексора 13 w амплитудой входною сигнала, то в блоке 3 происходит нейтрализация возникающих в мультиплексоре 13 коммутационных помех. Срабатывание блока 11 рабочего канала приводит к выравниванию напряжения на выходе мультиплексора 13 и напряжения на входе устройства, что фиксируется пероым компаратором 14. В эти моменты времени по сигналу с выхода компаратора 14 осуществляется запись уровня входного напряжения на выход блока 3. Таким образом, моменты квантования входного напряжения в рабочем канале дешифруются первым компаратором 14, а собственно работа блока 11 рабочего канала дублируется, ио уже без коммутационных помех блока 3.

Полученная таким способом огибающая компенсирующего напряжения вычитается в первом вычитателе 4 из синхронно задержанной с ним вторым элементом задержки 2 огибающей входного процесса. Ввиду того, что уровень компенсирующего напряжения в текущий момент времени отличается от амплитуды входного воздействия на величину, не превышающую шаг квантования блока 11 рабочего канала, то и на выходе вычитателя 4 максимальный уровень напряжения ке будет превышать величину шага квантования рабочего канала. Затем напряжение выхода вычитателя 4 (фиг. 4м), в котором наряду с сигнальными составляющими присутствуют незначительные компоненты нескомпенсированных остатков помехи, приводится сглаживающим фильтром 5 к первоначальной ширине спектра - априорно известной максимальной ширине спектра полезного сигнала. В результате этого существенно уменьшаются резкие выбросы огибающей выходного напряжения, обусловленные квантованием входного процесса в рабочем канале, сигнальные компоненты при этом остаются практически без изменения. В модуляторе 6 полученная огибающая переносится в область высоких частот (фиг.4н), происходит восстановление высокочастотной структуры полезного сигнала и далее через коммутатор 7 полученное напряжение поступает на выход устройства.

В случае прихода на вход устройства аддитивной смеси полезного сигнала и мощной радиоимпульсной помехи в зависимости от амплитуды входного воздействия различаются два режима работы устройства.

UBX Unop. В этом случае входная смесь без изменения поступает на выход устройства, так как подстраиваемый по частоте и фазе генератор 10 работает неустойчиво, эффективность цепей компенсации низка.

UBX 2: Unop. Осуществляется компенсация помехового колебания. В отсутствие полезного сигнала уровень нескомпенсированных остатков помех не превышаетвеличины наименьшего шага квантования - Uonopi, а при появлении полезного сигнала - Uonopj шага квантования блока 11 рабочего канала, величина которого близка к амплитуде полезного сигнала.

0 Приход на вход устройства полезного сигнала большого уровня в отсутствии помехового колебания не приводит к его подавлению в цепях компенсации устройства. Как и в рассмотренном случае прихода на вход

5 устройства аддитивной смеси полезного сигнала и помехи выход мультиплексора 13 автоматически соединяется с выходом рабочего канала, на выходе которого в этот момент времени нет составляющих полез0 ного сигнала. В результате компенсирующее напряжение не содержит сигнальных составляющих, на выходе первого вычитателя 4 формируется низкочастотное напряжение, максимально приближенное к уровню

5 и форме огибающей полезного сигнала. Одновременно с этим подстраиваемый по частоте и фазе генератор 10 вырабатывает высокочастотное напряжение постоянной амплитуды и фазы близким частоте и фазе.

0 полезного сигнала. Поэтому на выходе модулятора 6 происходит практически полное восстановление полезного сигнала, который затем через коммутатор 7 с постоянной - задержкой в элементе 2 передается на вы5 ход устройства.

Рассмотрим работу блоков 11.1-11.N. Так как схемы и принципы функционирования всех блоков 11 уровня идентичны между собой, рассмотрим работу лишь одного бло-.

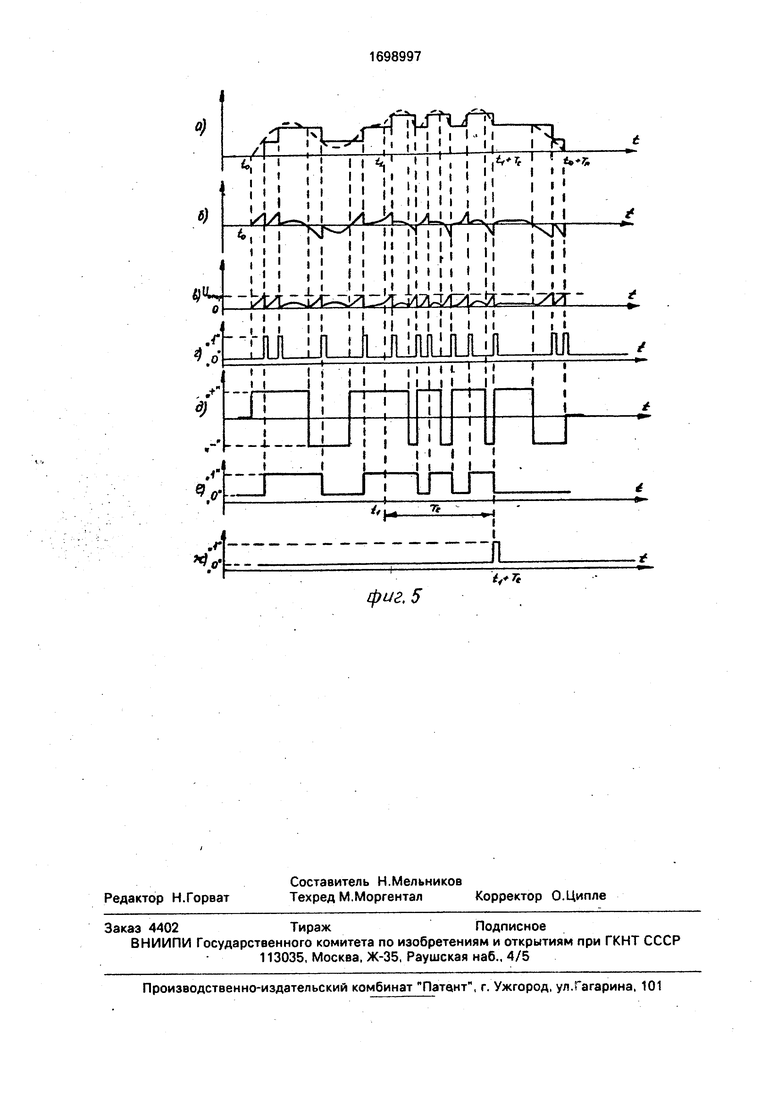

0 ка 11, например, с номером 11.1. Эпюры напряжения в характерных точках схемы представлены на фиг.5, причем фиг.Ба и фиг.бж аналогичны эпюрам, приведенным на фиг.4в и фиг.4г.

5 Входной сигнал, представляющий собой огибающую входной аддитивной смеси сигнала и помехи, одновременно поступает на входы второго блока 16 и второго вычитателя 17. Пусть до прихода на вход блока

0 11.1 сигнала на выходе второго блока 16 был записан нулевой потенциал (фиг.ба, сплошная линия). На выходе второго зычитателя 17 формируется напряжение (фиг.ба), равное разности между текущим входным на5 пряжением и напряжением на выходе второго блока 16. Затем абсолютная величина этого напряжения, вырабатываемая блоком 21, передается на вход второго компаратора 22, где осуществляется ее сравнение с величиной опорного напряжения Uonopi. При достижении уровня выходного напряжения блока 21 величины Uonopi на выходе компаратора 22 вырабатывается короткий стандартный импульс (фиг.бг), длительность которого достаточна для точной записи уровня входного напряжения блока 11.1 на выход блока 16. Таким образом, как только напряжение на выходе блока 11.1, постоянное в режиме хранения блока 16. становится отличным от уровня входного напряжения блока 11.1 на величину Uonopi, происходит скачкообразное выравнивание этих напряжений, т е. обеспечивается квантование огибающей входного процесса с шагом Uonopi. Одновременно с процессом записи напряжения в блоке 16 на выход D-триггера 19 производится запись логического уровня, формируемого детектором 13 из выходного напряжения второго вычитателя 1(фиг.5д). Положительное напряжение на выходе вычитателя 17 соответствует высокому логическому уровню на выходе детектора 18, отрицательное О. Как видно из фиг,5а, в рассматриваемом случае амплитуда полезного сигнала меньше величины шага квантования Uonopi, моменты изменения логического уровня на выходе детектора 1 (фиг.Бе)оказываются ориентированными на составляющие полезного сигнала Обнаружитель 20 фиксирует корреляцию между аы- ходчым напряжением D-тритера 19 и полезным сигналом по окончании времени анализа (в данном случае равным длительности почезного сигнала Тс) на выходе обнаружителя 20, а значит и на выходе обнаружителя блокг. 111 появляется короткий стандартный импульс обнаружения

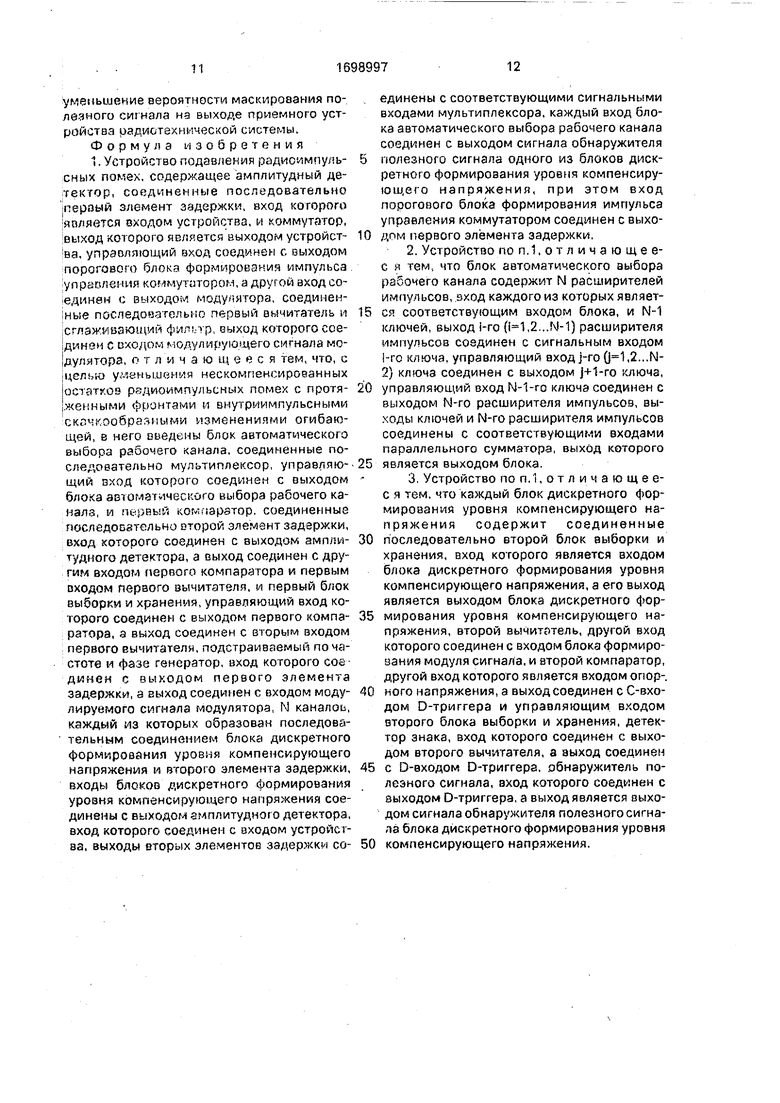

Рассмотрим работу блока 15.

Пусть s i-1 ov канале формирования огибающей компенсирующего напряжения произошло обнаружение на выходе цепей дискретизации составляющих полезного сигнала, т.е. в момент окончания полезного сигнала на выходе обнаружителя блока 11 появился короткий стандартный импульс обнаружения, В этот момент блок 15 должен сформировать на свеем многоразрядном выходе цифровой код, соответствующий числу I, т.е. номер следующего за 1-1 канала дискрет изации Э го г од должен поддерживаться на выходе блока 15 неизменным интервал времени равный длительности полезного сигнала Тс, 1 оиечно, если за это врем$ не появится импульс обнаружения в другом канале дискретизации с большим номером. Такова логика работы блока 15.

Реализуется эта логика следующим образом. Импульс обнаружения поступивший

на l-1-ый вход блока 15, расширяется по длительности полезного сигнала Тс в расширителе 23 i-1 и затем подается на сигнальный вход ключа 24.1-1. В зависимости от

уровня напряжения на управляющем входе ключа 24 различаются два режима его работы неискаженная передача входного напряжения ключа на его выход, когда на управляющем входе установлен О, и при0 нудительнат установка высокого выходного логического уровня, когда на управляющем входе ключа 24 1 Пусть в рассматриваемый интервал времени на входах блока 15 поддерживается О. Последовательно про5 смотрев с учетом этого логические состояния ключей 24, начиная с ключа 24 с наибольшим номером N, легко придти к выводу, что при названных начальных условиях на управляющем входе i-1-ro ключа 24

0 поддерживается О Поэтому входной высокий логический уровень (-1-го ключа 24 без изменения проходит на i-1-ый вход параллельного сумматора 25 и управляющий вход ключа 24 i 2 Появление 1 на управляю5 щем входе i-2-oro ключа 24 вызывает последующую принудитепьную установку в 1 i-3-его ключа 24 с одновременной подачей 1 на 1-3 ый вхоЈ пао 1ле/ ьного сумматора 25, в СБОЮ очередь 1 г-а аыходе i-3-ого

G ключа 24 переводит ключ 25 i-4 в высокое

выходное ло.мческоь состояние, и т д. до

ключа 74 1 зключительно и соответственно

первого влода параллельного сумматора 25.

Таким образом, в момент прихода 1-15 ый вход блока 15 имг.ульса обнаружения на первых i-1-ых входах параллельного сумматора 25 автоматически устанавливается 1, а на остальных N-I пЈраллельного сумматора 25 продолжает поддерживаться

0 О С учетом дополнитесь юго d/ода парал- г.ельного сумматор 5, -,« этора й постоянно подана Г , па ,ло параллельного С умматооа 25 в этот у анзаливается число i, г е не мер ргЗоепэ канала с наи5 меньшим но iepokc. а «ылодном напряжении которого в течущий момент времени отсутствуют составляющие полезного сигнала.

При отсутствии импульсов обнаружения в последующие моменты времени на входах

0 блока 15 с комеойми с i-oro по , сфор- ирозаннь-} блоком 15, код благодаря расширению имч/льср в 1-1-ом pQC,jnpi Te 16 23 пьсог б у дет поддерживаться пиотоя.тным ,есь интервал Тс.

5 Поедлочсн-юе устройство обеспечивает с ижекиэ моцносги нег-к.омпенсирован- HVX сстат оз помех на выхоцг устройства при н/искахеннсй передаче полезного сиг- нзпогз в 1,ода устройства на ею выход, обес- печисает повышение к- хоусгойчивостии

уменьшение вероятности маскирования полезного сигнала на выходе приемного устройства оадиотехнической системы. Формула изобретения 1. Устройство подавления радиоимпульсных помех, содержащее амплитудный детектор, соединенные последовательно пероый элемент задержки, вход которого является входом устройства, и коммутатор, выход которого является выходом устройства, управляющий вход соединен с выходом порогового блока формирования импульса управления коммутатором, а другой вход соединен с выходом модулятора, соединенные последовательно первый вычитатель и сглаживающий фильтр, выход которого соединен с сходен модулирующего сигнала модулятора, отличающееся тем, что, с целью ученый «ни я некомпенсированных остатков рядиоимпульсных помех с протяженными фронтами и внутриимпульсными скачкообразными изменениями огибающей, в него оведеиы блок автоматического выбора рабочего канала, соединенные последовательно мультиплексор, управляющий аход которого соединен с выходом блока автоматического выбора рабочего канала, и первый компаратор, соединенные последовательно второй элемент задержки, вход которого соединен с выходом амплитудного детектора, а выход соединен с другим входом первого компаратора и первым входом первого вычитзтеля, м первый блок выборки и хранения, управляющий вход которого соединен с выходом первого компаратора, а выход соединен с вторым входом первого вычитателя, подстраиваемый по частоте и фазе генератор, вход которого сое дмнен с выходом первого элемента задержки, а выход соединен с входом модулируемого сигнала модулятора, N каналов, каждый из которых образован последовательным соединением блока дискретного формирования уровня компенсирующего напряжения и второго элемента задержки, входы блоков дискретного формирования уровня компенсирующего напряжения соединены с выходом амплитудного детектора, вход которого соединен с входом устройства, выходы вторых элементов задержки соединены с соответствующими сигнальными входами мультиплексора, каждый вход блока автоматического выбора рабочего канала соединен с выходом сигнала обнаружителя

полезного сигнала одного из блоков дискретного формирования уровня компенсирующего напряжения, при этом вход порогового блока формирования импульса управления коммутатором соединен с выходом первого элемента задержки.

управляющий вход N-1-го ключа соединен с выходом N-ro расширителя импульсов, выходы ключей и N-ro расширителя импульсов соединены с соответствующими входами параллельного сумматора, выхйд которого

является выходом блока.

последовательно второй блок выборки и хранения, вход которого является входом блока дискретного формирования уровня компенсирующего напряжения, а его выход является выходом блока дискретного формирования уровня компенсирующего напряжения, второй вычитэтель, другой вход которого соединен с входом блока формирования модуля сигнала, и второй компаратор, другой вход которого является входом опор-.

ного напряжения, а выход соединен с С-вхо- дом D-триггера и управляющим входом второго блока выборки и хранения, детектор знака, вход которого соединен с выходом второго выч-итателя, а выход соединен

с D-входом D-триггера, обнаружитель полезного сигнала, вход которого соединен с выходом D-триггера, а выход является аыхо- v дом сигнала обнаружителя полезного сигнала блока дискретного формирования уровня

компенсирующего напряжения.

Входы

«W/

Фс/а.З

Tr

fСП

СП CO О)

со

JSFfcJI. Л

№

«%ч

«5

,S )

.1я

V.o.Г

)оI t

Tl

фиг, 5

Авторы

Даты

1991-12-15—Публикация

1989-10-30—Подача