Изобретение относится к области радиотехники, а именно к области техники радиосвязи и может быть использовано в составе радиоприемных устройств, предназначенных для приема широкополосных сигналов на фоне мощных, сосредоточенных в спектре сигнала, помех.

Известно устройство подавления помех, (см. например авт.св. СССР N 1338079, заявка N 4603676 от 09.11.88. опубл. 11. 1990 г.). Устройство содержит нелинейный преобразователь сигнала, дешифратор, счетчик, блок оперативной памяти, блок формирования управляющих импульсов, первый и второй буферные регистры, блок оценки второго начального момента распределения случайного процесса, квадратор, делитель, блок оценки четвертого начального момента распределения случайного процесса, аналого-цифровой преобразователь и генератор.

Работа этого устройства основана на определении эксцесс-параметра помехи, по которому адаптируется характеристика нелинейного преобразователя сигнала так, чтобы она была согласована с плотностью распределения помехи с вычисленным эксцессом.

Недостатком данного устройства подавления помех является низкая эффективность подавления мощных сосредоточенных в спектре сигнала помех, особенно если их структура близка к структуре принимаемого сигнала. В этом случае в нелинейном преобразователе возможно наряду с помехой подавление и полезного сигнала.

Известно также устройство для компенсации помех (см. например, авт.св. СССР N 1571774, заявка N 4315421 от 09.10.87. опубл. 09.1990 г.), содержащее первый и второй фильтры, первый и второй элементы задержки, вычитатель, обнаружитель помехи, детектор, пороговый элемент, импульсный генератор, регулируемый усилитель, блок определения амплитуды помехи, пиковый детектор со сбросом, элемент памяти.

В устройстве происходит линейная компенсация напряжений импульсной помехи, и результат поступает на выход устройства. Недостатком этого устройства для компенсации помех является возможность компенсации только импульсных помех, кроме того полоса частот принимаемого сигнала ограничена полосой пропускания входного полосового фильтра, а также в процессе компенсации помехи не учитывается уровень входного сигнала, что при воздействии на вход устройства мощных помех может привести к ложной компенсации полезного сигнала.

Наиболее близким аналогом к заявленному устройству (прототипом) по своей технической сущности является известное устройство компенсации импульсных помех (см. например, авт.св. СССР N 1619413, заявка N 4449356 от 23.06.88. опубл. 04.1991 г.). Устройство-прототип содержит первый и второй полосовые фильтры, генератор импульсов, вычитатель, элемент задержки, аналого-дискретный преобразователь, блок восстановления сигнала.

При этом входной сигнал одновременно подается на входы первого полосового фильтра, второго полосового фильтра и генератора импульсов, выход которого подключен к первому входу аналого-дискретного преобразователя, выход первого полосового фильтра подключен к первому входу вычитателя, выход второго полосового фильтра подключен к второму входу вычитателя, выход которого подключен к входу элемента задержки, выход которого подключен к второму входу аналого-дискретного преобразователя, выход которого подключен к входу блоку восстановления сигнала.

Подавление импульсной помехи достигается тем, что в аналого-дискретном преобразователе выборки берутся в моменты времени, когда сигнал на выходе вычитателя равен нулю. Полезный сигнал восстанавливается в блоке восстановления сигнала.

Недостатком этого устройства для компенсации помех является невозможность компенсации помех, сосредоточенных только в спектре сигнала и ограниченных полосой пропускания входного полосового фильтра, кроме того наличие постороннего сигнала в полосе пропускания второго фильтра приведет к ложной компенсации полезного сигнала.

Целью настоящего изобретения является разработка устройства компенсации помех, обладающего высокой эффективностью подавления мощных сосредоточенных в спектре широкополосного сигнала помех и обеспечивающее на выходе соотношение мощностей помехи и полезного широкополосного сигнала, близкое к единице с гарантированным сохранением мощности полезного сигнала.

Поставленная цель достигается тем, что в известное устройство компенсации импульсных помех, содержащее аналого-цифровой преобразователь (АЦП), вычитатель, элемент задержки, генератор импульсов, выход которого подключен к первому входу АЦП, дополнительно введены следующие элементы: триггер Шмитта, первая и вторая схемы сложения по модулю два, инвертор с расширением по выходу "ИЛИ-НЕ", инвертор и логическая схема "И". Выходы АЦП подключены к первым соответствующим входам вычитателя и часть из них дополнительно подключена к входам инвертора, выходы которого подключены к соответствующим вторым входам вычитателя. Один из выходов АЦП, кроме того, подключен к первому входу логической схемы "И". К второму входу логической схемы "И", и к первому входу элемента задержки подключен выход генератора импульсов. Выход логической схемы "И" подключен к входу инвертора с расширением по выходу "ИЛИ-НЕ", выход которого подключен к вторым соответствующим входам вычитателя. Дополнительно выход логической схемы "И" подключен к первому входу второго сумматора по модулю два. На второй вход последнего подключен выход триггера Шмитта, на вход которого подан входной сигнал. Выход второго сумматора по модулю два подключен к второму входу элемента задержки, выход которого подключен к первому входу первого сумматора по модулю два. На второй вход последнего подключен один из выходов вычитателя. Выход первого сумматора по модулю два и соответствующие выходы вычитателя подключены к выходу устройства.

Принцип создания предлагаемого устройства основан на использовании оценочно-непараметрического метода компенсации мощных помех. Названный метод базируется на априорном знании лишь предельных амплитудных значений реализаций сигнала, что вполне реально для каналов с постоянными параметрами. Алгоритм квазикомпенсации мощных сосредоточенных в спектре сигнала помех базируется на грубом отслеживании уровня помехи по мгновенным отсчетам аналого-цифрового преобразователя и вычитании из значения точного отсчета уровня аддитивной смеси сигнала и помехи, значения грубой оценки уровня помехи. Функционирование устройства можно сравнить с работой ограничителя со следящим порогом ("окном"), когда порог с заданной погрешностью отслеживает средний уровень огибающей помехи.

Такое построение устройства, в отличии от прототипа, где компенсация импульсных помех достигается за счет сравнения значений входного процесса на выходах полосового фильтра полезного сигнала и фильтра, отстроенного по частоте, и взятием выборок в аналого-дискретном преобразователе в моменты, когда результат сравнения равен нулю, обладает следующим преимуществом. Повышается возможность по видам компенсируемых помех, исключается ложная компенсация полезного сигнала вследствии отсутствия второго канала приема и обеспечивается гарантированное сохранение мощности полезного сигнала с сведением соотношения мощностей помехи и полезного сигнала на его входе, значительно превосходящего единицу, к значению близкому к единице (сверху) на выходе с точностью, обеспечиваемой параметрами аналого-цифрового преобразователя.

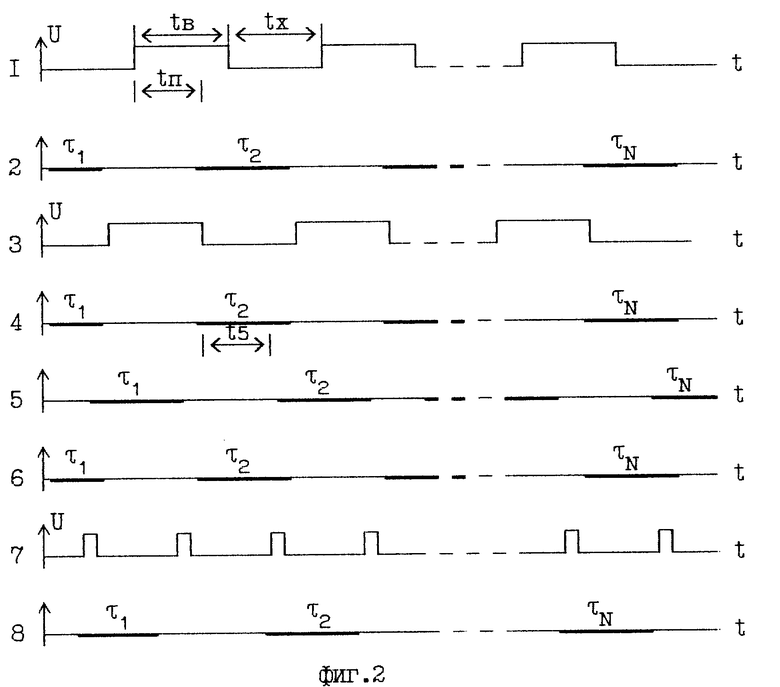

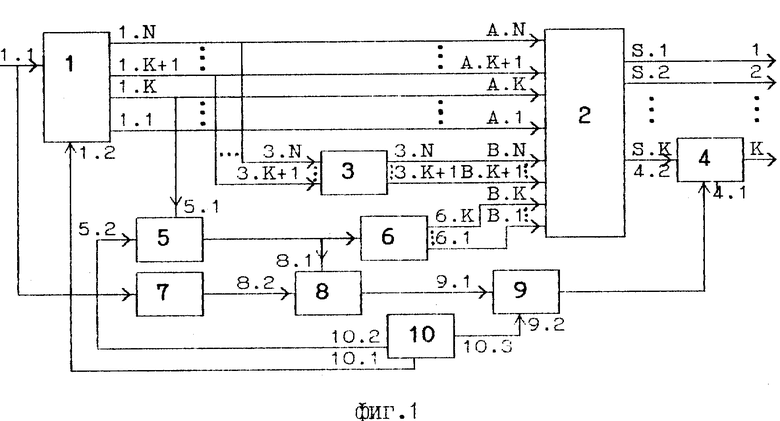

На фиг. 1 приведена общая функциональная схема устройства компенсации помех; на фиг. 2 временные диаграммы работы блоков устройства компенсации помех.

Устройство компенсации помех, показанное на фиг.1, содержит аналого-цифровой преобразователь 1, вычитатель 2, инвертор 3, первый сумматор по модулю два 4, логическую схему "И" 5, инвертор с расширением по выходу "ИЛИ-НЕ" 6, триггер Шмитта 7, второй сумматор по модулю два 8, элемент задержки 9, генератор импульсов 10. При этом выходы 1.1 1.N аналого-цифрового преобразователя 1 подключены к соответствующим входам А.1 - А.N вычитателя 2, кроме того, выходы 1. К+1 1.N АЦП 1 дополнительно подключены к соответствующим входам 3.К+1 3.N инвертора 3, выходы 3.К+1 - 3.N которого подключены к входам В. К+1 В.N вычитателя 2, а выход 1.К АЦП 1 дополнительно подключен к входу 5.1 логической схемы "И" 5, к входу 5.2 которой подключен выход 10.2 генератора импульсов; выход логической схемы "И" 5 подключен к входу инвертора с расширением по выходу к "ИЛИ-НЕ" 6, выходы 6.1 6.К которого подключены к входам В.1 В.К вычитателя 2; одновременно выход логической схемы "И" 5 подключен к входу 8.1 второго сумматора по модулю два 8, на вход 8.2 которого подключен выход триггера Шмитта 7, на вход которого подан входной сигнал; выход второго сумматора по модулю два 8 подключен к входу 9.1 элемента задержки 9, к входу 9.2 которого подключен выход 10.3 генератора импульсов; выход элемента задержки подключен к входу 4.1 первого сумматора по модулю два 4, на вход 4.2 которого подключен выход S.К вычитателя 2; выход 10.1 генератора импульсов подключен к входу 1.2 АЦП 1, на вход 1.1 которого подается входной сигнал; выход первого сумматора по модулю два 4 и выходы S.1 S.К-1 вычитателя 2 являются выходами устройства.

Устройство компенсации помех работает следующим образом. На вход устройства поступает аддитивная смесь сигнала и помехи, которая с учетом мощности белого гауссова шума в полосе сигнала имеет вид:

X(t)=S(t)+nn(t)+no(t);

С выходов 1.1 1.N АЦП значения числовых кодов, соответствующие уровню изменяющейся во времени аналоговой величине входного процесса X(t), поступают на входы А.1 А.N вычитателя. Дополнительно с выходов 1.К+1 1.N АЦП сигнал поступает на входы 3.К+1 3.N инвертора и с его выходов 3.К+1 3.N на входы В. К+1 В.N вычитателя. Кроме того, сигнал с выхода 1.К АЦП поступает на вход 5.1 логической схемы "И", на вход 5,2 которой поступает сигнал с выхода 10,2 генератора импульсов. Результат логического умножения с выхода логической схемы "И" поступает одновременно на вход 8.1 второго сумматора по модулю два и на вход инвертора с расширением по выходу "ИЛИ-НЕ", с выходов 6.1 6. К которого сигнал поступает на входы В.1 В.К вычитателя. Входной сигнал одновременно с поступлением на вход 1.1 АЦП поступает на вход триггера Шмитта, который имеет порог срабатывания, определяемый уровнем входного сигнала на фоне белого гауссова шума, т.е. если входной сигнал X(t)<S(t)+no(t), то на его выходе логическая "1" и если X(t)>S(t)+no(t), логический "0". Сигнал с выхода триггера Шмитта поступает на вход 8.2 второго сумматора по модулю два. На выходе которого появляется сигнал логической "1" или "0" в зависимости от значения сигналов на его входах 8.1 и 8.2 и равнозначен таблице истинности сумматора по модулю два. При этом, если X(t)>S(t)+no(t), то на выходе второго сумматора по модулю два сигнал будет соответствовать сигналу на выходе 1. К АЦП, если же X(t)<S(t)+no(t), то этот сигнал будет инвертирован относительно сигнала на выходе 1.К АЦП. Сигнал с выхода второго сумматора по модулю два поступает на вход 9.1 элемента задержки, где обеспечивается его задержка на время ts. С выхода элемента задержки сигнал поступает на вход 4.1 первого сумматора по модулю два. В вычитателе осуществляется операция алгебраического вычитания из значений сигнала на его входах А.1 А.N, значений сигнала на его входах В.1 В.N. При этом значения сигнала на входах А.1 А. N вычитателя представляют собой значения точного отсчета входного процесса X(t) с шагом квантования εт. Значения же сигнала на входах В.1 В.N, за счет преобразований в логической схеме "И" и инверторе с расширением по выходу "ИЛИ-НЕ", представляют собой значения грубого отсчета входного процесса X(t) с шагом квантования εг. Вычитатель представляет собой обычный сумматор, режим вычитания в котором обеспечивается за счет инвертора и инвертора с расширением по выходу "ИЛИ-НЕ", подключенным к его входам В.1 - В.N. С выходов S. 1 S. К-1 вычитателя результате вычитания поступает на выход устройства. Кроме того, сигнал с выхода S.К вычитателя поступает на вход 4.2 первого сумматора по модулю два, на выходе которого появляется сигнал логической "1" или "0" в зависимости от значений сигналов на его входах 4.1, 4.2 и равнозначен таблице истинности сумматора по модулю два. Совместная работа первого и второго сумматоров по модулю два, элемента задержки и логической схемы "И" обеспечивает выделение знака разности точного и грубого отсчетов входного процесса X(t) и соответствующее этому знаку разности дополнение кода сигнала на выходе устройства. При этом считаем, что если на выходе 1.К АЦП сигнал логического "0", то знак разности положителен и дополнение кода на выходе устройства не происходит. Если же на выходе 1.К АЦП логическая "1", то грубый отсчет входного процесса взят с избытком и на выходе первого сумматора по модулю два происходит соответствующее дополнение кода сигнала на выходе устройства. Выходы 1 К устройства компенсации помех подключаются к соответствующим входам цифрового демодулятора. С выходов 10.1 и 10.3 генератора импульсов сигналы тактовой частоты поступают на вход 1.2 АЦП и на вход 9.2 элемента задержки соответственно. Временные соотношения сигналов с выходов генератора импульсов и других элементов устройства приведены на фиг. 2, где

tв время выборки, время в течение которого компараторы АЦП находятся в режиме сравнения аналогового входного сигнала с набором эталонных опорных напряжений;

tx время хранения, время в течение которого в компараторах хранится значение аналогового входного сигнала;

tn время преобразования, которое состоит из времени перехода компараторов в режим хранения и времени обработки информации в шифраторе АЦП;

ts время суммирования в многоразрядном сумматоре, определяемое как ts= (m-1)tпер+tp, здесь: m число четырех разрядных секций с внутренней схемой ускоренного переноса;

tпер задержка формирования переноса в каждой секции;

tp задержка установления сигналов в разрядах каждой секции;

τ1,τ2, ... τn длительность и временное положение сигналов на выходах и входах соответствующих блоков.

Параметры аналого-цифрового преобразователя с равномерным шагом квантования по уровню во всем его динамическом диапазоне характеризуется следующими значениями:

динамический диапазон аналого-цифрового преобразователя (Uдд) не меньше уровня ожидаемого входного процесса, т.е.

(Ac+An)≅Uдд/2;

разрядность выходного двоичного слова аналого-цифрового преобразователя (N) обеспечивает различие сгнала при отсутствии помех на фоне шумов естественного происхождения и собственных шумов квантования. Общее число уровней квантовая (Nк),

Nк=2N;

точность квантовая процесса X(t) характеризуется 1/2 шага квантования по уровню (εт)εт= Uдд/Nk

точность грубой оценки помехи характеризуется 1/2 грубого шага квантования по уровню (εг)

εг= Uдд/2(N-K);

априорные данные о максимальном уровне сигнала, определены числом разрядов АЦП, в которых укладывается динамический диапазон сигнала с запасом на флуктуации канала передачи (σ

Ac+σ

частота выборки-хранения (FB-X, обеспечивает достаточно точную дискретизацию входного процесса во времени

FB-X>(6.10)fmax=L fmax;

тактовая частота аналого-цифрового преобразователя (fт ацп) позволяет за время Δt1/FB-X произвести кодопреобразование мгновенного отсчета в двоичный N разрядный код.

Технические преимущества предлагаемого устройства компенсации помех заключаются в том, что на его выходе получаем сигнал с соотношением мощности нескомпенсированных помех к мощности сигнала близким к единице (сверху):

Мощность шумов квантования для "тонкой" структуры аналого-цифрового преобразования (P

(εт/2) P

Аналогично, для "грубой" структуры базиса аналого-цифрового преобразования P

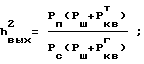

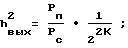

чем и обусловлена эффективность устройства компенсации помех. При этом интегральное отношение мощности помехи (Pп) к мощности сигнала на выходе компенсатора составляет порядка 3.5 дБ, а интегральная эффективность подавления, определяемая соотношением

Gукп= h

где h

Очевидно, чем больше число уровней квантования Nk, тем точнее отслеживается сигнал при заданном динамическом диапазоне на входе, тем меньше уровень шумов квантования. В свою очередь, чем больше число разрядов выделяется для анализа динамического диапазона полезного сигнала, тем грубее при заданных N и Uдд осуществляется отслеживание помехи, тем больше уровень шумов квантования. При этом оптимальные значения числа разрядов преобразователя (К), отводимые для анализа сигнала, должны выбираться в пределах (0,5.0,6) от числа разрядов двоичного кода (N) на выходе аналого-цифрового преобразователя.

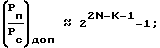

Потенциальная эффективность от применения устройства, оцениваемая допустимым превышением мощности помехи над мощностью сигнала на входе, выраженная через число разрядов аналого-цифрового преобразователя, отводимых для анализа сигнала (К) и его разрядности (N), может быть оценена по выражению вида:

Степень реального подавления помех будет определяться разрядностью аналого-цифрового преобразователя и числом разрядов отводимых для анализа сигнала.

Элементы предлагаемого устройства являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы. Конкретные значения временных параметров работы блоков, а также разрядность АЦП и вычитателя, порог срабатывания триггера Шмитта, выбираются исходя из параметров сигналов на входе устройства, требований к точности их квантования и необходимого уровня подавления помех. Аналого-цифровой преобразователь может быть выполнен на основе серийных интегральных микросхем, например, описанным в книге под ред. А. Й. К. Марцинкявичюса, Э.-А. К. Багданскиса. Быстродействующие интегральные микросхемы ЦАП и АЦП и измерение их параметров. М. Радио и связь, 1988. - 224 с. Вычитатель (сумматор работающий в режиме вычитания), триггер Шмитта, первый и второй сумматоры по модулю два, логическая схема "И", инвертор, элемент задержки, генератор импульсов и инвертор с расширением по выходу "ИЛИ-НЕ" могут быть выполнены на основе серийных интегральных микросхем, например, описанных в книге Шило В. П. Популярные цифровые микросхемы: Справочник. М. Радио и связь, 1987, 352 с. и в книге под ред. М.И. Жодзишского. Цифровые радиоприемные системы: Справочник. М. Радио и связь, 1990. 208 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| АДАПТИВНАЯ АНТЕННАЯ СИСТЕМА | 1995 |

|

RU2099837C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| СЛЕДЯЩИЙ ИЗМЕРИТЕЛЬ СКОРОСТИ СБЛИЖЕНИЯ | 1995 |

|

RU2087007C1 |

| АНАЛИЗАТОР ЧАСТОТНО-ВРЕМЕННОГО РАСПРЕДЕЛЕНИЯ МОЩНОСТИ | 1996 |

|

RU2108591C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1997 |

|

RU2110150C1 |

| УСТРОЙСТВО КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1997 |

|

RU2127945C1 |

Устройство относится к области радиотехники и может быть использовано в составе приемных устройств, предназначенных для приема широкополосных сигналов (ШПС) на фоне мощных, сосредоточенных в спектре сигнала, помех. Устройство содержит аналого-цифровой преобразователь (АЦП)1, вычитатель 2, инвертор 3, первый и второй сумматоры по модулю два 4 и 8, логическую схему "И" 5, инвертор с расширением по выходу "ИЛИ-НЕ" 6, триггер Шмитта 7, элемент задержки 9, генератор импульсов 10. АЦП осуществляет точное квантование, а в блоках 3, 4, 5 и 6 обеспечивается грубое квантование входного процесса (аддитивная смесь полезного сигнала и мощной помехи). Компенсация помехи осуществляется вычитанием в блоке 2 значений грубого отсчета входного процесса (помехи) из значений точного (аддитивная смесь сигнала и помехи). Высокая эффективность компенсации достигается выбором тактовой частоты и необходимого числа разрядов АЦП, обеспечивающих точное и грубое квантования входного процесса. 2 ил.

Устройство компенсации помех, содержащее аналого-цифровой преобразователь, вычитатель, элемент задержки и генератор импульсов, первый выход которого соединен с первым входом аналого-цифрового преобразователя, отличающееся тем, что в него введены инвертор, триггер Шмитта, первый и второй сумматоры по модулю два, элемент И и инвертор с расширением по выходу ИЛИ - НЕ, при этом первая и вторая группы выходов аналого-цифрового преобразователя подключены к соответствующим группам входов вычитателя, к первой дополнительной группе входов которого подключена первая группа выходов аналого-цифрового преобразователя через инвертор, первый выход второй группы выходов аналого-цифрового преобразователя подключен к первому входу элемента И, выход которого подключен к первому входу второго сумматора по модулю два и к входу инвертора с расширением по выходу ИЛИ НЕ, выходы которого подключены к соответствующим входам второй дополнительной группы входов вычитателя, один из выходов вычитателя подключен к первому входу первого сумматора, к второму входу которого подключен выход триггера Шмитта через последовательно соединенные второй сумматор по модулю два и элемент задержки, другой вход которого соединен с вторым выходом генератора импульсов, третий выход которого подключен к второму входу элемента И, вход триггера Шмитта соединен с входом аналого-цифрового преобразователя и является входом устройства, выходами которого являются соответствующие выходы вычитателя и выход сумматора по модулю два.

| SU, авторское свидетельство N 1619413, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-11-27—Публикация

1994-07-18—Подача