СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля сопротивления резистивного элемента | 1988 |

|

SU1700744A1 |

| Аналоговый ключ | 1982 |

|

SU1026310A1 |

| Активный фильтр на коммутируемых конденсаторах | 1986 |

|

SU1381690A1 |

| Устройство выборки и хранения | 1979 |

|

SU826564A1 |

| Мультивибратор | 1978 |

|

SU738107A1 |

| Формирователь импульсов | 1990 |

|

SU1800598A1 |

| Дискретный интегратор | 1987 |

|

SU1529251A1 |

| Усилитель | 1986 |

|

SU1376237A1 |

| ЭЛЕКТРОННЫЙ ПРЕДОХРАНИТЕЛЬ С САМОВОССТАНОВЛЕНИЕМ | 2010 |

|

RU2432656C1 |

| Перемножитель электрических сигналов | 1990 |

|

SU1820396A1 |

Изобретение относится к радиотехнике и может быть использовано в аналоговых интегральных фильтрах. Цель изобретения - повышение точности. Устройство содержит регулируемый дифференциальный резистивный элемент (РДРЭ), операционный усилитель с дифференциальным входом и балансным выходом, источник опорного напряжения с балансным выходом, первый и второй регулируемые источники тока и блок управления регулируемых источников тока. Последний содержит первый и второй эквиваленты резисторов, выполненных на первом и втором коммутируемых конденсаторах, операционный усилитель и три транзистора. Кроме того, устройство содержит двухфазный генератор тактовых импульсов и два интегрирующих конденсатора. Принцип работы устройства основан на выравнивании сопротивлений коммутируемого конденсатора и РДРЭ. 1 з.п. ф-лы, 3 ил.

Изобретение относится к радиотехнике и может быть использовано в аналоговых интегральных фильтрах.

Цель изобретения - повышение точности.

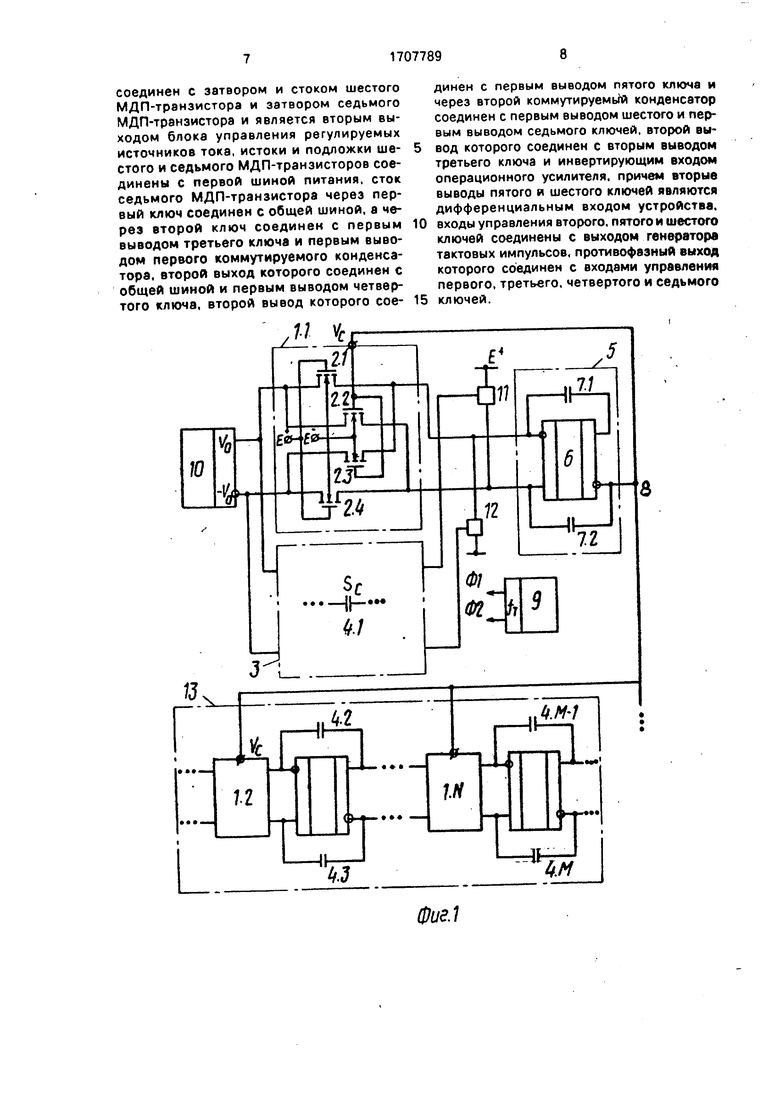

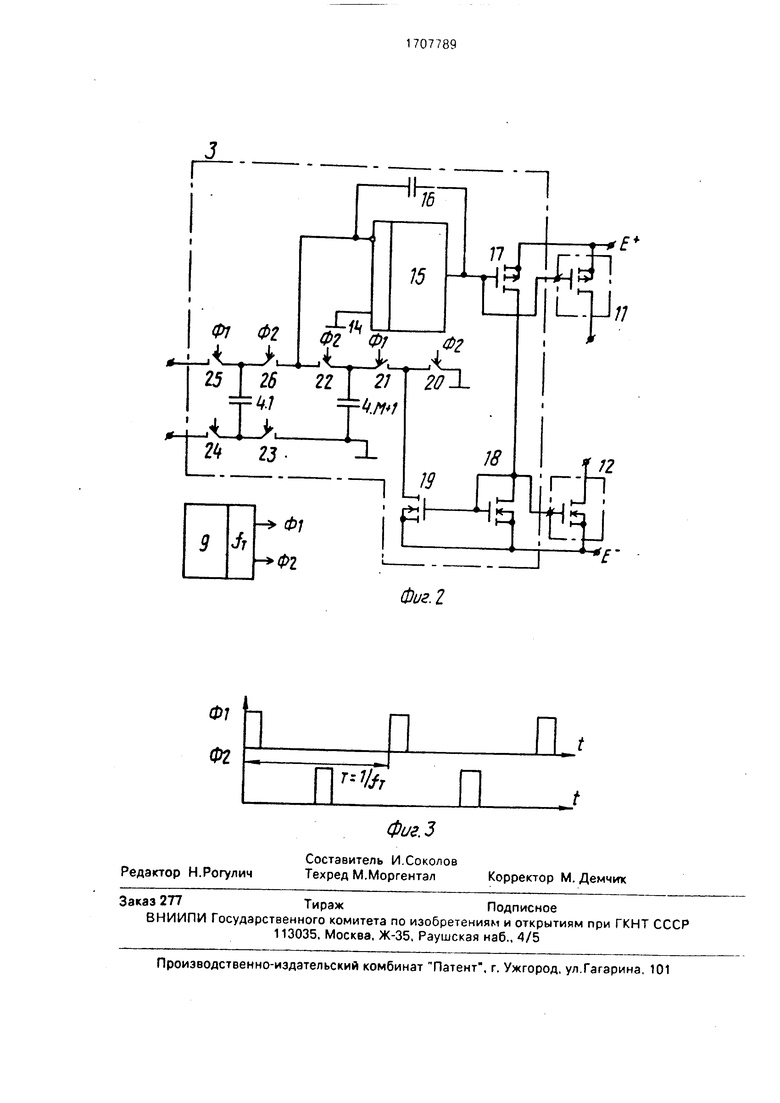

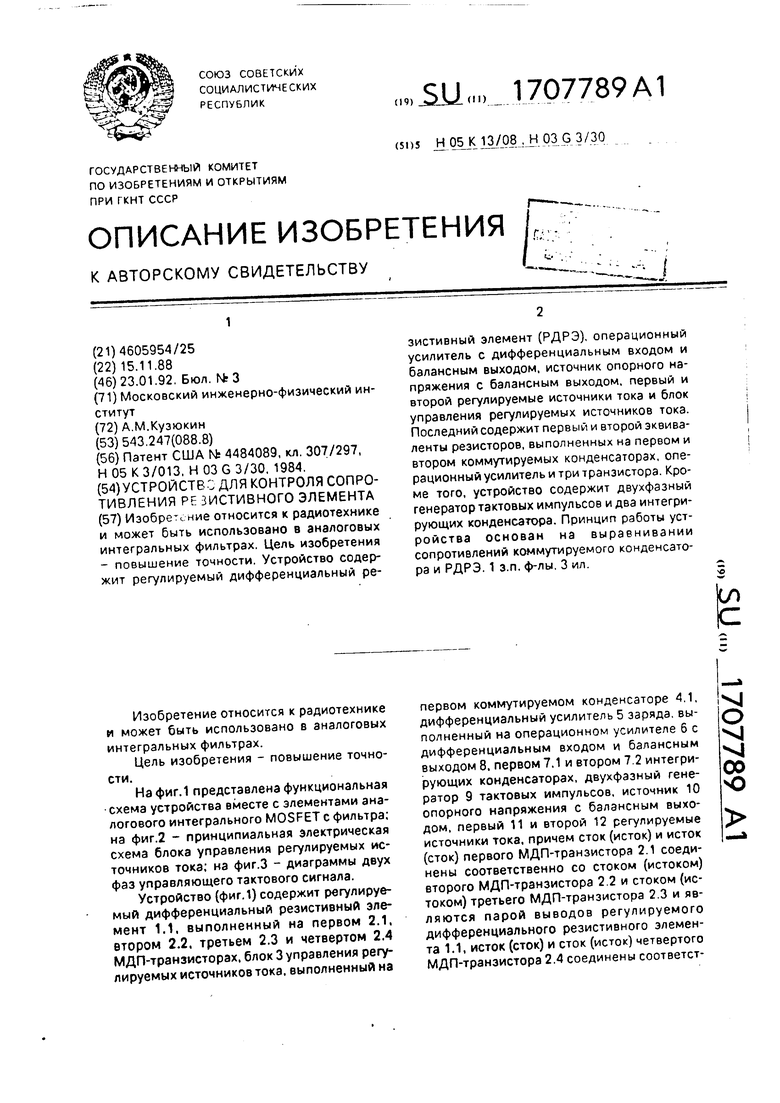

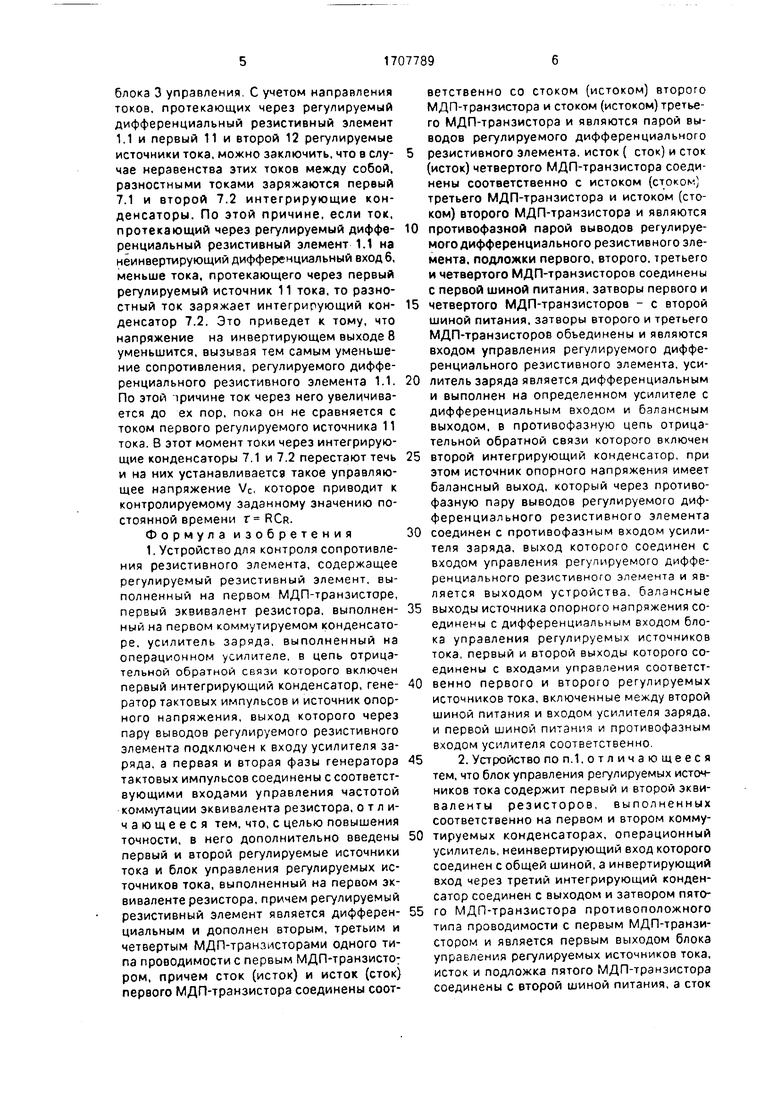

На фиг.1 представлена функциональная схема устройства вместе с элементами аналогового интегрального MOSFET с фильтра; на фиг.2 - принципиальная электрическая схема блока управления регулируемых источников тока; на фиг.З - диаграммы двух фаз управляющего тактового сигнала.

Устройство (фиг.1) содержит регулируемый дифференциальный резистивный элемент 1.1, выполненный на первом 2.1, втором 2.2, третьем 2.3 и четвертом 2.4 МДП-транзисторах, блок 3 управления регулируемых источников тока, выполненный на

первом коммутируемом конденсаторе 4.1, дифференциальный усилитель 5 заряда, выполненный на операционном усилителе 6 с дифференциальным входом и балансным выходом 8, первом 7.1 и втором 7.2 интегрирующих конденсаторах, двухфазный генератор 9 тактовых импульсов, источник 10 опорного напряжения с балансным выходом, первый 11 и второй 12 регулируемые источники тока, причем сток (исток) и исток (сток) первого МДП-транзистора 2.1 соединены соответственно со стоком (истоком) второго МДП-транзистора 2.2 и стоком (истоком) третьего МДП-транзистора 2.3 и являются парой выводов регулируемого дифференциального резистивного элемента 1.1, исток (сток) и сток (исток) четвертого МДП-транзистора 2.4 соединены соответстVI

о VI VI

00

о

вснно с истоком (стоком) второго дифференциального резистивного элемента 1.1, подложки первого 2.1,второго 2.2,третьего 2.3 и четвертого 2.4 МДП-транзистора соединены с первой шиной питания, затворы первого 2.1 и четвертого 2.4 МДП-транзисторов соединены с второй шиной питания, затворы второго 2.2 и третьего 2.3 МДП-транзисторов объединены и являются входом управления регулируемого дифференциального резистивного элемента 1.1. в цепь отрицательной обратной связи операционного усилителя 6 включен первый интегрирующий конденсатор 7.1, в противофазную цепь отрицательной обратной связи включен второй интегрирующий конденсатор 7.2. Балансные выходы источника 10 опорного напряжения через регулируемый дифференциальный резистивный элемент 1.1 подключены к дифференциальному входу дифференциального усилителя 5 заряда, выход которого соединен с входом управления регулируемого дифференциального резистивного элемента 1.1 и является выходом устройства, балансные выходы источника 10 опорного напряжения соединены с дифференциальным входом блока 3 управления регулируемых источников тока, первый и второй выходы которого соединены с входами управления соответственно первого 11 и второго 12 регулируемых источников тока, включенные между второй шиной питания и входом усилителя 5 заряда, и первой шиной питания и противофазным входом усилителя 5 заряда соответственно. Кроме того, устройство содержит аналоговый фильтр 13, выполненный на втором, третьем,..., N-м регулируемых дифференциальных элементах 1.2, 1.3, ..., 1. N, согласованных с первым регулируемым дифференциальным элементом 1.1, вход управления которых подключен к выходу усилителя 5 заряда, второй, третий...., M-й конденсаторы 4.2,4.3...,4. М. согласованные с первым коммутируемым конденсатором 4.1.

Устройство (фиг.2) содержит первый и второй эквиваленты резисторов, выполненных соответственно на первом 4.1 и втором 4.М+1 коммутируемых конденсаторах, операционный усилитель 15. неинвертирующий вход 14 которого соединен с общей шиной, а инвертирующий вход через третий интегрирующий конденсатор 16 соединен с выходом и затвором пятого МДП-транзистора 17 противоположного типа проводимости, с первым МДП-транэистором и Является первым выходом блока управления регулируемых источников тока, исток и подложка пятого МДП-транзистора 17 соединены с второй шиной питания, а сток соединен с затвором и стоком шестого 18 и затвором седьмого 19 МДП-транзисторов и является вторым выходом блока управления

регулируемых источников тока, истоки и подложки шестого 18 и седьмого 19 МДП- транзисторов соединены с первой шиной питания, сток седьмого МДП-транзистора 19 через первый ключ 20 соединен с общей

0 шиной, а через второй ключ 21 соединен с первым выводом третьего ключа 22 и первым выводом второго коммутируемого конденсатора 4.М+1. второй вывод которого соединен с общей шиной и первым выводом

5 четвертого ключа 23, второй вывод которого соединен с первым выводом пятого ключа 24 и через первый коммутируемый конденсатор 4.1 соединен с первым выводом шестого 25 и первым выводом седьмого 26

0 ключей, второй вывод которого соединен с вторым выводом третьего ключа 22 и инвертирующим входом операционного усилителя 16, причем вторые выводы пятого 24 и шестого 25 ключей являются дифференци5 альным входом устройства, входы управления второго 21, пятого 24 и шестого 25 ключей соединены с выходом генератора 9 тактовых импульсов, противофазный выход которого соединен с входами управления

0 первого 20, третьего 22, четвертого 23 и седьмого 26 ключей.

Устройство (фиг.1) работает следующим образом.

Использован известный принцип вы5 равнивания сопротивлений коммутируемого конденсатора (КК) и управляемого резистора. Так как сопротивление КК равно (Сртт), где CR - емкость КК. fj - частота коммутации КК, то, приравнивая его к со0 противлению управляемого резистора R. получают

(CRfy)1 R илиРСг Шт.(1)

Из выражения (1) видно, что постоянная

времени RCR оказывается равной периоду

5 тактовой частоты, с которой-коммутируется КК. Так как тактовую частоту можно вырабатывать эталонным генератором тактовых импульсов (например, кварцевым генератором), то погрешность абсолютного значения

0 постоянной времени RCs определяется погрешностью установки частоты эталонного генератора тактовых импульсов.

Так как напряжение на выходах источника 10 опорного напряжения не равно

5 нулю, то через регулируемый дифференциальный резистивный элемент 1.1 начинают течь токи. Одновременно начинают течь токи через первый 11 и второй 12 регулируемые источники тока вследствие подачи их на управляющие входы сигналов с выходов

блока 3 управления. С учетом направления токов, протекающих через регулируемый дифференциальный резистивный элемент 1.1 и первый 11 и второй 12 регулируемые источники тока, можно заключить, что в случае неравенства этих токов между собой, разностными токами заряжаются первый 7.1 и второй 7.2 интегрирующие конденсаторы. По этой причине, если ток, протекающий через регулируемый дифференциальный резистивный элемент 1.1 на неинвертирующий дифференциальный вход 6, меньше тока, протекающего через первый регулируемый источник 11 тока, то разностный ток заряжает интегрирующий конденсатор 7.2. Это приведет к тому, что напряжение на инвертирующем выходе 8 уменьшится, вызывая тем самым уменьшение сопротивления, регулируемого дифференциального реэистивного элемента 1.1. По этой причине ток через него увеличивается до ех пор, пока он не сравняется с током первого регулируемого источника 11 тока. В этот момент токи через интегрирующие конденсаторы 7.1 и 7.2 перестают течь и на них устанавливается такое управляющее напряжение Vc, которое приводит к контролируемому заданному значению постоянной времени г RCR.

Формула изобретения 1. Устройство для контроля сопротивления резистивного элемента, содержащее регулируемый резистивный элемент, выполненный на первом МДП-транзисторе, первый эквивалент резистора, выполненный на первом коммутируемом конденсаторе, усилитель заряда, выполненный на операционном усилителе, в цепь отрицательной обратной связи которого включен первый интегрирующий конденсатор, генератор тактовых импульсов и источник опорного напряжения, выход которого через пару выводов регулируемого резистивного элемента подключен к входу усилителя заряда, а первая и вторая фазы генератора тактовых импульсов соединены с соответствующими входами управления частотой коммутации эквивалента резистора, отличающееся тем, что, с целью повышения точности, в него дополнительно введены первый и второй регулируемые источники тока и блок управления регулируемых источников тока, выполненный на первом эквиваленте резистора, причем регулируемый резистивный элемент является дифференциальным и дополнен вторым, третьим и четвертым МДП-транзисторами одного типа проводимости с первым МДП-транзисто: ром, причем сток (исток) и исток (сток) первого МДП-транзистора соединены соответственно со стоком (истоком) второго МДП-транзистора и стоком (истоком) третьего МДП-транзистора и являются парой выводов регулируемого дифференциального

резистивного элемента, исток ( сток) и сток (исток) четвертого МДП-транзистора соединены соответственно с истоком (стоком) третьего МДП-транзистора и истоком (стоком) второго МДП-транзистора и являются

0 противофазной парой выводов регулируемого дифференциального резистивного элемента, подложки первого, второго, третьего и четвертого МДП-транзисторов соединены с первой шиной питания, затворы первого и

5 четвертого МДП-транзисторов - с второй шиной питания, затворы второго и третьего МДП-транзисторов объединены и являются входом управления регулируемого дифференциального резистивного элемента, уси0 литель заряда является дифференциальным и выполнен на определенном усилителе с дифференциальным входом и балансным выходом, в противофазную цепь отрицательной обратной связи которого включен

5 второй интегрирующий конденсатор, при этом источник опорного напряжения имеет балансный выход, который через противофазную пару выводов регулируемого дифференциального резистивного элемента

0 соединен с противофазным входом усилителя заряда, выход которого соединен с входом управления регулируемого дифференциального резистивного элемента и является выходом устройства, балансные

5 выходы источника опорного напряжения соединены с дифференциальным входом блока управления регулируемых источников тока, первый и второй выходы которого соединены с входами управления соответст0 венно первого и второго регулируемых источников тока, включенные между второй шиной питания и входом усилителя заряда, и первой шиной питания и противофазным входом усилителя соответственно.

5 2. Устройство по п. 1. о т л и ч а ю ще е с я тем, что блок управления регулируемых источников тока содержит первый и второй эквиваленты резисторов, выполненных соответственно на первом и втором комму0 тируемых конденсаторах, операционный усилитель, неинвертирующий вход которого соединен с общей шиной, а инвертирующий вход через третий интегрирующий конденсатор соединен с выходом и затвором пято5 го МДП-транзистора противоположного типа проводимости с первым МДП-транзи- стором и является первым выходом блока управления регулируемых источников тока, исток и подложка пятого МДП-транзистора соединены с второй шиной питания, а сток

соединен с затвором и стоком шестого МДП-транзистора и затвором седьмого МДП-транзистора и является вторым выходом блока управления регулируемых источников тока, истоки и подложки шестого и седьмого МДП-транзисторов соединены с первой шиной питания, сток седьмого МДП-транзистора через первый ключ соединен с общей шиной, а через второй ключ соединен с первым выводом третьего ключа и первым выводом первого коммутируемого конденсатора, второй выход которого соединен с общей шиной и первым выводом четвертого ключа, второй вывод которого сое

5

динен с первым выводом пятого ключа и через второй коммутируемый конденсатор соединен с первым выводом шестого и первым выводом седьмого ключей, второй вывод которого соединен с вторым выводом третьего ключа и инвертирующим входом операционного усилителя, причем вторые выводы пятого и шестого ключей являются дифференциальным входом устройства, входы управления второго, пятого и шестого ключей соединены с выходом генератора тактовых импульсов, противофазный выход которого соединен с входами управления первого, третьего, четвертого и седьмого ключей.

Фие.1

Фиг. 2

| Патент США Nfc 4484089, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1992-01-23—Публикация

1988-11-15—Подача