Изобретение относится к электриче-Интегрирующий конденсатор 27 будет

ским вычислительным устройствам и можетразряжен через ключ 10, интегрирующий

быть использовано в аналоговых вычисли-конденсатор 28 - через ключ 18, а запомительных машинах.нающий конденсатор 25 - через ключи 15 и

Цель изобретения - повышение точно-5 16, Кроме того, поскольку неинвертируюсти перемножения.щий вход ОУ 30 подключен к общей шине в

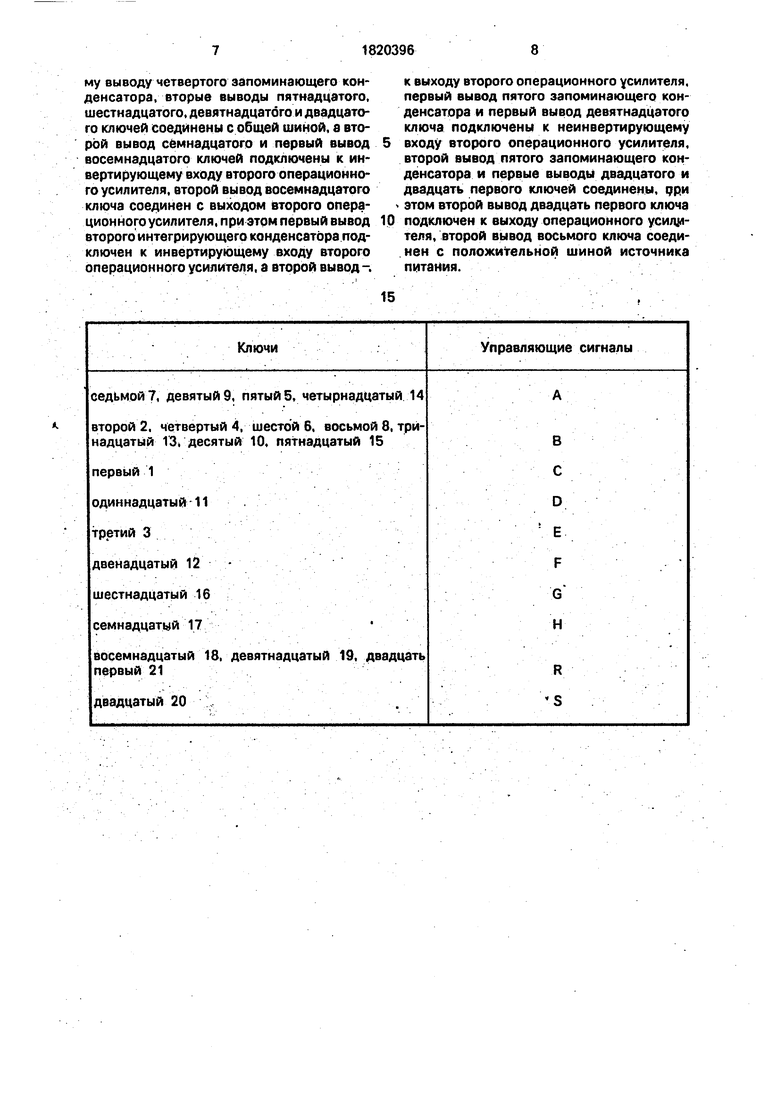

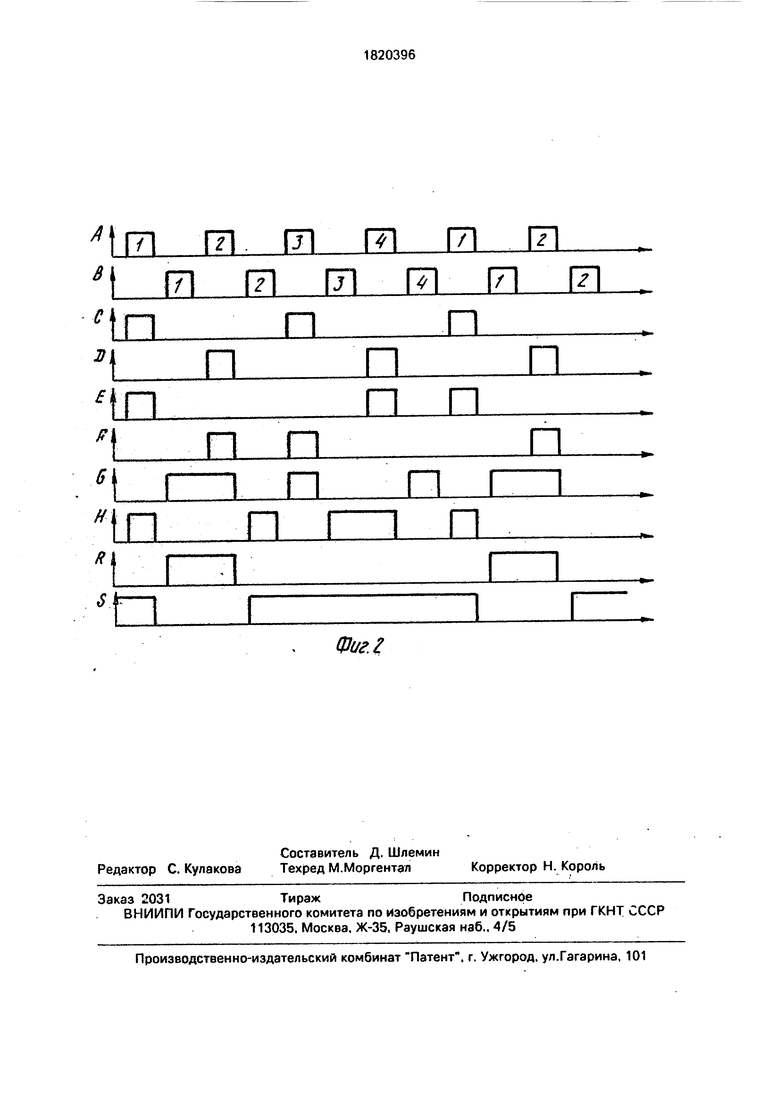

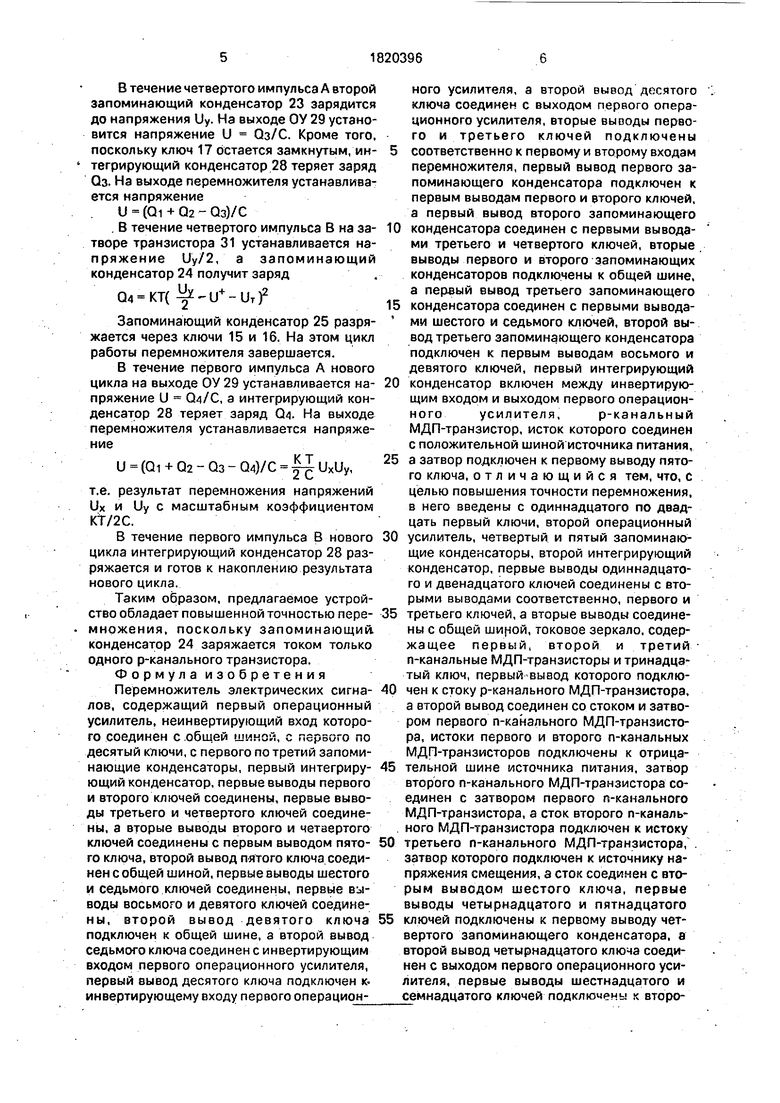

На фиг. 1 представлена принципиаль-данный момент, на его входе устанавливаная схема предлагаемого перемножителяется напряжение смещения этого ОУ. до веэлектрических сигналов; на фиг. 2 - изобра-личины которого зарядится запоминающий

жены временные диаграммы управляющихЮ конденсатор 26.

импульсов.В течение второго импульса А запоми- Перемножитель электрических сигна-нающие конденсаторы 22 и 23, а также залов содержит ключи 1-21, запоминающиетвор транзистора 31 разряжаются до нуля, конденсаторы 22-26, интегрирующие кон-а заряд Qi, накопленный запоминающим денсаторы 27, 28. операционные усилители15 конденсатором 24, передается в интегриру- 29, 30, р-канальный МДП-транзистор31, то-ющий конденсатор 27, конденсатор 24 при ковое зеркало 32. содержащее n-канальныеэтом разряжается. На выходе ОУ 29 появит- МДП-транзисторы 33-35, входы устройствася напряжение (при равенстве емкостей 36 и 37. выход 38, положительную 39, общуюконденсаторов 24 и 27) U СИ/С, где С - 40 и отрицательную 41 шины источника на-20 емкость конденсатора 24. До этого же напряжения питания, источник напряженияпряжения зарядится запоминающий кон- смещения 42.денсатор 25 через ключ 14.

Перемкожитель электрических сигна-В течение второго импульса В запоми- лов работает следующим образом.нающий конденсатор 24 посредством про- Ключи перемножителя управляются им-25 цессов, аналогичных протекавшим в пульсами, временные диаграммы приведе-. течение предыдущего импульса В, получит ны на фиг. 2. Соответствие между фазамизаряд управления и ключами устанавливается таб-Qa КТ(0 - U+ UT) лицей,Кроме того, интегрирующий конденса- На входы устройства 36 и 37 подаются30 тор 28 получит заряд, накопленный .ранее перемножаемые напряжения Ux и Uy coot-конденсатором 25, поскольку замкнулись ветственно.ключи 15 и 17. На неинвертирующий вход В течение первого импульса А заломи-ОУ 30 с запоминающего конденсатора 26 нающий конденсатор 22 через ключ 1 заря-подается напряжение, обратное по закону жается до напряжения Ux, а запоминающий35 напряжению, смещения, до которого этот конденсатор 23 через ключ 3-до напряже-конденсатор зарядился ранее. Следования иу. Затвор транзистора 31 разряжается. тельно, напряжение смещения ОУ ЗОокаяы- до нуля. Запоминающий конденсатор 24 вается скомпенсированным. Таким также разряжается через инвертирующийобразом, на выходе перемножителя при ра- входОУЗЭ.40 венстве емкостей конденсаторов 25, 28. 24 В течение первого импульса В замыка-и 27 устанавливается напряжение J-QifC. ются ключи 2 и 4, при этом на затворе тран-Конденсатор 25 будет разряжен, зистора 31 устанавливается напряжение.

(Ux + Uy)/2 (при одинаковых емкостях перво-В течение третьего импульса А заломиго и второго запоминающих конденсаторов45 нающий конденсатор 22 зарядится до на22 и 23). Таким образом, через транзисторпряжения Ux, а запоминающий конденсатор

31 начинает протекать ток23 разрядится до нуля. На выходе первого

I -к fib + Uy-u+-u 2ОУ 29 установится напряжение U Q2/C, до

2 которого зарядится конденсатор 25.

поскольку замыкается ключ 13. При этомSO В течение третьего импульса В на затвозаряжается запоминающий конденсатор24ре транзистора 31 установится напряжение

через ключ 6 и токовое зеркало 32 на тран-Ux/2, а запоминающий конденсатор 24 ползисторах 33-35. Заряд, полученный этимучит заряд

конденсатором к окончанию первого им-От КТ/--U -U V2

пульса В, при единичном коэффициенте пе-55 из I UT

редачи токового зеркала будет равен:В то же время интегрирующий конп кт fi -iMx-ij+-U V2денсатор 28 получит заряд Qa и напряже1 2 на выходе перемножителя будет U

где Т - продолжительность импульса В.(Qi + Q2)/C.

В течение четвертого импульса А второй запоминающий конденсатор 23 зарядится до напряжения Uy. На выходе ОУ 29 установится напряжение U Оз/С. Кроме того, поскольку ключ 17 остается замкнутым, интегрирующий конденсатор 28 теряет заряд Оз. На выходе перемножителя устанавливается напряжение

U (Qi + Оа - Оз)/С

. В течение четвертого импульса В на затворе транзистора 31 устанавливается напряжение Uy/2, а запоминающий конденсатор 24 получит заряд

(-U+-UTf

Запоминающий конденсатор 25 разряжается через ключи 15 и 16. На этом цикл работы перемножителя завершается.

В течение первого импульса А нового цикла на выходе ОУ 29 устанавливается напряжение U Q4/C, а интегрирующий конденсатор 28 теряет заряд Оз. На выходе перемножителя устанавливается напряжение

U (01 -«-02 - Оз - Q4)/C - yj UxUy,

т.е. результат перемножения напряжений Цх и Uy с масштабным коэффициентом КТ/2С.

В течение первого импульса В нового цикла интегрирующий конденсатор 28 разряжается и готов к накоплению результата нового цикла.

Таким образом, предлагаемое устройство обладает повышенной точностью пере- множения, поскольку запоминающий, конденсатор 24 заряжается током только одного р-канального транзистора.

Формула изобретения

Перемножитель электрических сигналов, содержащий первый операционный усилитель, неинвертирующий вход которого соединен с .общей шиной, с первого по десятый ключи, с первого по третий запоминающие конденсаторы, первый интегрирующий конденсатор, первые выводы первого и второго ключей соединены, первые выводы третьего и четвертого ключей соединены, а вторые выводы второго и четвертого ключей соединены с первым выводом пятого ключа, второй вывод пятого ключа соединен с общей шиной, первые выводы шестого и седьмого ключей соединены, первые выводы восьмого и девятого ключей соедине- ны, второй вывод девятого ключа подключен к общей шине, а второй вывод седьмого ключа соединен с инвертирующим входом первого операционного усилителя, первый вывод десятого ключа подключен к. инвертирующему входу первого операционного усилителя, а второй вывод десятого ключа соединен с выходом первого операционного усилителя, вторые выводы первого и третьего ключей подключены 5 соответственно к первому и второму входам перемножителя, первый вывод первого запоминающего конденсатора подключен к первым выводам первого и второго ключей, а первый вывод второго запоминающего 10 конденсатора соединен с первыми выводами третьего и четвертого ключей, вторые выводы первого и второго запоминающих конденсаторов подключены к общей шике, а первый вывод третьего запоминающего 15 конденсатора соединен с первыми вывода- ми шестого и седьмого ключей, второй вывод третьего запоминающего конденсатора подключен к первым выводам восьмого и девятого ключей, первый интегрирующий

0 конденсатор включен между инвертирующим входом и выходом первого операционногоусилителя, р-канальный МДП-транзистор, исток которого соединен с положительной шиной источника питания,

5 а затвор подключен к первому выводу пятого ключа, отличающийся тем, что, с целью повышения точности перемножения, в него введены с одиннадцатого по двадцать первый ключи, второй операционный

0 усилитель, четвертый и пятый запоминающие конденсаторы, второй интегрирующий конденсатор, первые выводы одиннадцатого и двенадцатого ключей соединены с вторыми выводами соответственно, первого и

5 третьего ключей, а вторые выводы соединены с общей шиной, токовое зеркало, содержащее первый, второй и третий- n-канальные МДП-транзисторы и тринадцатый ключ, первый-вывод которого подклю0 чен к стоку р-канального МДП-транзистора, а второй вывод соединен со стоком и затвором первого n-канального МДП-транзистора, истоки первого и второго п-канальных МДП-транзисторов подключены к отрица5 тельной шине источника питания, затвор второго n-канального МДП-транзистора соединен с затвором первого п-канального МДП-транзистора, а сток второго п-каналь- . ного МДП-транзистора подключен к истоку

0 третьего n-канального МДП-транзистора, . затвор которого подключен к источнику напряжения смещения, а сток соединен с вторым выводом шестого ключа, первые выводы четырнадцатого и пятнадцатого

5 ключей подключены к первому выводу четвертого запоминающего конденсатора, а второй вывод четырнадцатого ключа соединен с выходом первого операционного усилителя, первые выводы шестнадцатого и семнадцатого ключей подключены к второму выводу четвертого запоминающего конденсатора, вторые выводы пятнадцатого, шестнадцатого, девятнадцатого и двадцатого ключей соединены с общей шиной, а второй вывод семнадцатого и первый вывод восемнадцатого ключей подключены к инвертирующему входу второго операционного усилителя, второй вывод восемнадцатого ключа соединен с выходом второго операционного усилителя, при этом первый вывод второго интегрирующего конденсатора подключен к инвертирующему входу второго операционного усилителя, а второй вывод-.

0

к выходу второго операционного усилителя, первый вывод пятого запоминающего конденсатора и первый вывод девятнадцатого ключа подключены к неинвертирующему входу второго операционного усилителя, второй вывод пятого запоминающего конденсатора и первые выводы двадцатого и двадцать первого ключей соединены, рри этом второй вывод двадцать первого ключа подключен к выходу операционного уси/цл- теля, второй вывод восьмого ключа соединен с положительной шиной источника питания.

tm mm m m

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

| Устройство для контроля сопротивления резистивного элемента | 1988 |

|

SU1707789A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Преобразователь напряжение-временной интервал | 1981 |

|

SU991605A1 |

| Устройство контроля сопротивления резистивного элемента | 1988 |

|

SU1700744A1 |

| Аналого-дискретный интегратор | 1981 |

|

SU987632A1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| Устройство для ввода информации от аналогового датчика в вычислительную машину | 1979 |

|

SU860047A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Сущность изобретения. Устройство содержит ключи 1-21, запоминающие конденсаторы 22-26. два интегрирующих конденсатора 27, 28, два операционных усилителя 29-30, р-каналь- ный.МДП-транзистор 31, токовое зеркало 32, содержащее n-канэльные МДП-транэи- сторы 33-35, источник напряжения смещения 42, 2 ил. 1 табл.

Фиг. H

| Hong Z | |||

| Melchlpr H | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| ГАЛЬВАНИЧЕСКИЙ ЭЛЕМЕНТ | 1923 |

|

SU1015A1 |

Авторы

Даты

1993-06-07—Публикация

1990-10-22—Подача