Изобретение относится к вычислительной технике и может быть использовано для интегрирования сигналов, заданн1;йх цифровым кодом при нечетких границах,интегрирования.

Известен интегратор, содержащий элементы задержки..усилители и сумматор.

Недостатком устройства являются относительно низкие функциональные возможности.

Наиболее близким по технической сущности к предлагаемому является цифровой интегратор, содержащий формирователь временных меток в составе ГТЙ и формирователя Импульсов, а также интегрирующий блок.

Недостатком устройства являются относительно, низкие функциональные возможности, поскольку оно не позволяет осуществлять интегрирование при нечетко заданных моментах начала и конца интегрирования.

Цель изобретения-- расширение области применения за счет осуществления интегрирования при нечетко заданных моментах начала и конца интегрирования.

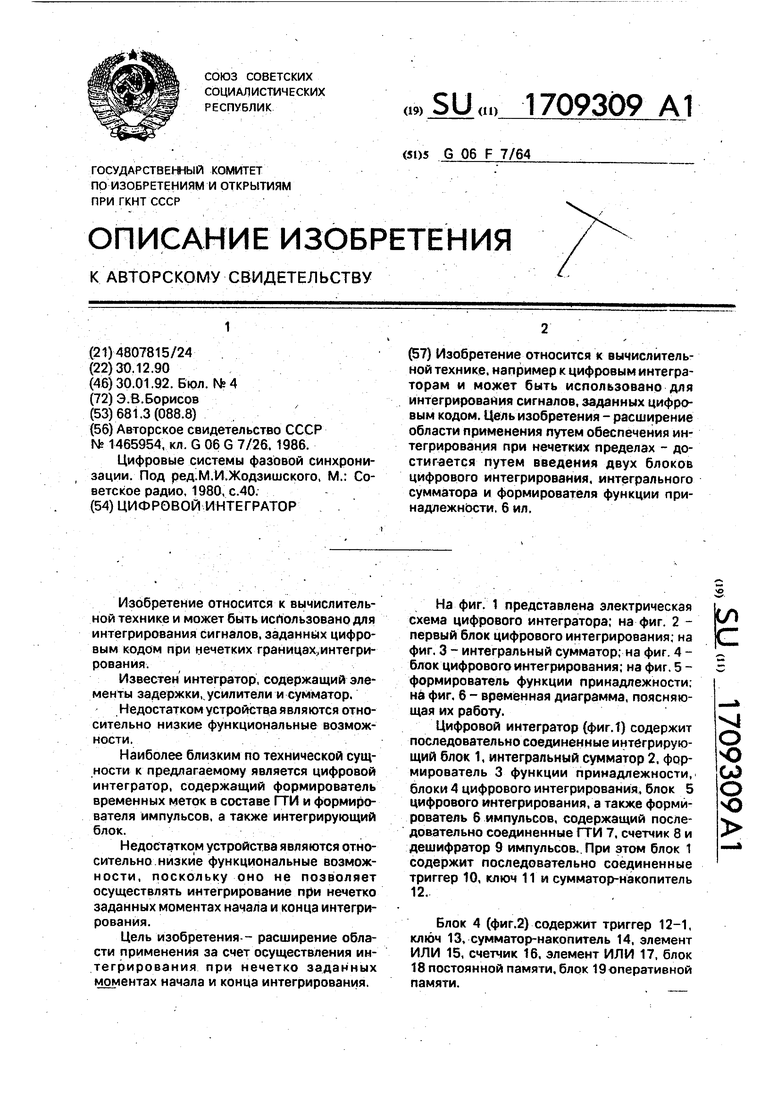

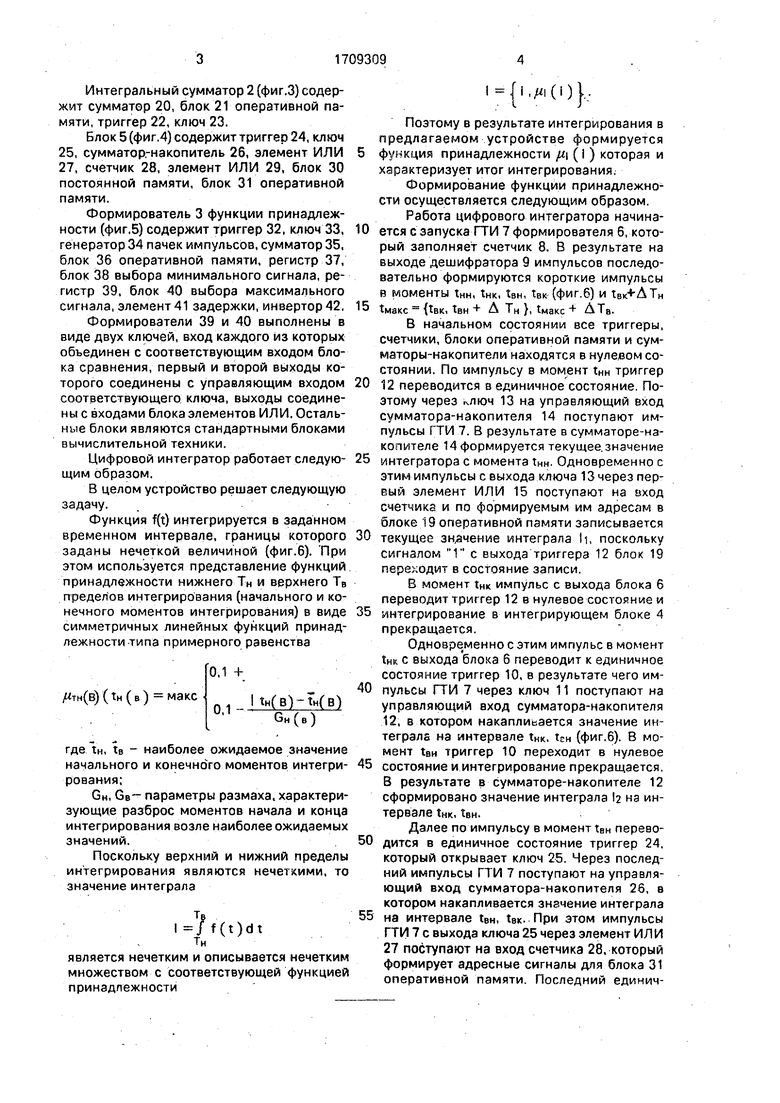

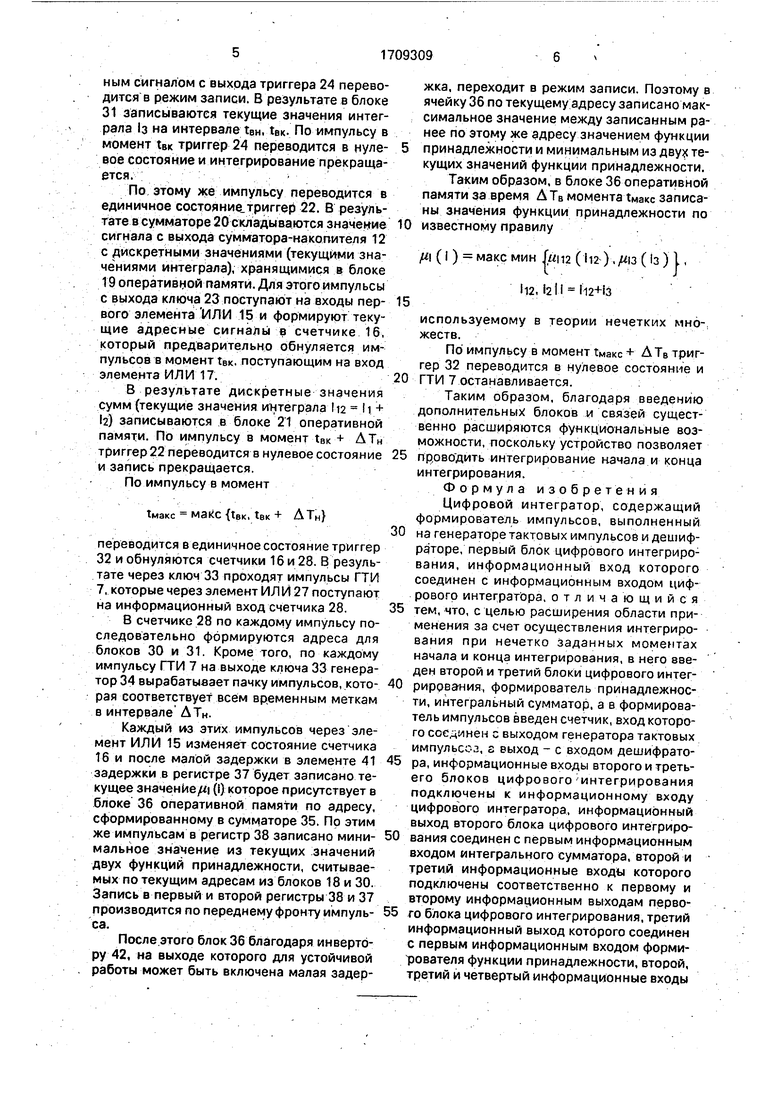

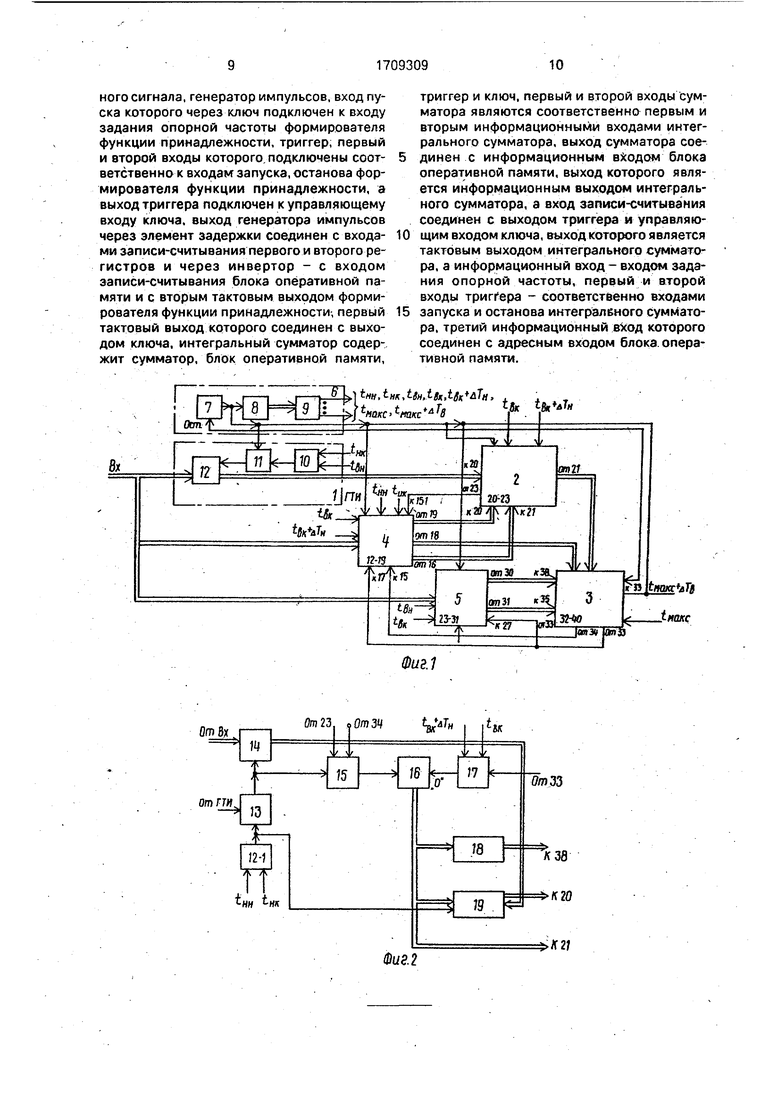

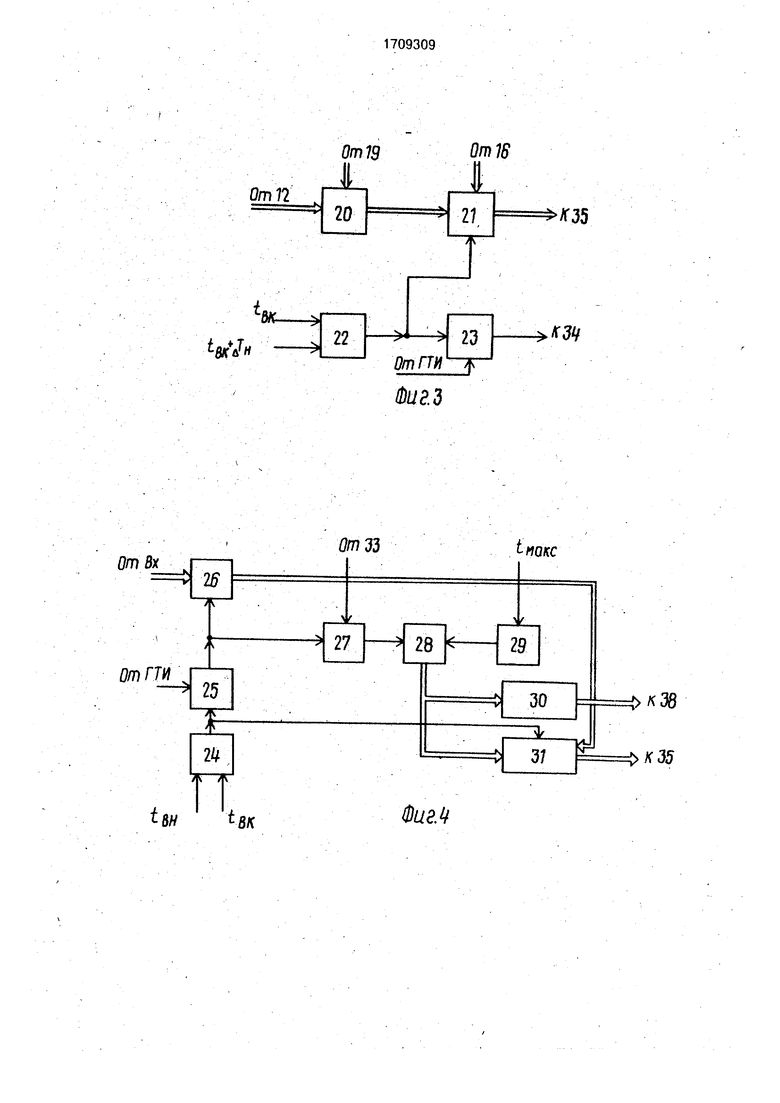

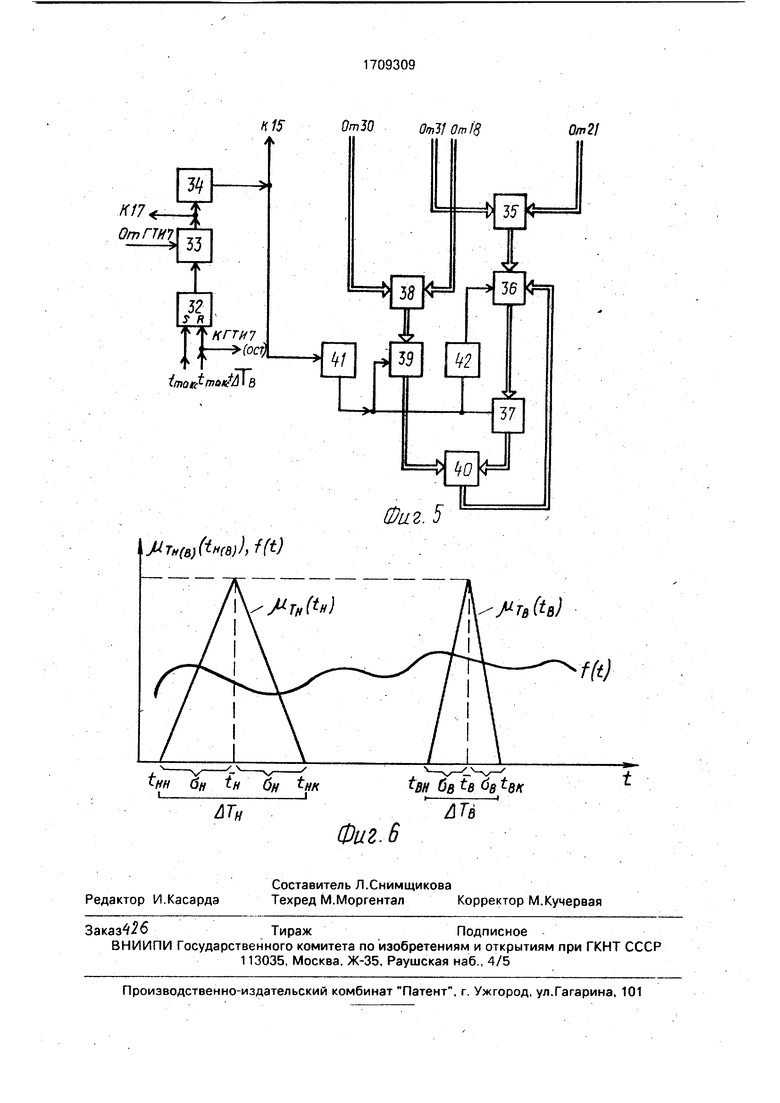

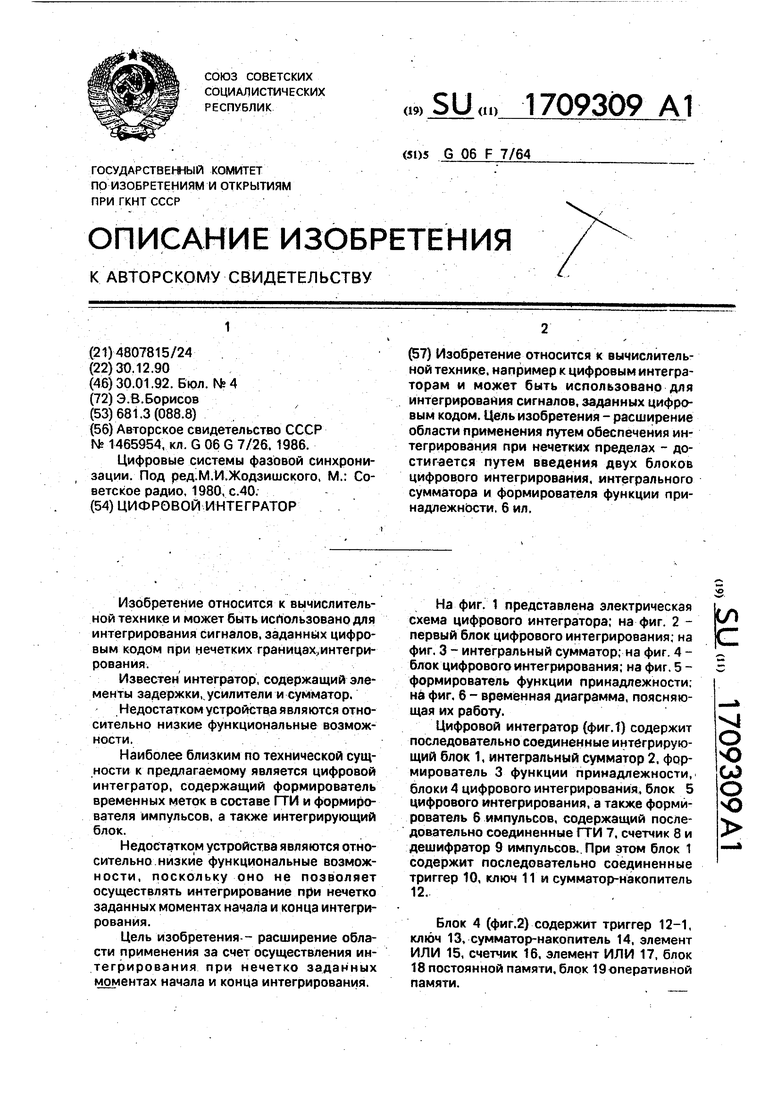

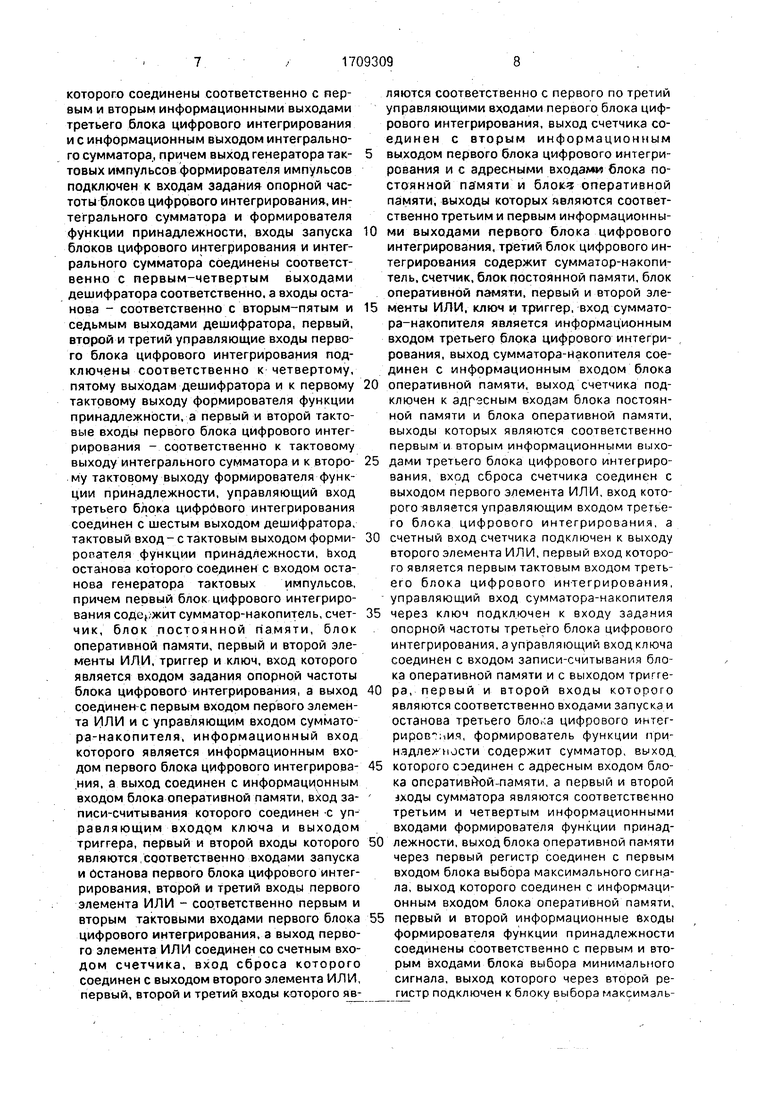

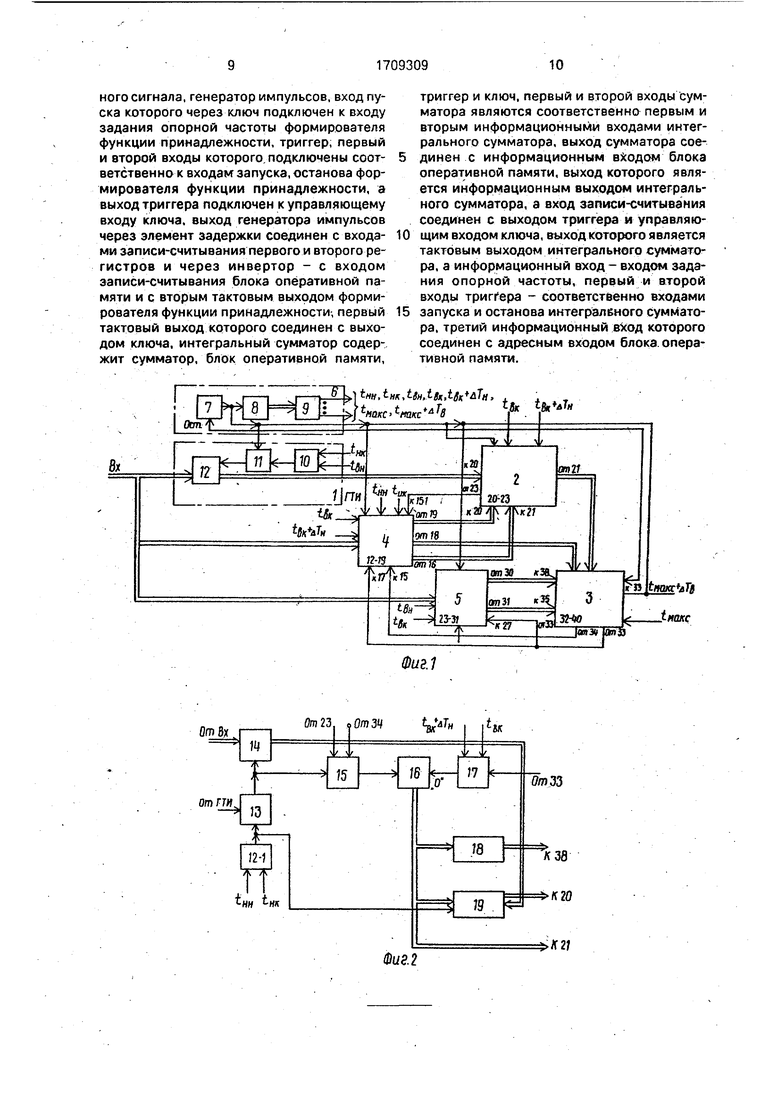

На фиг. 1 представлена электрическая схема цифрового интегратора; на фиг. 2 первый блок цифрового интегрирования,- на фиг, 3 - интегральный сумматор; на фиг. 4 блок цифрового интегрирования; на фиг. 5 формирователь функции принадлежности: на фиг. 6 - временная диаграмма, поясняющая их работу.

Цифровой интегратор (фиг.1) содержит последовательно соединенные интегрирующий блок 1. интегральный сумматор 2. формирователь 3 функции принадлежности, блоки 4 цифрового интегрирования, блок 5 цифрового интегрирования, а также формирователь 6 импульсов, содержащий последовательно соединенные ГТИ 7, счетчик 8 и дешифратор 9 импульсов.. При этом блок 1 содержит последовательно соединенные триггер 10, ключ 11 и сумматор-накопитель 12,

Блок 4 (фиг.2) содержит триггер 12-1. ключ 13, сумматор-накопитель 14, элемент ИЛИ 15. счетчик 16, элемент ИЛИ 17. блок 18 постоянной памяти, блок 19 оперативной памяти.

Интегральный сумматор 2 (фиг.З) содержит сумматор 20, блок 21 оперативной памяти, триггер 22, ключ 23.

Блок 5 (фиг,4) содержит триггер 24, ключ 25, сумматоргнакопитель 26, элемент ИЛИ 27, счетчик 28, элемент ИЛИ 29, блок 30 постоянной памяти, блок 31 оперативной памяти.

Формирователь 3 функции принадлежности (фиг.5) содержит триггер 32, ключ 33, генератор 34 пачек импульсов, сумматор 35, блок 36 оперативной памяти, регистр 37, блок 38 выбора минимального сигнала, регистр 39, блок 40 выбора максимального сигнала, элемент 41 задержки, инвертор 42.

Формирователи 39 и 40 выполнены в виде двух ключей, вход каждого из которых объединен с соответствующим входом блока сравнения, первый и второй выходы которого соединены с управляющим входом соответствующего ключа, выходы соединены с входами блока элементов ИЛИ. Остальные блоки являются стандартными блоками вычислительной техники.

Цифровой интегратор работает следующим образом.

В целом устройство решает следующую задачу.

Функция f(t) интегрируется в заданном временном интервале, границы которого заданы нечеткой величиной (фиг.6). При этом используется представление функций принадлежности нижнего Тн и верхнего Тв пределов интегрирования (начального и конечного моментов интегрирования) в виде симметричных линейных функций принадлежности типа примерного равенства

0,1 +

) (tH ( в ) макс

д Ин(в)-Тн(в)

(в)

гдеЛн, te - наиболее ожидаемое значение начального и конечно о моментов интегрирования;

GH, GB- параметры размаха, характеризующие разброс моментов начала и конца интегрирования возле наиболее ожидаемых значений.

Поскольку верхний и нижний пределы интегрирования являются нечеткими, то значение интеграла

f(t)dt

TH

является нечетким и описывается нечетким множеством с соответствующей функцией принадлежности

{i.)}.:

Поэтому в результате интегрирования в предлагаемом устройстве формируется функция принадлежности jMi (i ) которая и характеризует итог интегрирования.

Формирование функции принадлежности осуществляется следующим образом.

Работа цифрового интегратора начинается с запуска ГТИ 7 формирователя 6, который заполняет счетчик 8. В результате на выходе дешифратора 9 импульсов последовательно формируются короткие импульсы в моменты Хин, tHK, tsH, гвк(фиг.б) и

1макс {Твк, tsH + АТн}, 1макс+ А Та.

В начальном состоянии все триггеры, счетчики, блоки оперативной памяти и сумматоры-накопители находятся в нулевом состоянии. По импульсу в момент IHH триггер

12 переводится в единичное состояние. Поэтому через Г.ЛЮЧ 13 на управляющий вход сумматора-накопителя 14 поступают импульсы ГТИ 7. В результате в сумматоре-накопителе Сформируется текущее.значение

интегратора с момента Тнн. Одновременно с этим импульсы с выхода ключа 13 через первый элемент ИЛИ 15 поступают на вход счетчика и по формируемым им адресам в блоке 19 оперативной памяти записывается

текущее значение интеграла h, поскольку сигналом 1 с выхода триггера 12 блок 19 переходит в состояние записи.

В момент tHK импульс с выхода блока 6 переводит триггер 12 в нулевое состояние и

Н1нтегрирование в интегрирующем блоке 4 прекращается.

Одновременно с этим импульс в момент tHK с выхода блока 6 переводит к единичное состояние триггер 10, в результате чего импульсы ГТИ 7 через ключ 11 поступают на управляющий вход сумматора-накопителя 12, в котором накапливается значение интеграла на интервале tHK, tcH (фиг.6). В момент tsH триггер 10 переходит в нулевое

состояние и интегрирование прекращается. В результате в сумматоре-накопителе 12 сформировано значение интеграла 2 на интервале tHK, tsH.

Далее по импульсу в момент ten переводится в единичное состояние триггер 24. который открывает ключ 25. Через последний импульсы ГТИ 7 поступают на управляющий вход сумматора-накопителя 26, в котором накапливается значение интеграла на интервале tsH, tsK. При этом импульсы ГТИ 7 с выхода ключа 25 через элемент ИЛИ 27 поступают на вход счетчика 28, который формирует адресные сигналы для блока 31 оперативной памяти. Последний единичным сигналом с выхода триггера 24 переводится в режим записи. В результате в блоке

31записываются текущие значения интеграла 1з на интервале tBH.tBK. По импульсу в момент tBK триггер 24 переводится в нулевое состояние и интегрирование прекращается.--; /;-.. . .; . -

По этому же импульсу переводится в единичное состояние,триггер 22. В результате в сумматоре 20складываются значение сигнала с выхода сумматора-наког ителя 12 с дискретными значениями (текущй:ми значениями интеграла), хранящимися в блоке 19 оперативной памяти. Для этого импульсы с выхода ключа 23 поступаю1Т на входы первого элемента ИЛИ 15 и формируют текущие адресные сигналы в счетчике 16, который предварительно обнуляется импульсов в момент Гек. поступающим на вход элемента ИЛИ 17.

В результате дискретные значения сумм (текущие значения щгеграла 112 11 + 12) записываются в блоке 21 оперативной памяти. По импульсу в момент IBK + АТи триггер22 переводится в нулевое состояние и запись прекращается.

По импульсу в момент

Тмзкс Make {tBK, tBK + АТн}

переводится в единичное состояние триггер

32и обнуляются счетчики 16 и 28. В результате через ключ 33 проходят импульсы ГТИ 7, которые через элемент ИЛИ 27 поступают на информационный вход счетчика 28.

В счетчике 28 по каждому импульсу последовательно формируются адреса для блоков 30 и 31. Кроме того, по каждому импульсу ГТИ 7 на выходе ключа 33 генератор 34 вырабатывает пачку импульсов, которая соответствует всем временным меткам в интервале АТн.

Каждый этих импульсов через элемент ИЛИ 15 изменяет состояние счетчика 16 и после малой задержки в элементе 41 задержки в регистре 37 будет записано текущее значенйеуИ| (i) которое присутствует в блоке 36 оперативной памяти по адресу, сформированному в сумматоре 35. По этим же импульсам в регистр 38 записано минимальное значение из текущих :значений двух функций принадлежности, считываемых по текущим адресам из блоков 18 и 30. Запись в первый и второй регистры 38 и 37 производится по переднему фронту импульса., .,

После.этого блок 36 благодаря инвертору 42, на выходе которого для устойчивой работы может быть включена малая задержка, переходит в режим записи. Поэтому в ячейку 36 по текущему;адресу записано максимальное значение между записанным ранее по этому же адресу значением функции

5 принадлежности и минимальным из двух текущих значений функции принадлежности. Таким образом, в блоке 36 оперативной памяти за время А ТвмоментаЛмакс записаны значения функции принадлежности по

0 известному правилу.

/Л (I ) макс мин /И112 (ii2 ) ./Лз (1з ) 1,

112, I2ll ll2+i3

5

используемому в теории нечетких мно-, жеств.

По импульсу в момент Гмакс + АТв триггер 32 переводится в нулевое состояние и

0 ГТИ 7 останавливается.:

Таким образом, благодаря введению дополнительных блоков и связей существенно расширяются функциональные возможности, поскольку устройство позволяет

5 проводить интегрирование начала и конца интегрирования.

Формула изобретения Цифровой интегратор, содержащий формирователь импульсов, выполненный

0 на генераторе тактовых импульсов и дешифраторе, первый блок цифрового интегрирования, информационный вход которого соединен с информационным входом цифровогр интегратЬра. отличающийся

5 тем, что, с целью расширения области применения за счет осуществления интегрирования при нечетко заданных моментах начала и конца интегрирования, в него введен второй и третий блоки цифрового интег0 рировэния, формирователь принадлежности, интегральный сумматор, а в формирователь импульсов введен счетчик, вход которого соединен с выходом генератора тактовых импульсоз, S выход - с входом дешифратора, информационные входы второго и третьего блоков цифровогоинтегрирования подключены к информационному входу цифрового интегратора, информационный выход второго блока цифрового интегрирования соединен с первым информационным входом интегрального сумматора, второй и третий информационные входы которого подключены соответственно к первому и второму информационным выходам первого блока цифрового интегрирования, третий информационный выход которого соединен с первым информационным входом формирователя функции принадлежности, второй, третий и четвертый информационные входы

которого соединены соответственно с первым и вторым информационными выходами третьего блока цифрового интегрирования и с информационным выходом интегрального сумматора, причем выход генератора тактовых импульсов формирователя импульсов подключен к входам задания опорной частоты блоков цифрового интегрирования, интегрального сумматора и формирователя функции принадлежности, входы запуска блоков цифрового интегрирования и интегрального сумматора соединены соответственно с первым-четвертым выходами дешифратора соответственно, а входы останова - соответственно с вторым-пятым и седьмым выходами дешифратора, первый, второй и третий управляющие входы первого блока цифрового интегрирования подключены соответственно к четвертому, пятому выходам дешифратора и к первому тактовому выходу формирователя функции принадлежности, а первый и второй тактовые входы первого блока цифрового интегрирования - соответственно к тактовому выходу интегрального сумматорам к второму тактовому выходу формирователя функции принадлежности, управляющий вход третьего блока цифрбвого интегрирования соединен с шестым выходом дешифратора, тактовый вход-с тактовым выходом формирователя функции принадлежности, ёход останова которого Соединен с входом останова генератора тактовых импульсов, причем первый блок цифрового интегрирования сумматор-накопитель, счетчик, блок постоянной памяти, блок оперативной памяти, первый и второй элементы ИЛИ, триггер и ключ, вход которого является входом задания опорной частоты блока цифрового интегрирования, а выход соединен-с первым входом первого элемента ИЛИ и с управляющим входом сумматора-накопителя, информационный вход которого является информационным входом первого блока цифрового интегрирования, а выход соединен с информационным входом блока оперативной памяти, вход записи-считывания которого соединен -с управляющим входрм ключа и выходом триггера, первый и второй входы которого являются/соответственно входами запуска и Останова первого блока цифрового интегрирования, второй и третий входы первого элемента ИЛИ - соответственно первым и вторым тактовыми входами первого блока цифрового интегрирования, а выход первого элемента ИЛИ соединен со счетным входом счетчика, вход сброса которого соединен с выходом второго элемента ИЛИ, первый, второй и третий входы которого являются соответственно с первого по третий управляющими входами первого блока цифрового интегрирования, выход счетчика соединен с вторым информационным выходом первого блока цифрового интегрирования и с адресными входами блока постоянной памяти и блок оперативной памяти, выходы которых являются соответственно третьим и первым информационными выходами первого блока цифрового интегрирования, третий блок цифрового интегрирования содержит сумматор-накопитель, счетчик, блок постоянной памяти, блок оперативной памяти, первый и второй зле5 менты ИЛИ. ключ и триггер, вход сумматора-накопителя является информационным входом третьего блока цифрового интегрирования, выход сумматора-накопителя соединен с информационным входом блока 0 оперативной памяти, выход счетчика подключен к адрэсным входам блока постоянной памяти и блока оперативной памяти, выходы которых являются соответственно первым и вторым информационными выхо5 дами третьего блока цифрового интегрирования, вход сброса счетчика соединен с выходом первого элемента ИЛИ, вход которого является управляющим входом третьего блока цифрового интегрирования, а 0 счетный вход счетчика подключен к выходу второго элемента ИЛИ, первый вход которого является первым тактовым входом третьего блока цифрового интегрирования, управляющий вход сумматора-накопителя 5 через ключ подкл.ючен к входу задания опорной частоты третьего блока цифрового интегрирования, а управляющий вход ключа соединен с входом записи-считывания блока оперативной памяти и с выходом тригге0 ра, первый и второй входы которого являются соответственно входами запуска и останова третьего цифрового интегриров ;1ия, формирователь функции принэдле ности содержит сумматор, выход. 5 которого соединен с адресным входом блока опсративй-ой-памяти, а первый и второй ходы сумматора являются соответственно третьим и четвертым информационными входами формирователя функции принад0 лежности, выход блока оперативной памяти через первый регистр соединен с первым входом блока выбора максимального сигнала, выход которого соединен с информационным входом блока оперативной памяти, 5 первый и второй информационные входы формирователя функции принадлежности соединены соответственно с первым и вторым входами блока выбора минимального сигнала, выход которого через второй регистр подключен к блоку выбора максимальHoro сигнала, генератор импульсов, вход пуска которого через ключ подключен к входу задания опорной частоты формирователя функции принадлежности, триггер, первый и второй входы которого, подключены соответственно к входам запуска, останова формирователя функции принадлежности, а выход триггера подключен к управляющему входу ключа, выход генератора импульсов через элемент задержки соединен с входами записи-считывания первого и второго регистров и через инвертор - с входом записи-считывания блока оперативной памяти и с вторым тактовым выходом формирователя функции принадлежности-, первый тактовый выход которого соединен с выходом ключа, интегральный сумматор содержит сумматор, блок оперативной памяти.

триггер и ключ, первый и второй входы сумматора являются соответственно первым и вторым информационными входами интегрального сумматора, выход сумматора соединен с информационным в:$содом блока оперативной памяти, выход которого является информационным выходом интегрального сумматора, а вход записи-считывания соединен с выходом триггера и управляющим входом ключа, выход которого является тактовым выходом интегрального сумматора, а информационный вход - входом задания опорной частоты, первый и второй входы трипера - соответстбенно входами

5 запуска и останова интеграленого сумматора, третий информационный которого соединен с адресным входом блока, оперативной памяти.

0m 72

От IS

Л-Зб

21

j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двух нечетких величин | 1990 |

|

SU1791815A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| Генератор случайных чисел | 1989 |

|

SU1686440A1 |

| Генератор случайных чисел | 1990 |

|

SU1774333A1 |

| Цифровой интегратор | 1990 |

|

SU1795457A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1999 |

|

RU2149513C1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для сравнения двух нечетких величин | 1986 |

|

SU1442989A1 |

| Устройство для сравнения нечетких величин | 1990 |

|

SU1774331A1 |

Изобретение относится к вычислительной технике, например к цифровым интеграторам и может быть использовано для интегрирования сигналов, заданных цифровым кодом. Цель изобретения - расширение области применения путем обеспечения интегрирования при нечетких пределах - достигается путем введения двух блоков цифрового интегрирования, интегрального сумматора и формирователя функции принадлежности. 6 ил.

-

0m Sx

от ГТИ

11

rjv

-

Отгти

Шгз

HOKC

0m d

ФиёМ

П15

ОтЗОQmilOmfS

| Генератор равномерно распределенных псевдослучайных величин | 1987 |

|

SU1465954A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Под ред.М.И.Жодзи^шского | |||

| М.: Советское радио, 1980 | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1992-01-30—Публикация

1990-12-30—Подача