формирователь импульсов соединен с входом первого элемента задержки, единичный вход триггера соединен с выходом первого формирователя импульсов, а нулевой вход подключен к выходу второго формирователя импульсов, выход триггера соединен с первым входом первого элемента И, второй вход которого подключен к выходу второго генератора тактовых импульсов, выход первого элемента И соединен с тактовыми входами второго и третьего счетчиков, разрядные выходы второго счетчика соединены с соответствующими входами первого дешифратора, а разрядные входь начальной установки подключены к выходам Соответствующих элементов И шестой группы, выход переноса второго счетчика через последовательно соединенные третий формирователь импульсов и второй элемент задержки соединен с первыми входами элементов И шестой группы, вторые входы которых подключены к соответствующим выходам блока постоянной памяти, адресные входы которого подключены к соответствующи разрядным выходам четвертого счетчика, тактовый вход которого подключен к выходу третьего формирователя импульсов, входы второго дешифратора подключены к соответствующим разрядным выходам третьего счетчика, выход переноса которого соединен с входом второго формирователя импульсов, отличающе е ся тем, что, с целью повышения точности и упрощения устройства, в него введены третий и четвертый аналого-цифровые преобразователи, первый и второй фильтры, второй, третий, четвертый и пятый регистры, вторая группа блоков умножения, седьмая, восьмая, девятая, десятая и одиннадцатая группы элементов И, третья и четвертая группы блоков усреднения, вторая и третья группы элементов, задержки, вторая группа блоков памяти, третий и четвертый элементы ИЛИ, пятый и шестой счетчики, третий и четвертый дешифраторы, четвертый формирователь импульсов, второй элемент И, сз матор, элемент НЕ, блок сравнения, причем входы первого и второго фильтров ,соответственно соединены с входами первого и второго аналого-цифровых преобразователей, а выходы соответственно соединены с информационными

входами третьего и четвертого аналого-цифровых преобразователей, выходы которых соответственно соединены с информационными входами второго регистра и первыми входами блоков умножения второй группы, управляющие входы третьего и четвертого аналогоцифровых преобразователей и второго регистра объединены и подключены к первому выходу первого генератора тактовых импульсов, разрядные выходы второго регистра соединены с вторыми входами соответствующих блоков умножения второй группы, выходы которых соединены с первыми входами соответствующих элементов И седьмой группы, вторые входы объединены и подключены к второму выходу первого генератора тактовых импульсов, выходы элементов И седьмой группы соединены с информационными входами соответствующих блоков усреднения третьей группы,- управляющие входы которых объединены и подключены к выходу первого элемента задержки, выходы блоков усреднения третьей группы соединены с первыми Входами соответс.твзтощих элементов И восьмой группы, вторые входы которых объединены и подключены к выходу первого формирователя, импульсов , выходы элементов И восьмой группы через соответствующие элементы задержки второй группы соединены с информационными входами соответствующих блоков памяти второй группы, выходы которых соединены с первыми входами соответствующих элементов И девятой группы, вторые входы которых подключены к соответствующим выходам третьего дешифратора, выходы элементов И девятой группы соединены с соответствующими входами третьего элемента ИЛИ, выход которого соединен с первыми входами с;оответствзтощих элементов И десятой группы, вторые входы которых объединены с входа ми соответствующих элементов задержки третьей группы и подключены к соответствующим выходам первого дешифратора, выходы элементов И есятой группы через соответствующие . элементы задержки четвертой группы подключены к первым входам соответствующих элементов И одиннадцатой группы, вторые входы которых подклю-. чены к выходам соответствующих элементов задержки третьей группы, третьи входы элементов И десятой

группы объединены и подключены к выходу блока сравнения, выходы элементов И одиннадцатой rpyntibi соединены с соответствующими входами четвертого элемента ИЛИ, выход которого является вторым выходом устройства, входы третьего дешифратора подключены к соответствующим разрядным выходам пятого счетчика, тактовый вход которого подключен к выходу первого элемента И, тактовый вход шестого счетчика подключен к выходу переноса четвертого счетчика, разрядные выходы шестого счетчика соединены с соответствующими входами четвертого дешифратора, вьгход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, а выход соединен с информационньм входом третьего регистра и первым входом

сумматора, выход которого соединен с управляюпр1ми входами третьего и четвертого регистров, выход третьего регистра через элемент НЕ подключен к второму входу сумматора, информационные входы четвертого регистра подключены к соответствующим разрядным выходам четвертого счетчика, а выходы соединены с соответствующим информационньн входом пятого регистра, управляняций вход которого подключен к выходу четвертого формирователя импульсов, вход которого подключен к выходу переноса шестого счетчика, ,разрядные выходы пятого регистра соединены с соответствующими входами первой группы входов блока сравнения, входы второй группы входов которого подключены к соответствующим выходам четвертого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1979 |

|

SU783799A1 |

| Устройство для определения взаимной корреляционной функции | 1984 |

|

SU1188752A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Коррелометр | 1977 |

|

SU682904A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для определения взаимной корреляционной функции | 1989 |

|

SU1689968A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1727134A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЗАИМНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ, содержащее первый аналого-цифровой .преобразователь, информационный вход которого является первым входом уст.ройства, а выходы подключены к соответствующим информационн в { входам первого регистра, разрядные выходы которого подключены к первым входам соответствующих блоков умножения первой группы, вторые входы которых объединены и подключены к выходу второго аналого-цифрового преобразователя, информационный вход которого является вторым входом устройства, а управляю1ЦИЙ вход объединен с управляющими входами первого аналого-цифрового преобразователя и первого регистра, и подключен к первому выходу первого генератора тактовых импульсов, выходы блоков умножения первой группы под-, ключены к nepBbiM. входам соответствующих элементов И перйой группы, выходы которых соединены с информационными входами соответствующих блоков усреднения первой группы, вхо,ды элементов И первой группы объединены и подключены к второму выходу первого генератора тактовых импульсов, выходы блоков усреднения первой группы соединены с первыми входами соответствующих элементов И второй группы, а управляющие входы блоков усреднения первой группы объединены и подк.гаочены к выходу первого элемента задержки, вторые входы элементов И второй группы объединены и подключены к выходу первого формирователя импульсов , а выходы элементов И второй группы через соответствующие блоки памяти первой группы соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых подключены к соответствую(Л щим выходам первого дешифратора, выходы элементов И третьей группы соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первьми входами элементов И четвертой группы, вторые входы которых объединены с входами соответствующих элементов задержки перэо вой группы и подключены к соответствующим выходам второго дешифратора, 35 выходы элементов И четвертой группы со подключены через соответствующие блоки усреднения второй группы к первым входам соответствующих элементов И пятой группы, вторые входы которых подключены к выходам соответствующих элементов задержки первой группы, выходы элементов И пятой группы соединены с соответствующими входами второго элемента ШШ, выход которого является первым выходом устройства, третий выход первого генератора тактовых импульсов через последовательно .соединенные первый счетчик и первый

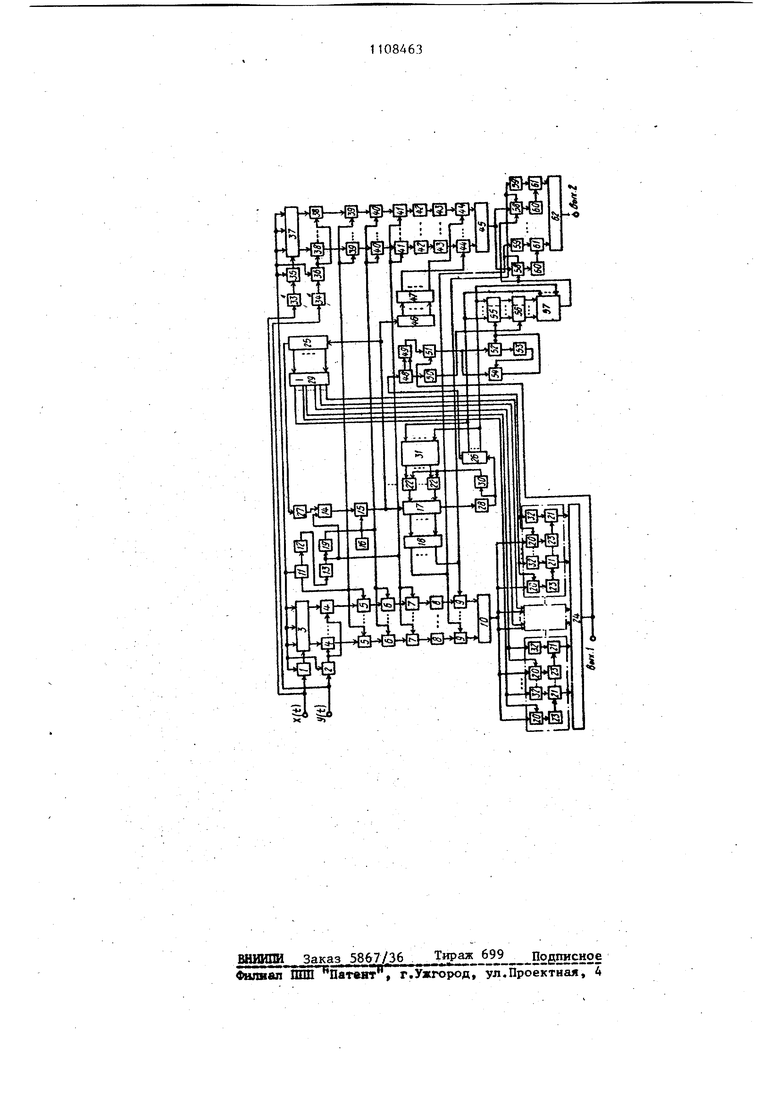

Изобретение относится к измерител ной и вычислительной технике и может быть использовано для измерения аргу мента и значения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого. Известны случаи, когда задержка между анализируемыми сигналами непре рывно изменяется, вследствие чего происходит масштабно-временное искажение принимаемых сигналов. Это при;водит к искажению форми взаимокорреляционной функции (ВКФ), в частности к уменьшению ее максимального значения и смещению его по оси г С1j. Чем больше время интегрирования Т тем больше корреляционная функция сглаживается и искажается. Известно устройство tH, в кото;ром скомпенсировано влияние линейного взаимного смещения по частоте спектро принимаемых сигналов, позво ляющее увеличивать время интегрирования без существенного искажения получаемой ВКФ. Корреляционньй анализ ведется между одним из исследуемых сигналов, принимаемым за опорный и другим, подвергнутым относительно первого масштабно-временному преобразованию, с коэффициентом, равным скорости изменения задержки . Данное устройство обладает низким. быстродействием, поэтому область его применения ограничена. Наиболее близким по технической сущности к изобретению является устройство L23, в котором компенсация искажений ВКФ осуществляется путем обработки результатов многократного корреляционного анализа с ограниченным в пределах каждого цикла временем интегрирования с последующим суммированием отсчетов частной коррелограммы, полученной в предыдущем цикле, со смещенными по оси t отсчетами коррелограмм, полученных в последующих циклах. Критерием правильности / смещения отсчетов последующих коррелограмм по оси tr является получение наибольшей величины глобального максимума ВКФ. Устройство Содержит (2(1 + 1) каналов корреляционной обработки, в каждом из которых происходит компенсация скорости изменения задержки между исследуемыми сигналами 1JO одному из возможных линейных законов за время вычисления 2 « At, где N - фактор усреднения оцен ки частной коррелограммы; Ц - количество суммирований частных оцено} ; At - временной интервал квантования входных сигналов. Однако в случае, когда поступающи на вход корреляционного приемника сигналы представлены суммой гармонической и широкополосной составляющими случайного процесса, определение глобального максимума ВКФ и соответствующего ему значения аргумента t при помощи известного устройства ста новится затруднительным, а при значи тельном превышении мощности гармони ческой составляющей над мощностью широкополосной части спектра и невоз можным. Это объясняется тем, что на выходе этого устройства ВКФ вьщелится в виде суммы гармонического и случайного процессов. Вид этой коррелограммы определяется в основном гармоническим процессом и имеет осциллирующий характер, что понижает точность определения задержки меж ду исследуемыми сигналами. Превышение амплитуды общей ВКФ в точке с ар гументом, равным искомой задержке, над остальной частью коррелограммы, а следовательно, и надежность опреде ления задержки в рассматриваемом случае зависит от соотношения амплитуд коррелограмм гармонического и случайного процессов. При относитель ном росте амплитуды гармонической составляющей или уменьшении амплитуды случайной составляющей это превышение уменьшается и может достигнуть величины, не позволяющей определить глобальньй максимум ВКФ за время Т. Цель изобретения - повьш1ение точности и упрощение устройства при ана лизе сигналов, подвергнутых масштабно-временному искажению и имеющих ярко выраженную дискретную составляю щую спектра.. Поставленная цель достигается тем что в устройство для определения взаимной корреляционной функции, содержащее первый аналого-цифровой преобразователь, информационный вход которого является первьм входом устройства, а выходы подключены к соответствующим информационным входам . первого регистра, разрядные выходьг которого подключены к первым входам соответствующих блоков умножения пер вой группы, вторые входы которых объ единены и подключены к выходу второго аналого-цифрового преобразователя, информационный вход которого является вторым входом устройства, а управляющий вход объединен с управляющими входами первого аналого-цифрового преобразователя и первого регистра и подключен к первому выходу первого генератора тактовых импульсов, выходы блоков умножения первой группы подключены к первым входам соответствующих элементов И первой группы, выходы которых соединены с информационными входами соответствующих блоков усреднения первой группы, вторые входы элементов И первой группы объединены и подключены к второму выходу первого генератора тактовых импульсов, выходы блоков усреднения первой группы соединены с первьии входами соответствующих элементов И второй группы, а управляющие входы блоков усреднения первой группы объединены и подключены к выходу первого элемента задержки, вторые входы элементов И второй группы объединены и подключены к выходу первого формирователя импульсов, а выходы элементов И второй группы через соответствующие блоки памяти первой группы соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых подключены к со ответствующим выходам первого дешифратора, выходы элементов И третьей группы соединены с соответствующими входами первого элемента РШИ, выход которого соединен с первыми входами элементов И четвертой группы, вторые входы которых объединены с входами соответствующих элементов задержки первой группы и подключены к соответствующим выходам второго дешифратора, выходы элементов И четвертой группы подключены через соответствующие блоки усреднения второй группы к первым входам соответствующих элементов И пятой группы, вторые входы которых подключены к выходам соответствующих элементов задержки первой группы, вьрсоды элементов И пятой группы соединены с соответствующими входами второго элемента ИЛИ, выход которого является первым выходом устройства, третий выход первого генератора тактовых импульсов через последовательно соединенные первый счетчик и первый формирователь импульсов соединен с входом первого элемента задержки, единичный вход триггера соединен с выходом первого формирователя импульсов, а нулевой вход подключен к выходу второго формирователя импульсов, выход триггера соединен с первым входом первого элемента И, второй вход которого под ключен к выходу второго генератора тактовых импульсов, выход первого элемента И соединен с тактовыми входами второго и третьего счетчиков, разрядные выходы второго счетчика соединены с соответствующими входами первого дешифратора, .а разрядные вхо ды начальнЬй установки подключены к выходам соответствующих элементов И шестой группы, выход переноса втор9 го счетчика через последовательно соединенные третий формирователь импульсов и второй элемент задержки соединен с первыми входами элементов И шестой группы, вторые входы ко торых подключены к соответствующим выходам блока постоянной памяти, адресные входы которого подключены к соответствующим разрядным выходам четвертого счетчика, тактовый вход которого подключен к выходу третьего формирователя импульсов, входы второ го дешифратора подключены к соответ ствующим разрядным выходам третьего счетчика, выход переноса которого соединен с входом второго формирователя импульсов, введены третий и чет вертый аналого-цифровые преобразователи, первый и второй фильтры, второй, третий, четвертый и пятый регистры, вторая группа блоков умножения, седьмая, восьмая, девятая, деся тая и одиннадцатая группы элементов И, третья и четвертая группы бло ков усреднения, вторая и третья груп пы элементов задержки, вторая группа блоков памяти, третий и четвертый элементы ИЛИ, пятый и шестой счетчики, третий и четвертый дешифраторы, четвертый формирователь импульсов, второй элемент И, сумматор, элемент НЕ, блок сравнения, причем .входы первого и второго фильтров соответственно соединены с входами перво го и второго аналого-цифровых преобразователей, а выходы соответственно соединены с информационньми входа - - .. . ми третьего и четвертого аналого-циф ровых преобразовате;1ей, выходы которых соответственно соединены с инфор мационными входами второго регистра И первыми входами блоков умножения второй группы, управляющие входы третьего и четвертого аналого-цифровых преобразователей и второго регистра объединены и подключены к первому выходу первого генератора тактовых импульсов, разрядные выходы второго регистра соединены с вторыми входами соответствующих блоков умножения второй группы, выходы которых соединены с первыми входами соответствующих элементов И седьмой группы, вторые входы объединеныи подключены к второму выходу первого генератора тактовых импульсов, выходы элементов И седьмой группы соединены с информационными входами соответствующих блоков усреднения третьей группы, управляющие входы которых объединены и подключены к выходу первого элемента задержки, выходы блоков усреднения третьей группы соединены с первьми входами соответствующих элементов И восьмой группы, вторые входы которых объединены и подключены к выходу первого формирователя импульсов, выходы элементов. И восьмой группы через соответствующие элементы задержки второй группы соединены с информационными входами соответстуующих блоков памяти второй группы, выходы которых соединены с первыми входами соответствующих элементов И девятой группы, вторые входы которых подключены к соответствующим выходам третьего дешифратора, выходы элементов И девятой группы соединены с соответствующими входами третьего элемента РШИ, выход которого соединен с первыми входами соответствующих элементов И десятой группы, вторые входы которых объединены с входами соответствующих элементов задержки третьей группы и подключены к соответствующим выходам первого дешифратора, выходы элементов И десятой группы через соответствующие элементы задержки четвертой группы подключены к первым входам соответствующих элементов И одиннадцатой группы, вторые входы которых подключены к выходам соответствующих элементов задержки третьей группы, третьи входы элементов И десятой группы объединены и подключены к выходу блока сравнеиия, выходы элемен« mrf «.-..-- у , ftr«v ii It тов И одиннадцатой группы соединены с соответствующими входами четвертого ИЛИ, выход которого является вторым выходом устройства, входы третьего дешифратора подключены к со ответствующим разрядным выходам пято го счетчика, тактовый вход которого подключен к выходу первого элемента И, тактовый вход шестого счетчика подключен к выходу переноса четвертого счетчика, разрядные выходы шестого счетчика соединены с соответ ствующими входами четвертого дещифратора, выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, а выход соединен с информационным входом тре тьего регистра и первым входом сумматора, выход которого .соединен с управляющими входами третьего и четвертого регистров, выход третьего регистра через элемент НЕ подключен к второму входу сумматора, информационные входы четвертого регистра по ключены к соответствующим разрядным выходам четвертого счетчика, а выходы соединены с соответствующими информационными входами пятого регист ра, управляющий вход которого подклю чен к выходу четвертого формировател импульсов, вход которого подключен к выходу переноса щестого счетчика, разрядные выходы пятого регистра сое динены с соответствующими входами первой группы входов блока сравнения входы второй группы входов которого подключены к соответствующим выходам четвертого счетчика. На чертеже представлена блок-схем ;устройства. Предлагаемое устройство содержит п-ра рядный аналого-цифровой npeo6pa зователь (АЦП) 1,подключенный входом к выходу первого источника сигнала i ч (i ), р-разрядный АЦП 2, подключенный входом к выходу второго источник сигналов u(i),nnn -разрядный первый регистр 3, содержащий ПН1-разрядных ячеек, пк -разрядных блоков 4 умноже ния первой группы, первую группу эле ментов И 5, первую группу блоков 6 усреднения, вторую группу элементов И 7, первз группу блоков 8 памя ти третью группу элементов И 9, пер вый элемент ИЛИ 10, первьй генератор 11 тактовых импульсов, первый счетчик Т2, первый формирователь 13 импульсов, триггер 14, элемент И 15, второй генератор 16 тактовых импульсов, второй счетчик 17, первый дешифратор 18, первый элемент 19 задержки, четвертую 20, пятую 21 и шестую 22 группы элементов И, вторую группу блоков 23 усреднения, второйэлемент ШВ-1 24, третий 25 и четвертый 26 счетчики, второй 27 и третий 28 формирователи импульсов, второй дешифратор 29, второй элемент 30 задержки, блок 31 постоянной памяти, группу элементов 32 задержки, причем каждый из выходов АЦП 1 подключен к входу соответствующей ячейки регистра 3, выходы одноименных разрядов регистров 3 подключены к соответствующим входам соответствующих блоков 4 умножения первой группы, другие входы которых поразрядно объединены и подключены к выходам АЦП 2, выход каждого блока 4 умножения первой группы подключен к первому входу соответствующего элемента И 5 первой группы, вых.оды которых соединены с информационными входами соответствующих блоков 6 усреднения первой группы, выходы которых подключены к первым входам элементов И 7 второй группы, выходы которых подключены к первым входам элементов И 9, третьей группы, выходы которых подключены к соответствующим входам первого элемента ИЛИ 10; управляющие входы регистров 3 и АЦП 1 и 2 объединены и подключены к первому выходу первого генератора 11 тактовых импульсов, второй выход которого соединен с вторыми входами элементов И 5, а третий выход генератора 11 тактовых импульсов подключен к ВХ.ОДУ счетчика 12, выход которого через первый формирователь 13 импульсов соединен с вторыми входами элементов И 7 второй группы, с единичным входом триггера 14 и через элемент 19 задержки с управ-. .ляющими входами блоков 6 усреднения первой группы, а выход триггера 14 подключен к первому входу элемента И 15, второй вход которого подключен к выходу второго генератора 16 тактовых импульсов, а выход - к тактовому входу второго счетчика 17, разрядные выхода которого через первый дешифратор 18 соединены с вторыми входами элементов И 9 третьей группы; первые входы элементов И 20 четвертой группы подключены к выходу первого элемента ШШ 10, выходы элементов И 20 через соответствующие блоки 23 усреднения второй группы подключены к первым входам элементов И 21 пятой группы, выходы которых соединены с входами второго элемента ИЛИ 24; выход элемента И 15 подключен к тактовому входу третьего счетчика 25, разрядные выходы которого через второй дешифратор 29 соединены с вторыми входами элементов И 20 четвертой группы и через элементы 32 задержки первой группы с вторыми входами элементов И 21 пятой группы, а выход переноса третьего счетчика 25 через второй формирователь 27 импульсов подключен к нуле вому входу триггера 14; выход перено са второго счетчика 17 через третий формирователь 28 импульсов подключен к так-товому входу четвертого счетчика 26, разрядные входы которого соединены с адресными входами блока 31 постоянной памяти, каждый из выходов которого,подключен к первому входу соответствующего элемента И 22 шесто группы, выход каждого из которых сое динен с входом начальной установки соответствующего разряда второго счетчика 17; вторые входы элементов И 22 шестой группы объединены и подключены к выходу третьего форми рователя 28 импульсов через второй элемент 30 задержки. Устройство содержит также первый 33 и второй 34 фильтры, третий И -разрядньй 35 и четвертый h-разрядный 36 АЦП, входы которых через фильтры 33 и 34 соединены соответственно с первым и вторым входами устройства, mn -разрядный второй регистр 37 ,т- -разрядные блоки 38 умно жения второй группы, седьмую группу элементов И 39, третью группу блоков АО усреднения, восьмую группу элементов И 41, вторую группу элемен тов 42 задержки, вторую группу блоков 43 памяти, девятую группу элемен тов И 44, третий элемент ИЛИ 45, пятый счетчик 46, третий, дешифратор 47 шестой счетчик 48, четвертый дешифра тор 49, четвертый формирователь 50 импульсов, второй элемент И 51, третий регистр 52, элемент НЕ 53,. сумма тор 54, четвертый 55 и пятый 56 регистры, блок 57 сравнения, десятую группу элементов И 58, третью группу элементов 59 задержки, четвертую группу элементов 60 задержки, одиннадцатую группу элементов И 61, четвертый элемент ИЛИ 62, причем выходы третьего 35 АЦП подключены к соответствующим входам второго регистра 37 задержки, разрядные выходы которого подключены к первым входам соответствующих блоков 38 умножения второй группы, вторые входы которых объединены и подключены к выходу четвертого 36 АЦП; выходы блоков 38 умножения второй группы подключены к первым входам соответствующих элементов И 39 седьмой группы, вторые входы которых объединены и подключены к второму выходу первого генератора 11 тактовых импульсов, а выходы соединены с информационными входами соответствующих блоков 40 усреднения третьей группы, управляющие входы которых объединены и подключены к выходу первого элемента 19 задержки, а выходы - к первым входам элементов И 41 восьмой группы, вторые входы которых объединены и соединены с выходом первого формирователя 13 импульсов, а выходы подключены к соответствующим входам элементов 42 задержки второй группы, выход каждого из которых подключен к информационньм входам соответствующих блоков 43 памяти второй группы, выход каждого из которых соединен с соответствующими первыми входами элементов И 44 девятой группы, выходы которых подключены к соответствующим входам третьего элемента ИЛИ 45; управляющие входы второго регистра 37, третьего 35 и четвертого 36 АЦП объединены и подключены к первому выходу первого генератора тактовьгх импульсов; выход переноса четвертого счетчика 26 подключен к тактовому входу шестого счетчика 48, разрядные выходы которого подключены к соответствующим входам четвертого дешифратора 49, выход которого соединен с первым входом второго элемента И 51, второй вход которого подключен к выходу второго элемента ИЛИ 24, а выход - к информационному входу третьего регистра 52, выход которого соединен с входом элемента НЕ 53, выход которого подключен к соответствуюп(ему входу сумматора 54, другой вход которого подключен к выходу второго элемента И 51, а выход сумматора 54 соединен с управляющим входом третьего регистра 52, вход четвертого формирователя 50 импульсов подключен к выходу переноса шестого счетчика 48, а выход является управляющим входом пятого регистра 56, информационные входы которого соединены с соответствующими разрядными выходами четвертого счетчика 26, тактовый вход счетчика 46 подключен к выходу первого элемента И 15, а разрядные выходы соединены с соответствзпощими входами третье го дешифратора 47, выходы которого подключены к вторым входам соответствующих элементов И 44 девятой груп пы; входы первой группы входов блока 57 сравнения подключены к соответствующим разрядным выходам пятого регистра 56, входы второй группы, входы блока 57 сравнения соединены с соответствующими разрядными выхода ми четвертого счетчика 26, а выход подключен к соответствзпощему входу каждого из элементов И 58 десятой группы, другие входы которых объединены и подключены к выходу третьего элемента ИЛИ 45, а последние входы соединены с соответствующими разрядными выходами первого дешифратора 18 выход каждого из элементов И 58 десятой группы подключен к входу Соответствующего блока 60 усреднения четвертой группы, выход каждого из которых соединен с первым входом соответствующего элемента И из элементов И. 61 одиннадцатой группы, второй вход из которых подключен к выходу соответствующего элемейта 59 задержки третьей группы, входы каждого из которых соединены с соответствующими разрядными выходами первого дешифратора 18; выходы каждого из элементов И 61 одиннадцатой группы подключены к соответствующим входам четвертого элемента ИЛИ 62. Принцип работы предпагаемого устройства заключается в следующем. За время одного цикла T N -5ut в .устройстве вычисляется 2. частных оценок, получаемых в результате крат ковременного корреляционного анализа между сигналами, представленными суммой гармонического и случайного процессов. Определение каждой частной оценки в устройстве происходит с фактором усреднения таким, что вьгаолняе.тся условие С2 где - максимальная ожидаемаяскорость изменения задержки; а - постоянная напер(д задан ная величина. За время определения одной частной оценки N/1 At задержка между входг ными сигналами очевидно может измениться на величину, не превышающую а-At, т.е. каждая следующая частная оценка может быть смещена относительно предыдущей по оси i на интервал, по абсолютной величине не превышающей а -л t. Реализуя при усреднении частных оценок различные варианты смещений каждой последующей оценки относительно предьщущей, устройство одновременно строит несколько моделей компенсации изменения задержки между входными сигналами. Полагая, что за время одного цикла скорость изменения задержки остается постоянной, на первом выходе устройства в конце цикла вычисления можно получить (2&+1) результирующих коррелограмм, каждая из которых отвечает определенной модели линейной скорости изменения задержки Vt, находящейся в интервале C-Vttnqy ; (. Если за время одного цикла задержка между входными сигналами изменилась на величину iAt, где i принимает значение от -t до +С , то скорость изменения задержки за это время составит , тогда i-я результирующая коррелограмма, состоящая из суммы гармонического и случайного процессов, будет иметь большую амплитуду косинусоиды, чем иные результирующие коррелограммы. По окончании каждого цикла происходит определение и запоминание закона, по которому происходило вычисление данной коррелограммы. В следующем цикле в многоканальной части устройства проис- , ходит вычисление следующих (2G+1) результирующих коррелограмм входных ; сигналов и определение нового значения скорости изменения задержки,„а в одноканальной части вычисляются частных оценок коррелограммы между задержанными за время одногоцикла входными сигналами с вырезанной дискретной составляющей спектра, которые суммируются по закону, определенному в предыдущем цикле в многоканальной части устройства. Таким образом, по окончании каждого цикла в устройстве определяется закон изменения задержки, по которому в еледующем цикле происходит усреднение частных оценок в его. одноканальной части. Процесс накопления продолжается до тех пор, пока на выходе одйоканальной части устройства не вцпелится коррелограмма, у которой ВКФ имеет глобальный максимум. Устройство работает следующим образом. Сигнал x(t) поступает на вход АЦП 1 и в момент поступления импульса с первого выхода генератора 11 тактовых импульсов преобразуется в соответствующий ivi-разрядны двоичный код, который поступает на входы регистров 3, выполняющих функцию цифровой линии задержки. Длина каждого из VYI регистров 3 опре деляется требуемой задержкой и коли чество частных оценок (i , At .где Туутду. требуемое время задержки. По мере поступления каждого ново го импульса с первого выхода генера тора 11 тактовых импульсов (ГТИ) ко ды входного сигнала продвигаются вправо по ячейкам регистра 3. Отсче ты сигнала с выхода каждой ячейки регистра 3 поступают на первые входы соответствующего блока 4 умножения. На вторые входы блока 4 умноже ния поступает код сигнала y(t) с выхода второго .АЦП 2. Синхронное поступление кодов с выхода АЦП 1 обеспечивается управляющими импульсами, формируемыми ГТИ 11. На выходе к,-го блока 4 умножения формирует код, равный произведению x(t-HAt)y(t), где A.t - период следования сдвигающих импульсов. Код произведения синхронно с так товыми импульсами, вырабатываемыми на втором выходе ГТИ 11, передается через К-й элеменя- И 5 на соответствующий блок 6 усреднения. Усреднени элементарных произведений в каждом блоке 6 усреднения продолжается до тех пор, пока не возникнет сигнал переполнения счетчика 12 с выхода переноса на выходе формирователя 13 импульсов. Емкость счетчика 12 равна выбран ному для частной оценки фактору усреднения Ни С возникновением импульса переполнения счетчика 12 на выходе формирователя 13 импульсов о крываются элементы И 7, и результат усреднения, сформировавшиеся в блоках 6 усреднения, зашсыпаются в бл ки 8 памяти. При этом блоки 6 усреднения обнуляются с задержкой, определяемой элементом 19 задержки. В течение следующих NI импульсов, поступающих с третьего выхода генератора 11 тактовых импульсов, происходит вычисление следующей частной оценки и т.д. Работа накопителя частных оценок многоканальной части аналогична работе накопителя устройства Е21. ;В блоке 31 постоянной памяти хранится программа изменения значения скорости изменения задержки, а команды на его выходе возникают при подаче кодов с выходов счетчика 26 (адресного). В исходном состоянии, которое продолжается до момента записи первой частной оценки, счетчики 1, 25 и 26 обнулены.. Импульс перевыполнения, поступающий с выхода формирователя 13 импульсов в конце вычисления очередной частной оценки, устанавливает триггер 14 в состояние 1. Импульсы от ГТИ 16 через элемент И 15 начинают поступать на тактовый вход счетчика 17,, емкость которого равна числу ординат частной оценки. По мере заполнения счетчика 17 дешифратор 18 синхронно.с частотой генератора 16 тактовых импульсов открывает элементы И 9 начиная с первого и кончая п-м, и значения п ординат частной оценки последовательно поступают на выход элемента ИЛИ 10. Импульсы генератора 16 тактовых импульсов через элемент И 15 поступают также на тактовый вход счетчика 25, емкость которого равна п(22 + 1). Дешифратор 29, подключенный к разрядным выходам счетчика 25, за первые п тактов открывает последовательно первые п элементов И 20 и значения ординат частной оценки заносятся соответственно в первые п блоков 23 усреднения. Сигналы дешифратора .29 поступают также на входы элементов 32 задержки . Величина задержки элементов 32 выбрана такой, чтобы .к моменту появления сигнала на выходе i-ro элемента 32 задержки переходные процессы в i-M блоке 23 усреднения были закончены. Задержанные на элементах 32 задержки сигналы дешифратора 29 открывают последовательно элементы И 21 и результаты усреднения из первых п блоков 23 усреднения поступают на выход элемента ИЛИ 24. После того, как счетчик 17 полностью заполнится, следующий импульс, пришедший на его вход, обнулит его, а сигнал переполнения, сформированный формирователем 28 импульсов, прибавит единицу к содержимому счетчика 26, емкость кото рого равна количеству моделей изменения скорости изменения задержки Vt между входами сигналов, и для рассматриваемого случая составляет (22-+1). На выходах блока 31 постоянной памяти возникает первая команда, которая для рассМатриваемого случая представлена нулевым кодом. Сигнал переполнения с выхода формирователя 28 импульсов проходит через элемент 30 задержки и открывает элементы И 22. Код команды с в . ходов блока 31 постоянной памяти по ступает на разрядные входы начально установки счетчика 17 и устанавлива ет его в состояние, равное коду команды. Величина задержки на элемент 30 задержки выбрана такой, что бы к моменту открытия элементов И 2 переходные процессы в счетчике 26 и блоке 31 постоянной памяти были за ончены, а (п+1)-й импульс от генератора 16 тактовых импульсов еще не поступил на вход счетчика 17. С поступлением следующих п импульсо с выхода генератора 16 тактовых импульсов происходит последовательное занесение ординат частной оценки, которые хранятся в блоках 8 памяти, через элемент ИЛИ 10 в соответствую щие п блоков второй подгруппы блоков 23 усреднения. Таким образом, в течение одного цикла значения орд нат первой частной оценки записываю ся в (21+1) подгруппах блоков 23 усреднения. Результаты усреднения че рез элемент ИЛИ 24 последовательно вьюодятся на первый выход устройства. После того, как на вход счетчика 25 поступит п(211+1) импульсов генератора 16 тактовых импульсов, на формирователе 27 импульсов возникает сигнал переполнения счетчика 25 и устанавливается в состояние О триг гер 14. Элемент И 15 закрывается и прекращает поступление импульсов генератора 16 тактовых импульсов на входы счетчиков 17 и 25, Частота следования И14пульсов генератора 16 тактовых импульсов выбрана такой, чтобы п() импульсов были выработаны за время определения одной частной оценки, т.е. за время, не превышающее период Ny формирования импульсов ГТИ 11. Вычисление второй и последующих частных оценок происходит аналогично вычислению первой оценки.. По окончании очередного цикла, в котором вычисляется новая частная оценка и заносится значение предыдущей частной оценки в блоки 23 усреднения, очередная оценка записывается в блоки 8 памяти, а сигнал переполнения счетчика 12 через формирователь 13 устанавливает триггер 14 в состояние 1. Импульсы генератора 16 тактовых импульсов через схему И 15 начинают поступать на вход счетчика 17, котррьй совместно с дешифратором 18, формирователем 28 импульсов, элементом 30. задержки, счетчиком 26, блоком 31 постоянной памяти, группами элементов: К 22, И. 9 управляет смещением последующих частных оценок относительно предьщущих. По окончании малого цикла, в котором значения частной оценки заносятся в очередные п блоков 23 усреднения, на выходе блока 28 импульсов формируется импульс переполнения счетчика 17 и происходит модификация состояния счетчика 26 на +1. На входах блока 31 постоянной памяти появляется очередная команда, содержание которой равно величине сдвига очередной частной оценки относительно первой. Сигнал переполнения счетчика 17, задержанный на элементе 30 задержки, предустанавливает счетчик 17 в состояние, равное величине смещения. При поступлении на вход счетчика 17 частоты от ГТИ 16 дешифратор 18 открывает последовательно элементы И 9, начиная с того, номер которого соответствует величине смещения, например второго элемента И 9. На выход элемента ИЛИ 10 последовательно поступают значения ординат частной оценки, начиная со второй. Дешифратор 29 синхронно с частотой ГТИ 16 открывает элементы И 20, начиная с (п+1)-го. Таким образом, вторая ордината очередной частной

оценки, поступая на вход (n-t-l)-ro блока 23 усреднения, складывается с первой ординатой предьщущей частной оценки и т.д. По окончании второго малого цикла состояние счетчика 26 изменяется на +1, блок 31 постоянной памяти формирует команду, инициирующую сдвиг очередной частной оценки на следующую величину и т.д. Таким образом, блок 31 постоянной памяти позволяет реализовать различные величины смещений очередной частной оценки относитель но первой.

По окончании второго цикли в блоках 23 усреднения сформированы (211 + 1) группы сумм двух частных оценок, причем вторые частные оценки в зависимости от принятых моделей скорости изменения задержки смещены по оси С на величины -au.t; 0; +a.A.t. Аналогичным образом многоканальная часть устройства - циклов, которые составляют, один большой цикл. За время большого цикла в блоке 23 усреднения формируется п(2Й1-1) сумм частных оценок в каждой сумме, т.е () результирующих коррелограмм п ординат.

Вычисление п ординат частной оценки в рдноканальной части устройства происходит аналогично определению значений частной оценки в его многоканальной части. Входные сигналы x(t) и y(t) через фильтры 33 и 34 (заградительные), настроенные на частоту гармонической составляющей сигналов, поступают на входы АЦП 35 и 36, в которых происходит их квантование с той же частотой, что и в АЦП и 2. С вьпсода АЦП 35 т-разрядный код поступает на входы регистров 37 ис приходом очередного импульса с первого выхода ГТИ 11 продвигается по ним вправо. С выхода каждого регистра 37 отсчеты сигнала поступают на первые входы соответствуклцего блока 38 умножения, а на вторые его входы поступают коды АЦП 36. Сформированные элементарные произведения с выхода каждого блока 38 умножения через элементы И 39 синхронно с тактовыми импульсами, вьфабатываемыми на втором выходе ГТИ 11, передаются на соответствующие блоки 40 усреднения. В блоках 40 усреднения происходит усреднение элементарных произведений входных сигналов с фактором

.N/(, который определяется емкостью счетчика 12. После формирования сигнала переполнения счетчика 12 результаты усреднения через элементы И 41 поступают на входы соответствующих элементов 42.задержки. Величина задержки в элементах 42 задержки определяется периодом вьтолнения одного большого Цикла и равна f Л t. Задержанные отсчеты сформированной частной оценки записьтаются в блоки 43 памяти и через элементы И 44 последовательно поступают на выход элемента ИЛИ 45. Управление передачей ординат частной оценки на выход элемента ИЛИ 45 осуществляет счетчик 46 совместно с дешифратором 47, которые аппаратурно реализованы аналогично счетчику 17 и дешифратору 18. Таким образом, в тот момент, когда в блоках 43 памяти хранятся ординаты i-й частной оценки, в блоках 8 памяти записаны отсчеты (i+O-й частной оценки. Передача j-ro отсчета частной оценки, записанного в блоках 43 памяти, на выход элемента ИЛИ 45 происходит синхронно с выводом j-ro отсчета частном оценки, записанного в блоках 8 памяти, на выход элемента 10.

По окончании каждого цикла занесения значений ординат очерёдной частной оценки в блоки 23 усреднения происходит обнуление счетчика 26, а сигнал его переполнения поступает на счетный вход счетчика 48, которьй в начале работы устройства находился в состоянии О, и модифицирует его состояние на +1, В момент, когда счетчик 48, емкость которого 2, установился в состояние (1-1) ив блоках 23 усреднения закончилось усреднение (il-1) частных оценок, на выходах дешифратора 29 возникнет разрешающий потенциал, по которому откроется элемент И 51 ип(2С+1) значений ординат усредненных () результирующих коррелограмм последовательно поступят на вход экстремального анализатора, в состав которого входят регистр 52, элемент ДБ 53 и сумматор 54. Очередной отсчёт ординаты каждой результирукщей коррелограммы, представленный га-разрядным кодом,

5 поступает на первый вход сумматора 54. На второй его вход поступает инвертированный элементом И 53 код второго слагаемого, записанного в регистре 52, которьй в начале работы устройства обнулен. В сумматоре 54 прои ходит сложение двух т-разрядных двои ных чисел. При этом, если код ордина ты, записанный в регистре 52, меньше кода, поступающего на первый вход сумматора 54, то на выходе переноса старшего разряда сумматора 54, являю щегося выходом экстремального анализатора, возникает импульс, по которо му произойдет занесение кода поступившей ординаты в регистр 52. В противном случае, если входной отсчет меньше кода, записанного в регистре 52, или равен ему, то на выходе экстремального анапизатора импульс н возникает и информация, хранящаяся в регистре 52, сохраняется до прихода кода следующей ординаты. Одновременно с записью очередного отсчета в регистре 52 в регистр 55 заносится код, соответствующий состоянию счетчика 26 в этот момент времени. Таким образом, в конце каждого большого цикла в регистре 52 содержится код одной из п(2(1+1) ординат, котора имеет максимальное значение, а в регистре 55 записано состояние счетчика 26, которое соответствует номеру модели скорости изменения задержки, при которой происходит наилучшая ком пенсация изменения задержки за время вьшолнения данного большого цикла. При поступлении следующего и-го импульса йа вход счетчика 48 произой дет его обнуление, а до сигналу пере полнения, сформированному формирователем 50 импульсов, код с выхода регистра 55 запишется в регистр 56, в jcbTopOM он будет храниться на протяжении следующего большого цикла. .Записанный в регистре 56 код подается на группу входов блог ка 57 сравнения, где он сравнивается с кодом, соответствующим состоя нию счетчика 26. При совпадении этих кодов на выходе блока 57 сравне ния формируется потенциал, который является разрешающим для элементов И 58. Очевидно, что в пределах одного большого цикла совпадение кодов на входах блока 57 сравнения произойдет Q раз. При совпадении кодов регистра 56 и состояния счетчика 26 i-й отсчет частной оценки, хра нящийся на i-M блоке 43 памяти, зано сится в i-й блок 60 усреднения. Если при этом счетчик 26 находился в К-м состоянии, то при втором и последующих совпадениях кодов регистра 56 и счетчика 26 в i-й блок 60 усреднения поступит ордината с того блока 43 памяти, номер которого задается блоком 31 постоянной памяти, счетчиком 17 и дешифратором 18. Закон, по которому происходит усреднение отсчетов частных оценок в элементах 60 задержки в последующем большом цикле, совпадает с законом построения К. -и результирующей коррелограммы в K-M канале многоканальной части устройства в предыдущем большом цикле. Если в следующем большом цикле в регистр 56 запишется код, соответствующий (К + 1)-му состоянию счетчика 26, то в очередном большом цикле устреднение отсчетов в блоках 60 усреднения происходит по закону, соответствующему (к+1) -и модели Vt и так далее. Сигналы дешифратора 18, которые управляют элементами И 58, поступают также на входы элементов 59 задержки. Величина задержки элементов 59 задержки выбрана такой, чтобы к моменту появления сигнала на выходе i-ro элемента 59 задержки переходные процессы в V-M блоке усреднения бьши закончены. Задержанные на элементах 59 задержки сигналы дешифратора 18 открьшают последовательно элементы И 61 и результаты усреднения из блоков 60 усреднения через элемент ИЛИ 62 поступают на второй выход устройства. Процесс усреднения в блоках 60 усреднения продолжается до тех пор, пока на втором вькоде устройства в результирукнцей коррелограмме не будет присутствовать глобальный максимум. Значение 2, при котором наблюдается глабальный максимум, является искомой задержкой между приходящими на вход устройства сигналами x(t) и y(t). Предлагаемое изобретение применяется в том случае, когда поступаюие на вход корреляционного приемника сигналы S(t) состоят из гар-, онического S(t) и случайного S.2.(t) процессов, причем процесс S(t) по ощности значительно превосходит проесс ). При использовании известного устройства 1:2 J при общем времени анализа 1/ в канале, в котором ассчитываемая модель совпадает с законом изменения задержки между исслеуемыми сигналами, ввделяется результирующая коррелограмма. Вид этой коррелограммы определяется в основном процессом Sy((t) и имеет осцил- лирующи характер, что не позволяет однозначно определить задержку между исследуемыми сигналами. В силу того что S(t)S2(t), дальнейшее увеличение времени усреднения не дает улучшения результата, так как общий вид результирующей коррелограммы остается прежним. При относительном росте амплитуды гармонической состав ляющей S(t) процесса S(t) или умень шении амплитуды его случайной состав ля1ацей S2(t) превышение ВКФ в точке с дргументом, равным искомой задержке, над остальной частью коррелограм мы уменьшается и может достигнуть величины, не позволяющей определить максимум ВКФ. Это уменьшает точность и надежность при измерении задержки известным устройством. По сравнению с известным t:2;j предлагаемое устройство позволяет су щественно сократить аппаратурные затраты при анализе сигналов с изменяю щейся в процессе измерения задержкой имеющих ярко вьфаженную дискретную составляющую спектра. Расчет экономии оборудования при применении предлагаемого устройства произведен для случая, когда величина максимума коррелограммы случайной составляющейменьше амплитуды косинусоидальной составлянлцей в п раз. После взаимной корреляционной обработки принимаемых сигналов (с ограниченным величиной Допплера временем усреднения Т/, ) выходной отсчет RCtr) частной коррелограммы будет пропорционаленRCt-) а+е-,(1) где а - пропорционально математическому ожиданию ординаты измеряемой взаимной корреляционной функции; случайная величина, определя ющаяся величиной принимаемьк в полосе сигналов помех. В рассматриваемом случае предполагается, что Т;| недостаточно велико, и а .fc, Согласно С отношение сигнал/помеха в одной частной коррелограмме можно выразить как с -|rv : где f средний квадрат помехи. ОЬерации, применяемые как в прототипе, так и в предлагаемом изобретении при сложении отсчетов частных коррелограмм, эквивалентны применению метода накопления С 31. После сложения N отсчетов частных коррелограмм (с учетом компенсации задержки между принимаемыми сигналами и скорости ее изменения) выходной отсчет результи- р нлцей (выходной) ВКФ пропорционален Kla-1-l i.. - (2) Первьй член (2) выражает полезный .сигнал, втор-ой - помеху. Взяв средние квадраты обоих членов, составим отношение сигнал/помеха 1Ж . По условиям проводимых измерений независимы. Поэтому . т.е. при К - кратном сложении отсчетов, частных коррелограмм отношение сигнал/помеха возрастает в Ы раз. Однако при пров,одимых измерениях важен не только сам факт обнаружения сигнала, но и вид измеряемой взаимокорреляционной функции, т.е. количественное превьшгение усредненного результата Q над средним усредненным значением помехи S. В этом случае выигрыш от VI -кратного сложения отсчетов частных коррелограмм пропорционален . Таким образом, чтобы увеличить превьш1ение максимума измеряемой ВКФ над уровнем помех в ЧкГ раз, необходимо сложить К отсчетов частных коррепограмм. При этом фактор усреднения увеличится в раз. Количество моделируемых каналов, а с ним и количество оборудования прямо пропорционально фактору усреднения, в данном случае Н. В рассматриваемом примере величина максимума ВКФ случайной составляющей меньше величины косинусоидальной составлякядей в п раз. Это значит, что для того, чтобы достигнуть одинакового превьшения максимума коррелограммы над урЪвнем помех как по гармонической составляющей, так и по широкополосной составляющей, фактор усреднения по каждой из них

23 1108А6324

необходимо брать раэньм. В рассмат-чем в прототипе. Например, при

,риваемом примере фактор усредненияколичество каналов корреляционной

косинусовдальной составляющей надообработки уменьшится приблизительно

брать в п раз меньшим (так как самав 25 раз, что оправдывает введение

косинусрндальная составлякицая в п5 дополнительных элементов, составляюраз больше случайной) . Следователь-,ьщх одноканальную часть системы

но, и аппаратурные затраты в предла-(блоки 35-45, 58-61) и дополнительгаемом устройстве«VB п раз меньше,ную схему управления (блоки 46-57).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Основы радиотехники | |||

| Связьиздат, 1962, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

Авторы

Даты

1984-08-15—Публикация

1983-02-08—Подача