Изобретение предназначено для использования в автоматике и вычислительной, технике, а также в высокочувствительных быстродействующих цифровых измерительных системах, работающих в широком динамическом диапазоне входных сигналов.

Известны функциональные преобразователи напряжения в двоичный код, совмещающие операции преобразования и получения функциональной зависимости, например логарифмической, в одном устройстве. ,

Недостатком таких устройств является малое быстродействие.

Известен логарифмический преобразователь напряжения в двоичный-код, содержащий последовательно соединенные каскады преобразования, каждый из которых выполнен на управляемом усилителе и компараторе, входы которых объединены и являются входом каскада, выход управляемого усилителя является выходом каскада, вход управления усилителя соединен с выходом компаратора. Обладая более высокимбыстродействием.этот преобразователь имеет недостаточную точность преобразования из-за высокого уровня коммутационной помехи и

нестабильности коэффициента усиления управляемого усилителя.

Известно устройство, состоящее из п последовательно включенных каскадов преобразования, каждый из которых содержит триггер Шмитта (компаратор) и последовательно соединенные инвертирующую схему, управляемый аттенюатор и усилитель, причем вход триггера Шмитта соединен с входом инвертирующей схемы, а выход - с вторым входом усилителя, выход которого соединен с входом триггера Шмитта последующего каскада,

Данное устройство реализует принцип построения преобразователей на базе непрерывно-логических функций (НЛФ), заключающихся в построении {г-1) НЛсб (г разрядность выходного кода), однозначно связанных с уровнем входного сигнала, переменным наклоном восходящих участков и дешифрации их признаков,

Этот преобразователь обладает высоким быстродействием, более прост в настройке из-за отсутствия усилителей с управляемым коэффициентом усиления, и, так как, неуправляемый усилитель более стабилен по коэффициенту усиления, чем управляемый, имеет более высокую точность преобразования. Однако из-за высокого уровня коммутационной помехи точность преобразования такого преобразователя недостаточно высока. Это особенно проявляется (худший случай) при формировании кода 1000.,,0(появление 1 на выходе каскада преобразования), когда каскады возвращаются в исходное состояние, т.е. работают с максимальными коэффициентами усиления. При этом коммутационная помеха, обусловленная срабатыванием триггера Шмитта, с управляемого аттенюатора будет усиливаться в Ко раз:

Ко Ki-K2...Kn,

где Ki,K2.-.Kn - коэффициенты усиления усилителей, а уровень помехи (Un.(n-n), Un.n, ... Un.2) на входе триггеров Шмитта будет определяться соответственно соотношениями;

Un.(n-H) Un.ui К4.Г K4.2.,.K4.n Un.rt Un.mK4.rK4.2,,.K4.(n-1)

(1) Un...1

где Un.uj -уровень коммутационных помех, обсуловленных работой триггера и аттенюатора на входе усил ите л я. .

Сравнительно высокий уровень помехи на входах триггеров Шмитта

.() ип.шК4.гК4.2,,,К4.п

Un.n ип.шК4.гК4.2.,,К4(п-1)(1)

Un..mK4.l

обуславливает невысокую точность преобразования преобразователя.

Цель изобретения - повышение точности преобразования логарифмического преобразователя напряжения в двоичный код путем снижения уровня коммутационной помехи,

Поставленная цель достигается тем, что логарифмический преобразователь напряжения в двоичный код, содержащий п последовательно соединенных каскадов преобразования, каждый из которых выполнен на компараторе, управляемом аттенюаторе и усилителе, выход которого в каждом

5 1-м, кроме первого, является выходом 1-го каскада преобразования, а вход соединен с выходом управляемого аттенюатора, вход компаратора является входом соответствующего каскада преобразования, выход последнего каскада преобразования соединен с входом компаратора младшего разряда, выход компаратора каждого i-ro каскада преобразования подключен к управляющему входу управляемого аттенюатора этого каскада преобразования, выходы компараторов всех каскадов преобразования и компаратора младшего разряда являются шинами соответствующих разрядов выходного кода, в первый каскад преобразования введены элемент задержки, блок логического сложения с выбором максимального уровня сигнала, дополнительный усилитель, а управляемый аттенюатор в первом каскаде выполнен на электронном ключе, управляющий вход которого является управляющим входом управляемого аттенюатора, информационный вход электронного ключа подключен к выходу элемента задержки, вход которого объединен с входом компаратора и соединен с выходом усилителя, вход которого является входной шиной и объединен с входом дополнительного усилителя, выход которого соединен с первым входом блока логического сложения

5 с выбором максимального уровня сигнала, второй вход которого соединен с выходом электронного ключа, а выход является выходом первого каскада Преобразования, при этом в каждом 1-м каскаде преобразования.

0 кроме первого, вход компаратора объединен с информационным входом управляемого аттенюатора.

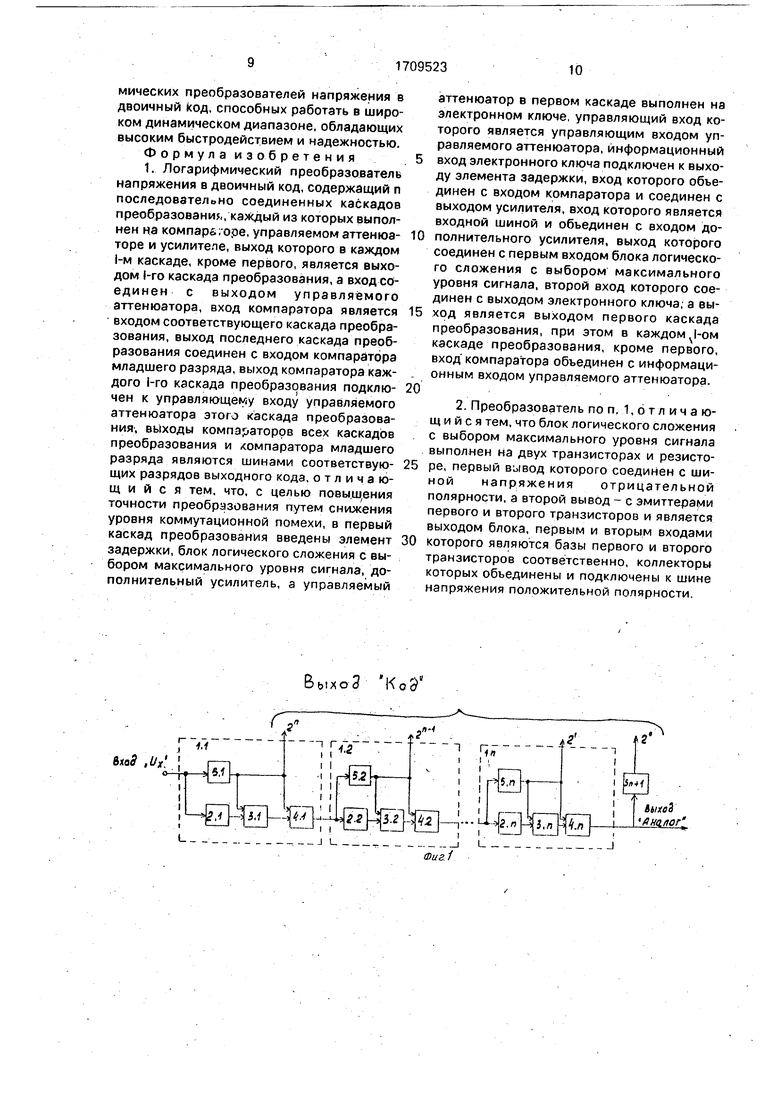

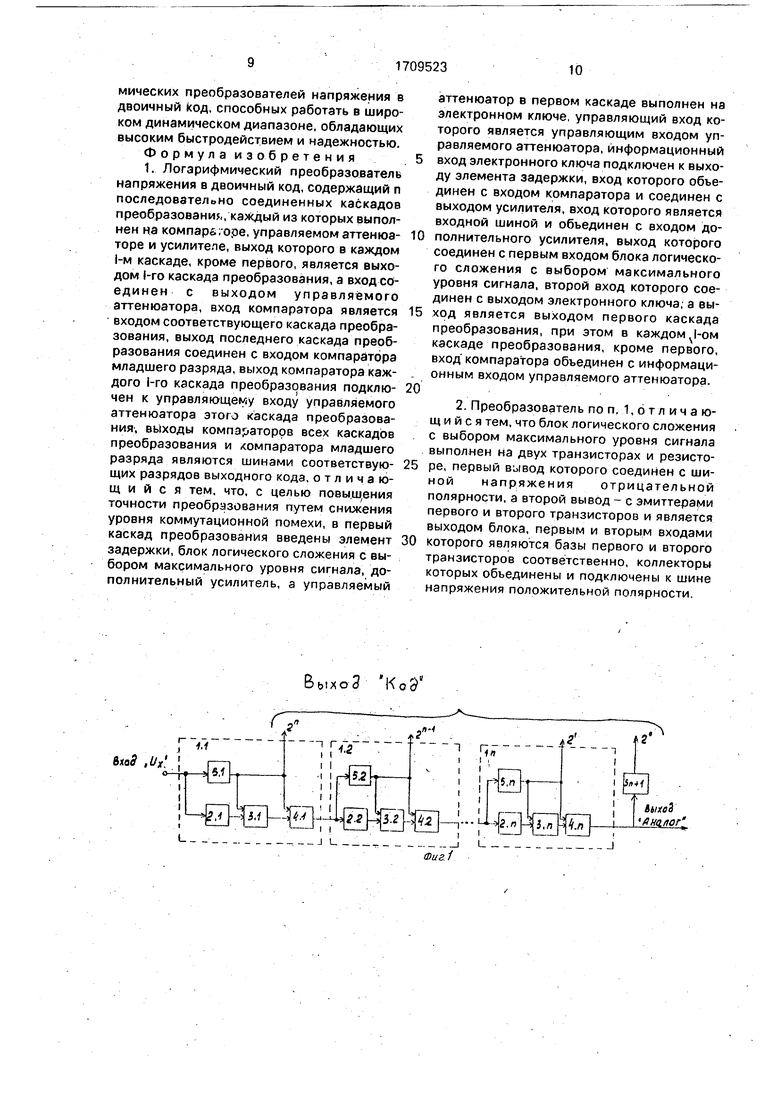

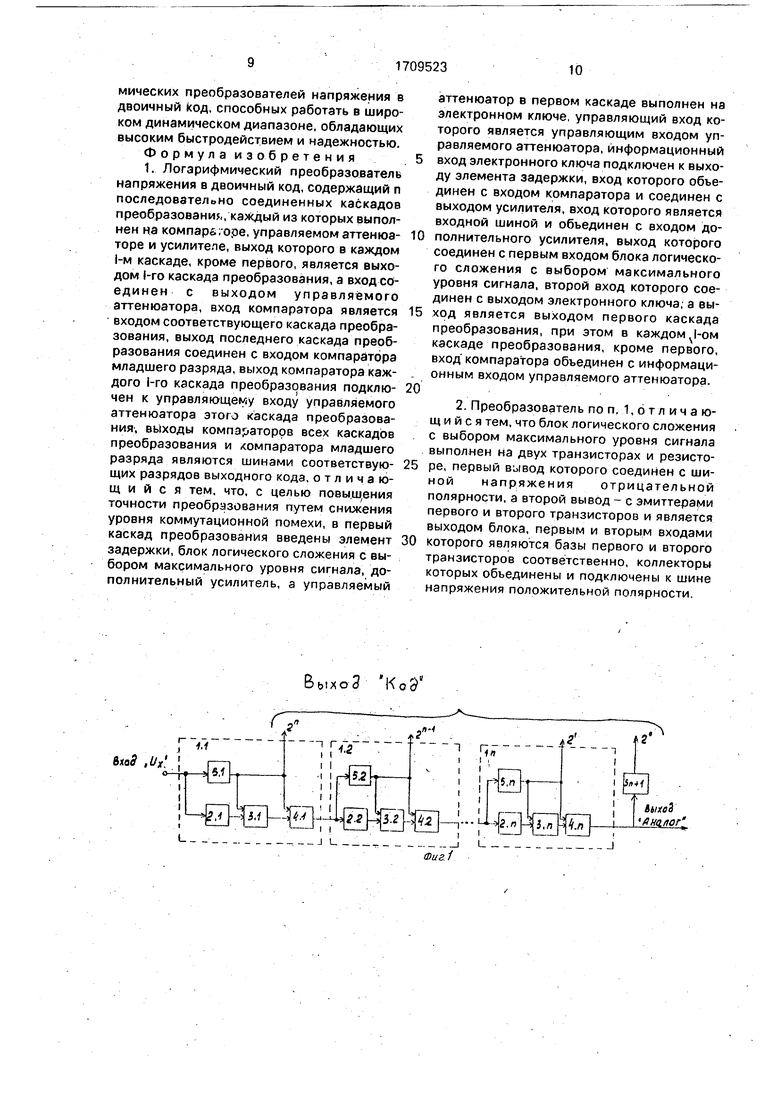

На фиг, 1 приведена структурная схема прототипа: на фиг. 2 - структурная схема

5 предлагаемого преобразователя; на фиг, 3 структурная схема трехразрядного преобразователя; на фиг. 4 - схема электрическая принципиальная первого каскада преобразования, используемого в составе логарифмическогоаналого-цифрового

преобразователя; на фиг. 5, б - эпюры напряжений в контрольных точках.

Устройство (фиг. 1) содержит п каскадов преобразования (1.1..,1,п), каждый из которых содержит последовательно соединенHue инвертирующий элемент (2.1..,2,h), управляемый аттенюатор (3.1...З.п) и усилитель (4.1...4.п), а также компаратор (5.1...5,п), вход которого подключен к входу каскада преобразования, а выход - к входу управления аттенюатора и второму входу усилителя.

Устройство (фиг. 2) состоит из п последовательно соединенных каскадов преобразования (1.1 1.2...1.п), каждый из которых содержит компаратор (2.1, 2.2...2.п), выход которого соед1 нен с управляющим входом управляемого аттенюатора (З....3.п), и усилитель (4.1,4.2... 4.п), при этом первый каскад преобразования 1.1 дополнительно содержит второй усилитель 5, вход которого объединен с входом первого усилителя 4.1 и входом преобразователя, элемент 6 задержки, вход кЬторого соединен с выходом первого усилителя 4.1 и входом компаратора 2.1, а выход - с сигнальным входом уп- равляемого аттенюатора 3.1, и схему 7 логического сложения с выбором максимального уровня, первый вход которой поД ключен к выходу управляемого аттенюатора 3.1 второй-к выходу второго усилителя 5, а выход является выходом первого каскада преобразования 1.1, причем в остальных каскадах преобразования 1,2,1.3,.1.п входы компараторов 2.2,2.3...2.п соединены с сигнальными входами управляемых аттенюаторов 3.2,3.3...З.п.

Работу устройства рассмотрим на примере трехразрядного преобразователя, содержащего два каскада преобразования 1.1,1.2 и компаратор 2.3 (фиг. 3).

В исходном состоянии коэффициенты передачи управляемых аттенюаторов 3.1,3.2. равны 1, а коэффициенты усиления усилителей 4.1,4.2 соответственно равны Ki,

К2.

При достижении сигналом уровня Ui амплитуда сигнала на входе компаратора 2.3 (ивх.з) будет равна его порогу срабатывания (Un.3).

UBx.3 UrKrK2 Un.3.

Сформируется код 001.

При входном сигнале Ua (3 Ui (где 5

U2 из Un,

y- Tj- ... ц -дискрет квантования)

уровень сигнала на входе компаратора 2.2 (Овх.а) будет равен его порогу срабатывания (Un.2).

UBx.2 U2-Ki UrdKi Un.2.

При этом по сигналу с выхода компаратора 2.2 скачкообраэно в 5 раа уменьшает ся коэффициент передачи аттенюатора 3.2.

Уровень сигнала Uax.a станет равным l UiKiK2

Un3/(5

UBX.3-U2-Kl.-V-K2

Так как Ивх-З. UM-S. то компаратор 2.3 возвратится в исходное состояние, Сформируется код 010.

При уровне входного сигнала Уз амплитуда сигнала на входе компаратора 2.3 станет равной

ивх.з из-Кг-Ь К2 Ui KiK2 Un3-.

о

сформируется код 011.

При уровне входного сигнала U4 5 Ui амплитуда сигнала на входе (омпаратора 2.1 (UBX.I) будет равна его порогу (Un.i).

Uex.l Щ Ki Ui Un.T.

По импульсу с выхода компаратора 2.1 запрещается прохождение сигнала через управляемый аттенюатор 3.1, что достигается выполнением его на электронном ключе, при этом входной сигнал будет усиливаться вторым усилителем 5 (с коэффициентом усиления Ki.2 KI/ d ) и через схему 7 логического сложения с выбором максимального уровня подаваться на вход следующего каскада 1.2. Элемент 6 задержки обеспечивает более полное выключение сигнала, снимаемого с выхода усилителя 4.1, улучшая тем самым работу преобразователя по коротким (доли секунды) импульсным сигналам.

Уровни сигналов на входах компараторов 2.2 и 2.3 следующие;

U4 Ki

Ui d Ki Un.2

ивх.2

0

U4 Kl K2 Ul(J

KiKa Un.3

UBX.3

5

Сформируется код 100.

При уровне входного сигнала Us 5 Ui

5 амплитуда сигнала на входе компаратора 2,3 будет

UBX.3 UlKiK2 Un3, а на входе компаратора 2.2,

Un.2

0

UBX.2

А

Сформируется код 101.

При уровне входного сигнала Ue U амплитуда сигнала на входе компаратора 2.2 будет

.. ( д ,, V II

UBX.2 -Т4 UlKi Un.2.

Компаратор 2.2 сработает, а по импульсу с его выхода в (5 раз уменьшится коэффиицент передачи аттенюатора 3.2, При этом амплитуда сигнала на входе компаратора 2,3 станет равной

5 UlKiK2 Un.3

UBX.3

Сформируется код 110.

При уровне входного сигнала Uy 5 U амплитуда сигнала на входе компаратора 2,3 будет

KiK2

Un.3.

UBX.S

сформируется код 111. Из приведенного описания видно, что переходная характеристика предлагаемого устройства является логарифмической, при этом уровень коммутационной помехи на входах компараторов 2,2,2,3,,,2(п+1) будет определяться выражениями:

Un.{n+1) ип.шК4.2-К4.3 ... К4.П 1

Un.n ип.ш- К4.2-Ю1.3 ... K-q(n-l) V-(2)

--- J

Un.2 Un.ui

Из соотношений (1) и (2) видно, что уровень коммутационных помех на входах компараторов 2,2,2.3,..2{n-i-1) в предлагаемом устройстве в К4.1 раз ниже, чем в прототипе. Следовательно, предлагаемое устройство в сравнении с прототипом будет обладать более высокой точностью преобразования и проще в настройке.

Предлагаемое устройство легко реализуется. Одна из возможных схем каскада преобразования 1.1 приведена на фиг. 2.

В данном варианте первый быстродействующий усилитель 4,1 выполнен на двух транзисторных дифференциальных каскадах VI...V3, V6, V8, компаратор 2,1 - на микросхеме 597СА2 (компаратор напряжения), управляемый аттенюатор 3.1 - на электронном ключе, состоящем из резистора R 24 и транзистора V11 (при закрытом V11 коэффициент передачи электронного ключа близок к 1, при открытом близок к 0). второй усилитель 5 на операционном усилителе 544УД2А и эмиттерном повторителе V5, элемент б задержки - на операционном усилителе 544УД2А и эмиттерном повторителе V9 (временная задержка сигнала в.данной схеме обуславливается ее инерционными свойствами и составляет величину 20-30 не), схема 7 логического сложения с выбором максимального уровня - на двух эмиттерных повторителях VI2, V13, работающих на общую нагрузку (R 27),

Работа схемы 7 логического сложения заключается в следующем, В исходном состоянии смещения на базе транзисторов VI2 (например 0,2-0,3) и VI3 (0,6-0,7), подаваемые с выхода второго усилителя 5 на базу V12 и с выхода электронного ключа 3,1

на базу VI3), за счет разности коэффициентов усиления усилителей 5 и 4 обеспечивают на входе каскада преобразования 1,1 напряжение, равное нулю, при этом транзистор V13 открыт, а V12 закрыт,

Сигналы с уровнем 0-Ui(Ui -соответствует срабатыванию компаратора 2.1), поступающие на вход каскада преобразования 1.1, усиливаются усилителем 4.1 и через схему 6 задержки, управляемый аттенюатор 3.1

и эмиттерный повторитель V13 поступают на выход каскада 1.1.

При уровне входного сигнала равном или большем срабатывает компаратор 2,1, транзистор V11 аттенюатора 3.1 открывается, напряжение на базе VI3 становится нулевым (V13 закрывается), открывается V12, на базе которого напряжение будет равно и UCM + А Uc (UCM - начальное смещение 0,2-0,Зв, AUc - напряжение, равное усиленной усилителем 5 амплитуде входного сигнала) и входной сигнал через усилитель 5 и эмиттерный повторитель V12 поступает на выход каскада преобразования 1.1,

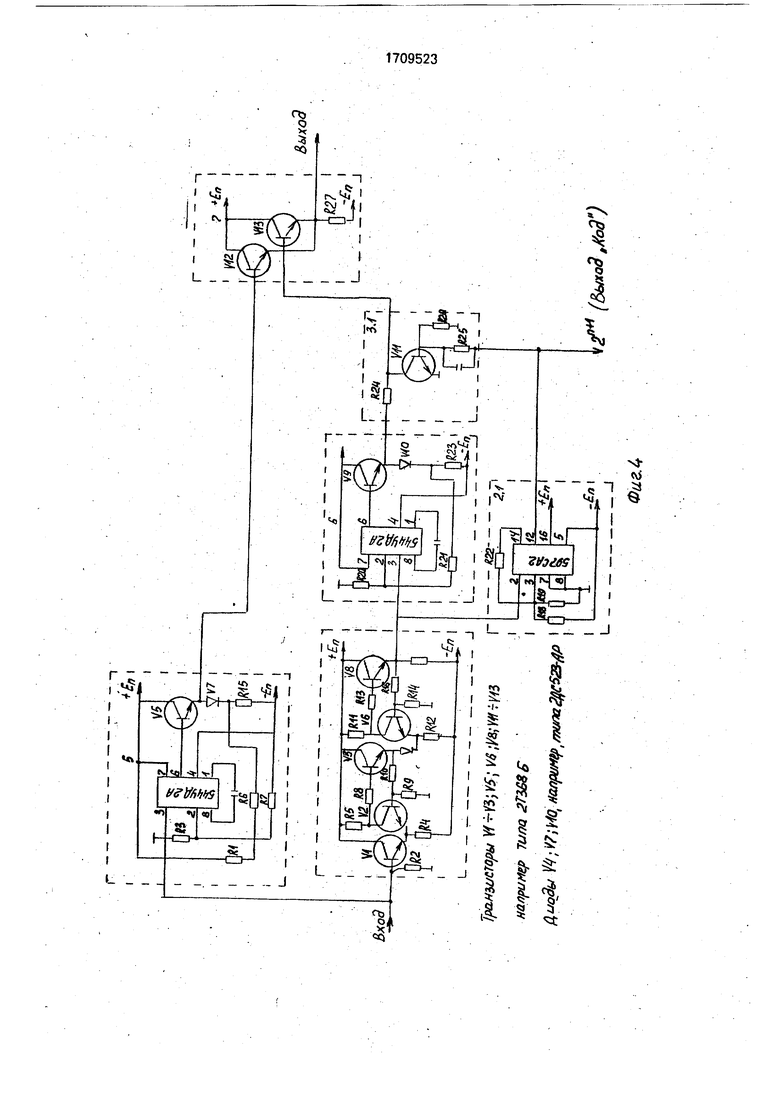

На фиг. 5 изображены эпюры напряжеНИИ на входах и выходах элементов первого каскада преобразования при уровне сигнала на входе, превышающем порог срабатывания компаратора 3.1; на фиг. 6 - эпюры напряжений при уровне сигнала на входе

нмже порога срабатывания компаратора 3,1,

На фиг, 5 и 6 обозначено: а - эпюра напряжения на входе 1-го каскада преобразования (входы элементов 4,1 и 5); б - эпюра

напряжения на выходе усилителя 4.1; в эпюра напряжения на выходе усилителя 5; г - эпюра напряжения на выходе элемента 6; д - эпюра напряжения на выходе элемента 2.1; е - эпюра напряжения на выходе элемента 3.1; ж-эпюра напряжения на выходе элемента 7..

Введение новых элементов:, второго усилителя 5, элемента-б задержки и схемы 7 логического сложения с выбором максимального уровня выгодно отличает предлагаемое устройство от прототипа, так как позволяет в широком динамическом диапазоне повысить точность преобразования и упрощает его настройку. Использование

предлагаемого устройства в измерительных системах с цифровой обработкой информации позволяет улучшить их точностные характеристики и исключит необходимость разработки высокочувствительных логарифмических преобразователей напряжения в двоичный код, способных работать в широком динамическом диапазоне, обладающих высоким быстродействием и надежностью. Формула из обретения 1, Логарифмический преобразователь напряжения в двоичный код, содержащий п последовательно соединенных каскадов преобразование,, каждый из которых выполнен на компаро;оре, управляемом аттенюаторе и усилителе, выход которого а каждом 1-м каскаде, кроме первого, является выходом 1-го каскада преобразования, а вход соединен с выходом управляемого аттенюатора, вход компаратора является входом соответствующего каскада преобразования, выход последнего каскада преобразования соединен с входом компаратора младшего разряда, выход компаратора каждого 1-го каскада преобразования подключен к управляющему входу управляемого аттенюатора этого каскада преобразования, вУходы компараторов всех каскадов преобразования и компаратора младшего разряда являются шинами соответствунэщих разрядов выходного кода, отличающийся тем, что, с целью повы. точности преобразования путем снижения уровня коммутационной помехи, в первый каскад преобразования введены элемент задержки, блок логического сложения с выбором максимального уровня сигнала, дополнительный усилитель, а управляемый аттенюатор в первом каскаде выполнен на электронном ключе, управляющий вход которого является управляющим входом управляемого аттенюатора, информационный вход электронного ключа подключен к выходу элемента задержки, вход которого обьединен с входом компаратора и соединен с выходом усилителя, вход которого является входной шиной и обьединен с входом дополнительного усилителя, выход которого соединен с первым входом блока логического сложения с выбором максимального уровня сигнала, второй вход которого соединен с выходом электронного ключа, а выход является выходом первого каскада преобразования, при этом в каждом, 1-ом каскаде преобразования, кроме первого, входкомпаратора объединен с информационным входом управляемого аттенюатора. 2. Преобразователь по п, 1, о т л и ч а ющ и и с я тем, что блок логического сложения с выбором максимального уровня сигнала выполнен на двух транзисторах и резисторе, первый вывод которого соединен с шиной напряжения отрицательной полярности, а второй вывод - с эмиттерами первого и второго транзисторов и является выходом блока, первым и вторым входами которого являются базы первого и второго транзисторов соответственно, коллекторы которых объединены и подключены к шине напряжения положительной полярности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь амплитудного значения импульсного напряжения в постоянное напряжение | 1990 |

|

SU1716599A2 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Функциональный преобразователь напряжения в двоичный код | 1982 |

|

SU1051704A1 |

| Устройство для измерения ширины спектра сигнала радиопередатчиков на различных уровнях | 1991 |

|

SU1798723A1 |

| Аналого-цифровой преобразователь амплитудных значений радиоимпульсов | 1986 |

|

SU1317659A1 |

| Устройство для контроля чувствительности побочных и интермодуляционных каналов в радиоприемниках | 1990 |

|

SU1704287A1 |

| Устройство для контроля чувствительности побочных и интермодуляционных каналов в радиоприемниках | 1991 |

|

SU1811016A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Устройство для измерения электропроводности жидкости | 1990 |

|

SU1736936A1 |

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU955110A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение точности преобразования за счет снижения уровня коммутационной помехи. Цель достигается тем, что в известный логарифмический преобразователь напряжения в двоичный код, содержащий п последова- тел(>&но соединенных каскадов преобразования, каждый из которых содержиткомпаратор, первый усилитель и управляемый аттенюатор, управляющий вход которого подключен к выходу компаратора, при зтом выход п-го каскада преобразования соединен с входом компаратора младшего разряда, в первый каскад преобразования дополнительно введены второй усилитель, вход которого объединен с входом первого усилителя и является входом преобразователя, элемент задержки, вход которого соединен с выходом первого усилителя и входом компаратора, а выход - с сигнальным входом управляемого аттенюатора, в качестве которого в первом каскаде применен электронный ключ, и блок логического сложения с выбором максимального уровня, первый вход которого подключен к выходу управляемого аттенюатора, второй - к выходу второго усилителя, а выход является выходом первого каскада преобразования, причем в остальных каскадах преобразования вход компаратора соединен с сигнальным входом управляемого аттенюатора. 1 з.п. ф-лы, 6 ил.

Вь1ХоЗ КоЭ

ВмЗ .Ux

о«

to

ж и

Фиг

d и

И

.(9,

Фиг.6

| Бахтиаров Г.Д | |||

| Аналого-цифровые преобразователи | |||

| М.: Сов | |||

| радио, 1980, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Функциональный преобразователь напряжения в двоичный код | 1982 |

|

SU1051704A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-11—Подача