Изобретение относится к автоматике и может быть использовано для управления станками, оснащенными шаговыми приводами

Цель изобретении - упрощение и повышение надежности.

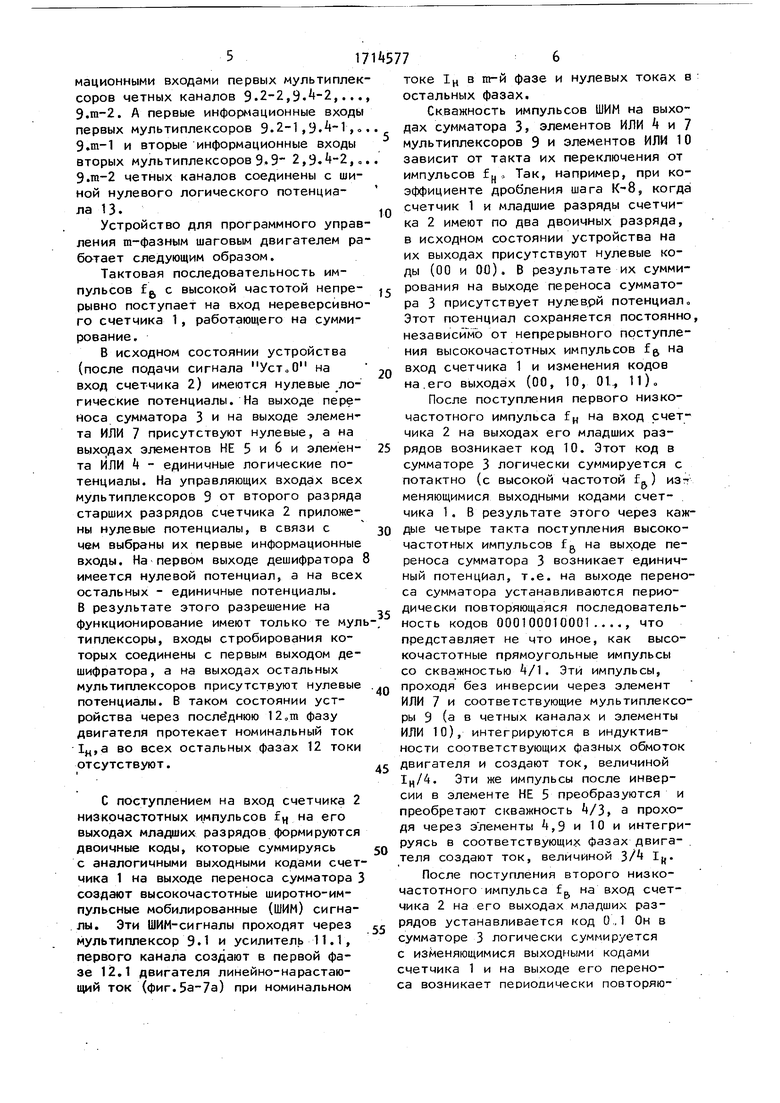

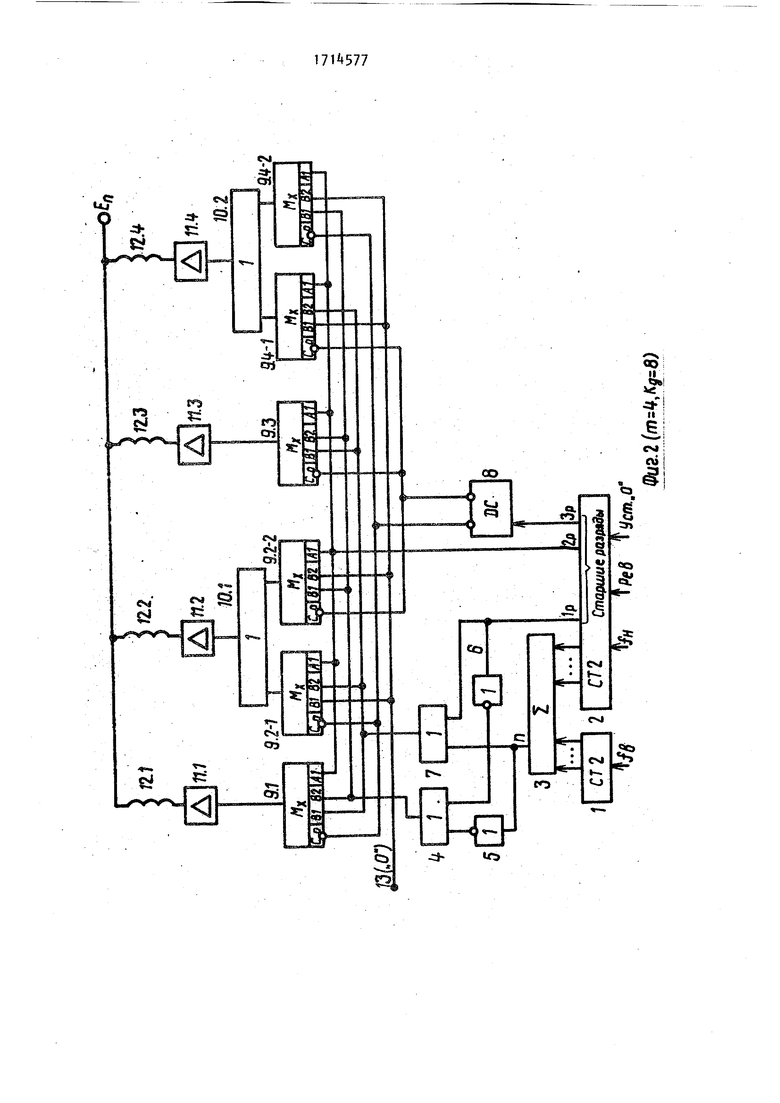

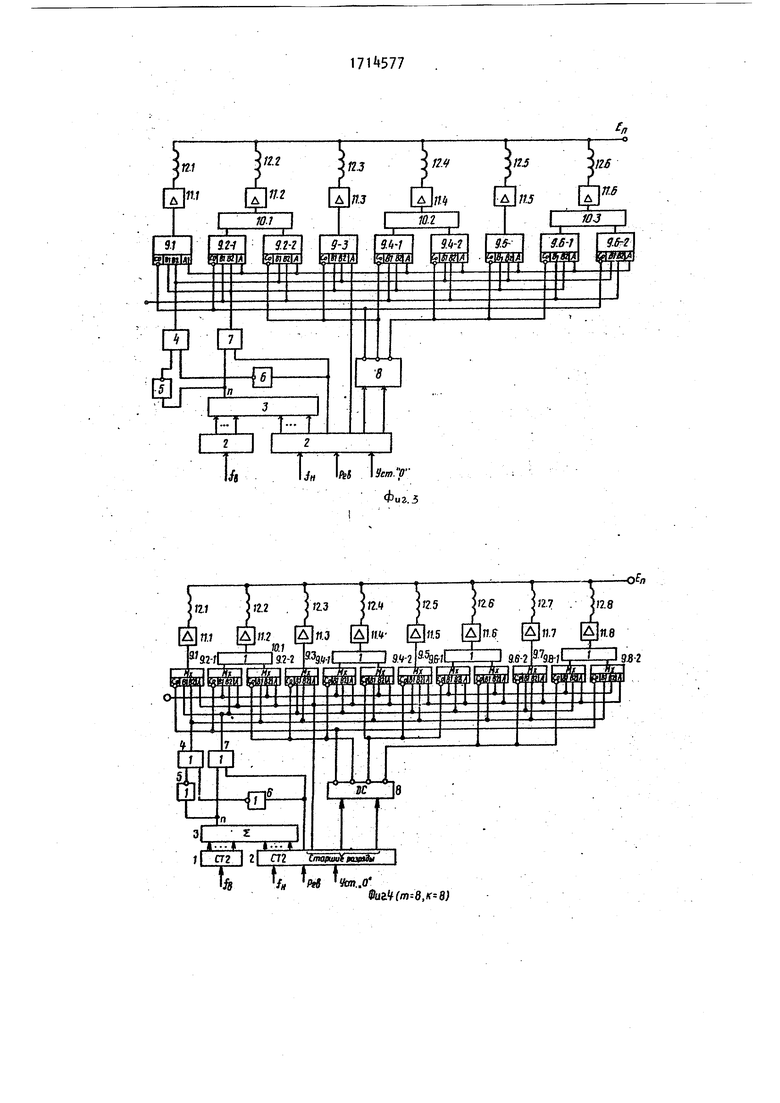

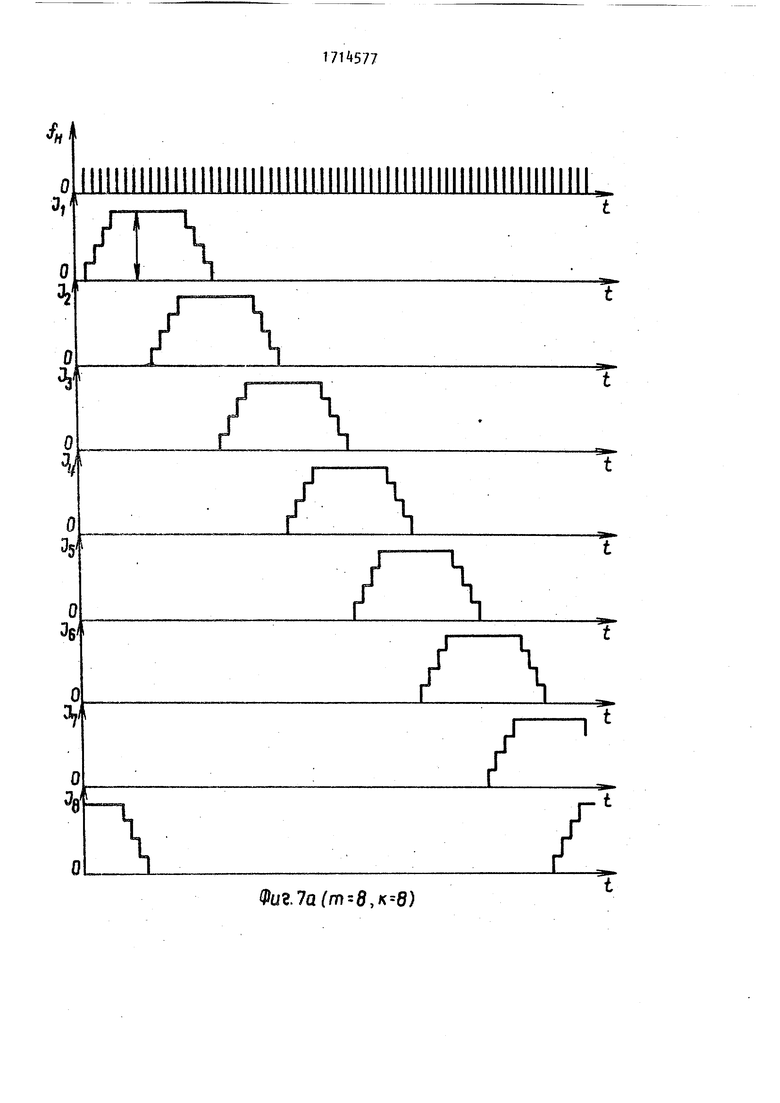

На фиг.1 представлена функциональная схема устройства для прог раммного управления т-фазным шаговым двигателем; на фиг.2- - то же, для управления соответственно -х, 6-и, 8-ми фазными двигателями;, на фиг.57 - временные диаграммы фазных токов и номограммы векторов результирующих моментов применительно соответственно к -х, 6-ти, 8-ни фазным двигателям.

Устройство содержит нереверсивный двоичный счетчик 1 счетный вход которого соединен с шиной высокочастотных импульсов тактирования fg, реверсивный двоичный счетчик 2 счетный вход, входы управления реверсом и установка в О которого соединены соотетстьенно с шинами низкочас Тотных импульсов тактирования i, реверсироБания Рев и установки в нулевое исходное состояние Уст„О, сумматор 3 кодов, первая группа входов которого соединена с выходами нереверсивного двоичного счетчика 1, а вторая группа входов - с выходами младших разрядов реверсивного двоичного счетчика 2, первый элемент ИЛИ k, входы которого через первый 5 и второй 6 элементы НЕ соединены соответственно с выходом переноса сумматора 3 кодов,и с выходом пераого разряда старших разрядов реверсивного двоичного счетчика 2, второй элемент ИЛИ 7s входы которого соединены соответственно с выходом переноса сумматора 3 кодов и выходом первого разряда старших разрядов реверсивно го двоичного счетчика 2, дешифратор 8, входы которого соединены с выходами с третьего по последний раз ряды старших разрядов реверсивного двоичного счетчика 2,В нечетныхканалах управления содержатся мультиплексоры 2на .1,9.3...,9{m-l), а в четных каналах управления - первые мультиплексоры 2 на 1 9.2-1,9.-1. 9.т-1 и вторые мультиплексоры 2 на 1 9.2-2,9.t-Z,. ..9.41-2, выходы которых соединены соответственно с BXO дами элементов ИЛИ 10,1,10«2.,,1 о |

Выходы мультиплексоров ,,«..,

9.(п1-1) нечетных каналов и выходы элементов ИЛИ 10.1,10.2j...10.| четных каналов соединены соответственно с выходными усилителями мощности 11.1 ,11,2,...,11.га, коммутирующие токи фазных обмоток 12.1,12.2,.«.12,га шагового двигателя. Выход второго разряда старший разрядов реверсивног двоичного счетчика 2 подключен к управляющим/ входам всех мультиплексоров 9. Первый выход дешифратора 8 соединен с входами стробирования мультиплексора первого канала 9.1, первого мультиплексора второго канала 9.2-1 и второго мультиплексора га-го канала 9.iii-2. Второй выход дешифратора 8 соединен с входами стробирования мультиплексоров третьего канала 9.3 первого мультиплексора четвертого канала 9.-1 и второго мультиплексора второго канала .9.2-2. Третий выход дешифратора 8 соединен с входами стробирования мультиплексора пятого канала 9.5, первого мультиплексора шестого канала 9.6-1 и второго мультиплексора четвертого

канала , j-й j 1,, | )

выход дешифратора 8 подключен к входам стробирования мультиплексора (j-l)-ro канала 9.(j-1), первого мультиплексора j-ro канала 9. и второго мультиплексора (j-2)-ro канала 9й-2)-.2.(| -1)-й выход дешифратора 8 соединен с входами стробирования мультиплексора (ш-З)-го канала 9(т-3), первого мультиплексора ()-го канала 9.()-1 и второго мультиплексора (т-)-го канала

9.(п1-4)-2.- -и выход дешифратора 8

соединен с входами стробирования мультиплексора (т-1) - го канала 9 .(т-1) первого мультиплексора т-го канала 9.т-1 и второго мультиплексора (т-2)-го канала 9.(ni-2)-2. Выход первого элемента ИЛИ соединен с вторыми информационными входами мультиплексоров нечетных каналов 9.1, 9оЗо..9о(т-1) и с первыми информационными входами первых мультиплексоров четных каналов 9.2-2,9.,.. .9.mrВыход второго элемента ИЛИ 7 соединен с первыми информационными входами мультиплексоров нечетных каналов 9.1,9.3...9.(m-l) и с вторыми информационными входами первых мультиплек соров четных каналов 9.2-2,9Л-2,.. 9.т-2. А первые инфop aциoнныe входы первых мультиплексоров 9.2-1,у.4-1,о 9.т-1 и вторые информационные входы вторых мультиплексоров 9.Э 2,9.2, 9.га-2 четных каналов соединены с шиной нулевого логического потенциала 1 3 . Устройство для программного управ ления т-фазным шаговым двигателем ра ботает следующим образом. Тактовая последовательность импульсов fg, с высокой частотой непрерывно поступает на вход нереверсивно го счетчика 1, работающего на суммирование, В исходном состоянии устройства (после подачи сигнала УсТоО на вход счетчика 2) имеются нулевые логические потенциалы. На выходе переноса сумматора 3 и на выходе элемента ИЛИ 7 присутствуют нулевые, а на выходах элементов НЕ 5 и 6 и элемента ИЛИ k единичные логические потенциалы. На управляющих входах всех мультиплексоров 9 от второго разряда старших разрядов счетчика 2 приложены нулевые потенциалы, в связи с чем выбраны их первые информационные входы. На первом выходе дешифратора имеется нулевой потенциал, а на всех остальных - единичные потенциалы. В результате этого разрешение на функционирование имеют только те мул типлексоры, входы стробирования которых соединены с первым выходом дешифратора, а на выходах остальных мультиплексоров присутствуют нулевые потенциалы. В таком состоянии устройства через последнюю 12 „т фазу двигателя протекает номинальный ток 1„,а во всех остальных фазах 12 токи отсутствуют. С поступлением на вход счетчика 2 низкочастотных импульсов Гн на его выходах младших разрядов формируются двоичные коды, которые суммируясь с аналогичными выходными кодами счетчика 1 на выходе переноса сумматора 3 создают высокочастотные широтно-импульсные мобилированные (ШИМ) сигналы. Эти ШИМ-сигналы проходят через мультиплексор 9.1 и усилитель 11.1, первого канала создают в первой фазе 12.1 двигателя линейно-нарастающий ток (фиг.5а-7а) при номинальном токе 1ц в га-й фазе и нулевых токах в остальных фазах. Скважность импульсов ШИМ на выходах сумматора 3 элементов ИЛИ 4 и 7 мультиплексоров 9 и элементов ИЛИ 10 зависит от такта их переключения от импульсов f, Так, например, при коэффициенте дробления шага К-8, когда счетчик 1 и младшие разряды счетчика 2 имеют по два двоичных разряда, в исходном состоянии устройства на их выходах присутствуют нулевые коды (00 и 00). В результате их суммирования на выходе переноса сумматора 3 присутствует нулеврй потенциал Этот потенциал сохраняется постоянно, независимо от непрерывного поступления высокочастотных импульсов fg на вход счетчика 1 и изменения кодов на,его выходах (00, 10, 01., 11) После поступления первого низкочастотного импульса ц на вход счетчика 2 на выходах его младших разрядов возникает код 10. Этот код в сумматоре 3 логически суммируется с потактно (с высокой частотой f) изт меняющимися выходными кодами счетчика 1. В результате этого через каждые четыре такта поступления высокочастотных импульсов fg на выходе переноса сумматора 3 возникает единичный потенциал, т.е. на выходе переноса сумматора устанавливаются периодически повторяющаяся последовательность кодов 000100010001...., что представляет не что иное, как высокочастотные прямоугольные импульсы со скважностью 4/1. Эти импульсы, проходя без инверсии через элемент ИЛИ 7 и соответствующие мультиплексоры 9 (а в четных каналах и элементы ИЛИ 10), интегрируются в индуктивности соответствующих фазных обмоток вигателя и создают ток, величиной 1ц/4. Эти же импульсы после инверсии в элементе НЕ 5 преобразуются и реобретают скважность 4/3, а прохоя через элементы 4,9 и 10 и интегриуясь в соответствующих фазах двига- . еля создают ток, величиной 3/4 I. После поступления второго низкоастотного импульса fg на вход счетика 2 на его выходах младших разядов устанавливается код 0., 1 Он в умматоре 3 логически суммируется изменяющимися выходными кодами четчика 1 и на выходе его переноа возникает периодически повторяющаяея кодовая последовательность 00110011..., что равносильно высокочастотным прямоугольным импульсам со скважностью 4/2. Эти импульсы, проходя без инверсии через соответствующие элементы устройства и интегрируясь в фазах двигателя , создают ток, величиной 2/k Ij, а после инверсии - также ток, величиной 2/Ц 1ц„ После третьего низкочастотного импульса fj, на выходе переноса сумматора 3 возникают коды 01110111..., т.е. информируются импульсы со скважностью 1/31 э через определенные фазы двигателя устан авливаются соответствующие токи 3/ 1ц и 1/ После переполнения младших разрядов счетчика 2 (т.е. после запол нения всех этих разрядов логическими единицами) на выходе Первого разряда его старших разрядов появляется единичный потенциал. Благодаря этому в такт формирования кодов на выходах младших разрядов сметчика 2 в первой фазе 1.1 двигателя устанавливается номииаг.ьный ток 1, с ш-й фазе линейно-ступенчато спадаюгдий ток (при нулевых гоках в остальных фазах После повторного переполнения мла ших разрядов счетчигсз 2 единица появ ляется во втором разряде старших его разрядов с. Это приводит к выборке вто рых информационных входов мультиплек соров 9. Благодаря этому при нулевом потенциале.первого разряда старших разрядов счетчика 2 в первой фазе 12.1 Двигателя устанавливается номинальный ток во второй фазе 12.2 формируется линейно-ступенчато нарас тающий ток. а при единичном потенциа ле первого разряда старших разрядов счетчика 2 в первой фазе формируется линейно-ступенчато спадающий ток, во второй фазе устанавливается номинальный ток (при нулевых токах в остальных фазах). Дальнейшее функционирование уст ройства.аналогично описанному. Отличие заключается лишь в том, что в последующих тактах работы поочередно выбираются последующие выходы дешифратора 8, в соответствии с чем разре шение получают другие группы мультиплексора 9 В результате этого ступенчато нарастающие и спадающие токи создаются в последующих парах фаз двигателя. Благодаря описанному порядку функционирования устройства вектор результирующего момента на валу двигателя описывает т-гольную номограмму по полю двигателя, и в соответствии с этим его ротор отрабатывает заданное число дробных шагов (фиг.56-76). Реверсирование двигателя осуществляется изменением на обратный логического потенциала на шине Рев счетчика 2, в результате которого он переходит на режим вычитания„ Коэффициент дробленияосновного шага двигателя определяется выражением , где п-выбранное число младших разрядов счетчика 2 и выбранное число разрядов счетчика 1, Это число определяется выражением п loggt -l- . Число старших разрядов счетчика 2 л .-li -m/2rопределяется выражением P 2+Jlog | где m - число фаз двигателя. Число выходов дешифратора 8 равно in/2. Количество уровней квантования тока в каждой фазе равно При реализации счетчика 2 могут быть использованы два последовательно соединенных двоичных счетчика, первый из которых формирует эквивалентный код младших разрядов счетчика 2 и имеет коэффициент пересчета п, а второй формирует эквивалентный код старших разрядов счетчика 2 и имеет коэффициент пересчета P 2- -3log Частота импульсов высокочастотного тактирования f выбирается исходя из величины электромагнитной постоянной времени данного двигателя. А частота импульсов низкочастотного тактирования ц выбирается в соответствии с требуемой скоростью вращения ротора двигателя. Таким образом, устройство по сравнению с известным имеет значительно ;более простую логическую структуру, :поскольку в нем вместо мультиплексоров с m информационными входами используются самые простые мультиплексоры с двумя информационными входами. Это упрощение приводит к значительному повышению надежности устройства. А введение дополнительного дешифратора 8 мало влияет на общий объем аппаратуры устройства. Формула изобретения Устройство для программного управ ления ш-фазным шаговым двигателем, где ,6,8,... - четное число, содержащее нереверсивный двоичный счет чик, счетный вход которого соединен с шиной высокочастотных импульсов та тирования, реверсивный двоичный счет чик, счетный вход., входы управления реверсом и установки в О которого соединены соответственно с шинами низкочастотных импульсов тактирования, реверсирования и установки в ну левое исходное состояние, сумматор кодов, первая группа входов которого соединена с выходами нереверсивного двоичного счетчика, а вторая группа входов - с выходами младших разрядов реверсивного двоичного счетчика, пер вый элемент ИЛИ, входы которого чере первый и второй элементы НЕ соедине- ны соответственно с выходом переноса сумматора кодов и с выходом первого разряда старших разрядов реверсивног двоичного счетчика, второй элемент ИЛИ, входы которого соединены соответственно с выходом переноса сумма;Тора кодов и выходом первого разряда 1старших разрядов реверсивного двоичного счетчика, а в каждом канале управления - усилитель мощности, выходом подключенный к фазной обмотке шагового двигателя, отличаю щ е е с я тем, что, с целью упрощения и повышения надежности, введены дешифратор и в каждый нечетный канал - мультиплексор 2 на 1, выход которого соединен с входом соответст вующего усилителя мощности, в каждый четный канал - первый и второй мульт плексоры 2 на 1 и соединенный с .их выходами элемент ИЛИ, выход которого подключен к входу соответствующего усилителя мощности, входы дешифратора соединены с выходами с , третьего по последний разряды старш их разрядов реверсивного двоичного сметчика, выход второго разряда старших разрядов которого подключен к управляющим входам всех мультиплексоров у первый выход дешифратора соединен с входами стробирования мультиплексора первого канала, первого мультиплексора второго канала и второго мультиплексора т-го канала, второй выход дешифратора - с входами стробирования мультиплексора третьего канала, первого мультиплексора четвертого канала и второго мультиплексора второго канала, третий выход дешифратора - с входами стробирования мультиплексора иятого канала, первого мультиплексора шестого канала и второго мультиплексора четвертого канала,j-й (,...,т/2) выход Дешифратора подключен к входам стробирования мультиплексора (j-l)-ro канала, первого мультиплексора j-ro канала и второго мультиплексора (J-2)-го канала, (т/2)-1 -и выход дешифратора соединен с входами стробирования мультиплексора (т-З)-го канала, первого мультиплексора (ш-2)-го канала и второго мультиплексора (т-4)-го канала, (т/2)-й выход дешифратора соединен с-входами стробирования мультиплексора (ni-l)-ro канала, первого мультиплексора т-го канала и второго мультиплексора (т-2)-го канала, выход первого элемента ИЛИ соединен с вторыми информационными входами мультиплексоров нечетных каналов и с первыми информационными входами вторых мультиплексоров четных каналов, выход второго элемента ИЛИ - с первыми инфор- мационными входами мультиплексоров нечетных каналов и с вторыми информационными входами первых мультиплексоров четных каналов, а первые инфорационные входы первых мультиплексоров и вторые информационные входы вторых мультиплексоров четных канаов соединены с шиной нулевого логиеского потенциала.

cl- Ci

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления @ -фазным шаговым двигателем | 1990 |

|

SU1718187A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1989 |

|

SU1679598A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для программного управления четырехфазным шаговым двигателем с насыщенной магнитной системой | 1989 |

|

SU1702340A1 |

| Устройство для программного управления @ -фазным шаговым двигателем | 1988 |

|

SU1594488A1 |

| Устройство для программного управления четырехфазным шаговым двигателем | 1989 |

|

SU1649513A1 |

| Распределитель импульсов для управления трехфазным шаговым двигателем | 1990 |

|

SU1705998A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для программного управления @ -фазным шаговым двигателем | 1987 |

|

SU1529179A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Изоб^ретение относится к автоматике и может быть использовано для ' управления станками, оснащенными шаговыми приводами подач. Цель изобретения - упрощение схемы и повышение надежности* Устройство содержит нереверсивный 1 и реверсивный 2 двоичные счетчики, элемент или А, элементы НЕ 5 и 6, элемент ИЛИ 7, дешифратор 8, в нечетных каналах управления которых содержатся мультиплексоры "2 на 1" 9.1,9.3,...,9.(т-1), а в четных каналах управления Первые мультиплексоры "2 на 1" 9.2- . . 1.9,^-1,...,9.(т-1) и вторичные мультиплексоры "2 на 1" 9.2-2,9.^-2,..., 97(т~2). Четные каналы управления содержат также элементы ИЛИ 10.1,^10.2,..1О.г . Устройство по сравнению с прототипом имеет значительно более простую логическую структуру, поскольку в нем вместо мультиплексоров с т-информационными входами Используются самые простые мультиплексоры с двумя информационными входами, что приводит к значительному повышению надежности устройства. 7 ил..fit^слXIXI

те S

GO;

rfl

II :

1 I

oi I

п

-о

ns

П6

2| ГТ2 /Сдадву лаиЗУ j

U/« Лв Ьп..О

(,) -Of/j Г Зэл-2

V

JH

01-

/л

УЗ

лл

н.

У Фаг.55 Гт,)

%8.5ar/n,)

Ф

Зф

ц

о

3,

о

о

зу

5

%

Фив.6б(т-6.)

/

/л

/

Фиг.ба (т-6,)

л

LA

Зб

Фиг7аГт а,)

/

/

. cf (,)

| Устройство для программного управления @ -фазным шаговым двигателем | 1982 |

|

SU1020800A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-02-23—Публикация

1989-11-23—Подача