Изобретение относится .к измери- тельной технике, а именно к многока- нальному аналого-цифровому преобразованию динамических сигналов,и может использоваться в системах сбора информации от большого числа аналоговых датчиков.

Целью изобретения является уменьшение времени преобразования.

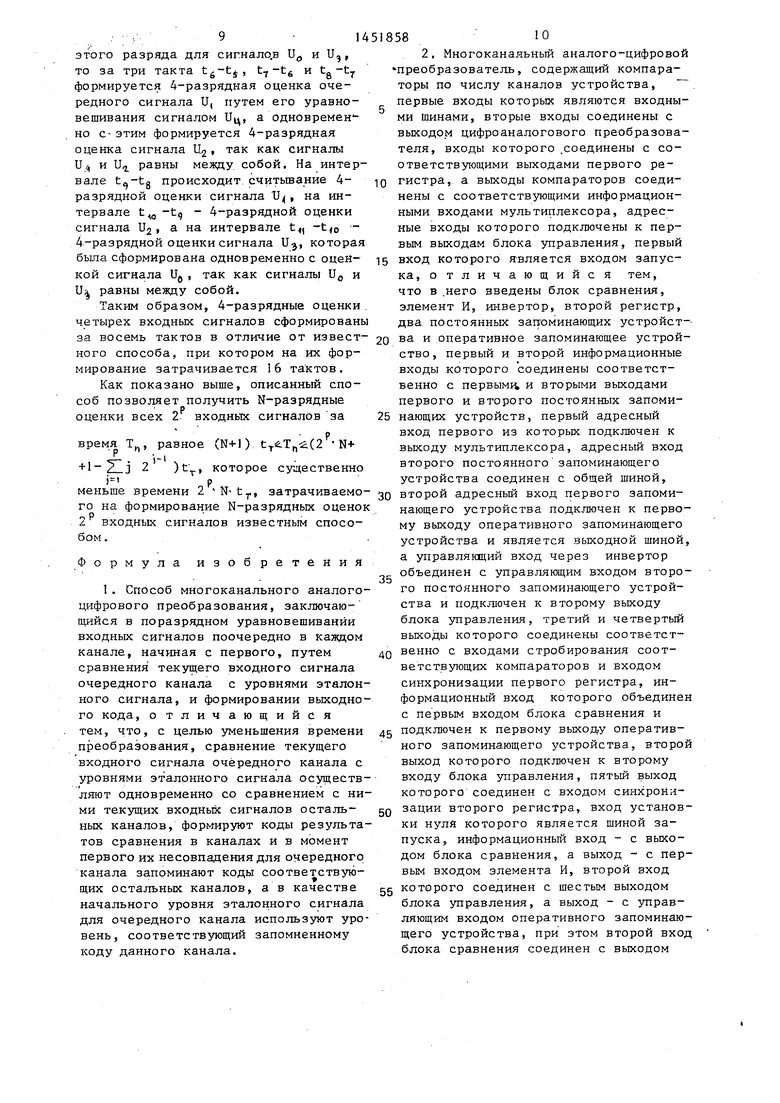

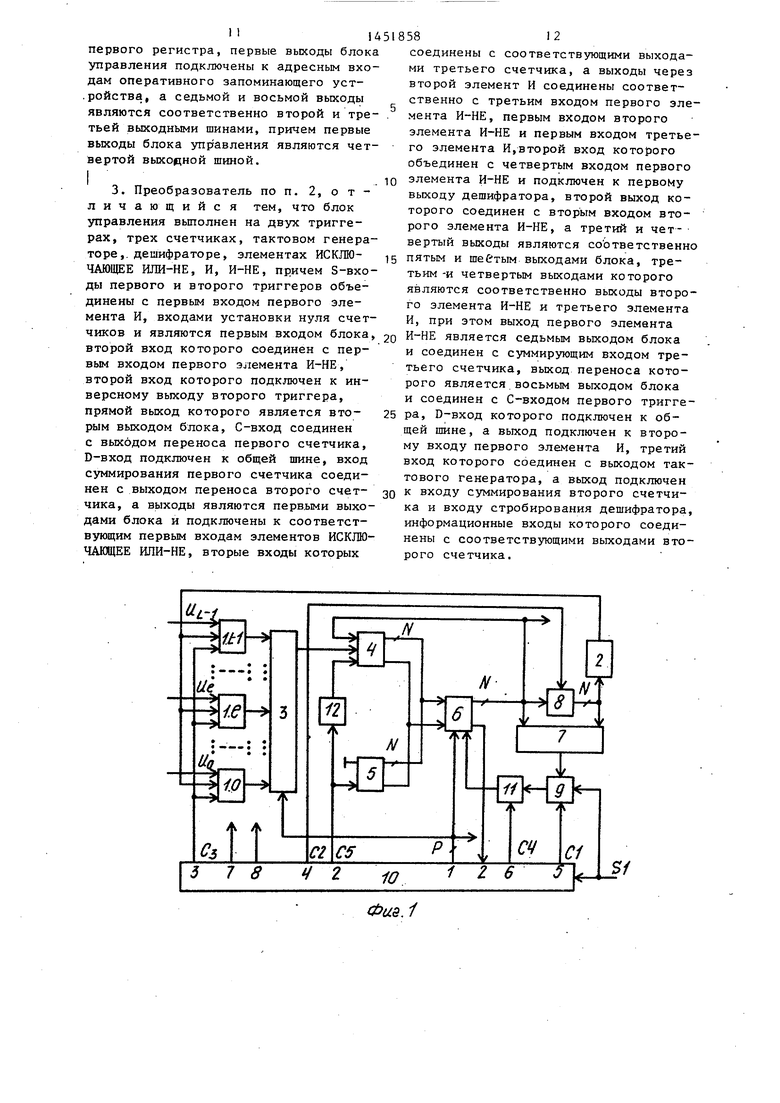

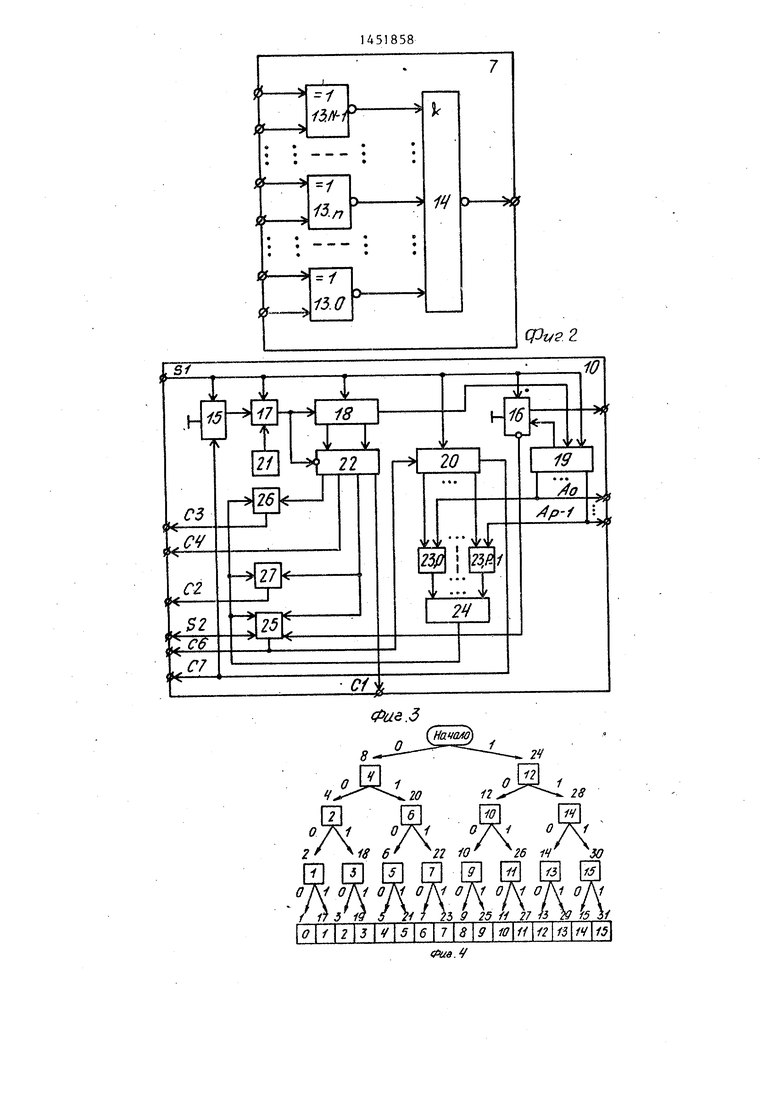

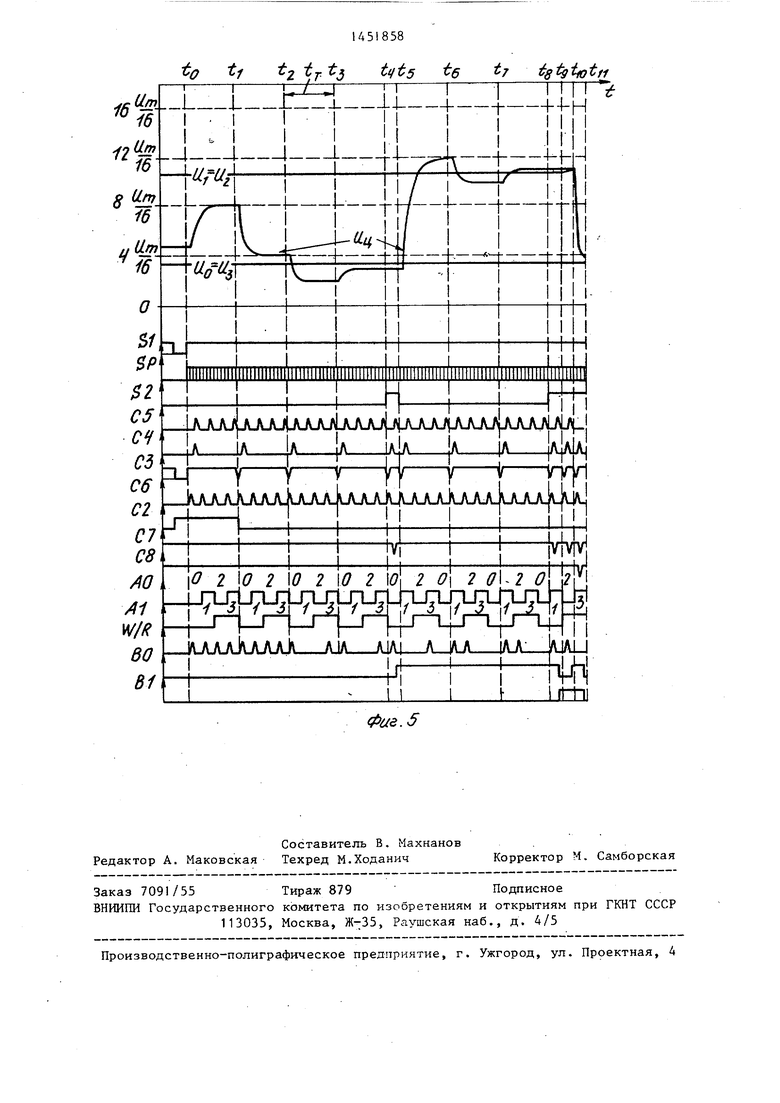

Изобретение позволяет при формировании N-разрядной оценки очередного входного сигнала одновременно фор мировать оценки входных сигналов в каждом из последующих каналов до тех пор, пока входные сигналы в этих каналах уравновешиваются эталонным сигналом так же, как очередной входной сигнал, запоминать эти промежуточные оценки и производить уравновешивание каждого очередного сигнала, начиная со своего уровня эталонного сигнала, в соответствии со значениями промежуточных оценок, полученных в процессе поочередного уравновешивания всех предьщущих входных сигналов, что сокращает полное время преобразования. На фиг. 1 изображена функциональная схема описьшаемого преобразователя; на фиг,2- тоже, блока сравнения; на фиг. 3 - то е, блока управления; на фиг. 4 приведен граф переходов дл составлений таблицы программирования постоянного запоминающего устройства (ПЗУ);, на фиг.5 даны временные диаграммы, поясняющие работу многоканального аналого-цифрового преобразователя.

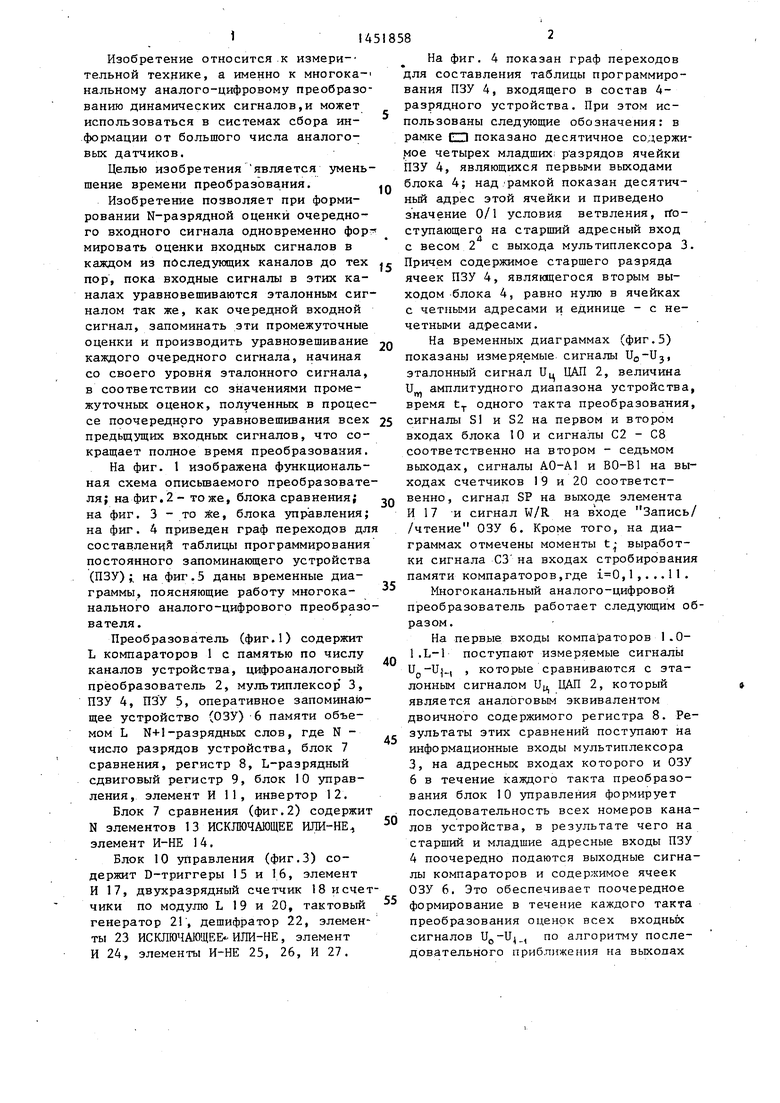

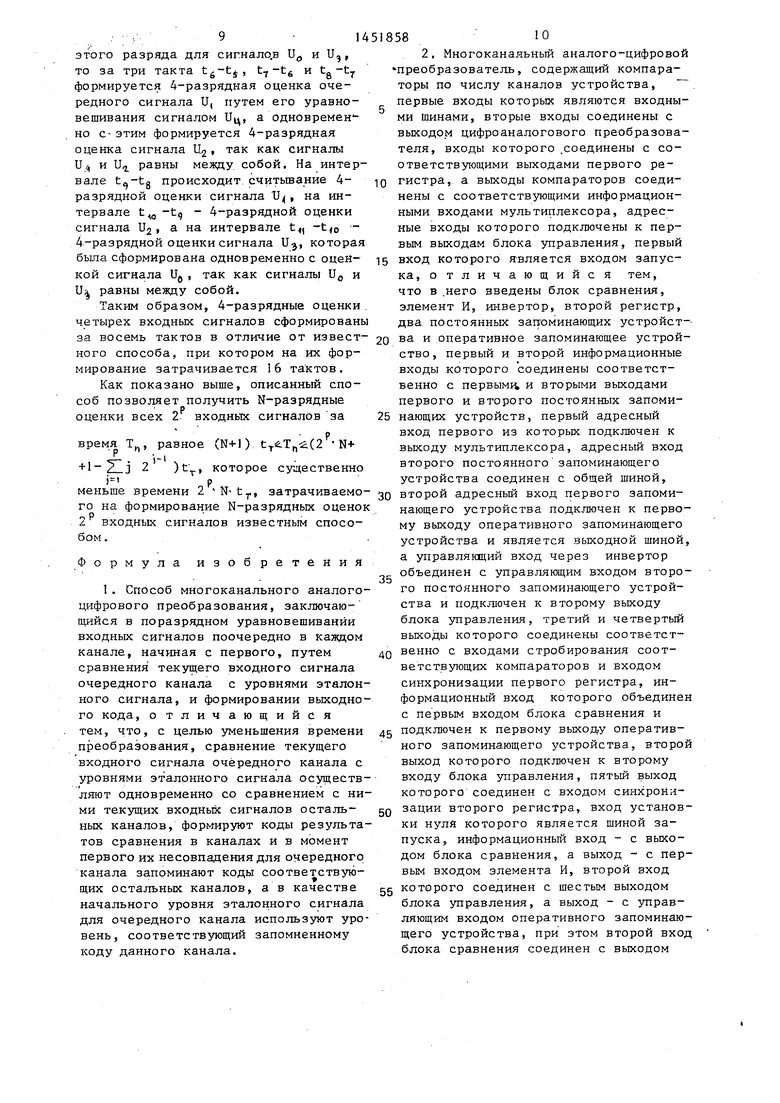

Преобразователь (фиг.1) содержит L компараторов 1 с памятью по числу каналов устройства, цифроаналоговый преобразователь 2, мультиплексор 3, ПЗУ 4, ПЗУ 5, оперативное запоминающее устройство (ОЗУ) 6 памяти объемом L N+i-разрядных слов, где N - число разрядов устройства, блок 7 сравнения, регистр 8, L-разрядный сдвиговый регистр 9, блок 10 управления, элемент И 11, инвертор 12.

Блок 7 сравнения (фиг.2) содержит N элементов 13 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ элемент И-НЕ 14.

Блок 10 управления (фиг.З) содержит D-триггеры 15 и 16, элемент И 17, двухразрядный счетчик 18исчет чики по модулю L 19 и 20, тактовый генератор 2Г, дешифратор 22, элементы 23 ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ, элемент И 24, элементы И-НЕ 25, 26, И 27.

10

г 2о 25эп

- 18582

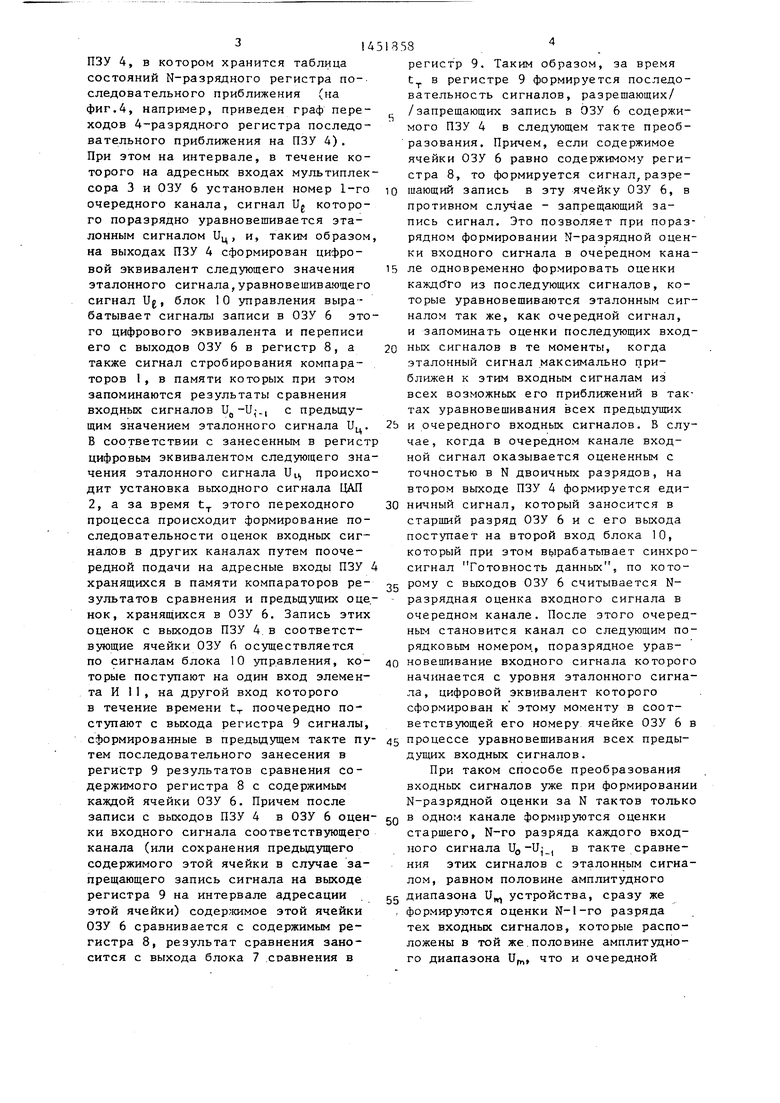

На фиг. 4 показан граф переходов для составления таблицы программирования ПЗУ 4, входящего в состав 4- разрядного устройства. При этом использованы следующие обозначения: в рамке cm показано десятичное содержимое четырех младших разрядов ячейки ПЗУ 4, являющихся первыми выходами блока 4; над/рамкой показан десятичный адрес этой ячейки и приведено значение 0/1 условия ветвления, гГо- ступающего на старший адресный вход с весом 2 с выхода мультиплексора 3. Причем содержимое старшего разряда ячеек ПЗУ 4, являющегося вторым выходом блока 4, равно нулю в ячейках с четными адресами и единице - с нечетными адресами.

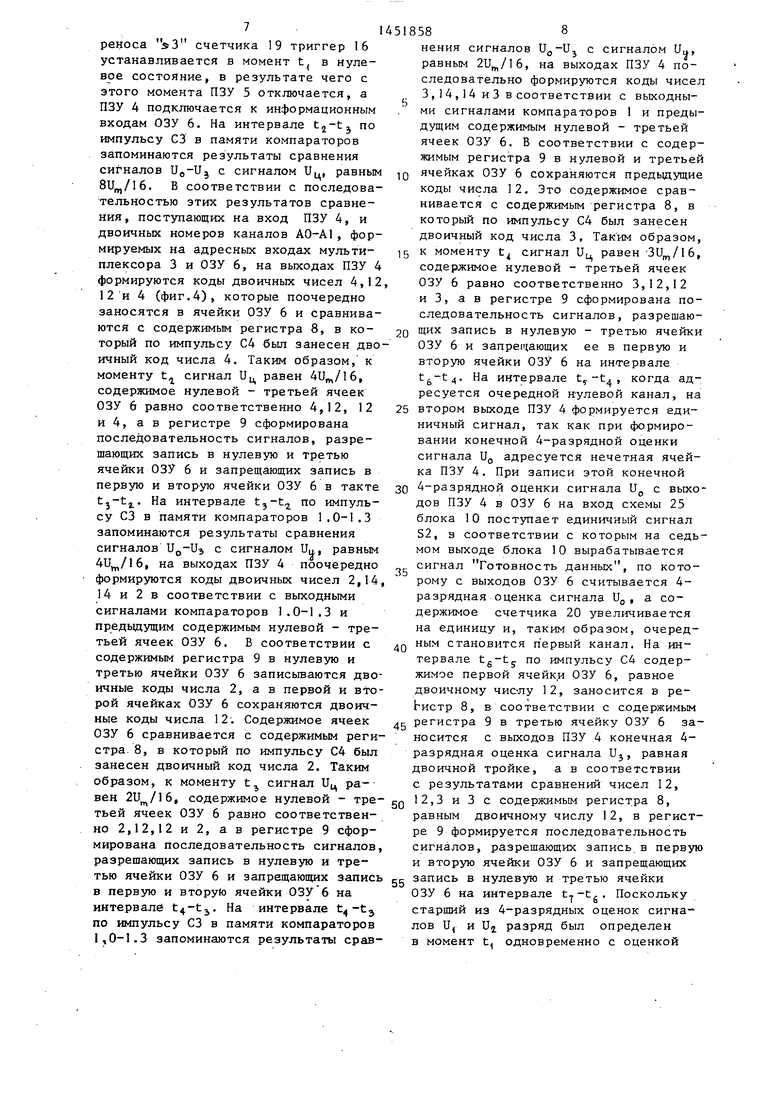

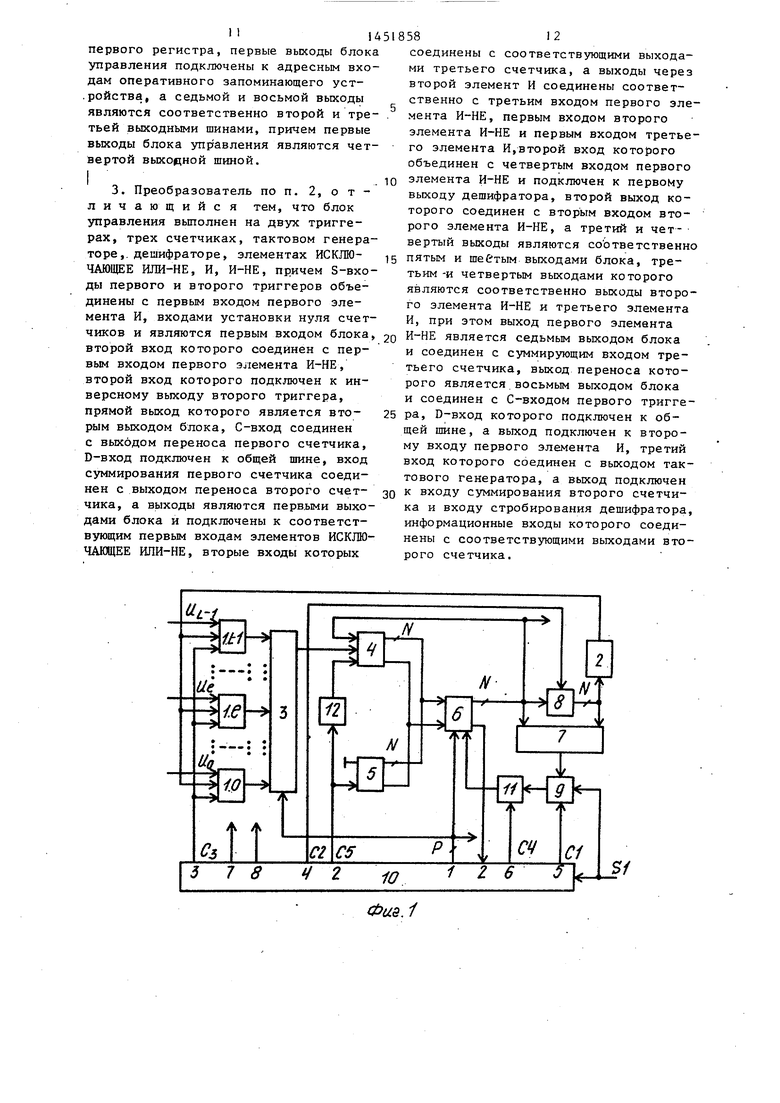

На временных диаграммах (фиг.5) показаны измеря емые сигналы UQ-UJ, эталонный сигнал Пц ЦАП 2, величина

35

40

45

50

55

и амплитудного диапазона устройства, время t одного такта преобразования, сигналы S1 и S2 на первом и втором входах блока 10 и сигналы С2 - С8 соответственно на втором - седьмом выходах, сигналы АО-А1 и ВО-В1 на выходах счетчиков 19 и 20 соответственно , сигнал SP на выходе элемента И 17 -и сигнал W/R на входе Запись/ /чтение ОЗУ 6. Кроме того, на диаграммах отмечены моменты выработки сигнала СЗ на входах стробирования памяти компараторов,где ,1,... 11.

Многоканальный аналого-цифровой преобразователь работает следующим образом.

На первые входы компараторов 1.0- 1.L-1 поступают измеряемые сигналы и -U}, , которые сравниваются с эталонным сигналом Пц ЦАП 2, который является аналоговым эквивалентом двоичного содержимого регистра 8. Результаты этих сравнений поступают на информационные входы мультиплексора 3, на адресных входах которого и ОЗУ 6 в течение каждого такта преобразования блок 10 управления формирует последовательность всех номеров каналов устройства, в результате чего на старший и младшие адресные входы ПЗУ 4 поочередно подаются выходные сигналы компараторов и содержимое ячеек ОЗУ 6. Это обеспечивает поочередное формирование в течение каждого такта преобразования оценок всех входньгх сигналов Ug-U,, по алгоритму последовательного приближения на выхопах

314

ПЗУ 4, в котором хранится таблица состояний N-разрадного регистра последовательного приближения (на фиг.4, например, приведен граф переходов 4-разрядно-го регистра последовательного приближения на ПЗУ 4) . При этом на интервале, в течение которого на адресных входах мультиплексора 3 и ОЗУ 6 установлен номер 1-го очередного канала, сигнал Ug которого поразрядно уравновешивается эталонным сигналом Иц, и, таким образом на выходах ПЗУ 4 сформирован цифровой эквивалент следующего значения эталонного сигнала,уравновешивающего сигнал Ug, блок 10 управления вырабатывает сигналы записи в ОЗУ 6 этого цифрового эквивалента и переписи его с выходов ОЗУ 6 в регистр 8, а также сигнал стробирования компараторов 1, в памяти которых при этом запоминаются результаты сравнения входных сигналов U U,-., с предыдущим значением эталонного сигнала U. В соответствии с занесенным в регист цифровым эквивалентом следующего значения эталонного сигнала Иц происходит установка выходного сигнала ЦАП 2, а за время t этого переходного процесса происходит формирование последовательности оценок входных сигналов в других каналах путем поочередной подачи на адресные входы ПЗУ хранящихся в памяти компараторов ре- зультатов сравнения и предьщущкх оце нок, хранящихся в ОЗУ 6. Запись этих оценок с выходов ПЗУ 4 в соответствующие ячейки ОЗУ fi осуществляется по сигналам блока 10 управления, ко- торые поступают на один вход элемента И 1 1 , на другой вход которого в течение времени t. поочередно поступают с выхода регистра 9 сигналы, сформированные в предьщущем такте пу тем последовательного занесения в регистр 9 результатов сравнения содержимого регистра 8 с содержимым каждой ячейки ОЗУ 6. Причем после записи с выходов ПЗУ 4 в ОЗУ 6 оцен ки входного сигнала соответствующего канала (или сохранения предьщущего содержимого этой ячейки в случае запрещающего запись сигнала на выходе регистра 9 на интервале адресации

этой ячейки) содер;кимое этой ячейки ОЗУ 6 сравнивается с содержимым регистра 8, результат сравнения заносится с выхода блока 7 сравнения в

8..

регистр 9. Таким образом, за время t в регистре 9 формируется последовательность сигналов, разрешающих/ /запрещающих запись в ОЗУ 6 содержимого ПЗУ 4 в следующем такте преобразования. Причем, если содержимое ячейки ОЗУ 6 равно содержимому регистра 8, то формируется сигнал,разрешающий запись в эту ячейку ОЗУ 6, в противном случае - запрещающий запись сигнал. Это позволяет при поразрядном формировании N-разрядной оценки входного сигнала в очередном канале одновременно формировать оценки каждбТо из последующих сигналов, которые уравновешиваются эталонным сигналом так же, как очередной сигнал, и запоминать оценки последующих входных сигналов в те моменты, когда эталонный сигнал максимально приближен к этим входньм сигналам из всех возможных его приближений в тактах уравновешивания всех предьщущих и очередного входных сигналов. В случае, когда в очередном канале входной сигнал оказывается оцененным с точностью в N двоичных разрядов, на втором выходе ПЗУ 4 формируется единичный сигнал, который заносится в старший разряд ОЗУ бис его выхода поступает на второй вход блока 10, который при этом вырабатьшает синхросигнал Готовность данных, по которому с выходов ОЗУ 6 считывается N- разрядная оценка входного сигнала в очередном канале. После этого очередным становится канал со следующим порядковым номером., поразрядное уравновешивание входного сигнала которого начинается с уровня эталонного сигнала, цифровой эквивалент которого сформирован к этому моменту в соответствующей его номеру ячейке ОЗУ 6 в процессе уравновешивания всех предыущих входных сигналов.

При таком способе преобразования входных сигналов уже при формировании -разрядной оценки за N тактов только в одном канале формируются оценки старшего, N-ro разряда каждого входного сигнала U(j-Uj, в такте сравнеия этих сигналов с эталонным сигнаом, равном половине амплитудного иапазона U устройства, сразу же ормируются оценки N-1-го разряда тех входных сигналов, которые распоожены в той же.половине амплитудного диапазона U, что и очередной

5

входной сигнал, уравновешиваемый э.т лонным сигналом, и т.д. А при формировании N-разрядной оценки за N-I тактов в одном канале, сигнал которого расположен в другой половине амплитудного диапазона Ur, чём вход ной сигнал, оценка которого сформирована за N тактов, сразу же формирется оценка N-1-го разряда всех тех входных сигналов,, которые расположены в той же половине амплитудного диапазона, что и этот очередной сигнал, и т.д. Таким образом, на получение N-разрядных оценок всех 2 входных сигналов Ug-U,.p затрачивается N тактов в лучшем случае, когда все входные сигналы равны между собой с точностью до двух квантов,

(Ы-1)+2 (N-2)+...+

+2 (N-p)3. тактов в худшем случае, когда во всех каналах входные сигна имеют различные .значения. С уче

лы

том того, что в устрбйстве на счи-г тывание Ы-райрядной оценки в. каждом канале затрачивается время, равное , , полное время Т, преобразования всех 2 сигналов равно:

,)-

) t

т

(N+l).(2 -N+1- 21J 2

Так например, на фиг.5 приведены

временные диаграммы сигналов, формируемых в 4-разрядном преобразователе в процессе уравновешивания сигналов Ug-Uj. Цикл преобразования сигналов инициируется импульсом S1, поступаю щим на второй вход преобразователи. В соответствии с низким уровнем этого импульса S1 4-разрядный сдвиговьй регистр-9 (фиг.1) и счетчики 18, 19 и 20 блока 10 управления (фиг.3)- устанавливаются в нулевое, а триггеры 15 и 16 блока 10 - в .единичное состояния. При этом единичньш сигнал триггера 15 разрешает прохождение через элемент. И 17 импульсов SP тактового генератора 21, которые начинают поступать на входы суммирования счетчика 18 и стробирования - дешифратора 22 с момента t окончания импульса S1, в результате чего на выходах блока 10 -управления формируется последовательность управляющих сигналов (фиг.5). А в соответствии с единичным сигналом С2 триггера 16, поступающим на вход управления ПЗУ 5 и (через инвертор 12) на вход управления ПЗУ 4, выходы ПЗУ 5 подключают

ся

5

а ПЗУ 4 отключаются от информа- ционных входов ОЗУ 6. Таким образом, на младшие и старший информационные входы ОЗУ 6 поступают соответственно циф1)овой эквивалент сигнала 8U /16

ГЛ

и нулевой бит хранящиеся в ячейке .ПЗУ 5. Это содержимое ПЗУ 5 поочередно заносится на интервале в нулевую - третьи ячейки ОЗУ 6 в соответствии с кодом АО-А1 счетчика 19, поступающим на адресные входы мультиплексора 3 и ОЗУ 6, и импульсами-записи высокого уровня, поступающими на вход Запись/чтение ОЗУ 6 с выхода элемента И 11, на один вход которого поступают импульсы с первого выхода дешифратора 22, управляемого счетчиком 18, а на другой - последо-

0

вательно выдвигаемое на инверсньй выход старшего разряда содержш юе регистра 9, синхронизируемого импульсами С5 с третьего выхода дешифрато- ра 22. При этом,когда код АО-А1 счет5 чика 19 равен коду BO-BI счетчика 20,. в котором хранится номер-очередного канала, сигнал которого поразрядно уравновешивается сигналом Пц, на выходе элемента И-НЕ 26 вырабатывается

0 импульс СЗ стробирования памяти компараторов 1, а на выходе элемента И 27 - импульс С4 синхронизации ре- гистра 8. Так, на интервале t, -t в регистр 8 заносится двоичный код восьмерки, в соответствии с которым к моменту t, сигнал Цц устанавливается равным 8Un,/i6, а за время установления сигнала U осуществляется занесение двоичного кода восьмерки

Q в первую ячейку ОЗУ 6, сравнение ее содержимого с содержимым регистра 8 и занесение результата сравнения с выходов блока 7 в регистр 9 путем сдвига его содержимого на один раз- ряд вправо, затем - занесение двоичного кода восьмерки во вторую ячейку ОЗУ 6, сравнение ее содержимого с содержимым регистра 8 и занесение результата сравнения с выходов блока 7 в регистр 9 и т.д. Таким обра0

5

зом. К моменту t устройство оказывается установленным в начальное состояние, т.е. сигнал Цц равен , содержимое каждой из четырех ячеек ОЗУ 6 равно двоичной восьмерке, а в регистре 9 сформирована последовательность сигналов, разрешающих запись всех четырех ячеек ОЗУ 6 в следующем такте tj-t,. По импульсу переноса s3 счетчика 19 триггер 16 устанавливается в момент t. в нулевое состояние, в результате чего с этого момента ПЗУ 5 отключается, а ПЗУ 4 подключается к информационным входам ОЗУ 6. На интервале tj-tj по импульсу СЗ в памяти компараторов запоминаются результаты сравнения с сигналом и

сигналов Ue-Uj

.

ц, равньм В соответствии с последовательностью этих результатов сравнения, поступающих на вход ПЗУ 4, и двоичных номеров каналов АО-А1, формируемых на адресньк входах мультиплексора 3 и ОЗУ 6, на выходах ПЗУ 4 формируются коды двоичных чисел 4,12 12 и 4 (фиг.4), которые поочередно заносятся в ячейки ОЗУ 6 и сравниваются с содержимым регистра 8, в который по импульсу С4 был занесен двоичный код числа 4. Таким образом, к моменту t сигнал Пц равен , содержимое нулевой - третьей ячеек ОЗУ 6 равно соответственно 4,12, 12 и 4, а в регистре 9 сформирована последовательность сигналов, разрешающих запись в нулевую и третью ячейки ОЗУ 6 и запрещающих запись в первую и вторую ячейки ОЗУ 6 в такте tj-tj. На интервале t,-t по импульсу СЗ в памяти компараторов 1.0-1.3 запоминаются результаты сравнения сигналов UQ-UJ с сигналом U,., равным , на выходах ПЗУ 4 поочередно формируются коды двоичных чисел 2,14 14 и 2 в соответствии с выходными сигналами компараторов 1.0-1.3 и предьщущим содержимым нулевой - третьей ячеек ОЗУ 6. В соответствии с содержимым регистра 9 в нулевую и третью ячейки ОЗУ 6 записьшаются двоичные коды числа 2, а в первой и вТо- рой ячейках ОЗУ 6 сохраняются двоичные коды числа 12. Содержимое ячеек ОЗУ 6 сравнивается с содержимым регистра. 8, в который по импульсу С4 был занесен двоичный код числа 2. Таким образом, к моменту t сигнал Пц равен , содержимое нулевой - третьей ячеек ОЗУ 6 равно соответственно 2,12,12 и 2, а в регистре 9 сформирована последовательность сигналов, разрешающих запись в нулевую и третью ячейки ОЗУ 6 и запрещающих запись в первую и вторую ячейки ОЗУ 6 на интервале t4-t,,. На интервале по импульсу СЗ в памяти компараторов 1,0-1.3 запоминаются результаты сравI45I858

0

5

0

нения сигналов

с сигналом Uu

равным , на выходах ПЗУ 4 последовательно формируются коды чисел 3,14 ,14 и 3 в соответствии с выходными сигналами компараторов 1 и предыдущим содержимым нулевой - третьей ячеек ОЗУ 6. В соответствии с содержимым регистра 9 в нулевой и третьей ячейках ОЗУ 6 сохраняются предыдущие коды числа 12. Это содержимое сравнивается с содержимым регистра 8, в который по импульсу С4 был занесен двоичный код числа 3, Так им образом, 15 к моменту t сигнал Цц равен , содержимое нулевой - третьей ячеек ОЗУ 6 равно соответственно 3,12,12 и 3, а в регистре 9 сформирована последовательность сигналов, разрешаю- Q щих запись в нулевую - третью ячейки ОЗУ 6 и запрещающих ее в первую и вторую ячейки ОЗУ 6 на интервале . На интервале , когда адресуется очередной нулевой канал, на 5 втором выходе ПЗУ 4 формируется единичный сигнал, так как при формировании конечной 4-разрядной оценки сигнала UQ адресуется нечетная ячейка ПЗУ 4. При записи этой конечной 0 4-разрядной оценки сигнала Uj, с выходов ПЗУ 4 в ОЗУ 6 на вход схемы 25 блока 10 поступает eдинIiчный сигнал S2, в соответствии с которым на седьмом выходе блока 10 вырабатывается сигнал Готовность данных, по которому с выходов ОЗУ 6 считывается 4- разрядная оценка сигнала UQ, а содержимое счетчика 20 увеличивается на единицу и, таким образом, очередным становится первый канал. На интервале tg-tj по импульсу С4 содержимое первой ячейки ОЗУ 6, равное двоичному числу 12, заносится в ре- Ьистр 8, в соответствии с содержимым регистра 9 в третью ячейку ОЗУ 6 заносится с выходов ПЗУ 4 конечная 4- разрядная оценка сигнала Uj, равная двоичной тройке, а в соответствии с результатами сравнений чисел 12, 12,3 и 3 с содержимым регистра 8, равным двоичному числу 12, в регистре 9 формируется последовательность сигналов, разрешающих запись в первую и вторую ячейки ОЗУ 6 и запрещающих запись в нулевую и третью ячейки ОЗУ 6 на интервале ,. Поскольку старший из 4-разрядных оценок сигналов и, и Uj разряд был определен

5

0

5

в момент t, одновременно с оценкой

этого разряда для сиг.нало.в то за три такта

и

tfi-t.

t7-t

о 6 и t

и и

В

Э

-t.

формируется 4-разрядная оценка очередного сигнала U, путем его уравновешивания сигналом иц, а одновремен - но с-этим формируется 4-разрядная оценка сигнала U2. так как сигналы и/, и и равны между собой. На интервале t.-tg происходит считьшание 4- разрядной оценки сигнала U, , на интервале -tq - 4-разрядной оценки сигнала U, а на интервале t) 4-разрядной оценки сигнала U, котора была сформирована одновременно с оцен- кой сигнала U, так как сигналы U и и равны между собой.

Таким образом, 4-разрядные оценки четырех входных сигналов сформирован за восемь тактов в отличие от известного способа, при котором на их формирование затрачивается 16 тактов.

Как показано выше, описанный способ позволяет получить N-разрядные

Р

оценки всех 2 входнь1х сигналов за

время Т р

и, равное (N+1) (2 N+

2 )t которое существенно

р

меньше времени 2 №t.p, затрачиваемого на формирование N-разрядных оценок 2 входных сигналов известным способом .

Формула изобретения

1 . Способ многоканального аналого- цифрового преобразования, заключаю- цийся в поразрядном уравновешивании входных сигналов поочередно в каяодом канале, начиная с первого, путем сравнения текущего входного сигнала очередного канала с уровнями эталонного сигнала, и формировании выходного кода, о тличающийся тем, что, с целью уменьшения времени п зеобразования, сравнение текущего входного сигнала очередного канала с уровнями эталонного сигнала осуществляют одновременно со сравнением с ними текущих входных сигналов остальных каналов, формируют коды результатов сравнения в каналах и в момент первого их несовпадения для очередного канала запоминают коды соответствующих остальных каналов, а в качестве начального уровня эталонного сигнала для очередного канала используют уровень, соответствующий запомненному коду данного канала.

10

-15

20

5185810

2, Многоканальный аналого-цифровой преобразователь, содержащий компараторы по числу каналов устройства, первые входы которых являются входными Шинами, вторые входы соединены с выходом цифроаналогового преобразователя, входы которого .соединены с соответствующими выходами первого регистра, а выходы компараторов соединены с соответствующими информационными входами мультиплексора, адресные входы которого подключены к первым выходам блока управления, первый вход которого является входом запуска,отличающийся тем, что в .него введены блок сравнения, элемент И, инвертор, второй регистр, два постоянных запоминающих устройст-- ва и оперативное запоминающее устройство , первый и второй информационные входы которого соединены соответственно с первым и вторыми выходами первого и второго постоянных запоми- 25 нающих устройств, первый адресный вход первого из которых подключен к выходу мультиплексора, адресный вход второго постоянного запоминающего устройства соединен с общей шиной, второй адресный вход первого запоминающего устройства подключен к первому выходу оперативного запоминающего устройства и является выходной шиной, а управлянщий вход через инвертор объединен с управляющим входом второго постоянного запоминающего устройства и подключен к второму выходу блока управления, третий и четвертый выходы которого соединены соответственно с входами стробирования соответствующих компараторов и входом синхронизации первого регистра, информационный вход которого объединен с первым входом блока сравнения и подключен к первому выходу оперативного запоминающего устройства, второй выход которого подключен к второму входу блока управления, пятый выход которого соединен с входом синхронизации второго регистра, вход установки нули которого является шиной запуска, информационный вход - с выходом блока сравнения, а выход - с пер- вьм входом элемента И, второй вход которого соединен с шестым выходом

30

35

40

45

50

55

блока управления, а выход - с управляющим входом оперативного запоминающего устройства, при этом второй вход блока сравнения соединен с выходом

1

первого регистра, первые выходы блока управления подключены к адресным входам оперативного запоминающего уст- .ройства, а седьмой и восьмой выходы являются соответственно второй и третьей выходными шинами, причем первые выходы блока управления являются четвертой выходной шиной.

3. Преобразователь по п. 2, о т - личающийс я тем, что блок управления выполнен на двух триггерах, трех счетчиках, тактовом генераторе,, дешифраторе, элементах ИСКЛЮ- ЧАЮЩЕЕ ИЛИ-НЕ, И, И-НЕ, причем S-вхо- ды первого и второго триггеров объединены с первым входом первого элемента И, входами установки нуля счетчиков и являются первым входом блока, второй вход которого соединен с первым входом первого элемента И-НЕ, второй вход которого подключен к инверсному выходу второго триггера, прямой выход которого является вто- рым выходом блока, С-вход соединен с выходом переноса первого счетчика, D-вход подключен к общей шине, вход суммирования первого счетчика соединен с выходом переноса второго счет- чика, а выходы являются первьми выходами блока и подключены к соответствующим первым входам элементов ИСКЛЮЧАЮЩЕЕ Ш1И-НЕ, вторые входы которых

85812

соединены с соответствующими выходами третьего счетчика, а выходы через второй элемент И соединены соответственно с третьим входом первого элемента И-НЕ, первым входом второго элемента И-НЕ и первым входом третьего элемента И,второй вход которого объединен с четвертым входом первого элемента И-НЕ и подключен к первому выходу дешифратора, второй выход которого соединен с вторым входом второго элемента И-НЕ, а третий и четвертый выходы являются со ответственно пятым и ше&тым выходами блока, третьим -и четвертым выходами которого являются соответственно выходы второго элемента И-НЕ и третьего элемента И, при этом выход первого элемента И-НЕ является седьмым выходом блока и соединен с суммирующим входом третьего счетчика, выход переноса которого является восьмьм выходом блока и соединен с С-входом первого триггера, D-вход которого подключен к общей шине, а выход подключен к второму входу первого элемента И, третий вход которого соединен с выходом тактового генератора, а выход подключен к входу суммирования второго счетчика и входу стробирования дешифратора, информационные входы которого соединены с соответствующими выходами второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1829117A1 |

Изобретение относится к измерительной технике и может использоваться в системах сбора информации от большого числа аналоговых датчиков. Целью изобретения является уменьшение времени преобразования. Устройство содержит компараторы по числу каналов устройства, первые входы которых являются входами измеряемых сигналов, вторые входы соединены с выходом цифроаналогового преобразователя (ЦАП), входы стробирования - с третьим выходом блока управления (БУ), а выходы - с информационными входами мультиплексора, выход которого подключен к старшему адресному входу первого постоянного запоминающего устройства (ПЗУ), первые и второй выходы которого и второго ПЗУ соединены соответственно с младшими и старшим информационньми входами оперативного запоминающего устройства памяти (ОЗУ), младшие выходы которого являются вькодными шинами данных и подключены к младшим адресным входам первого ПЗУ, первым входам блока сравнения и информационньм входам регистра, выходы которого подключены к входам ЦАП и вторым входам блока сравнения, выход которого соединен с информационным входом сдвигового регистра, вход установки нуля которого подключен к первому входу БУ и является входом запускающего сигнала, а выход соединен с первым входом эле- мента И, выход которого подключен к входу Запись/чтение ОЗУ, старший выход которого соединен с вторым входом БУ, первый и второй выходы которого подключены к входам синхронизации регистров, четвертый вход - к второму входу элемента И, пятый вход- к входам управления первого и второго ПЗУ соответственно через швертор и непосредственно, шестой и седьмой выходы являются выходами Готовность данных и Конец цикла .преобразования. 2 с, и 1 з.п.ф-лы, 5 ил. 1C 4 СД 00 сд 00

00000001

Ч VV /Y li ii l 7V / /) J /y / / / Ь ; // / 7 3/

б |/|г |J I |й7| /|/ из|/У|/ |

Фи&.д

28

./Х

22 iO 26 14

30

16

Urn

16

tff tf±2 tj.t ti/ts istgifotfi

11-/ r

.

I i I Т I I I If

4f-h-1--+|H

4I1L l- H4-fI ,/.„ 1 IТI Т I,.

-UrU.,

2 C5 CH C3 C6 C2

C7 C8

АО

1 /R

60 Bi

JлJUu|лJL JiJL JuUлJU j

1Л

л-

n

ц Y 7 у f Y I (uL л|лJUU л

Mvfv{

I I

0 2 0 2 0 2 0 2 0 2

- -LbnhV

jI I I 11

rn

ti/ts istgifotfi

I i I Т I I I If

4f-h-1--+|H

л-

n

Mvfv{

jI I I 11

rn

Фае. 5

| Приборы и техника эксперимента, 1985, № 2, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Каган Б.М | |||

| и др | |||

| Системы связи УЕМ с объектами управления в АСУТП, 1978, с | |||

| Рельсовый башмак | 1921 |

|

SU166A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-01-15—Публикация

1986-11-27—Подача