(21)4488735/24

(22)30.09.88

(46) 07.01.91. Бкш. 1 (72) С.С.Мощицкий, Г.И.Тимонькин, С.А.Соколов, С.Н.Ткаченко, В.А.Ткаче нко и В.С.Харченко

(53)681.374(088.8)

(56)Авторское свидетельство СССР Г 875383, кл. G 06 F 11/00, 1980.

Авторское свидетельство СССР В- 1092512, кл. G 06 F 11/18, 1983.

Авторское свидетельство СССР № 1538759, 1988.

(54)УСТРОЙСТВО. ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ

(57)Изобретенье относится к автоматике и вычислительной технике и может быть использовано при построении резервированных автоматических систем управления повышенной точности, например, в системах обработки и передачи служебной и измерительной

информации. Цель изобретения - повышение достоверности функционирования устройства при работе с измерительной информацией. Устройство содержит регистры сдвига вправо, блок вычисления среднего значения, дешифратор, коммутатор, мультиплексор, счетчик адреса, триггеры, генератор импульсов, мажоритарный элемент, сумматоры по модулю два, блоки элементов И, элементы ШШ, одновибратор, регистр хранения кода. Сущность изобретения заключается в повышении достоверности и точности функционирования устройства путем раздельной обработки старших разрядов кодовых сообщенийj старших разрядов измерительной информации и младших разрядов кодовых сообщений,которые в одном цикле измерения могут отличаться в каналах вследствие различных значений случайных ошибок, а также путем анализа результата проверок на четность.3 ил.

Q $

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для программного управления | 1987 |

|

SU1432461A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1667280A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении резервированных автоматических систем управления повышенной точности,.в частности в системах обработки и передачи измерительной информации.

Цель изобретения - повышение достоверности функционирования устройства при работ е с измерительной информацией .

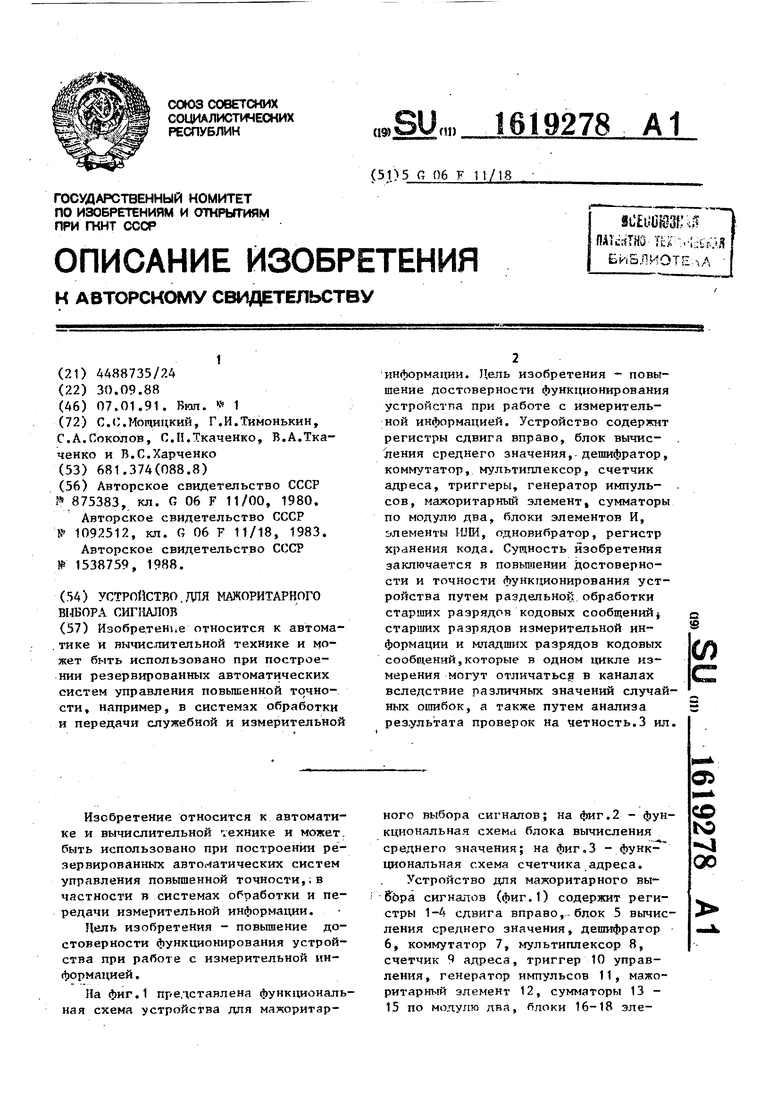

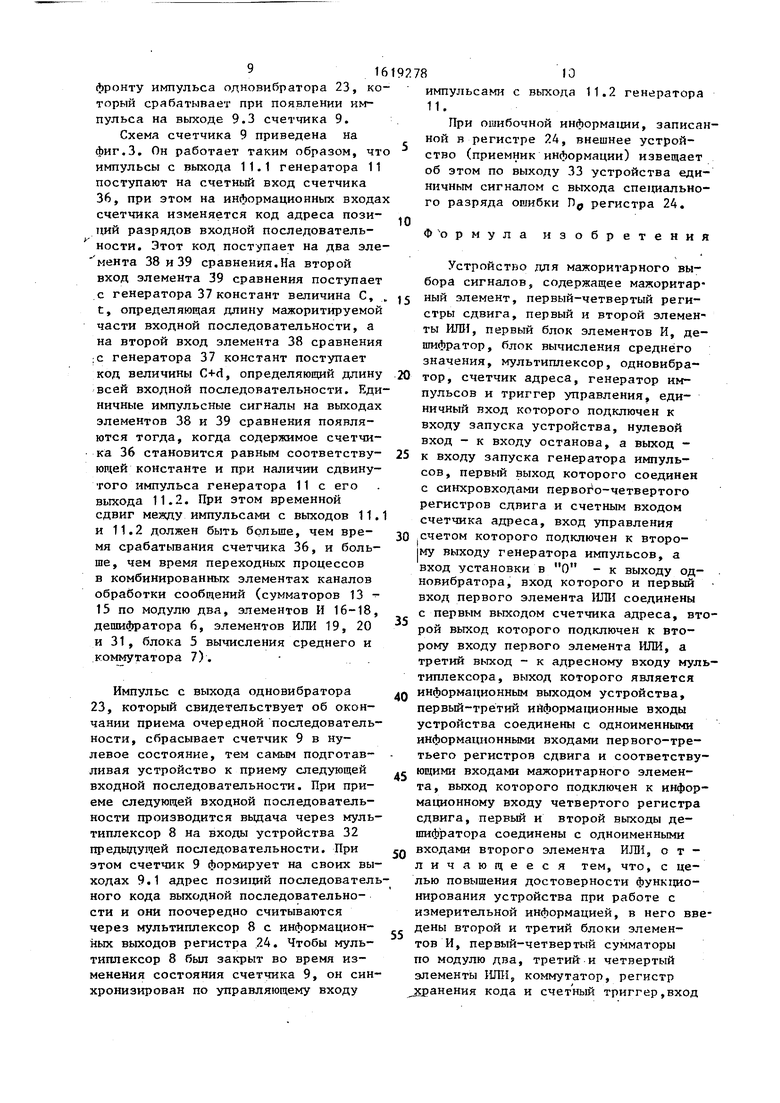

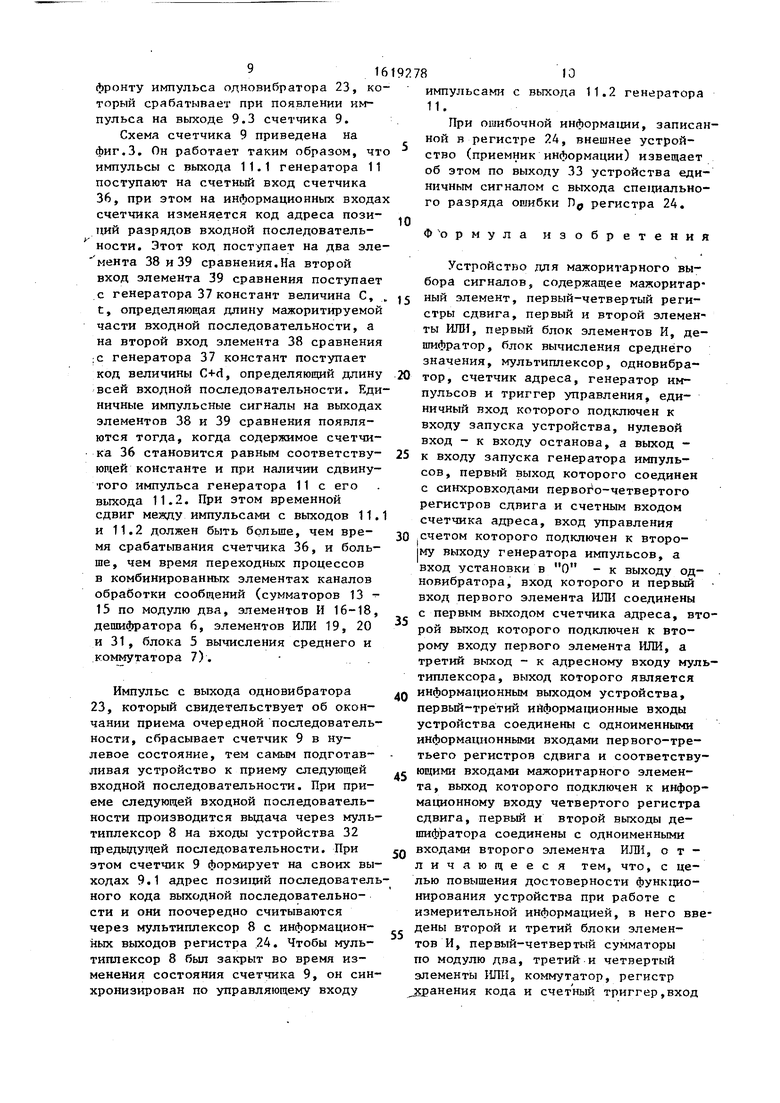

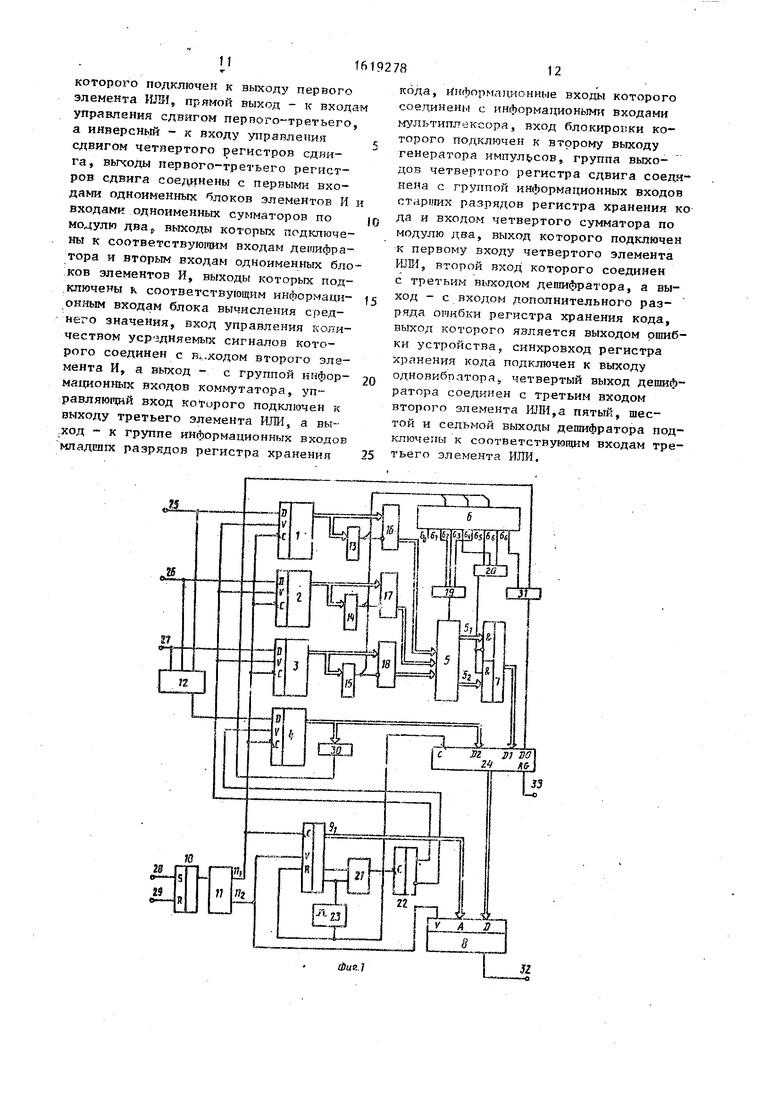

На фиг.1 представлена функциональная схема устройства для махоритарного выбора сигналов; на фиг.2 - функциональная схема блока вычисления среднего значения; на фиг.З - функ- циональная схема счетчика адреса.

Устройство для мажоритарного выбора сигналов (фиг.1) содержит регистры 1-й сдвига вправо, блок 5 вычисления среднего значения, дешифратор 6, коммутатор 7, мультиплексор 8, счетчик 9 адреса, триггер 10 управления, генератор импульсов 11, мажоритарный элемент 12, сумматоры 13 - 15 по модулю два, блоки 16-18 элес

со to 00

316

ментов И, элементы ИЛИ 19-21, счетный триггер 22, одновибратор 23, регистр 24 хранения кода, информацион - ные входы 25-27, вход 28 запуска, вход 29 останова, сумматор 30 по модулю два, элемент ИЛИ 31, информационный выход 32, выход 33 сигнала ошибки.

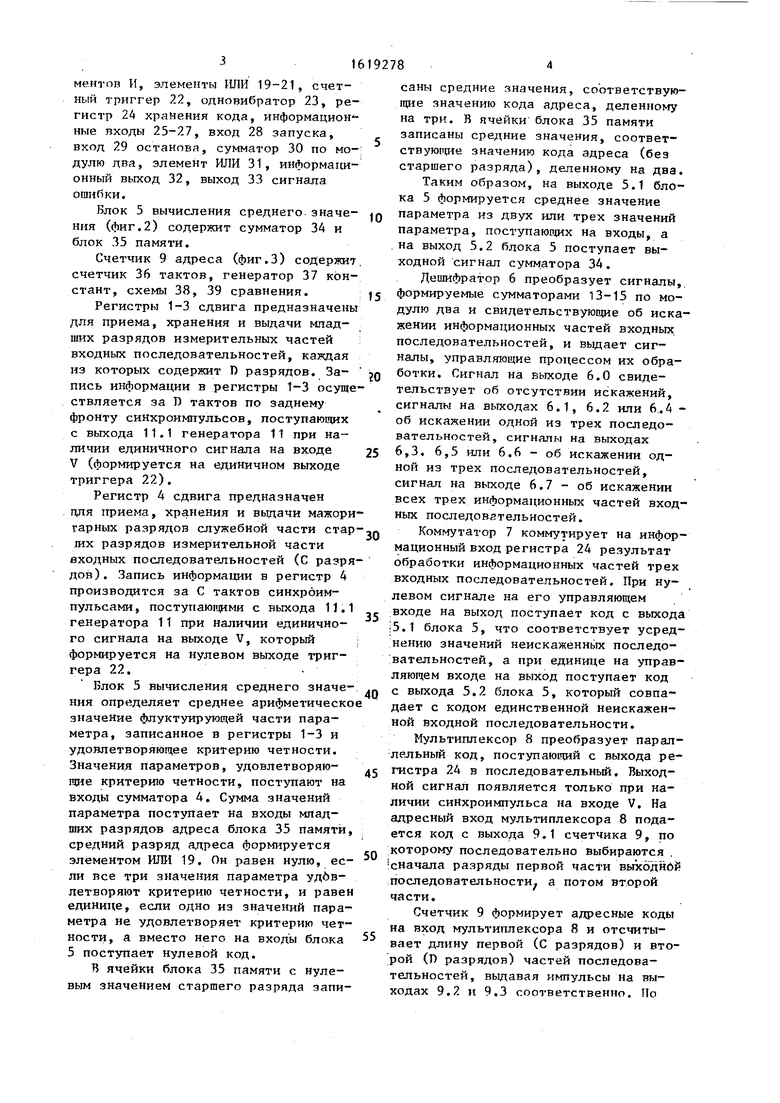

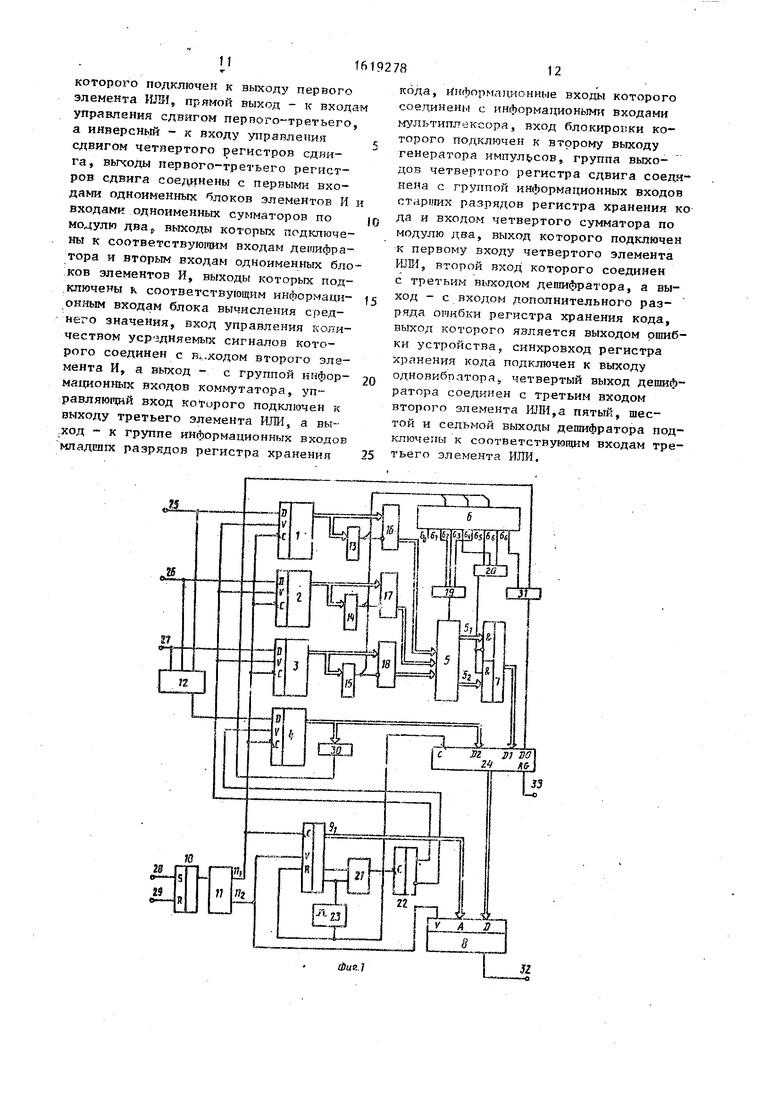

Блок 5 вычисления среднего значения (фиг.2) содержит сумматор 34 и блок 35 памяти.

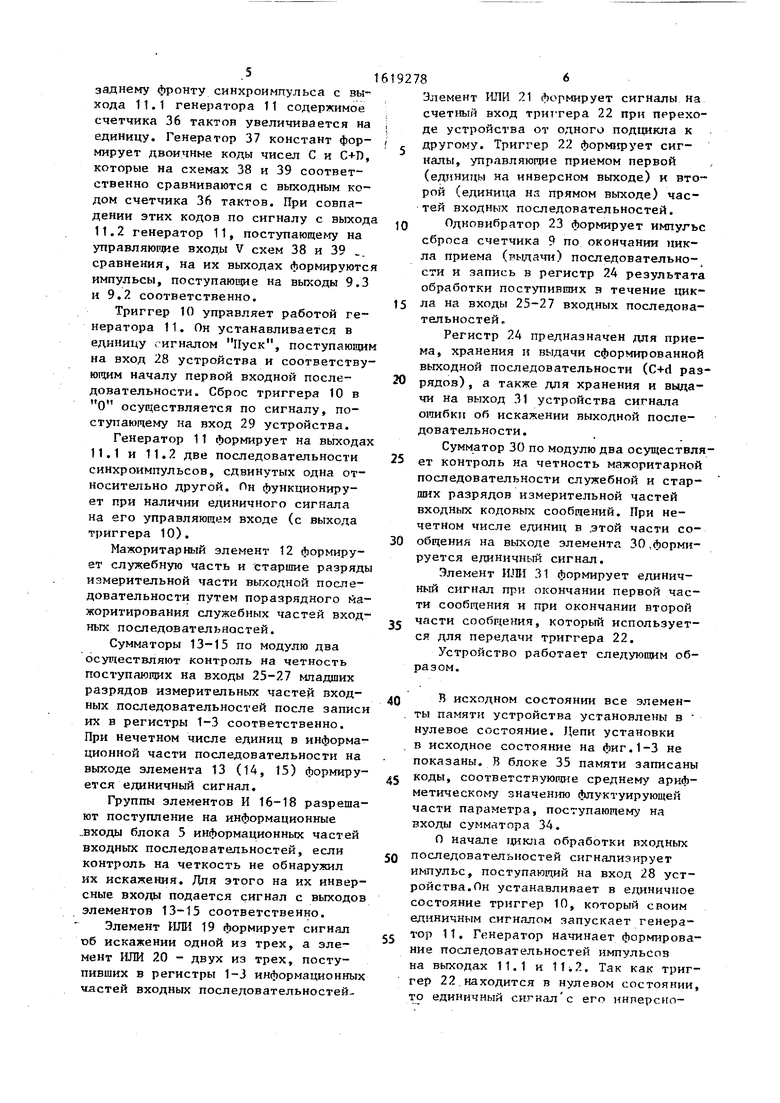

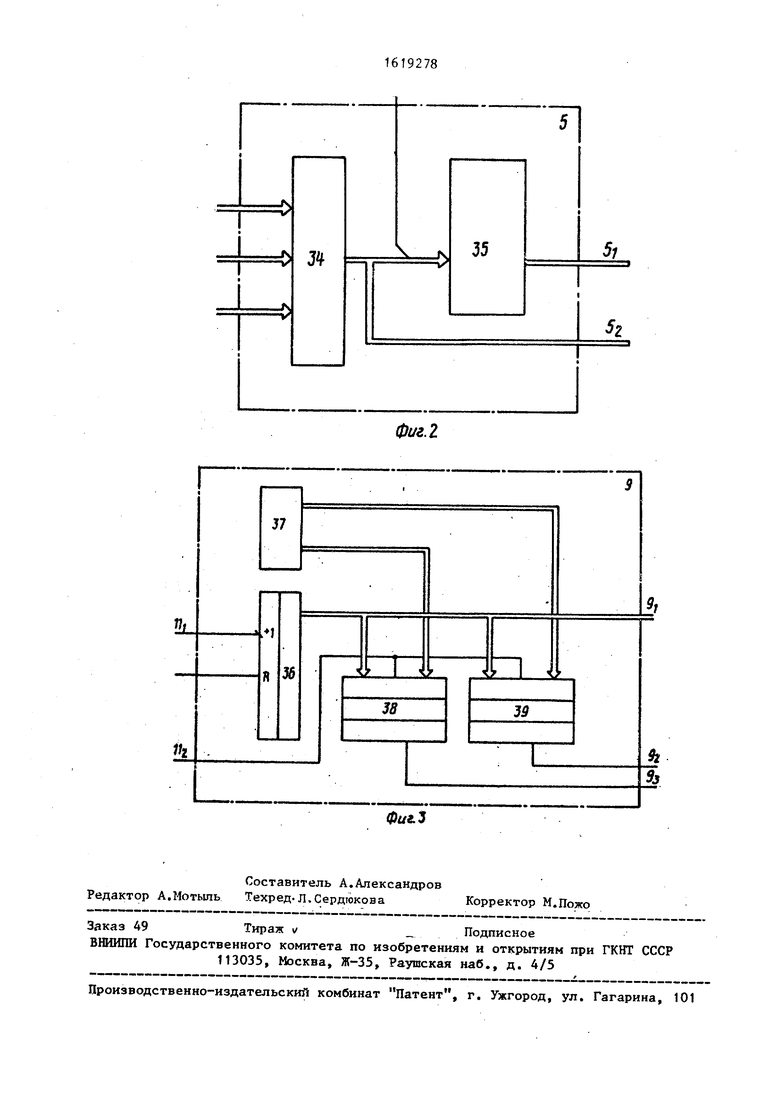

Счетчик 9 адреса (фиг.З) содержит счетчик 36 тактов, генератор 37 констант, схемы 38, 39 сравнения.

Регистры 1-3 сдвига предназначены для приема, хранения и выдачи младших разрядов измерительных частей входных последовательностей, каждая из которых содержит D разрядов. Запись информации в регистры 1-3 осуществляется за D тактов по заднему фронту синхроимпульсов, поступающих с выхода 11.1 генератора 11 при наличии единичного сигнала на входе V (формируется на единичном выходе триггера 22).

Регистр 4 сдвига предназначен для приема, хранения и выдачи мажоритарных разрядов служебной части стар тх разрядов измерительной части входных последовательностей (С разрядов). Запись информации в регистр 4 производится за С тактов синхроимпульсами, поступающими с выхода 11.1 генератора 11 при наличии единичного сигнала на выходе V, который формируется на нулевом выходе триггера 22.

Блок 5 вычисления среднего значения определяет среднее арифметическо значение флуктуирующей части параметра, записанное в регистры 1-3 и удовлетворяющее критерию четности. Значения параметров, удовлетворяющие критерию четности, поступают на входы сумматора 4. Сумма значений параметра поступает на входы младших разрядов адреса блока 35 памяти, средний разряд адреса формируется элементом ИЛИ 19. Он равен нулю, если все три значения параметра удбв- летворяют критерию четности, и равен единице, если одно из значений параметра не удовлетворяет критерию четности, а вместо него на входы блока 5 поступает нулевой код.

В ячейки блока 35 памяти с нулевым значением старшего разряда запи

0

5

о

5

л

5

0

5

0

5

саны средние значения, соответствующие значению кода адреса, деленному на три. В ячейки блока 35 памяти записаны средние значения, соответствующие значению кода адреса (без старшего разряда), деленному на два.

Таким образом, на выходе 5.1 блока 5 формируется среднее значение параметра из двух или трех значений параметра, поступающих на входы, а на выход 5.2 блока 5 поступает выходной сигнал сумматора 34.

.Дешифратор 6 преобразует сигналы, формируемые сумматорами 13-15 по модулю два и свидетельствующие об искажении информационных частей входных последовательностей, и выдает сигналы, управляющие процессом их обработки. Сигнал на выходе 6.0 свидетельствует об отсутствии искажений, сигналы на выходах 6.1, 6.2 или 6.4 - об искажении одной из трех последовательностей, сигналы на выходах 6,3, 6,5 или 6.6 - об искажении одной из трех последовательностей, сигнал на выходе 6.7 - об искажении всех трех информационных частей входных последовательностей.

Коммутатор 7 коммутирует на информационный вход регистра 24 результат обработки информационных частей трех входных последовательностей. При нулевом сигнале на его управляющем входе на выход поступает код с выхода 5.1 блока 5, что соответствует усреднению значений неискаженных последовательностей, а при единице на управляющем входе на выход поступает код с выхода 5.2 блока 5, который совпадает с кодом единственной неискаженной входной последовательности.

Мультиплексор 8 преобразует параллельный код, поступающий с выхода регистра 24 в последовательный. Выходной сигнал появляется только при наличии синхроимпульса на входе V. На адресный вход мультиплексора 8 подается код с выхода 9.1 счетчика 9, по которому последовательно выбираются сначала разряды первой части выходной последовательности, а потом второй части.

Счетчик 9 формирует адресные коды на вход мультиплексора 8 и отсчитывает длину первой (С разрядов) и второй (Т) разрядов) частей последовательностей, выдавая импульсы на выходах 9.2 и 9.3 соответственно. По

51

заднему фронту синхроимпульса с выхода 11.1 генератора 11 содержимое счетчика 36 тактов увеличивается на единицу. Генератор 37 констант формирует двоичные коды чисел С и C+D, которые на схемах 38 и 39 соответственно сравниваются с выходным кодом счетчика 36 тактов. При совпадении этих кодов по сигналу с выхода 11.2 генератор 11, поступающему на управляющие входы V схем 38 и 39 . сравнения, на их выходах формируются импульсы, поступающие на выходы 9.3 и 9.2 соответственно.

Триггер 10 управляет работой генератора 11. Он устанавливается в единицу сигналом Пуск, поступающим на вход 28 устройства и соответствующим началу первой входной последовательности. Сброс триггера 10 в О осурдествляется по сигналу, поступающему на вход 29 устройства.

Генератор 11 формирует на выходах 11.1 и 11.2 две последовательности синхроимпульсов, сдвинутых одна относительно другой. Он функционирует при наличии единичного сигнала на его управляющем входе (с выхода триггера 10).

Мажоритарный элемент 12 формирует служебную часть и старшие разряды измерительной части выходной последовательности путем поразрядного ма- жоритирования служебных частей входных последовательностей.

Сумматоры 13-15 по модулю два осуществляют контроль на четность поступающих на входы 25-27 младших разрядов измерительных частей входных последовательностей после записи их в регистры 1-3 соответственно. При нечетном числе единиц в информационной части последовательности на выходе элемента 13 (14, 15) формируется единичный сигнал.

Группы элементов И 16-18 разрешают поступление на информационные .входы блока 5 информационных частей входных последовательностей, если контроль на четкость не обнаружил их искажения. Для этого на их инверсные входы подается сигнал с выходов элементов 13-15 соответственно.

Элемент ИЛИ 19 формирует сигнал об искажении одной из трех, а элемент ИЛИ 20 - двух из трех, поступивших в регистры 1-J информационных частей входных последовательностей192786

Элемент ИЛИ 21 Аормирует сигналы на счетным вход триггера 22 при перехо- де устройства от одного подцикла к г другому. Триггер 22 Аормирует сигналы, управляющие приемом первой (единицы на инверсном выходе) и второй (единица на прямом выходе) частей входных последовательностей.

jg Одновибратор 23 формирует импугьс сброса счетчика 9 по окончании цикла приема (выдачи) последовательно- сти и запись в регистр 24 результата обработки поступивших з течение цик15 ла на входы 25-27 входных последовательностей.

Регистр 24 предназначен для приема, хранения и выдачи сформированной выходной последовательности (C+d раз20 рядов), а также для хранения и выдачи на выход 31 устройства сигнала ошибки об искажении выходной последовательности.

Сумматор 30 по модулю два осуществля25 ет контроль на четность мажоритарной последовательности служебной и старших разрядов измерительной частей входных кодовых сообщений. При нечетном числе единиц в .этой части со30 общения на выходе элемента 30,формируется единичный сигнал.

Элемент ИЛИ 31 формирует единичный сигнал при окончании первой части сообщения и при окончании второй

ас части сообщения, который используется для передачи триггера 22.

Устройство работает следующим образом.

40 В исходном состоянии все элементы памяти устройства установлены в нулевое состояние. Цепи установки в исходное состояние на фиг.1-3 не показаны. В блоке 35 памяти записаны

45 коды, соответствующие среднему арифметическому значению флуктуирующей части параметра, поступающему на входы суммнтора 34.

О начале цикла обработки входных

50 последовательностей сигнализирует импульс, поступающий на вход 28 устройства. Он устанавливает в единичное состояние триггер 10, который своим единичным сигналом запускает генерасс тор 11. Генератор начинает формирование последовательностей импульсов на выходах 11.1 и 11.2. Так как триггер 22 находится в нулевом состоянии, то единичный сигнал с его инверсного выхода разрешает запись информации в регистр 4.

Старшие разряды входных последовательностей, соответствующие служебным и старшим разрядам измерительных частей сообщения, поступающим на входы 25-27 устройства,, мажоритируются на элементе 12 и поступают на вход D регистра 4 сдвига вправо. Запись зна чений разрядов в регистр 4 осуществляется по заднему фронту синхроимпульсов, поступающих на вход С. По прохождении С тактов в регистре 4 запишется результат мажоритирова- ния служебных и старших разрядов измерительных частей входных последовательностей. По очередному импульсу с выхода 11.2 генератора 11 на выходе 9.1 счетчика 9 появится единичный импульс, который, пройдя через элемент ШШ 21, задним фронтом переключит триггер 22 в единичное состояние. При этом регистр 4 по управляющему входу будет закрыт, а регистры 1-3 единичным сигналом с прямого выхода триггера 22 откроются. В результате последующие d импульсов входных последовательностей, определяющие младшие разряды измерительной информации, подверженной флуктуациям, будут со входов 25-27 записываться соответственно в регистры 1-3. После записи полной входной последовательности в регистры 1-4 с выходов последних записанная информация будет проверяться соответственно сумматорами 13-15 и 30 по модулю два, на четность. Если в одном или нескольких регистрах из числа 1-3 контроль информации на четность не выполняется, то соответствующий сумматор выдает единичный сигнал на инверсный вход соответствующего элемента И из числа 16-18. При этом искаженная информация с соответствующего регистра на вход блока вычисления среднего не поступает. Одновременно результаты контроля на четность информации в каждом из регистров 1-3 поступают с выходов элементов 16М8 в виде трехразрядного кода на входы дешифратора 6, выходы которого соот ветствующим образом подключены к элементам ШШ 19, 20 и 31. Если ошиб ка по нечетности обнаружена в одном канале, то единичный сигнал появит- ся на выходе элемента ИЛИ 19, если в

0

5

0

5

0

5

0

5

0

5

двух каналах, то на выходе элемента ИЛИ 20, если во всех трех каналах, то на выходе элемента ИЛИ 31. Если ошибки нет, то на выходах всех элементов ИЛИ 19, 20 и 31 присутствуют нулевые сигналы.

Если ошибки в каналах не обнаружено, то в вычислении среднего значения участвует информация со всех трех регистров 1-3. При этом с выходов элементов И 16-18 она поступает на сумматор 34 блока 5 вычисления среднего значения. Полученная сумма в качестве адресного кода поступает на вход элемента 35 памяти. При этом старший разряд адреса, снимаемый с выхода элемента ИЛИ 19,равен нулю, т.е. обращение будет производиться к области памяти, в которой хранятся средние значения параметра, полученные при делении суммы на три. Полученное среднее значение флуктуирующей части измеряемой величины с выхода 5.1 блока выделения среднего через открытый коммутатор 7 поступит на вход Т)ц регистра 24 для записи в качестве младших разрядов обработанного сообщения.

Если в процессе контроля на четность будет обнаружена ошибка в одном из каналов, то появится единичный сигнал на выходе элемента ИЛИ 19, этот сигнал в качестве старшего разряда адресного кода поступит на элемент 35 памяти блока 5 вычисления среднего. При этом обращение проходит к области памяти, где хранятся сред- ние значения из двух входных величин. Полученное среднее значение, как в предыдущем случае, будет передаваться на входы 1) регистра 24.

При обнаружении ошибок сразу в двух каналах единичный сигнал с выхода элемента ИЛИ 20 откроет вторую половину коммутатора 7 и на входы DH регистра 24 будет с выхода 5.2 блока 5 вычисления среднего поступать информация непосредственно с того канала, в котором не обнаружена ошибка, минуя элемент 35 памяти.

Если ошибки обнаружены во всех трех регистрах 1-3, либо в первой, мажоритарной, части сообщения, то единичный сигнал поступит с выхода элемента ИЛИ 31 на вход D0 специального разряда ошибки регистра 24. Завись обработанного сообщения в ре- гистр 24 осуществляется по заднему

10

91619278

фронту импульса одновибратора 23, который срабатывает при появлении импульса на выходе 9.3 счетчика 9.

Схема счетчика 9 приведена на иг.З. Он работает таким образом, что импульсы с выхода 11.1 генератора 11 поступают на счетный вход счетчика 36, при этом на информационных входах счетчика изменяется код адреса позиций разрядов входной последовательности. Этот код поступает на два эле- мента 38 и 39 сравнения.На второй вход элемента 39 сравнения поступает с генератора 37 констант величина С, . t, определяющая длину мажоритируемой части входной последовательности, а на второй вход элемента 38 сравнения с генератора 37 констант поступает код величины C+d, определяющий длину всей входной последовательности. Единичные импульсные сигналы на выходах элементов 38 и 39 сравнения появляются тогда, когда содержимое счетчика 36 становится равным соответствующей константе и при наличии сдвинутого импульса генератора 11 с его выхода 11.2. При этом временной сдвиг между импульсами с выходов 11.1 и 11.2 должен быть больше, чем время срабатывания счетчика 36, и больше, чем время переходных процессов в комбинированных элементах каналов обработки сообщений (сумматоров 13 - 15 по модулю два, элементов И 16-18, дешифратора 6, элементов ИЛИ 19, 20 и 31, блока 5 вычисления среднего и коммутатора 7).

25

30

35

15

20

|м в н в с р р тр т дл и п ус ин т ющ та ма сд ши вх л ль ни из де то по эл хр

Импульс с выхода одновибратора 23, который свидетельствует об окончании приема очередной последовательности, сбрасывает счетчик 9 в нулевое состояние, тем самым подготавливая устройство к приему следующей входной последовательности. При приеме следующей входной последовательности производится выдача через мультиплексор 8 на входы устройства 32 предыдущей последовательности. При этом счетчик 9 формирует на своих выходах 9.1 адрес позиций последовательного кода выходной последовательности и они поочередно считываются через мультиплексор 8 с информационных выходов регистра 24. Чтобы мультиплексор 8 был закрыт во время изменения состояния счетчика 9, он синхронизирован по управляющему входу

8

10

выхода

импульсами 11.

При ошибочной информации, записанной в регистре 24, внешнее устройство (приемник информации) извещает об этом по выходу 33 устройства единичным сигналом с выхода специального разряда ошибки П0 регистра 24.

Ф чо р м у л а изобретения

5

0

5

5

0

5

5

0

Устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент, первый-четвертый регистры сдвига, первый и второй элементы ИЛИ, первый блок элементов И, дешифратор, блок вычисления среднего значения, мультиплексор, одновибра- тор, счетчик адреса, генератор импульсов и триггер управления, единичный вход которого подключен к входу запуска устройства, нулевой вход - к входу останова, а выход - к входу запуска генератора импульсов, первый выход которого соединен с синхровходами первого-четвертого регистров сдвига и счетным входом счетчика адреса, вход управления счетом которого подключен к второ- |му выходу генератора импульсов, а вход установки в О - к выходу одновибратора, вход которого и первый вход первого элемента ИЛИ соединены с первым выходом счетчика адреса, второй выход которого подключен к второму входу первого элемента ИЛИ, а третий выход - к адресному входу мультиплексора, выход которого является л информационным выходом устройства, первый-третий информационные входы устройства соединены с одноименными информационными входами первого-третьего регистров сдвига и соответствующими входами мажоритарного элемента, выход которого подключен к информационному входу четвертого регистра сдвига, первый и второй выходы дешифратора соединены с одноименными входами второго элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности функционирования устройства при работе с измерительной информацией, в него введены второй и третий блоки элементов И, первый-четвертый сумматоры по модулю два, третий и четвертый элементы ИЛИ, коммутатор, регистр хранения кода и счетный триггер,вход

которого подключен к выходу первого элемента ИЛИ, прямой выход - к входа управления сдвигом первого-третьего, а инверсный - к входу управления сдвигом четвертого регистров сдвига, выходы первого-третьего регистров сдвига соединены с первыми входами одноименных блоков элементов И входами одноименных сумматоров по модулю два выходы которых подключены к соответствующим входам дешифратора и вторым входам одноименных блоков элементов И, выходы которых подключены к соответствующим ннйормаци- окяым входам блока вычисления среднего значения, вход управления количеством усредняемых сигналов которого соединен с выходом второго элемента И, а выход - с группой информационных входов коммутатора, управляющий вход которого подключен к выходу третьего элемента ИЛИ, а выход - к группе информационных входов младших разрядов регистра хранения

Ю

0

5

кода, Информационные входы которого соединены с информациоными входами мультиплексора, вход блокировки которого подключен к второму выходу генератора импульсов, группа выходов четвертого регистра сдвига соединена с группой информационных входов старших разрядов регистра хранения ко да и входом четвертого сумматора по модулю два, выход которого подключен к первому входу четвертого элемента ИЛИ, второй вход которого соединен с третьим выходом дешифратора, а выход - с входом дополнительного разряда ошибки регистра хранения кода, выход которого является выходом ошибки устройства синхровход регистра хранения кода подключен к выходу одновкбпатора., четвертый выход дешифратора соединен с третьим входом второго элемента ИЛИ,а пятый, шестой и седьмой выходы дешифратора подключены к соответствующим входам третьего элемента ИЛИ.

1

;

Я

1k

35

5;

фиг.2

о

о

о

J

J4

fc

Авторы

Даты

1991-01-07—Публикация

1988-09-30—Подача