Изобретение относится к импульсной технике и может быть использовано в устройствах управления вычислительных систем.

Целью изобретения является повышение функциональной надежности.

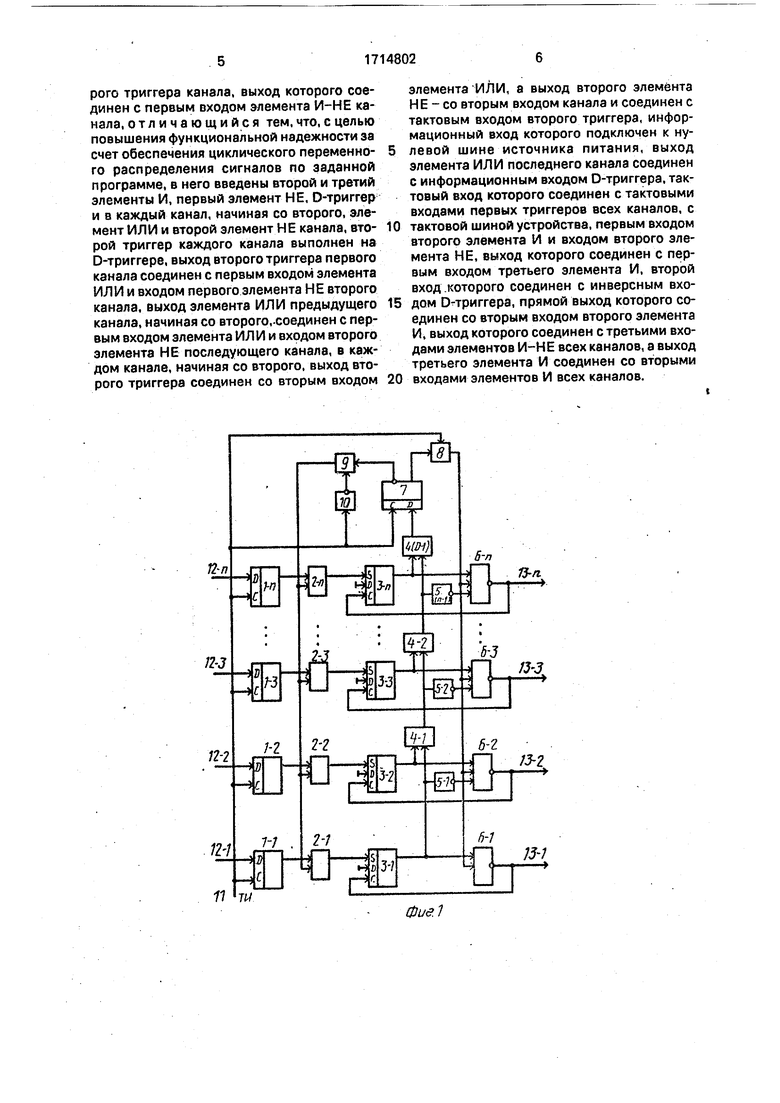

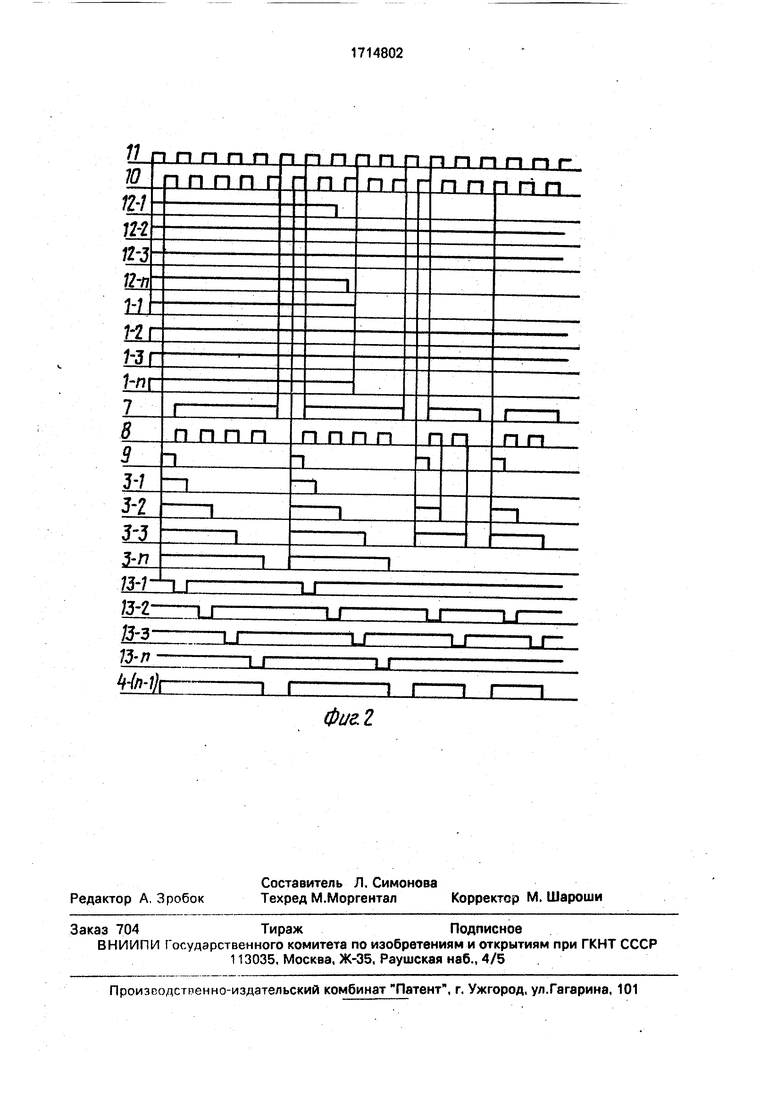

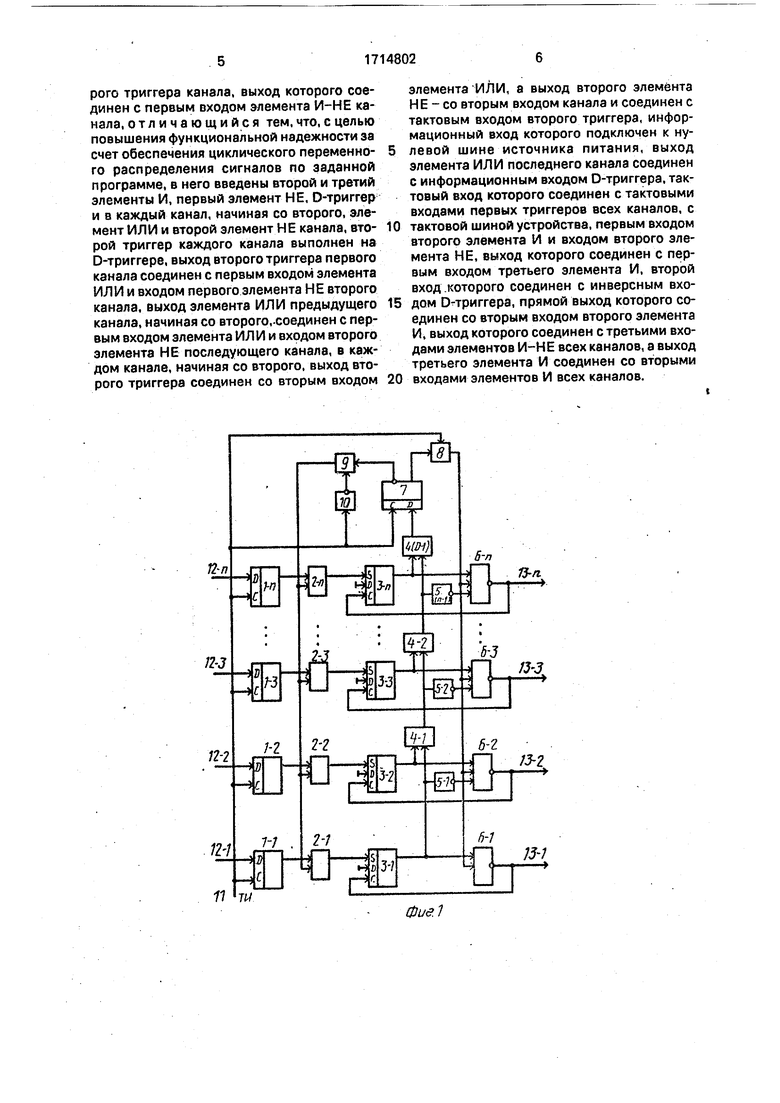

На фиг. 1. приведена схема распределителя; на фиг.2 - временная диаграмма его работы.

Распределитель содержит в каждом канале первый триггер 1.11.п, выполненный на D-триггере, первый элемент И

2.12.П, второй триггер 3.1,....3.п (на Dтриггере), элемент ИЛИ 4.1,...,4.п, первый

элемент НЕ 5.15.п, элемент И-НЕ

6.16.П, а также О-триггер.7, второй элемент И 8, третий элемент И 9, второй элемент НЕ 10, шину 11 тактовых импульсов, входы 12.112.п установки программы задействования каналов распределителя, выходы 13.1,...,13.п каналов распределителя. Информационные D-входы триггеров 1 являются входами 12 распределителя для задания программы. Шина 11 соединена с С-входами триггеров 1, триггера 7, первым

входом элемента И 8 и через элемент НЕ 10 - с первым входом элемента И 9. Выход элемента И 9 соединен с первыми входами элементов 2.1,....2.п, вторые входы которых

соединены с выходами триггеров 1.11.п.

Выходы элементов 2.1,...,2.п соединены с

единичными входами триггеров 3.1З.п.

Выходы триггеров 3.1З.п соединены с

первыми входами элементов 6.1,...,6.п и входами соответствующих элементов 4.14.п.

Выход каждого элемента 4.I соединен с пер.вым входом элемента 4,i+1 и через элементы 5.i -со входом элемента 6.i+1, третьи входы элементов 6.1,...,6.п соединены с выходом элемента И 8. Выходы элементов 6.1,...,6,п

являются выходами 13.113.п каналов

распределителя и соединены с тактовыми С-входами соответствующих триггеров 3.1,...,3.п, D-входы которых соединены с нулевой шиной источника питания. Выход элемента 4.(п-1) соединен с О-входом триггера 7, прямой и инверсный выходы которого соединены соответственно со вторыми входами элементов И 8, 9. На выходах 13.113.п

распределителя формируются отрицательные импульсы, для получения положительных выходных импульсов выходы 13 подключаются к инверторам (на схеме не показаны).

Устройство работает следующим обра- 5 зом.

В исходном состоянии все триггеры установлены в нулевое положение (цепи начальной установки на схеме не показаны). Программа распределения импульсов на ка- 10 налах задается в виде потенциальных сигналов, поступающих по входам устройства, например, на входы 12.1, 12,2,,..,12.п. Эти сигналы подаются на D-входы соответствующих триггеров 1.1,...1.п. По фронту такто- 15 вого импульса с шины 11 соответствующие триггеры 1.1, 1.2,1.3 1.П устанавливаются в единичное состояние и открывают соответствующие элементы 2.1,2.2,2.3,2.п. Триггер 7 в нулевом положении закрывает элемент 20

-И 8 и открывает элемент И 9. Тактовые импульсы с шины 11 инвертируются элементом НЕ 10. По фронту инверсного тактового импульса, поступающего с выхода элемента 10 через элемент 9 на вторые входы элемен- 25 тов 2.1,...,2.п устанавливаются в единичное состояние соответствующие триггеры 3.13.п. Триггеры 3.1,...,3.п через элементы 4.1,...,4.п и 5.1,...,5.п управляют элементами 6.1б.п таким образом, что каждый 30

предыдущий из триггеров 3.1 закрывает последующие элементы 6.1+1, соединенные с последующими триггерами 3.1+1. В рассматриваемом случае триггер 3.1, находящийся в единичном состоянии, открывает соответ- 35 ствующий ему элемент 6.1, через элемент 5.1 запирает элемент 6.2, через элементы 4.1, 5.2 запирает элемент 6.3 через элементы И 2, НЕ 5.(п-1)-элемент И-НЕ 6.п. Триггер 3.2 подготавливает к открыванию 40 соответствующий элемент 6.2, через элементы 4.1,4.2,5.2,5(п-1) закрывает последующие элементы 6.3, б.п и т.д. После установки хотя бы одного из триггеров 3.1 в единичное состояние формируется потен- 45 циальный единичный сигнал на выходе последнего элемента ИЛИ 4.(п-1), который подается на D-вход триггера 7, По фронту следующего тактового импульса с шины 11 триггер 7 устанавливается в единичное со- 50 стояние, закрывает элемент И 9 и открывает элемент И 8. При этом тактовые импульсы через элемент И 8 поступают на входы элементов 6.1,...,6.п. Так как из всех элементов И-НЕ подготовлен к открыванию только 55 элемент 6.1, а все остальные заблокированы, то текущий тактовый импульс проходит через этот элемент И-НЕ 6.1 на выход 13.1 в виде отрицательного импульса. С выхода элемента И-НЕ 6.1 этот импульс подается

на тактовый вход триггера 3.1, на D-вход которого подан нулевой потенциал источника питаний. По фронту отрицательного импульса триггер 3.1 устанавливается в иулезое положение. При этом снимается сигнал запрета с выхода элемента НЕ 5.1 и открывается следующий элемент И-НЕ 6.2, подготовленный к открыванию следующим сработанным триггером 3.2, Очередной тактовый импульс через элемент И-НЕ 6.2 поступает на выход 13.2 и устанавливает триггер 3.2 в нулевое положение. После обнуления триггеров 3.1,3.2 снимается сигнал запрета с выходов элементов ИЛИ 4.1, НЕ 5.2 и открывается элемент И-НЕ 6.3 и т.д. Таким образом, после одного цикла прохождения п тактовых импульсов все триггеры 3,1,...,3.г, установленные в единичное состояние в соответствии с заданной программой, обнуляются, на заданных выходах 13 формируются распределенные последовательности импульсов, снимается сигнал с выхода элемента ИЛИ 4.(п-1). По фронту текущего тактового импульса триггер 7 вновь устанавливается в единичное состояние, закрывается элемент И 8 и открывается эле-мент И 9. Инверсный тактовый импульс через элементы И 9, И 2 снова устанавливает вединичное состояние триггеры 3.1З.п

в соответствии с заданной программой и описанный выше процесс повторяется. Таким образом обеспечивается циклическое распределение импульсов на выходах

13.113.п устройства. Если в процессе

распредения импульсов программа задействования каналов изменилась, например, в единичное состояние установлены триггеры 1,2, 1.3, триггеры 1.1, 1.П - в нулевое положение, то инверсный тактовый импульс установит в единичное состояние триггеры 3,2,3.3. Триггер 3,2 через элементы ИЛ И 4.1, НЕ 5,2 закрывает элемент И-НЕ 6,3 и открывает элемент И-НЕ 6,2, Сигнал запрета через элемент НЕ 5.1 не поступает, т.к. триггеры 1.1,3.1 находятся в нулевом состоянии. После прохождения двух тактовых импульсов, аналогично описанному выше формируется распределенная последовательность импульсов на выходах 13,2, 13.3 устройства. Аналогично работает устройство при любых других комбинациях программного распределения сигналов на входах

12.112,п устройства.

Формула изобретен 11 я Распределитель, содержащий в каждом канале первый триггер, информационный вход которого является установочным входом канала, а выход соединен с первым входом первого элемента И канала, выход которого соединен с единичным входом втоporo триггера канала, выход которого соединен с первым входом элемента И-НЕ канала, отличающийся тем, что, с целью повышения функциональной надежности за счет обеспечения циклического переменного распределения сигналов по заданной программе, в него введены второй и третий элементы И, первый элемент НЕ, О-триггер и в каждый канал, начиная со второго, элемент ИЛИ и второй элемент НЕ канала, второй триггер каждого канала выполнен на D-триггере, выход второго триггера первого канала соединен с первым входом элемента ИЛИ и входом первого элемента НЕ второго канала, выход элемента ИЛИ предыдущего канала, начиная со второго,.соединен с первым входом элемента ИЛИ и входом второго элемента НЕ последующего канала, в каждом канале, начиная со второго, выход второго триггера соединен со вторым входом

элемента ИЛИ, а выход второго элемента НЕ - со вторым входом канала и соединен с тактовым входом второго триггера, информационный вход которого подключен к нулевой шине источника питания, выход элемента ИЛИ последнего канала соединен с информационным входом О-триггера, тактовый вход которого соединен с тактовыми входами первых триггеров всех каналов, с

тактовой шиной устройства, первым входом второго элемента И и входом второго элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход .которого соединен с инверсным входом О триггера, прямой выход которого соединен со вторым входом второго элемента И, выход которого соединен с третьими входами элементов И-Н Е всех каналов, а выход третьего элемента И соединен со вторыми

входами элементов И всех каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов | 1986 |

|

SU1325688A1 |

| Частотный дискриминатор | 1987 |

|

SU1448404A1 |

| Счетчик импульсов | 1983 |

|

SU1187263A1 |

| Счетчик импульсов | 1983 |

|

SU1150761A2 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Распределитель импульсов | 1987 |

|

SU1541584A1 |

| Счетчик импульсов | 1985 |

|

SU1261112A1 |

| Счетчик импульсов | 1984 |

|

SU1205302A2 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах управления вычислительных систем. Целью изобретения является повышение функциональной надежности. Поставленная цель достигается тем, что в распределитель, содержащий в каждом канале первый и второй триггеры, 1.1 ...1 .П...3.1 ...З.п первый элемент И 2.1 ...2,п элемент И-НЕ 6.1...6.П, установочный вход 12.1...12.П, введены второй и третий элементы И 8, 9, первый элемент НЕ 10, О-триггер 7, и в каждый канал, начиная со второго, - элемент ИЛИ 4.1..,4.п и второй элемент НЕ 5.1..,5.п. 2 ил.

Фиг. г

| Распределитель импульсов | 1979 |

|

SU879776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1992-02-23—Публикация

1989-10-05—Подача