Изобретение относится к вычислительной технике и предназначено для построения высоконадежных управляющих и вычислительных комплексов.

Известно устройство приоритета, со- держащее два канала и в каждом канале триггер захвата 1.

Недостатками этого устройства являются узкая область применения и низкая достоверность функционирования.

Известно также устройство приоритета, содержащее два канала, а в каждом канале триггер захвата, инверсный выход которого соединен с первым входом элемента И 2.

Недостатками этого устройства являют- ся узкая область применения и низкая достоверность функционирования.

Наиболее близким к заявляемому по технической сущности и достигаемому эффекту является устройство приоритетного доступа, содержащее два канала, а в каждом канале триггер запроса, триггер разрешения, триггер захвата, триггер прерывания, первый и второй элементы И, первый и второй элементы ИЛИ, первый и второй буферные элементы, причем в каждом канале единичный выход триггера запроса соединен с входом синхронизации триггера прерывания и информационным входом первого буферного элемента друго- го канала, нулевой выход триггера запроса каждого канала соединен с первым входом первого элемента ИЛИ канала, выход которого соединен с нулевым входом триггера захвата, нулевой выход триггера разреше- ния соединен с информационным входом второго буферного элемента другого кана- . ла, выход которого является первым информационным выходом одноименного канала, единичный выход триггера захвата второго канала является выходом коммутации второго канала и соединен с вторым входом первого элемента ИЛИ первого канала, выход второго элемента ИЛИ каждого канала соединен с единичным входом триггера прерывания, единичный выход которого является выходом прерывания одноименного канала, J-вход триггера прерывания каждого канала соединен с шиной единичного потенциала устройства, а вход сброса - с входом подтверждения одноименного канала, выход первого элемента И каждого канала соединен с первым входом второго элемента ИЛИ другого канала, выход второго элемента И первого канала соединен с вторым входом первого элемента ИЛИ второго канала, выход второго буферного элемента каждого канала является вторым информационным выходом канала, а вход синхронизации выхода какала соединен с

управляющими входами первого и второго буферных элементов одноименного канала, вход запроса каждого канала соединен с информационным входом триггера запроса канала, вход разрешения канала соединен с информационным входом триггера разрешения и с первым входом первого элемента И канала, вход сброса канала соединен с первым входом второго элемента И того же канала, вход синхронизации вывода канала соединен с вторым входом первого элемента И, синхровходами триггеров разрешения и запроса, а также с вторым входом второго элемента И того же канала, выход прерывания первого и второго каналов образуют первый и второй выходы прерывания устройства, первый и второй информационные выходы первого канала и первый и второй информационные выходы второго канала образуют соответственно первый, второй, третий и четвертый информационные выходы устройства, выход коммутации второго канала является первым выходом коммутации устройства, выходы подтверждения первого и второго каналов образуют первый и второй входы подтверждения устройства, входы синхронизации ввода первого и второго каналов являются первым и вторым входами синхронизации ввода устройства, входы запросов первого и второго каналов являются входами разрешения устройства, входы сброса первого и второго каналов являются первым и вторым входами сброса устройства, входы синхронизации вывода первого и второго каналов являются первым и вторым входами синхронизации устройства соответственно 3.

Недостатками этого устройства являются низкая достоверность функционирования и узкая область применения.

Устройство-прототип содержит технические средства, которые позволяют каждой ЭВМ принимать на себя управление магистралью, а также запрещать или разрешать захват магистрали другой ЭВМ программным путем. При этом не реализуется режим перехвата магистрали в случае наличия ограничений на время занятия магистрали одной ЭВМ. Этим ограничивается область применения прототипа. Низкая достоверность функционирования прототипа обусловлена отсутствием технических средств, позволяющих организовать работу устройства в условиях отказа одной из ЭВМ от принудительного захвата магистрали исправной ЭВМ.

Целью изобретения является расширение области применения устройства и повышение достоверности функционирования.

Цель достигается тем, что в устройство приоритетного доступа, содержащее два канала, а в каждом канале триггер запроса, триггер разрешения, триггер захвата, триггер прерывания, первый и второй элементы И, первый и второй элементы ИЛИ, первый и второй буферные элементы, причем в каждом канале единичный выход триггера запроса соединен с входом синхронизации триггера прерывания и информационным входом первого буферного элемента другого канала, нулевой выход триггера запроса каждого канала соединен с первым входом первого элемента ИЛИ канала, выход которого соединен с нулевым входом триггера захвата, нулевой выход триггера разрешения соединён с информационным входом второго буферного элемента другого канала, вход которого является первым информационным выходом одноименного канала, единичный выход триггера захвата второго канала является выходом коммутации второго канала и соединен с вторым входом первого элемента ИЛИ первого канала, выход второго элемента ИЛИ каждого канала соединен с единичным входом триггера прерывания, единичный выход которого является выходом прерывания одноименного канала, J-вход триггера прерывания каждого канала соединен с шиной единичного потенциала устройства, а вход сброса - с входом подтверждения одноименного канала, выход первого элемента И каждого канала соединен с первым входом второго элемента ИЛИ другого канала, выход второго элемента И первого канала соединен с вторым входом первого элемента ИЛИ второго канала, выход второго буферного элемента каждого канала является вторым информационным выходом канала, а вход синхронизации вывода канала соединен с управляющими входами первого и второго буферных элементов одноименного канала, вход запроса каждого канала соединен с информационным входом триггера запроса канала, вход разрешения канала соединен с информационным входом триггера разрешения и с первым входом первого элемента И канала, вход сброса канала соединен с первым входом второго элемента И того же канала, вход синхронизации вывода канала соединен с вторым входом первого элемента И, с входом синхронизации триггера разрешения и запроса, а также с вторым входом второго элемента И того же канала, выходы прерывания первого и второго каналов образуют первый и второй выходы прерывания устройства, первый и второй информационные выходы первого канала и первый и второй информационные выходы

второго канала образуют соответственно первый, второй, третий и четвертый информационные выходы устройства, выход коммутации второго канала является первым

выходом коммутации устройства, иходы подтверждения первого и второго каналов образуют первый и второй входы подтверждения устройства, входы синхронизации ввода первого и второго каналов являются

0 первым и вторым входами синхронизации ввода устройства, входы запроса первого и второго каналов являются первым и вторым входами разрешения устройства, входы сброса первого и второго каналов являются

5 первым и вторым входами сброса устройства, входы синхронизации выхода первого и второго каналов являются первым и вторым входами синхронизации устройства соответственно, введены счетчик, блок памяти,

0 блок сравнения, генератор импульсов, первый и второй элементы И и одновибратор, а в каждый канал - регистр кода интервала, третий элемент И и одновибратор, кроме того, в первый канал введены четвертый

5 элемент И и элемент задержки, при этом в каждом канале группы выходов регистра кода интервала через информационную шину соединены с группой входов блока памяти, группа выходов которого соединена с пер0 вой группой входов блока сравнения, входы третьего элемента И канала через одновибратор соединен с вторым входом второго элемента ИЛИ, единичным входом триггера разрешения, нулевым входом триггера за5 проса того же канала и третьим входом второго элемента ИЛИ другого канала, нулевой выход триггера запроса первого канала соединен с первыми инверсными входами третьих элементов И первого и второго ка0 налов, единичный выход триггера захвата канала соединен с первым прямым входом третьего элемента И и управляющим входом регистра кода интервала, кроме того, единичный выход триггера захвата первого ка5 нала соединен с первым входом, а через элемент задержки с вторым входом четвертого элемента И первого канала, выход которого является выходом коммутации первого канала и вторым выходом коммута0 ции устройства, нулевой выход триггера запроса второго канала соединен с вторыми инверсными входами третьих элементов И каналов, первый и второй входы кода интервала устройства, являются соответственно

5 входами кода интервала первого и второго каналов, соединены с группами информационных входов регистров кода интервала первого и второго каналов соответственно, вход синхронизации вывода каждого канала соединен с синхровходом регистра кода интервала канала, вход разрешения канала соединен с вторым управляющим входом регистра кода интервала того же канала, первый и второй входы неисправности устройства, являющиеся соответственно одноименными входами неисправности первого и второго каналов,соединены с четвертыми входами вторых элементов И одноименных каналов, нулевой выходтриггера захвата канала соединен с единичным входом триггера захвата другого канала и одним из двух входов первого элемента И устройства, выход которого соединен с первым инверсным входом второго элемента И устройства, а через одновибратор с входом сброса счетчика, группа входов счетчика соединена с второй группой входов блока сравнения, выход которого соединен с вторыми прямыми входами третьих элементов И обоих каналов и вторым инверсным входом второго элемента И устройства, выход генератора импульсов соединен с первым входом второго элемента И устройства, выход которого подключен к счетному входу счетчика.

Сущность изобретения состоит в расширении области применения устройства за счет введения конструктивных признаков, позволяющих реализовать перехват магистрали в случае наличия ограничений на время занятия магистрали одной ЭВМ, Это позволяет применять устройство в системах, работающих в условиях жестких временных ограничений, например в системах реального времени.

Достоверность функционирования устройства повышается благодаря введению элементов и связей, которые обеспечивают возможность предотвращения отказа устройства в условиях неисправности одной из ЭВМ путем принудительного захвата магистрали исправной ЭВМ.

Заявляемое устройство отвечает критерию новизна благодаря введению следующих новых элементов и связей.

Введение в каждый канал регистров кода интервала позволяет осуществлять прием, хранение и передачу кодов интервалов времени доступа к общей магистрали первой и второй ЭВМ, Введение в каналы третьих элементов И и одновибраторов позволяет формировать сигналы переключения триггеров разрешения и запроса, а также управлять триггерами прерывания при передаче управления между ЭВМ после истечения заданного времени доступа. Введение счетчика позволяет обеспечить отчет времени занятия общей магистрали первой или второй ЭВМ, Введение блока памяти позволяет хранить коды временных интервалов, соответствующих всем возможным интервалам времени занятия общей магистрали ЭВМ. Введение блока сравнения позволяет идентифицировать моменты

окончания интервала времени занятия магистрали. Введение генератора импульсов позволяет осуществлять измерение интервала времени занятия общей магистрали ЭВМ. Введение первого элемента И устрой0 ства позволяет формировать сигнал незанятости общей магистрали. Введение второго элемента И устройства позволяет управлять подачей счетных импульсов на вход счетчика. Введение четвертого элемента И и эле5 мента задержки в первый канал позволяет фильтровать ложные импульсы, которые могут возникать на втором выходе коммутации устройства. Соединение входа неисправности канала с четвертым входом второго эле0 мента ИЛИ канала позволяет осуществлять перехват магистрали в случае отказа одной из ЭВМ.

Предлагаемое устройство соответствует критерию существенное отличие, по5 скольку не известно применение указанной- совокупности признаков в прототипе и аналогах, которое бы приводило к положительному эффекту, состоящему в расширении области применения и повышении досто0 верности функционирования устройства.

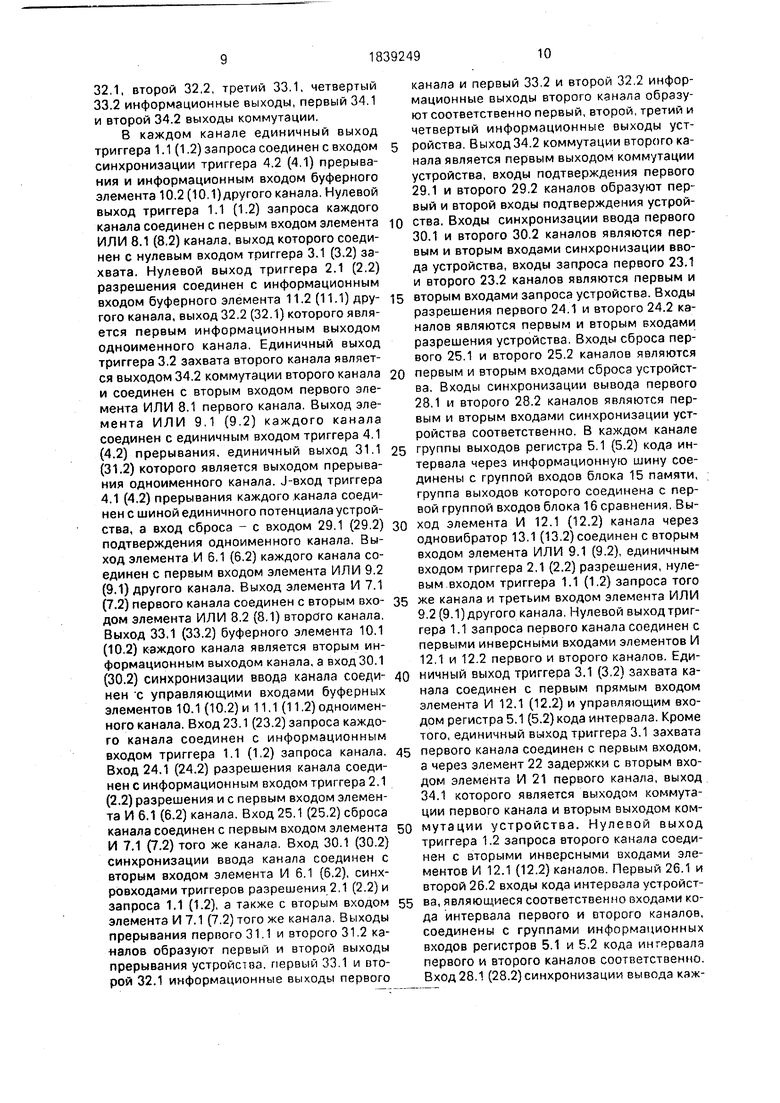

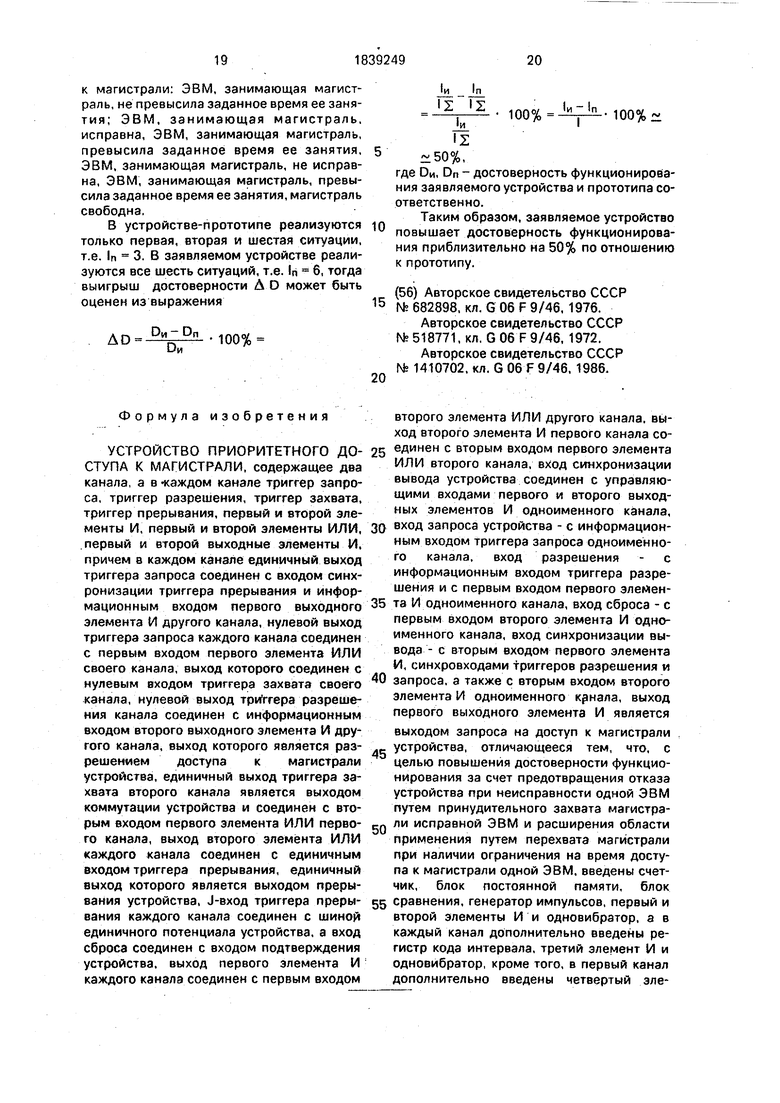

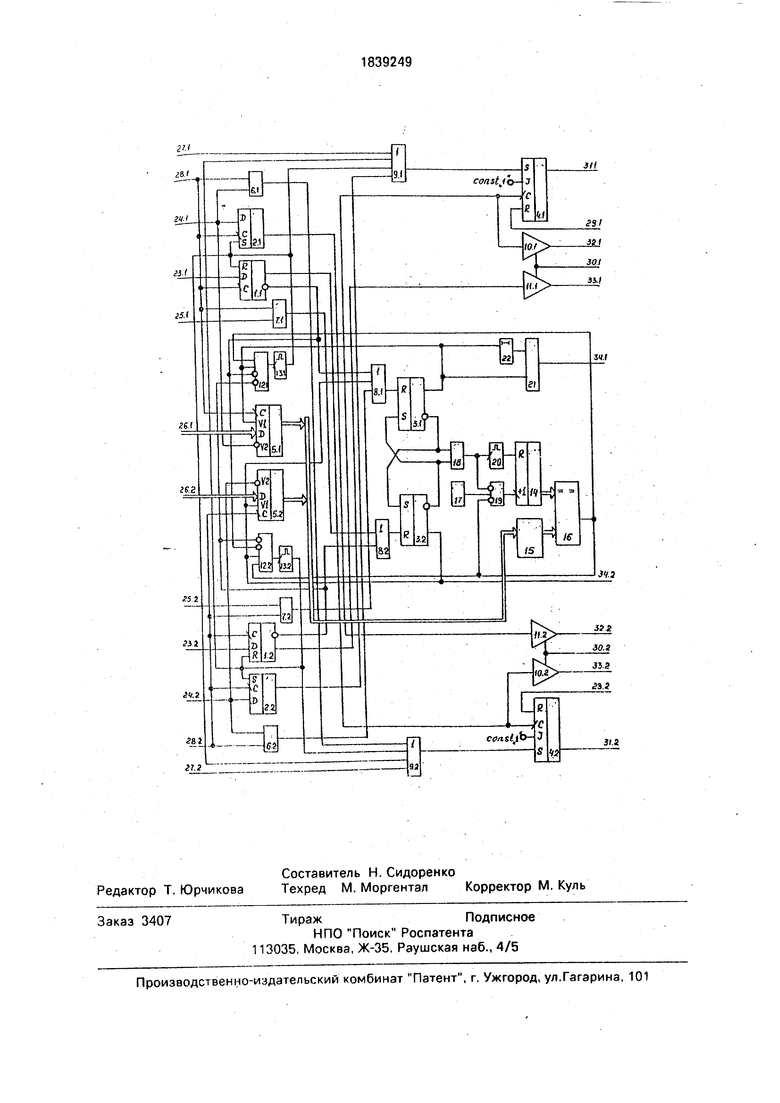

На чертеже представлена функциональная схема устройства приоритетного доступа к магистрали.

Устройство содержит первый 1.1 и вто5 рой 1.2 триггеры запроса, первый 2.1 и второй 2.2 триггеры разрешения первый 3.1 и второй 3.2 триггеры захвата, первый 4.1 и второй 4.2 триггеры прерывания, первый 5.1 и второй 5.2 регистры кода интервала, пер0 вый 6.1, второй 6.2, третий 7.1, четвертый 7.2 элементы И, первый 8.1, второй 8.2, третий 9.1, четвертый 9.2 элементы ИЛИ, первый 10.1, второй 10.2, третий 11.1, четвертый 11.2 буферные элементы, пятый 12.1 и шес5 той 12.2 элементы И, первый 13.1 и второй 13.2 одновибраторы, счетчик 14, ПЗУ 15, схему 16 сравнения, генератор 17 импуль- .сов, седьмой 18 и восьмой 19 элементы И, третий одновибратор 20, девятый элемент И

0 21, элемент 22 задержки, первый 23.1 и второй 23.2 входы запроса, первый 24.1 и второй 24.2 входы разрешения, первый 25.1 и второй 25.2 входы сброса, первый 26.1 и второй 26.2 входы кода интервала, первый

5 27.1 и второй 27.2 входы неисправности, первый 28.1 и второй 28.2 входы синхронизации, первый 29.1 и второй 29.2 входы подтверждения, первый 30.1 и второй 30.2 входы синхронизации ввода, первый 31.1 и второй 31.2 выходы прерывания, первый

32,1, второй 32,2, третий 33.1, четвертый 33.2 информационные выходы, первый 34.1 и второй 34.2 выходы коммутации.

В каждом канале единичный выход триггера 1.1 (1.2) запроса соединен с входом синхронизации триггера 4.2 (4.1) прерывания и информационным входом буферного элемента 10.2 (10.1)другого канала. Нулевой выход триггера 1.1 (1.2) запроса каждого канала соединен с первым входом элемента ИЛИ 8.1 (8.2) канала, выход которого соединен с нулевым входом триггера 3.1 (3.2) захвата. Нулевой выход триггера 2.1 (2.2) разрешения соединен с информационным входом буферного элемента 11.2 (11.1) дру- того канала, выход 32.2 (32.1) которого является первым информационным выходом одноименного канала. Единичный выход триггера 3.2 захвата второго канала является выходом 34.2 коммутации второго канала и соединен с вторым входом первого элемента ИЛИ 8.1 первого канала. Выход элемента ИЛИ 9.1 (9.2) каждого канала соединен с единичным входом триггера 4,1 (4.2) прерывания, единичный выход 31.1 (31.2) которого является выходом прерывания одноименного канала. J-вход триггера 4.1 (4,2) прерывания каждого .канала соединен с шиной единичного потенциала устройства, а вход сброса - с входом 29.1 (29.2) подтверждения одноименного канала. Выход элемента И 6.1 (6.2) каждого канала соединен с первым входом элемента ИЛИ 9.2 (9.1) другого канала. Выход элемента И 7.1 (7.2) первого канала соединен с вторым вхо- дом элемента ИЛИ 8.2 (8.1) второго канала. Выход 33.1 (33.2) буферного элемента 10.1 (10.2) каждого канала является вторым информационным выходом канала, а вход 30.1 (30.2) синхронизации ввода канала соеди- нен с управляющими входами буферных элементов 10.1 (10.2) и 11.1 (11.2) одноименного канала. Вход 23.1 (23.2) запроса каждого канала соединен с информационным входом триггера 1.1 (1,2) запроса канала. Вход 24.1 (24.2) разрешения канала соединен с информационным входом триггера 2,1 (2.2) разрешения и с первым входом элемента И 6.1 (6.2) канала. Вход 25.1 (25.2) сброса канала соединен с первым входом элемента И 7.1 (7.2) того же канала. Вход 30.1 (30.2) синхронизации ввода канала соединен с вторым входом элемента И 6.1 (6.2), синх- ровходами триггеров разрешения 2,1 (2.2) и запроса 1.1 (1.2), а также с вторым входом элемента И 7.1 (7.2) того же канала. Выходы прерывания первого 31.1 и второго 31.2 каналов образуют первый и второй выходы прерывания устройства, первый 33.1 и второй 32.1 информационные выходы первого

канала и первый 33.2 и второй 32.2 информационные выходы второго канала образуют соответственно первый, второй, третий и четвертый информационные выходы устройства. Выход 34.2 коммутации второго канала является первым выходом коммутации устройства, входы подтверждения первого 29.1 и второго 29.2 каналов образуют первый и второй входы подтверждения устройства. Входы синхронизации ввода первого 30.1 и второго 30,2 каналов являются первым и вторым входами синхронизации ввода устройства, входы запроса первого 23.1 и второго 23.2 каналов являются первым и вторым входами запроса устройства. Входы разрешения первого 24.1 и второго 24.2 каналов являются первым и вторым входами разрешения устройства. Входы сброса первого 25.1 и второго 25.2 каналов являются первым и вторым входами сброса устройства. Входы синхронизации вывода первого 28.1 и второго 28.2 каналов являются первым и вторым входами синхронизации устройства соответственно. В каждом канале группы выходов регистра 5.1 (5.2) кода интервала через информационную шину соединены с группой входов блока 15 памяти, группа выходов которого соединена с первой группой входов блока 16 сравнения, Выход элемента И 12.1 (12.2) канала через одновибратор 13.1 (13.2) соединен с вторым входом элемента ИЛИ 9.1 (9.2), единичным входом триггера 2.1 (2.2) разрешения, нулевым входом триггера 1.1 (1.2) запроса того же канала и третьим входом элемента ИЛИ 9.2 (9.1) другого канала. Нулевой выход триггера 1.1 запроса первого канала соединен с первыми инверсными входами элементов И 12.1 и 12.2 первого и второго каналов. Единичный выход триггера 3.1 (3,2) захвата канала соединен с первым прямым входом элемента И 12.1 (12.2) и управляющим входом регистра 5.1 (5.2) кода интервала. Кроме того, единичный выход триггера 3.1 захвата первого канала соединен с первым входом, а через элемент 22 задержки с вторым входом элемента И 21 первого канала, выход 34.1 которого является выходом коммутации первого канала и вторым выходом ком- мутации устройства. Нулевой выход триггера 1.2 запроса второго канала соединен с вторыми инверсными входами элементов И 12.1 (12.2) каналов. Первый 26.1 и второй 26.2 входы кода интервала устройства, являющиеся соответственно входами кода интервала первого и второго каналов, соединены с группами информационных входов регистров 5.1 и 5.2 кода интервала первого и второго каналов соответственно. Вход 28.1 (28.2)синхронизации вывода кэждого канала соединен с синхровходом регистра 5,1 (5.2) кода интервала канала. Вход 24.1 (24.2) разрешения канала соединен с вторым управляющим входом регистра 5.1 (5.2) кода интервала того же канала. Первый 27.1 и второй 27.2 входы неисправности устройства, являющиеся соответственно одноименными входами неисправности первого и второго каналов, соединены с четвертыми входами элементов И 9.1 и 9.2 од- поименных каналов. Нулевой выход триггера 3,1 (3.2) захвата канала соединен с единичным входом триггера 3.2 (3.1) захвата другого канала и одним из двух входов элемента И 18 устройства, выход которого сое- динен с первым инверсным входом элемента И 19 устройства, а через одновиб- ратор 20 с входом сброса счетчика 14. Группа выходов счетчика 14 соединена с второй группой входов блока 16 сравнения, выход которого соединен с вторыми прямыми входами элементов И 12.1 (12.2) обоих каналов и вторым инверсным входом элемента И 19 устройства. Выход генератора 17 импульсов соединен с первым входом элемента И 19, выход которого подключен к счетному входу счетчика 14.

Триггеры 1.1 и 1.2 запроса предназначены для приема, хранения и выдачи сигналов запроса на доступ к общей магистрали от ЭВМ (на чертеже не показаны). Запись сигналов запроса осуществляется по синхроимпульсу, поступающему на С-вход. Установка в ноль асинхронная.

Триггеры 2.12 и 2.2 разрешения пред- назначены для приема, хранения и выдачи сигнала разрешения доступа к магистрали, формируемого ЭВМ, Запись сигнала разрешения синхронная, установка в единицу по S-входу асинхронная.

Триггеры 3.1 и 3.2 захвата предназначены для формирования сигнала захвата общей магистрали ЭВМ и выдачи его на выходы 34.1 и 34.2 коммутации. Они являются асинхронными R-триггерами, у которых комбинация входных сигналов RS-11 не является запрещенной, и при поступлении ее на входы триггера он устанавливается в нулевое состояние,

Триггеры 4.1 и 4.2 прерывания предназначены для приема, хранения и выдачи на выходы 31.1 и 31.2 сигналов прерывания ЭВМ. Они реализованы на синхронных IK- триггерах. имеющих асинхронные R- и S- входы. Синхронная установка в единицу осуществляется по переднему фронту импульса на входе С. На l-вход постоянно подается единичный сигнал, а на вход К - нулевой.

Регистры 5.1 и 5.2 предназначены для приема, хранения и выдачи кодов интервала, определяющих заданное время доступа ЭВМ к общей магистрали. Прием кода по D-входу осуществляется по заданному фронту импульса, поступающего на С-вход, если имеется нулевой сигнал на входе V2 разрешения записи. Выдача записанного в регистры 5.1 и 5,2 кода на выход осуществляется только при наличии единичного сигнала на управляющем входе V1.

Элементы И 6.1, 6.2 предназначены для формирования сигналов установки в единицу триггеров 4.2, 4.1 прерывания, если от ЭВМ поступил сигнал на вход 24,1 (24,2) разрешения. Элементы И 7.1, 7.2 формиру- ,ют сигналы сброса триггеров 3.2, 3.1, при перехвате общей магистрали, если ЭВМ неисправна.

Элементы ИЛИ 8.1, 8.2 формируют сигналы установки в ноль триггеров 3.1, 3.2 запроса. Элементы ИЛИ 9.1, 9.2 формируют сигналы установки в единицу триггеров 4.1, 4.2 прерывания.

Буферные элементы 10.1 (10.2) и 11.1 (11.2) предназначены для передачи на информационные выходы 32,1 (32.2) и 33.1 (33.2) устройства сигналов состояния триггеров 1.2 (1.1) и 2.2 (2,1) при поступлении сигналов синхронизации ввода от ЭВМ,

Элементы И 12.1, 12.2 и одновибраторы 13.1, 13,2 предназначены для формирования сигналов переключения триггеров 1.1 (1.2) и 2.1 (2,2), а также установки в единицу триггеров 4.1 и 4.2 прерывания при передаче управления общей магистралью от первой ЭВМ к второй после истечения заданного времени доступа.

Счетчик 14 предназначен для подсчета числа импульсов, соответствующих времени занятия общей магистрали ЭВМ. ПЗУ 15 содержит коды временных интервалов (число импульсов), соответствующих всем возможным интервалам времени доступа к общей магистрали ЭВМ, Оно представляет собой статическое ЗУ, информация на входе которого присутствует в течение всего интервала времени наличия кода адреса на входе. Схема 16 сравнения формирует единичный сигнал при совпадении кодов, поступающих на его входы. Генератор 17 формирует последовательность импульсов, используемых для измерения интервала времени занятия общей магистрали ЭВМ.

Элемент И 18 формирует единичный сигнал, если общая магистраль свободна (триггеры 3.1,3.2 находятся в нуле). Элемент И 19 разрешает поступление импульсов на счетный вход счетчика 14 при измерении времени занятия общей магистрали. Одновибратор 20 формирует сигнал сброса счетчика 14 при освобождении общей магистрали, Элементы И 21 и задержки 22 образуют триггер, не пропускающий на выход 34.1 ложные импульсы, формируемые при одновременном включении триггеров 3.1 и 3.2. Время задержки Г22 элемента 22 выбирается из условия Г22 тв.1 + гз 1, где гз.1 и тз.1 - максимальные времена задержки сигналов на элементе ИЛИ 8.1 и триггере 3.1.

Рассмотрим работу предлагаемого устройства приоритетного доступа.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в исходное состояние не показаны). Входы и выходы устройства подключены соответственно к выходам и входам первой и второй ЭВМ, которые образуют дуплексную систему. Каждая ЭВМ может выдать информацию на общую магистраль, к которой подключены внешние устройства. Одна ЭВМ захватывает магистраль по своему запросу и работает с ней до тех пор, пока в этом есть необходимость либо пока магистраль не потребует другая ЭВМ, выставив запрос на доступ к общей магистрали. Вопрос о передаче доступа к общей магистрали при наличии запросов от двух.ЭВМ решается в зависимости от следующих обстоятельств: ЭВМ, занимающая магистраль, не превысила (превысила) заданное время ее занятия, ЭВМ, занимающая магистраль, исправна (не исправна), ЭВМ, занимающая магистраль, отклонила (не отклонила) требования к передаче магистрали, ЭВМ, занимающая магистраль, не отреагировала (отреагировала) на требование о передаче магистрали.

Сигнал о подключении ЭВМ к общей магистрали действует на выходе 34.1 (34.2). Когда триггеры 3.1 и 3.2 находятся в исходном состоянии на выходах 34.1 и 34.2 действуют нулевые сигналы и ни одна из ЭВМ не подключена к общей магистрали.

Для организации доступа к общей магистрали от ЭВМ на вход 23.1 (23.2) поступает сигнал запроса, сопровождаемый синхронизирующим импульсом по входу 28.1 (28,2) синхронизации вывода, который устанавливает триггер 1.1 (1.2) запроса в единичное состояние. Одновременно ЭВМ выставляет код интервала времени доступа к общей магистрали на вход 2 6.1 (26.2), который по тому же синхроимпульсу записывается в регистр 5.1 (5.2). Входы 23.1-26.1 (23.2-26.2) устройства соединены с выходами разрядов информационного слова ЭВМ и управляются программно.

Если, например, сигнал запроса доступа к общей магистрали поступает от первой ЭВМ, а вторая ЭВМ не подключена к общей магистрали, то триггер 1.1 переключается в единичное состояние и с его инверсного выхода снимается единичный сигнал, который через второй элемент ИЛ И 8.1 принудительно удерживал триггер 3.1 в нулевом состоянии. Так как триггер 3.2 находится в 0 исходном состоянии, то единичный сигнал с его инверсного выхода, поступающий на S- вход триггера 3.1, переключает его в единичное состояние.

Единичный сигнал с прямого выхода 5 триггера 3.1 проходит через элементы задержки 22 и И 21 на выход 34.1 и разрешает подключение первой ЭВМ к общей магистрали. Одновременно этот сигнал поступает на вход чтения регистра 5.1 и записанный в 0 нем код поступает на адресный вход ПЗУ 15. В результате из адресной ячейки памяти ПЗУ 15 считывается код, который поступает на вход схемы 16 сравнения.

После переключения триггера 3.1 в еди-. 5 ничное состояние нулевой сигнал с его инверсного выхода исключает возможность включения триггера 3.2 (подключения второй ЭВМ к общей магистрали) и закрывает элемент И 18. Нулевой сигнал с выхода эле- 0 мента И 18 открывает элемент И 19 и на его выход начинают поступать импульсы с выхода генератора 17 импульсов. В результате счетчик 14 начинает отсчет времени занятия первой ЭВМ общей магистрали. 5 В дальнейшем в работе устройства возможны следующие ситуации.

Первая ЭВМ освободила магистраль до истечения времени ее занятия, считанного из ПЗУ 15, при этом требование на доступ к 0 общей магистрали от второй ЭВМ не поступило.

Интервал времени, считанный из ПЗУ 15, истек, однако первая ЭВМ продолжает занимать магистраль. Запроса на доступ к 5 общей магистрали от второй ЭВМ нет.

Запрос на доступ к общей магистрали от второй ЭВМ поступил до истечения времени занятия магистрали первой ЭВМ.

Запрос на доступ к общей магистрали от 0 второй ЭВМ поступил после истечения времени занятия магистрали первой ЭВМ.

Рассмотрим последовательно перечисленные ситуации.

Если первая ЭВМ закончила работу с 5 общей магистралью, то она выставляет нулевой сигнал на вход 23.1 запроса и подает сигнал синхронизации на вход 28.1 синхронизации вывода. По этому сигналу триггер 1.1 устанавливается в ноль. Единичный сигнал с его инверсного выхода поступает на

R-вход триггера 3.1 и сбрасывает его в ноль. В результате этого с выхода 34.1 коммутации снимается единичный сигнал и первая ЭВМ отключается от общей магистрали. Одновременно единичный сигнал с инверсного выхода триггера 3.1 поступает на вход элемента И 18, единичный сигнал с его выхода закрывает элемент И 19 и запускает одновибратор 20, который устанавливает в ноль счетчик 14.

Если интервал времени занятия общей магистрали первой ЭВМ достигает заданного ( считанного из ПЗУ 15), то на выходе схемы 16 сравнения появляется единичный сигнал, который поступает на элементы И 12.1 и 12.2 и закрывает элемент И 19, прекратив тем самым поступление импульсов на счетный вход счетчика 14. Отсчет интервала времени занятия общей магистрали прекращается, но первая ЭВМ по-прежнему занимает магистраль, так как запроса от второй ЭВМ нет.

Если запрос на доступ к общей магистрали от второй ЭВМ поступил до истечения времени занятия магистрали первой ЭВМ, то по синхросигналу на входе 28.2 триггер 1.2 устанавливается в единичное состояние, а в регистр 5.2 записывается код интервала времени доступа к общей магистрали, запрашиваемый для второй ЭВМ, Триггер 1,2 снимает сигнал сброса с R-входа триггера 3.2, однако последний не переключается в единицу, так как на его S-входе присутствует нулевой сигнал (триггер 3.1 находится в единице). Одновременно единичный сигнал с прямого выхода триггера 1.2 поступает на С-вход триггера 4.1 и переключает его в единицу. В результате этого триггер 4.1 формирует сигнал прерывания на выходе 31.1 для первой ЭВМ. После того, как первая ЭВМ воспримет сигнал прерывания, она формирует сигнал подтверждения на вход 29.1 подтверждения устройства, который возвращает триггер 4.1 в исходное состояние.

Получив сигнал прерывания, первая ЭВМ с выходов 32.1,33.1 производит считывание состояний триггеров 1.2 и 2.2, подав на вход 30.1 сигнал синхронизации ввода. Таким образом, первая ЭВМ получает запрос от второй ЭВМ на доступ к магистрали (состояние триггеров 1.2, 2.2 представляется для первой ЭВМ разрядами регистра состояния) и должна принять решение, сможет ли она в данный момент отдать магистраль. Если первая ЭВМ приняла решение отдать управление магистралью второй ЭВМ, то она подает на вход 23.1 запроса нулевой сигнал, на вход 24.1 разрешения единичный сигнал и на вход 28.1 - сигнал синхронизации ввода. В результате этого

триггер 1.1 устанавливается в ноль, триггер 2.1 - в единицу, а регистр 5.1 не изменяет своего состояния. Единичный сигнал с инверсного выхода триггера 1.1 проходит на

R-вход триггера 3.1 и устанавливает его в ноль. Единичный сигнал с его инверсного выхода устанавливает в единицу триггер 3.2 и на выходы 34.2 коммутации поступает единичный сигнал. Одновременно сигнал раз0 решения проходит через элементы И 6.1, ИЛИ 9.2 на S-вход триггера 4.2 и устанавливает его в единицу, формируя тем самым сигнал прерывания второй ЭВМ на выходы 31.2. После отработки этого прерывания

5 вторая ЭВМ читает состояние триггеров 1,1 и 2.1, подавая импульсный сигнал синхронизации ввода на вход 30.2 устройства. Состояние, когда триггер 1.1 находится в О, а триггер 2.1 - в 1, означает, что первая

0 ЭВМ предоставила второй ЭВМ доступ к общей магистрали.

Если первая ЭВМ при возникновении требования второй ЭВМ отдать магистраль не может, то она должна выставить на входы

5 23.1, 24.1 единичные сигналы и подать сигнал синхронизации на вход 28.1. В этом случае триггер 2.1 устанавливается в единицу, а триггеры 1.1, 3.1 и регистр 5.1 сохраняют свои состояния. Одновременно, как и в

0 предыдущем случае, устанавливается в единицу триггер 4.2 и выдаст единичный сигнал на выход 31.2 прерывания. После отработки прерывания и чтения регистра состояния (выходы 32.2,33.2) вторая ЭВМ обнаружива5 ет, что триггеры 1.1 и 2.1 находятся в единице. Это означает, что требование доступа к общей магистрали, выбранное второй ЭВМ, передано первой ЭВМ, но было отклонено. В этом случае управление магистралью ос0 тается за первой ЭВМ вплоть до истечения заданного интервала времени.

После истечения заданного интервала времени число, записанное в счетчике 14, становится равным числу, считываемому из

5 ПЗУ 15, и на выходе схемы 16 сравнения появляется единичный сигнал, который поступает на входы элементов И 12.1,12,2, 19. В результате этого на выходе элемента И 12.1 появляется единичный сигнал. Он запу0 екает одновибратор 13.1, который формирует импульс, устанавливающий триггер 1.1 в ноль, а триггеры 2.1, 4.1 и 4.2 в единицу. Вследствие этого единичный сигнал с инверсного выхода триггера 1.1 сбрасывает в

5 ноль триггер 3.1, который единичным сигналом с инверсного выхода устанавливает в единицу триггер 3.2 и сбрасывает в ноль счетчик 14. Триггер 3.2, переключившись в единицу, формирует единичный сигнал на выходе 34.2 коммутации и открывает элемент И 19, в результате чего счетчик 14 начинает отсчет времени занятия второй ЭВМ общей магистрали. Одновременно триггеры 4,1 и 4.2, установившись в единицу, формируют сигналы прерывания первой и второй ЭВМ на выходах 31.1 и 31.2 соответственно, После отработки этих прерываний ЭВМ сбрасывают триггеры 4.1 и 4.2 и по выходам 32.1,33.1 и 32.2, 33.2 читают состояния триггеров 1.2, 2.2 и 1.1, 2.1. В результате этого вторая ЭВМ обнаруживает, что триггер 1.1 .находится в нуле, триггер 2.1 - в единице, а первая ЭВМ обнаруживает, что триггер 2.1 находится в единице, триггер 2,2 - в нуле. Это означает, что управление магистралью передано от первой ЭВМ к второй по истечении максимального времени занятия магистрали первой ЭВМ.

Если запрос на доступ к общей магистрали от второй ЭВМ поступил после того, как закончилось заданное время занятия магистрали первой ЭВМ, но последняя магистраль не освободила, то после включения триггера 1.2 срабатывает одновибратор 13.1 исправление магистралью передается второй ЭВМ так. как это описано выше.

Кроме рассмотренных выше ситуаций, в работе устройства возможны, режимы, связанные с неисправностью одной из ЭВМ либо с одновременным обращением ЭВМ для доступа к магистрали. Рассмотрим эти режимы.

Если магистраль занята, например, первой ЭВМ, а вторая ЭВМ сформировала сигнал запроса на доступ к магистрали, но по истечении заданного времени не получила сигнала прерывания либо, получив сигнал прерывания, обнаружила, что триггер 2.1 находится в нуле, то она делает вывод о неисправности первой ЭВМ либо связанного с ней канала управления (прерывание в данном случае может быть вызвано аппаратным сигналом неисправности, поступившим по входу 27).

В данной ситуации вторая ЭВМ производит принудительный перехват магистрали независимо от времени занятия магистрали первой ЭВМ. Для этого на входы 24.2 и 25.2 вторая ЭВМ выставляет единичные сигналы и подает синхросигнал на вход 28.2, который проходит через элемент И 7.2 и сбрасывает ноль триггер 3.1. В результате этого устанавливается единицу триггер 3.2 и подает единичный сигнал на выход 34.2 коммутации для подключения второй ЭВМ к общей магистрали.

В этом случае, если с запросами на доступ магистрали обе ЭВМ обращаются одновременно, то этот конфликт разрешается следующим образом. По синхросигналам.

поступающим на входы 28.1. 28.2, триггеры 1.1 и 1.2 устанавливаются в единицу, а в регистры 5.1. 5.2 записываются коды интервалов. Так как сигналы с R-входов триггеров

5 3.1, 3.2 сняты одновременно, то оба триггера 3.1 и 3.2 начинают переключаться в единицу. Если оба триггера 3.1 и 3.2 устанавливаются в единицу (что маловероятно), то единичный сигнал с прямого выхо0 да триггера 3.2 через элемент ИЛИ 8.1 проходит на вход триггера 3.1 и сбрасывает его в ноль, триггер 3.2 остается в единице. Его выходной сигнал одновременно проходит на выход 34.2 коммутации для подклю5 чения второй ЭВМ к общей магистрали, а счетчик 14 начинает отсчет времени занятия магистрали второй ЭВМ.

Короткий импульс, который в этом случае формируется на выходе триггера 3.1, на

0 выход 34.1 не проходит, так как его не пропускает фильтр, реализованный на элементах задержки 22 и И 21. Для этого время задержки сигнала на элементе 22 задержки выбирается из условия

5Г22 Тили + ГТр,

где Тили, TVp максимальное время переключения элементов ИЛИ 8.1 и триггера 3.1 соответственно.

По окончании интервала времени заня0 тия магистрали второй ЭВМ сбрасывается триггер 3.2, включается триггер 3.1 и управление магистралью передается первой ЭВМ. Детально этот процесс описан выше. Расширение области применения уст5 ройства по сравнению с прототипом состоит в том, что оно позволяет помимо реализации функций прототипа организовать перехват магистрали в случае наличия ограничений на время доступа к магистрали

0 для ЭВМ. Это позволяет использовать устройство в системах, работающих в условиях жестких временных ограничений, например в системах реального времени.

Достоверность функционирования уст5 ройства повышается за счет предотвращения отказа устройства условиях неисправности одной из ЭВМ путем принудительного захвата магистрали другой ЭВМ.

0 Достоверность функционирования D условно можно выразить через вероятность того, что устройство верно функционирует во всех возможных ситуациях I v, возникающих в процессе его работы:

5 о - -L 0 Г

где I - число учитываемых устройством ситуаций.

В устройстве возможны следующие си- --хуации при выставлении запросов на доступ

к магистрали: ЭВМ, занимающая магистраль, не превысила заданное время ее заня- тия; ЭВМ, занимающая магистраль, исправна, ЭВМ, занимающая магистраль, превысила заданное время ее занятия, ЭВМ, занимающая магистраль, не исправна, ЭВМ, занимающая магистраль, превысила заданное время ее занятия, магистраль свободна.

В устройстве-прототипе реализуются только первая, вторая и шестая ситуации, т.е. In 3. В заявляемом устройстве реализуются все шесть ситуаций, т.е. In б, тогда выигрыш достоверности ДО может быть оценен из выражения

ДО- -100%L/и

JiL-ilL

II II

100% 100%

и

Ч

50%,

где DM, Dn - достоверность функционирования заявляемого устройства и прототипа соответственно.

Таким образом, заявляемое устройство

повышает достоверность функционирования приблизительно на 50% по отношению к прототипу.

(56) Авторское свидетельство СССР № 682898, кл. G 06 F 9/46, 1976.

Авторское свидетельство СССР №518771, кл. G 06 F 9/46, 1972. Авторское свидетельство СССР

№ 1410702, кл. G 06 F 9/46, 1986.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство для обмена данными | 1984 |

|

SU1211742A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

Изобретение относится к вычислительной технике и предназначено для построения высоконадежных управляющих машин за счет перехвата магистрали в случае наличия ограничений на время доступа к магистрали одной ЭВМ и повышения достоверности функционирования за счет предотвращения отказа устройства при неисправности одной ЭВМ путем принудительного захвата магистрали исправной ЭВМ. Устройство содержит по два триггера запроса разрешения, захвата, прерывания два регистра кода интервала, девять элементов И, четыре элемента ИЛИ, четыре выходных элемента И, три одновибратора, счетчик, ПЗУ, схему сравнения, генератор импульсов, элемент задержки. 1 ид

Формула изобретения

УСТРОЙСТВО ПРИОРИТЕТНОГО ДОСТУПА К МАГИСТРАЛИ, содержащее два канала, а в -каждом канале триггер запроса, триггер разрешения, триггер захвата, триггер прерывания, первый и второй элементы И, первый и второй элементы ИЛИ, .первый и второй выходные элементы И, причем в каждом канале единичный выход триггера запроса соединен с входом синхронизации триггера прерывания и информационным входом первого выходного элемента И другого канала, нулевой выход триггера запроса каждого канала соединен с первым входом первого элемента ИЛИ своего канала, выход которого соединен с нулевым входом триггера захвата своего канала, нулевой выход триггера разрешения канала соединен с информационным входом второго выходного элемента И дру гого канала, выход которого является разрешением доступа к магистрали устройства, единичный выход триггера захвата второго канала является выходом коммутации устройства и соединен с вторым входом первого элемента ИЛИ первого канала, выход второго элемента ИЛИ каждого канала соединен с единичным входом триггера прерывания, единичный выход которого является выходом прерывания устройства, J-вход триггера прерывания каждого канала соединен с шиной единичного потенциала устройства, а вход сброса соединен с входом подтверждения устройства, выход первого элемента И каждого канала соединен с первым входом

второго элемента ИЛИ другого канала, выход второго элемента И первого канала соединен с вторым входом первого элемента ИЛИ второго канала, вход синхронизации вывода устройства соединен с управляющими входами первого и второго выходных элементов И одноименного канала,

ВХ°Д запроса устройства - с информационным входом триггера запроса одноименного канала, вход разрешения - с информационным входом триггера разрешения и с первым входом первого элемента И одноименного канала, вход сброса - с первым входом второго элемента И одноименного канала, вход синхронизации вывода - с вторым входом первого элемента И, синхровходами триггеров разрешения и

запроса, а также с вторым входом второго элемента И одноименного канала, выход первого выходного элемента И является

выходом запроса на доступ к магистрали устройства, отличающееся тем, что, с целью повышения достоверности функционирования за счет предотвращения отказа устройства при неисправности одной ЭВМ путем принудительного захвата магистрали исправной ЭВМ и расширения области применения путем перехвата магистрали при наличии ограничения на время доступа к магистрали одной ЭВМ. введены счетчик, блок постоянной памяти, блок

сравнения, генератор импульсов, первый и второй элементы И и одновибратор, а в каждый канал дополнительно введены регистр кода интервала, третий элемент И и одновибратор, кроме того, в первый канал дополнительно введены четвертый зле

мент И и элемент задержки, причем в каждом канале группы выходов регистра кода интервала через информационную шину устройства соединены с группой адресных входов блока постоянной памяти, группа выходов которого соединена с первой группой входов блока сравнения, выход третьего элемента И канала через одно- вибратор соединен с вторым входом второго элемента ИЛИ, единичным входом триггера разрешения, нулевым входом триггера запроса своего канала и третьим входом второго элемента ИЛИ другого канала, нулевой выход триггера запроса первого канала соединен с первыми инверсными входами третьих элементов И первого и второго каналов, единичный выход триггера захвата канала - с первым прямым входом третьего элемента И и управляющим входом регистра кода интервала своего канала, кроме того, единичный выход триггера захвата первого канала соединен с первым входом четвертого элемента И и через элемент задержки - с вторым входом четвертого элемента И первого канала, выход которого является выходом коммутации устройства, нулевой выход триггера запроса второго канала соединен с вторыми инверсными входами третьих элементов И канала, вход кода интервала устройства - с группой информационных входов регистра кода интервала

одноименного канала, вход синхронизации вывода устройства соединен с синхровхо- дом регистра кода интервала одноименного канала, вход разрешения устройства - с вторым управляющим входом регистра ко0 да интервала одноименного канала, вход неисправности устройства соединен с четвертым входом второго элемента И одноименного канала, нулевой выход триггера захвата канала - с единичным входом триг5 гера захвата другого канала и с соответствующим входом первого элемента И, выход которого соединен с первым инверсным входом второго элемента И и через одновибратор с входом сброса счетчика, группа выходов которого соединена с второй группой входов блока сравнения, выход которого соединен с вторыми прямыми входами третьих элементов И обоих кана- лов и вторым инверсным входом второго элемента И, выход генератора импульсов соединен с прямым входом второго элемента И, выход которого подключен к счетному входу счетчика.

0

Авторы

Даты

1993-12-30—Публикация

1990-10-22—Подача