ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполятор | 1987 |

|

SU1439620A1 |

| СТУПЕНЧАТО-ЛИНЕЙНЫЙ ЭКСТРАНОЛЯТОР | 1973 |

|

SU370611A1 |

| Линейный экстраполятор | 1981 |

|

SU1024943A1 |

| Цифровой экстраполятор | 1983 |

|

SU1126970A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1478978A1 |

| Ступенчато-линейный экстраполятор | 1976 |

|

SU591873A1 |

| Ступенчато-линейный экстраполятор | 1980 |

|

SU942059A1 |

| Цифро-аналоговый экстраполятор | 1978 |

|

SU752380A1 |

| Ступенчато-линейный экстраполятор второго порядка | 1977 |

|

SU705472A1 |

| Экстраполятор видеосигнала изображения | 1983 |

|

SU1091189A1 |

Изобретение относится к вычислительной технике и может быть использовано при предсказании случайных сигналов двумерных изображений, представляемых в виде растра, на фоне импульсных и флуктуацион- ных помех. Цель изобретения - повышение точности экстраполяции. При экстраполяции используют информацию о яркости точек, соответствующих наклонным границам изображаемого объекта. Логическая обработка значений яркости групп точек, расположенных по вертикали, двум диагоналям и горизонтали с экстраполируемой точкой, позволяет сделать вывод о наличии или отсутствии контрастного контура изображаемого объекта и устранить случайные флуктуации яркости. 6 ил.

Изобретение относится к технике обработки видеосигналов двумерного изображения и может быть использовано в любых отраслях науки и техники, где необходимы предсказание или экстраполяция случайных сигналов двумерных изображений на фоне импульсных и флуктуационных помех.

Известен экстраполятор видеосигнала изображения, содержащий ряд входных линий задержки, выходы которых соединены с соответствующими входами ряда блоков вычитания, выходы которых попарно подключены к информационным входам соответствующих переключателей, и с элементами сравнения, выходы которых через пороговые элементы соединены с уп- равляющими входами переключателей, вход экстраполятора и выходы переключателей соединены с входами сумматора.

Недостатком известного устройства

является низкая точность экстраполяции.

Наиболее близким к предлагаемому является экстраполятор видеосигнала изображения, содержащий пять линий задержки, входы которых соединены с входом экстраполятора, сумматор, два пороговых элемента, два блока вычитания, входы первого из которых соединены с выходами первой и второй линий задержки, а входы второго - с выходами третьей и четвертой линий задержки, и переключатель, два блока выделения модуля, элемент И, при этом выходы пятой линии задержки соединены с первым входом сумматора, выход второго элемента И соединен с управляющим входом переключателя, выход пятой линии задержки и выход сумматора соединены с информацией00

N5 О

ными входами переключателя, выход которого является выходом экстраполятора.

Недостатком известного экстраполятора является невысокая точность экстраполяции, так как для экстраполяции используются лишь те точки сигнала, которые расположены относительно экстраполируемой либо в одной строке, либо в одном столбце, а другие точки не используются, например точки, соответствующие наклонным границам объекта.

Целью изобретения является повышение точности экстраполяции.

Поставленная цель достигается тем, что в экстраполятор видеосигнала изображения, содержащий первый и второй блоки вычитания, первый и второй пороговые элементы, выходы которых соединены соответственно с первым и вторым входами элемента И, и сумматор, введены аналого- цифровой преобразователь, генератор тактовых импульсов, делитель частоты, два счетчика, дешифратор, пять блоков памяти, блок формирования адресов, алгебраический сумматор, регистр, цифроаналоговый преобразователь и элемент НЕ, при этом информационный вход аналого-цифрового преобразователя является входом экстраполятора, выход аналого-цифрового преобразователя соединен с информационными входами блоков памяти, адресные входы которых связаны с соответствующими выходами блока формирования адресов, выходы первого и второго блоков памяти соединены с соответствующими входами первого блока вычитания, выходы третьего и четвертого блоков памяти - с входами второго блока вычитания, кодовые выходы первого и второго блоков вычитания подключены к первым входам первого и второго пороговых элементов, вторые входы которых - к шине задания порогового уровня, кодовый и знаковый выходы второго блока вычитания соединены с первым кодовым входом и знаковым входом алгебраического сумматора, второй кодовый вход которого связан с выходом регистра и первым входом сумматора, второй вход которого - с выходом пятого блока памяти, а выход - с информационным входом цифроаналогового преобразователя, выход алгебраического сумматора подключен к информационному входу регистра, выход генератора тактовых импульсов соединен с тактовыми входами цифроаналогового и аналого-цифрового преобразователей и через делитель частоты - с выходом первого счетчика, входом запуска аналого-цифрового преобразователя и входом элемента НЕ, кодовый выход первого счетчика связан-с входом дешифратора,

выход переполнения первого счетчика соединен с входом второго счетчика и входом сброса регистра, выход второго счетчика - с информационным входом блока формирования адресов, первый выход дешифратора подключен к входам записи-считывания всех блоков памяти и тактирующему входу блока формирования адресов, второй выход дешифратора соединен с входом запуска

цифроаналогового преобразователя, группа выходов дешифратора связана с группой управляющих входов блока формирования адреса, выход элемента НЕ соединен с третьим входом элемента И, выход которого - с входом записи регистра.

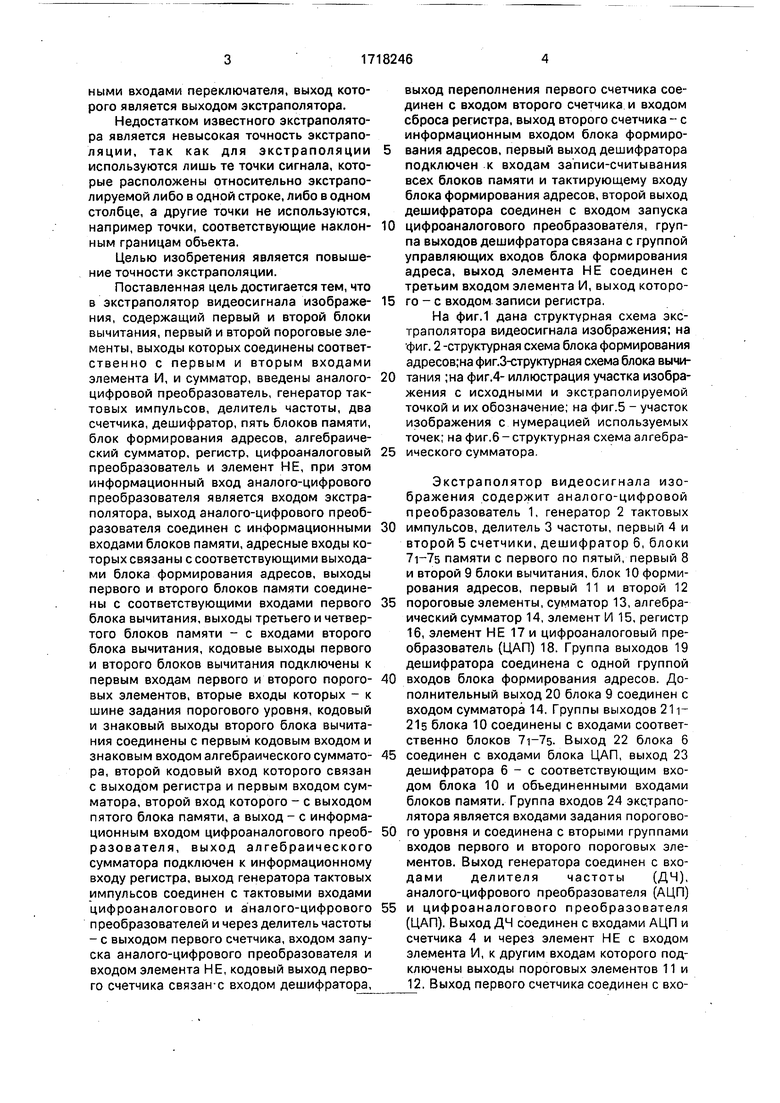

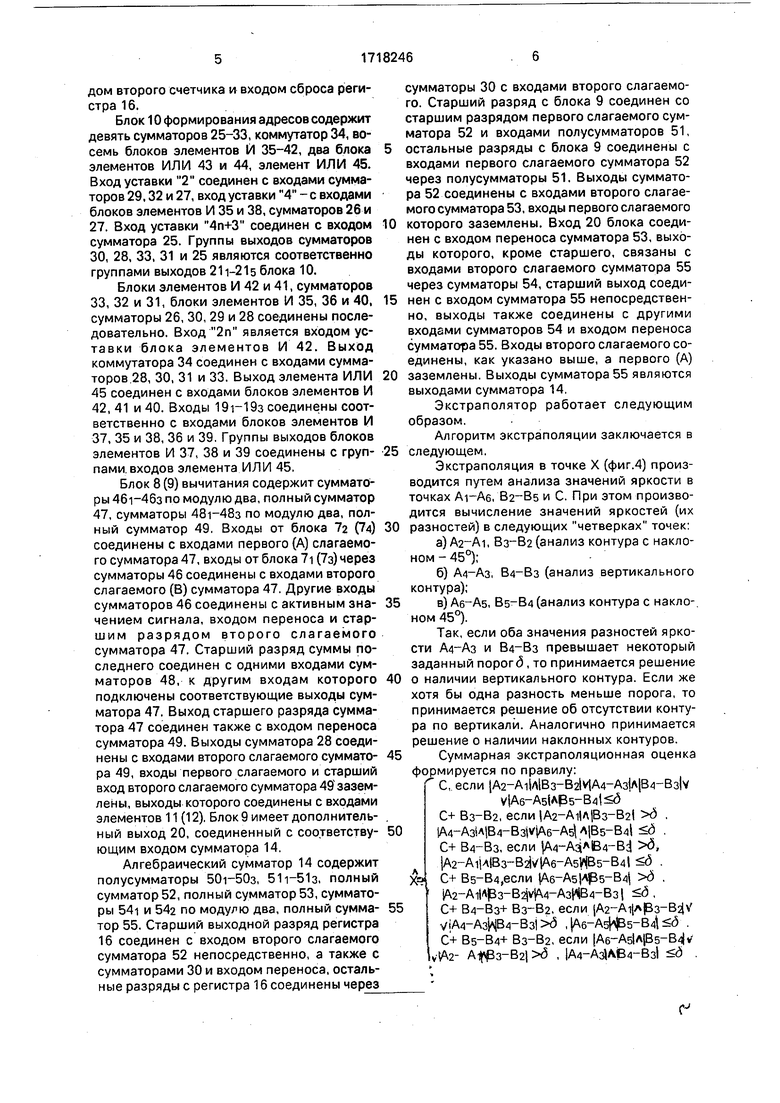

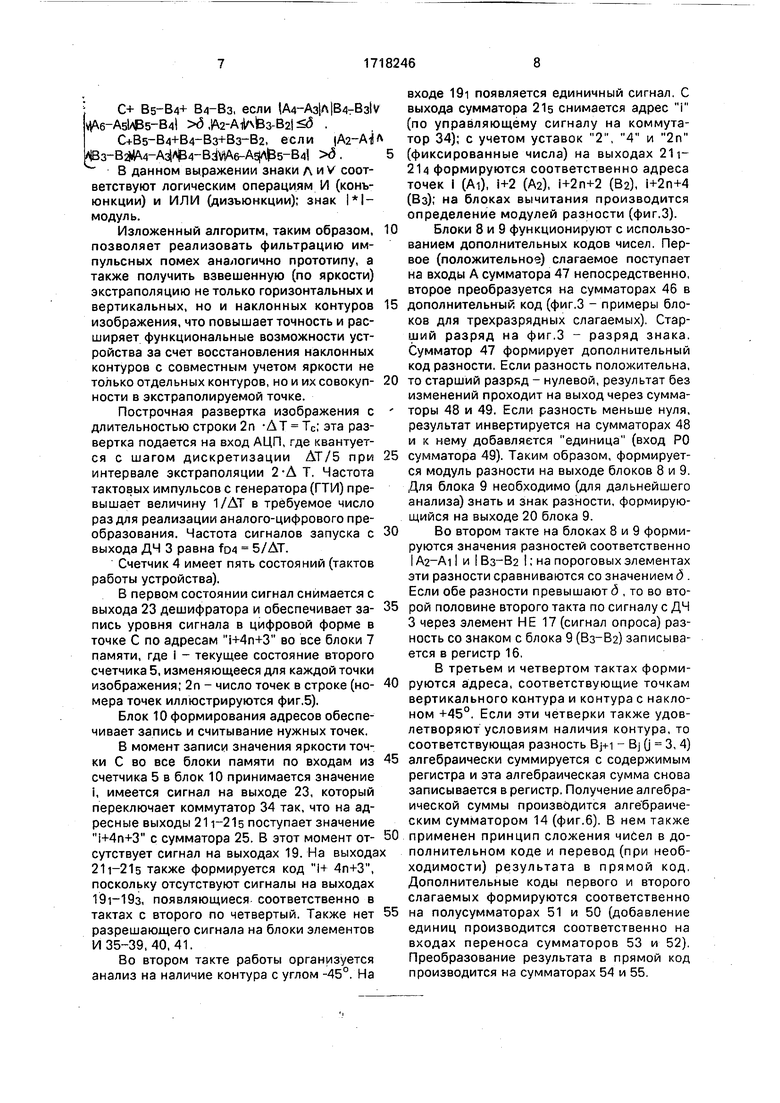

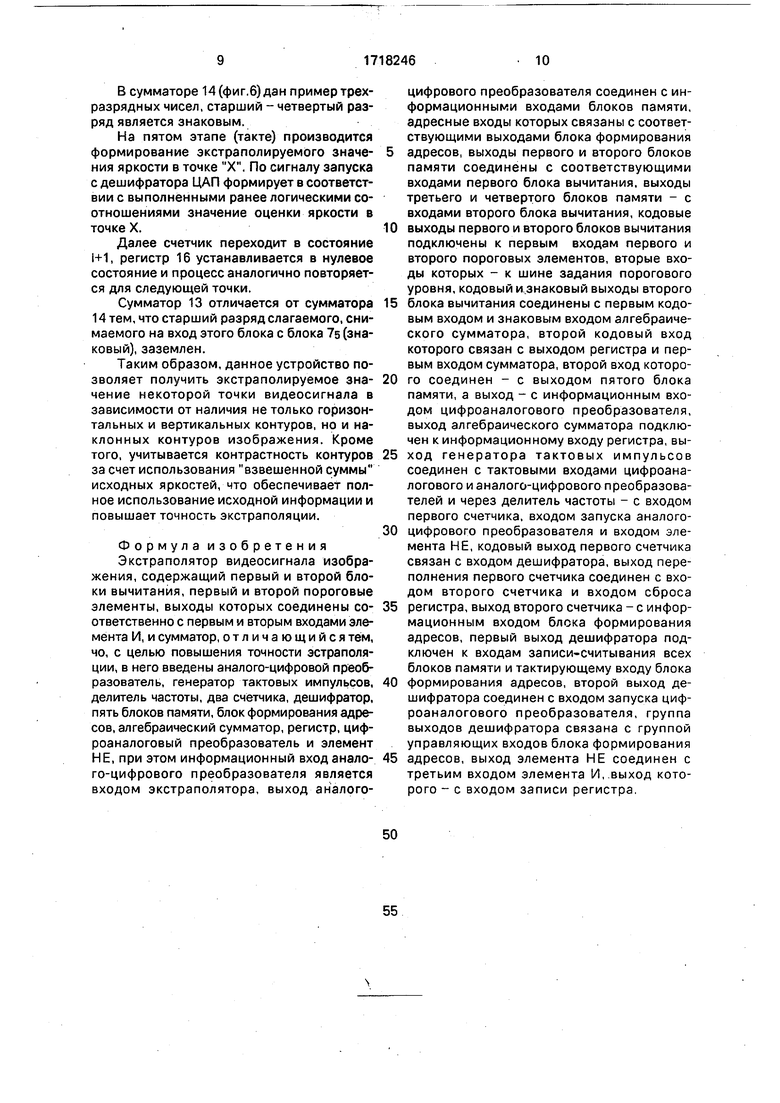

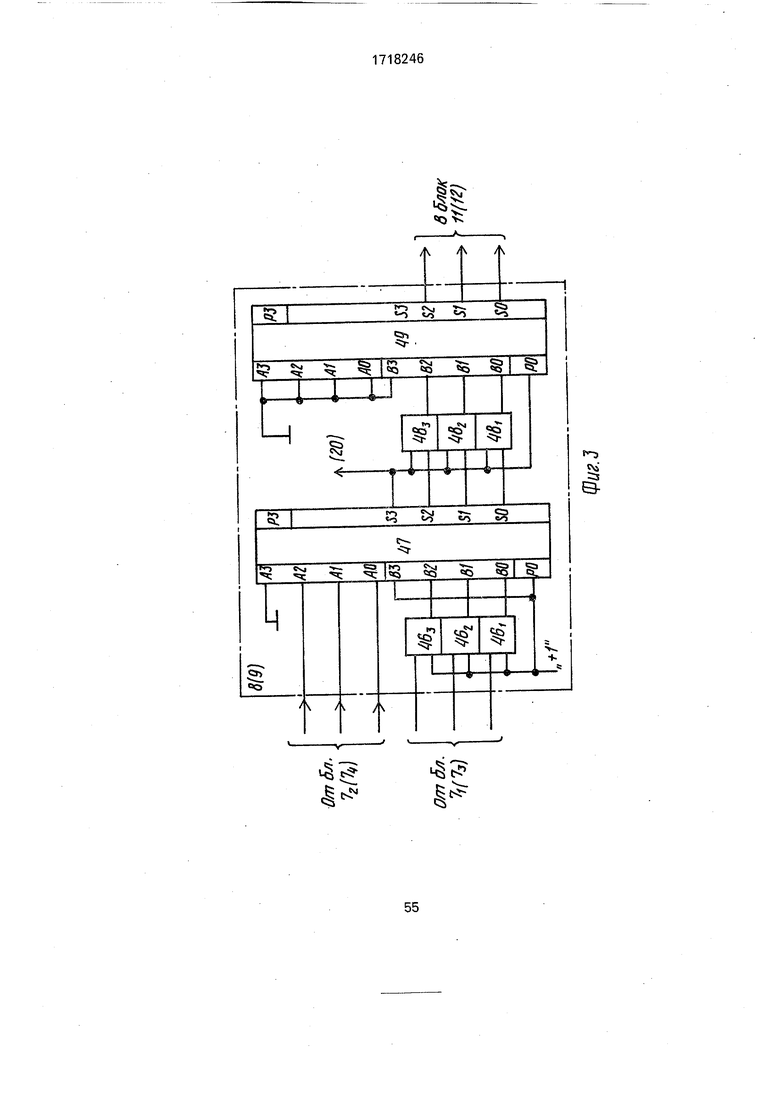

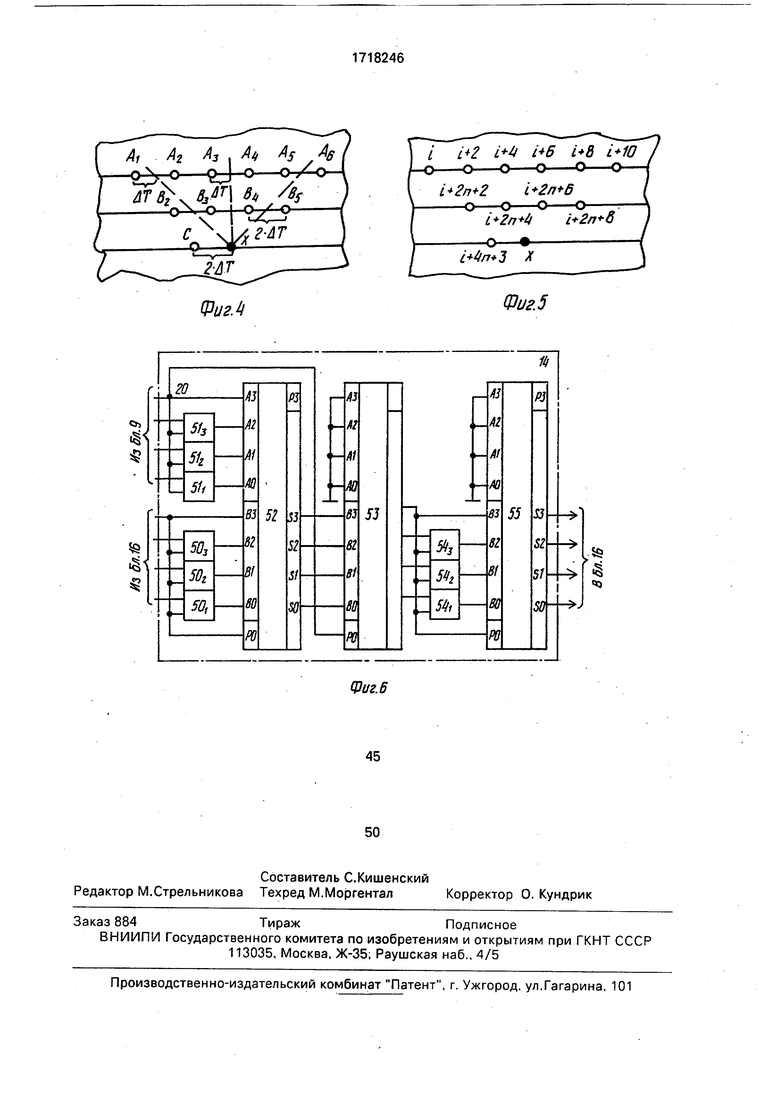

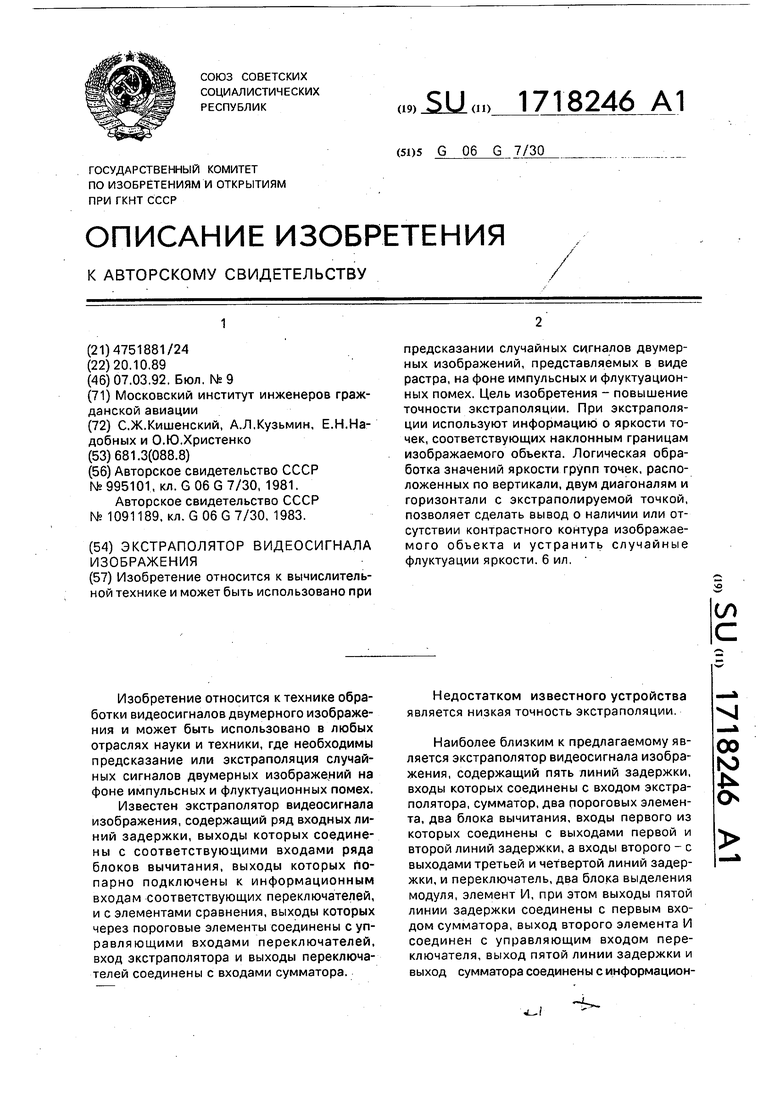

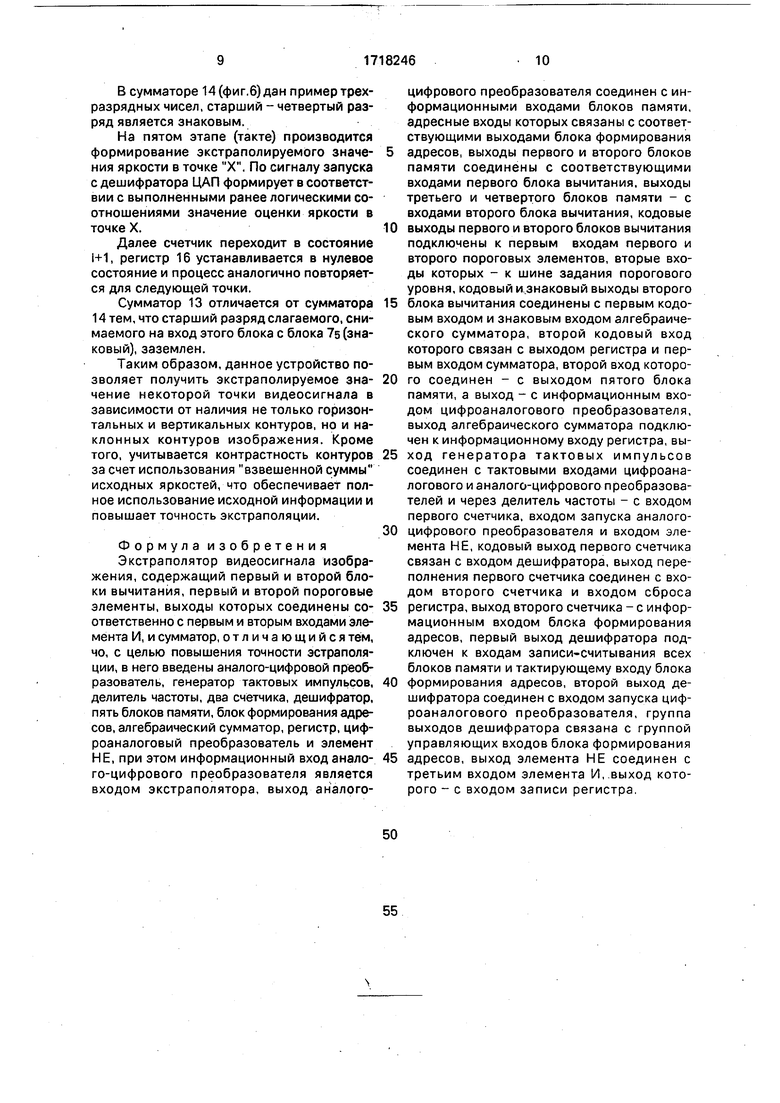

На фиг.1 дана структурная схема экстраполятора видеосигнала изображения; на фиг. 2 -структурная схема блока формирования адресов;на фиг.З-структурная схема блока вычитания ;на фиг.4- иллюстрация участка изображения с исходными и экстраполируемой точкой и их обозначение; на фиг.5 - участок изображения с нумерацией используемых точек; на фиг,6-структурная схема алгебраического сумматора.

Экстраполятор видеосигнала изображения содержит аналого-цифровой преобразователь 1, генератор 2 тактовых

импульсов, делитель 3 частоты, первый 4 и второй 5 счетчики, дешифратор 6, блоки 7i-7s памяти с первого по пятый/первый 8 и второй 9 блоки вычитания, блок 10 формирования адресов, первый 11 и второй 12

пороговые элементы, сумматор 13, алгебраический сумматор 14, элемент И 15, регистр 16, элемент НЕ 17 и цифроаналоговый преобразователь (ЦАП) 18. Группа выходов 19 дешифратора соединена с одной группой

входов блока формирования адресов. Дополнительный выход 20 блока 9 соединен с входом сумматора 14. Группы выходов 21i- 21s блока 10 соединены с входами соответственно блоков 7i-7s. Выход 22 блока 6

соединен с входами блока ЦАП, выход 23 дешифратора 6 - с соответствующим входом блока 10 и объединенными входами блоков памяти. Группа входов 24 экс.трапо- лятора является входами задания порогового уровня и соединена с вторыми группами входов первого и второго пороговых элементов. Выход генератора соединен с входами делителя частоты (ДЧ), аналого-цифрового преобразователя (АЦП)

и цифроаналогового преобразователя (ЦАП). Выход ДЧ соединен с входами АЦП и счетчика 4 и через элемент НЕ с входом элемента И, к другим входам которого подключены выходы пороговых элементов 11 и 12, Выход первого счетчика соединен с входом второго счетчика и входом сброса регистра 16.

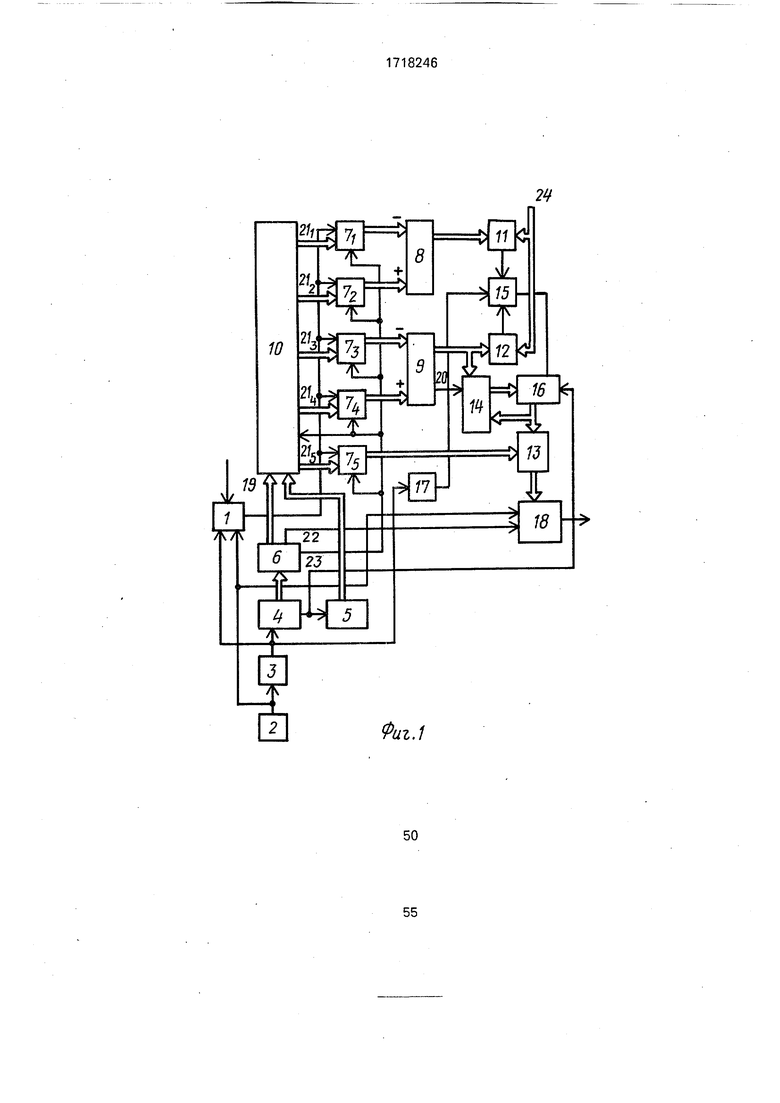

Блок 10 формирования адресов содержит девять сумматоров 25-33, коммутатор 34, восемь блоков элементов И 35-42, два блока элементов ИЛИ 43 и 44, элемент ИЛИ 45. Вход уставки 2 соединен с входами сумматоров 29,32 и 27, вход уставки 4 - с входами блоков элементов И 35 и 38, сумматоров 26 и 27. Вход уставки 4п+3 соединен с входом сумматора 25. Группы выходов сумматоров 30, 28, 33, 31 и 25 являются соответственно группами выходов 21i-21s блока 10.

Блоки элементов И 42 и 41, сумматоров 33, 32 и 31, блоки элементов И 35, 36 и 40, сумматоры 26, 30, 29 и 28 соединены последовательно. Вход 2п является входом уставки блока элементов И 42. Выход коммутатора 34 соединен с входами сумматоров 28, 30, 31 и 33. Выход элемента ИЛИ 45 соединен с входами блоков элементов И 42, 41 и 40. Входы соединены соответственно с входами блоков элементов И 37, 35 и 38, 36 и 39. Группы выходов блоков элементов И 37, 38 и 39 соединены с группами, входов элемента ИЛИ 45.

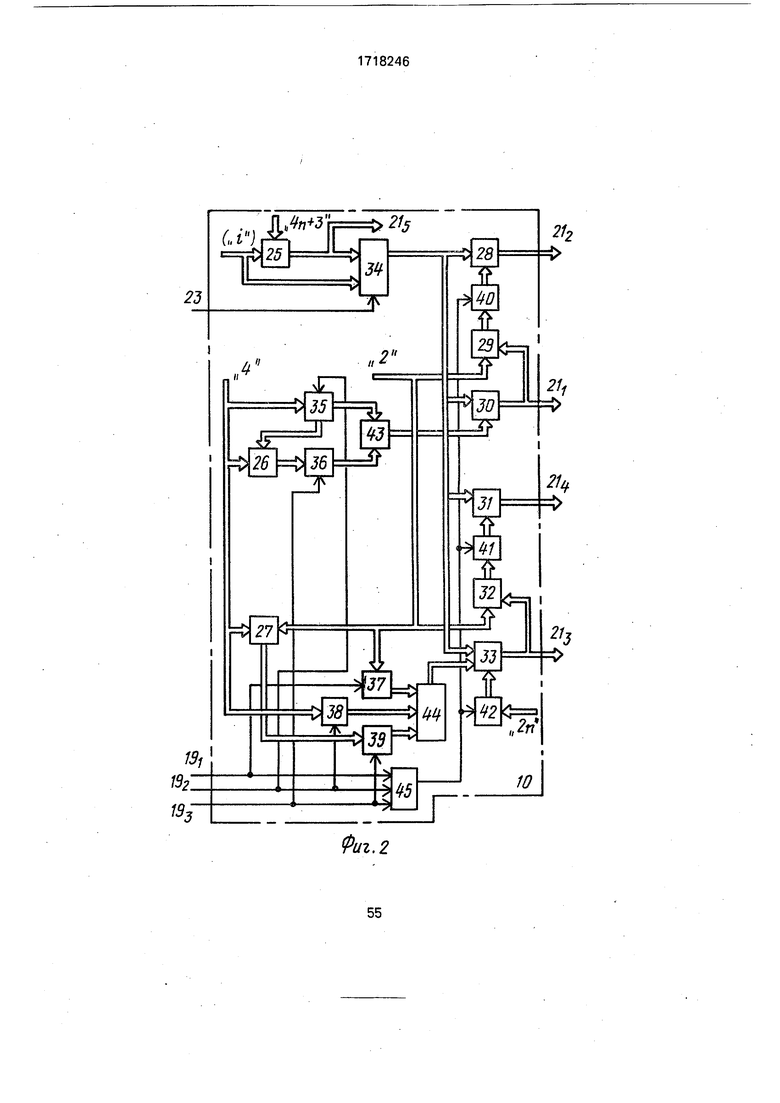

Блок 8 (9) вычитания содержит сумматоры по модулю два, полный сумматор 47, сумматоры 48ч-48з по модулю два, полный сумматор 49. Входы от блока 7а (74) соединены с входами первого (А) слагаемого сумматора 47, входы от блока 7i (7з) через сумматоры 46 соединены с входами второго слагаемого (В) сумматора 47. Другие входы сумматоров 46 соединены с активным значением сигнала, входом переноса и старшим разрядом второго слагаемого сумматора 47. Старший разряд суммы последнего соединен с одними входами сумматоров 48, к другим входам которого подключены соответствующие выходы сумматора 47. Выход старшего разряда сумматора 47 соединен также с входом переноса сумматора 49. Выходы сумматора 28 соединены с входами второго слагаемого сумматора 49, входы первого слагаемого и старший вход второго слагаемого сумматора 49заземлены, выходы которого соединены с входами элементов 11 (12), Блок 9 имеет дополнительный выход 20, соединенный с соответствующим входом сумматора 14.

Алгебраический сумматор 14 содержит полусумматоры 50-|-50з, , полный сумматор 52, полный сумматор 53, сумматоры 54i и 542 по модулю два, полный сумматор 55. Старший выходной разряд регистра 16 соединен с входом второго слагаемого сумматора 52 непосредственно, а также с сумматорами 30 и входом переноса, остальные разряды с регистра 16 соединены через

сумматоры 30 с входами второго слагаемого. Старший разряд с блока 9 соединен со старшим разрядом первого слагаемого сумматора 52 и входами полусумматоров 51,

остальные разряды с блока 9 соединены с входами первого слагаемого сумматора 52 через полусумматоры 51. Выходы сумматора 52 соединены с входами второго слагаемого сумматора 53, входы первого слагаемого

0 которого заземлены. Вход 20 блока соединен с входом переноса сумматора 53, выходы которого, кроме старшего, связаны с входами второго слагаемого сумматора 55 через сумматоры 54, старший выход соеди5 нен с входом сумматора 55 непосредственно, выходы также соединены с другими входами сумматоров 54 и входом переноса сумматора 55. Входы второго слагаемого соединены, как указано выше, а первого (А)

0 заземлены. Выходы сумматора 55 являются выходами сумматора 14.

Экстраполятор работает следующим образом.

Алгоритм экстраполяции заключается в

5 следующем.

Экстраполяция в точке X (фиг.4) производится путем анализа значений яркости в точках , B2-Bs и С. При этом производится вычисление значений яркостей (их

0 разностей) в следующих четверках точек:

а), 83-62 (анализ контура с наклоном-45°);

б), (анализ вертикального контура);

5в) , 65-64 (анализ контура с наклоном 45°).

Так, если оба значения разностей яркости и В4-Вз превышает некоторый заданный пороги, то принимается решение

0 о наличии вертикального контура. Если же хотя бы одна разность меньше порога, то принимается решение об отсутствии контура по вертикали. Аналогично принимается решение о наличии наклонных контуров.

5 Суммарная экстраполяционная оценка формируется по правилу: С, если А2-А1(л1Вз-В2|ЦА4-Аз|л(В4-Вз|у

V|A6-A5(AP5-B41(5

С+ Вз-Ва, если |А2-А1|А|Вз-В2| д . 0|А4-АзИВ4-Вз|У|Аб-А Л|В5-В4) д .

С+ В4-Вз, если |А4-АзлВ4-Вз д, |А2-А1|л|Вз-В2| |Аб-А5ЙВ5-В4| б

Х

5

С+ В5-В4,если |Аб-А5|лр5-В4 д .

А2-А1|А|Зз-В2|У 4-АзЙВ4-Вз| 6 ,

С+ В4-Вз+ , если |A2-AijA|B3-BjiV

у|А4-АзИВ4-В3| б ,|Аб-А5НВ5-В4(5

С+ В5-В4+ Вз-В2, если Аб-А5|л|В5-В4|у

/1&2- Afp3-B2| д , |А4-Аз1ЛВ4-В31 д .

С+ В5-В4+ В4-Вз, если |А4-Аз1л|В4-Вз№ у б-А5 лВ5-В4 5 ,г 2-А1 1Вз-В2| 6 ,

С+В5-В4+В4-Вз+Вз В2, если

3-B2MA4-A3№4-B3W6-A5J/ $5-B4l Х5 .

В данном выражении знаки л и V соответствуют логическим операциям И (конъюнкции) и ИЛИ (дизъюнкции); знак модуль.

Изложенный алгоритм, таким образом, позволяет реализовать фильтрацию импульсных помех аналогично прототипу, а также получить взвешенную (по яркости) экстраполяцию не только горизонтальных и вертикальных, но и наклонных контуров изображения, что повышает точность и расширяет функциональные возможности устройства за счет восстановления наклонных контуров с совместным учетом яркости не только отдельных контуров, но и их совокуп- ности в экстраполируемой точке.

Построчная развертка изображения с длительностью строки 2п -ДТ Тс; эта развертка подается на вход АЦП, где квантуется с шагом дискретизации АТ/5 при интервале экстраполяции 2-Д Т, Частота тактовых импульсов с генератора (ГТИ) превышает величину 1/АТ в требуемое число раз для реализации аналого-цифрового преобразования. Частота сигналов запуска с выхода ДЧ 3 равна fo4 5/АТ.

Счетчик 4 имеет пять состояний (тактов работы устройства).

В первом состоянии сигнал снимается с выхода 23 дешифратора и обеспечивает за- пись уровня сигнала в цифровой форме в точке С по адресам i+4n+3 во все блоки 7 памяти, где i - текущее состояние второго счетчика 5, изменяющееся для каждой точки изображения; 2п - число точек в строке (но- мера точек иллюстрируются фиг.5).

Блок 10 формирования адресов обеспечивает запись и считывание нужных точек,

В момент записи значения яркости точки С во все блоки памяти по входам из счетчика 5 в блок 10 принимается значение i, имеется сигнал на выходе 23, который переключает коммутатор 34 так, что на адресные выходы 21 i-21s поступает значение i+4n+3 с сумматора 25. В этот момент от- сутствует сигнал на выходах 19. На выхода 211-215 также формируется код I+ 4п+3, поскольку отсутствуют сигналы на выходах 19г-19з, появляющиеся соответственно в тактах с второго по четвертый. Также нет разрешающего сигнала на блоки элементов И 35-39, 40, 41.

Во втором такте работы организуется анализ на наличие контура с углом -45°. На

входе 19i появляется единичный сигнал. С выхода сумматора 21s снимается адрес i (по управляющему сигналу на коммутатор 34); с учетом уставок 2, 4 и 2п (фиксированные числа) на выходах 21 - 214 формируются соответственно адреса точек i (Ai), i+2 (A2), i+2n+2 (82), i+2n+4 (Вз); на блоках вычитания производится определение модулей разности (фиг.З).

Блоки 8 и 9 функционируют с использованием дополнительных кодов чисел. Первое (положительное) слагаемое поступает на входы А сумматора 47 непосредственно, второе преобразуется на сумматорах 46 в дополнительный код (фиг.З - примеры блоков для трехразрядных слагаемых). Старший разряд на фиг.З - разряд знака. Сумматор 47 формирует дополнительный код разности. Если разность положительна, то старший разряд - нулевой, результат без изменений проходит на выход через сумматоры 48 и 49. Если разность меньше нуля, результат инвертируется на сумматорах 48 и к нему добавляется единица (вход РО сумматора 49). Таким образом, формируется модуль разности на выходе блоков 8 и 9. Для блока 9 необходимо (для дальнейшего анализа) знать и знак разности, формирующийся на выходе 20 блока 9.

Во втором такте на блоках 8 и 9 формируются значения разностей соответственно IA2-A11 и I I; на пороговых элементах эти разности сравниваются со значением д . Если обе разности превышают б , то во второй половине второго такта по сигналу с ДЧ 3 через элемент НЕ 17 (сигнал опроса) разность со знаком с блока 9 (63-62) записывается в регистр 16,

В третьем и четвертом тактах формируются адреса, соответствующие точкам вертикального контура и контура с наклоном +45°. Если эти четверки также удовлетворяют условиям наличия контура, то соответствующая разность Bj+i - Bj (j 3, 4) алгебраически суммируется с содержимым регистра и эта алгебраическая сумма снова записывается в регистр. Получение алгебраической суммы производится алгебраическим сумматором 14 (фиг.6). В нем также применен принцип сложения чисел в дополнительном коде и перевод (при необходимости) результата в прямой код, Дополнительные коды первого и второго слагаемых формируются соответственно на полусумматорах 51 и 50 (добавление единиц производится соответственно на входах переноса сумматоров 53 и 52). Преобразование результата в прямой код производится на сумматорах 54 и 55.

В сумматоре 14(фиг.6)дан пример трехразрядных чисел, старший - четвертый разряд является знаковым.

На пятом этапе (такте) производится формирование экстраполируемого значения яркости в точке X. По сигналу запуска с дешифратора ЦАП формирует в соответствии с выполненными ранее логическими соотношениями значение оценки яркости в точке X.

Далее счетчик переходит в состояние 1+1, регистр 16 устанавливается в нулевое состояние и процесс аналогично повторяется для следующей точки.

Сумматор 13 отличается от сумматора 14 тем, что старший разряд слагаемого, снимаемого на вход этого блока с блока 7s (знаковый), заземлен.

Таким образом, данное устройство позволяет получить экстраполируемое значение некоторой точки видеосигнала в зависимости от наличия не только горизонтальных и вертикальных контуров, но и наклонных контуров изображения. Кроме того, учитывается контрастность контуров за счет использования взвешенной суммы исходных яркостей, что обеспечивает полное использование исходной информации и повышает точность экстраполяции.

Формула изобретения Экстраполятор видеосигнала изображения, содержащий первый и второй блоки вычитания, первый и второй пороговые элементы, выходы которых соединены соответственно с первым и вторым входами элемента И, и сумматор, отличающийся тем, чо, с целью повышения точности эстраполя- ции в него введены аналого-цифровой преобразователь, генератор тактовых импульсов, делитель частоты, два счётчика, дешифратор, пять блоков памяти, блок формирования адресов, алгебраический сумматор, регистр, циф- роаналоговый преобразователь и элемент НЕ, при этом информационный вход аналого-цифрового преобразователя является входом экстраполятора, выход аналогоцифрового преобразователя соединен с информационными входами блоков памяти, адресные входы которых связаны с соответствующими выходами блока формирования

адресов, выходы первого и второго блоков памяти соединены с соответствующими входами первого блока вычитания, выходы третьего и четвертого блоков памяти - с входами второго блока вычитания, кодовые

выходы первого и второго блоков вычитания подключены к первым входам первого и второго пороговых элементов, вторые входы которых - к шине задания порогового уровня, кодовый и знаковый выходы второго

блока вычитания соединены с первым кодовым входом и знаковым входом алгебраического сумматора, второй кодовый вход которого связан с выходом регистра и первым входом сумматора, второй вход которого соединен - с выходом пятого блока памяти, а выход - с информационным входом цифроаналогового преобразователя, выход алгебраического сумматора подключен к информационному входу регистра, выход генератора тактовых импульсов соединен с тактовыми входами цифроаналогового и аналого-цифрового преобразователей и через делитель частоты - с входом первого счетчика, входом запуска аналогоцифрового преобразователя и входом элемента НЕ, кодовый выход первого счетчика связан с входом дешифратора, выход переполнения первого счетчика соединен с входом второго счетчика и входом сброса

регистра, выход второго счетчика - с информационным входом блока формирования адресов, первый выход дешифратора подключен к входам записи-считывания всех блоков памяти и тактирующему входу блока

формирования адресов, второй выход дешифратора соединен с входом запуска цифроаналогового преобразователя, группа выходов дешифратора связана с группой управляющих входов блока формирования

адресов, выход элемента НЕ соединен с третьим входом элемента И,.выход которого - с входом записи регистра.

ton.1

fin. 2

f

C-j

° $§

-§

9frS8Ul

А2 А3 Ац А5 Ъ

з 4bXo-j-Oy -0 PU2.4

с

«9

Ǥ

Фиг. 5

| Экстраполятор | 1981 |

|

SU995101A1 |

| Экстраполятор видеосигнала изображения | 1983 |

|

SU1091189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-03-07—Публикация

1989-10-20—Подача