чей к сиихровходу первого регистра, счетчика, выход третьего разряда синхровходу первого сумматора, вторым сдвигового регистра подключен к тревходам элементов И третьей группы, тьим входам элементов И третьей вторым-входам элементов И второй группы и синхровходу второго регистгруппы и синхровходу реверсивного

1126970

ра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления с коррекцией траектории обработки | 1990 |

|

SU1727111A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для контроля аналоговых объектов | 1988 |

|

SU1522239A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

ЦИФРОВОЙ ЭКСТРАПОЛЯТОР, содержащий блок управления, первый регистр, информационные входы которого подключены к первым входам соответствующих элементов И первой группы, выходы которых подключены к со- . ответствующим информационным входам первой группы первого сумматора, информационный выход которого подключен к информационному входу второго регистра, информационные выходы которого подключены к первым входам соответс вующих элементов И второй группы, выходы которых подключены к соответствующим информационным входам первой группы второго сумматора, информационный выход которого подключен к информационному входу преобразователя код-частота,- информационньш выход которого подключен к счетному входу реверсивного счетчика, информационньй вход которого поразрядно соединен с информационными входами второй группы первого сумматора, информационным входом первого регистра и является информационным входом экстраполятора, первьш и второй знаковый выходы второго сумматора подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, информационный выход которого является информационным выходом экстраполятора, отличающийся тем, что, с целью упрощения экстраполятора, он содержит третью группу элементов И, информационньй выход первого сумматора подключен поразрядно к первым входам соответствующих элементов И третьей группы, выходы которых подключены к соответствую 191м информационным входам второй группы второго сумматора, причем блок управления содержит элемент ИЛИ, формирователь (Л импульсов, триггер, генератор опор ной частоты, элемент И и сдвиговый регистр, тактовый вход которого подключен к выходу элемента И, первый вход которого подключен к выходу триггера, вход установки в единицу которого подключен к выходу формирователя импульсов, вход которого подключен к выходу элемента ИЛИ, входы которого соединены поразрядно с информационным входом первого регистра, выход генератора опорной частоты подключен к второму входу элемента И, . выход четвертого разряда сдвигового регистра подключен к входу обнуления сдвигового регистра, входу установки в ноль триггера и синхровходу преобразователя код-частота, выход первого разряда, .сдвигового регистра подключен к вторым входам элементов И первой группы и установочному входу реверсивного счетчика, выход второго разряда сдвигового регистра подклю

Изобретение относится к вычислительной технике и может использоваться в цифровых системах автоматического .управления.

Известен цифровой экстраполятор5 содержащий регистр памяти элемент И, параллельный сумматор, преобразователь код-частота, реверсивный с.четчик и устройство управления lj .

Недостатком известного цифрового экстраполятора является низкая точ ность экстраполяции, что обуславливается игнорированием информации на предпоследнем шаге экстраполяции.

Наиболее близким к предлагаемому является цифровой экстраполятор, содержащий первый регистр, первую группу элементов И, первый (параллельный) сумматор, преобразователь код-частота, реверсивный счетчик, второй (параллельный) сумматор, третий (параллельный) сумматор, второй регистр, вторую группу элементов И, блок управления, первый, второй, третий, четвертый, пятый выходы блока управления подключены к управляющим входам соответствующих узлов экстраполятора, первый регистр, первая группа элементов И, первый сумматор, второй регистр, первая группа элементов И, второй сумматор, преобразователь код-частота реверсивный счетчик соединены последовательно 2 ,

Недостатками данного устройства являются низкая скорость работы (для реализации алгоритма вычисления экстраполируемого отсчета требуется пять тактов, что наряду с большим числом необходимых операций суммирования определяет низкую скорость работы устройства), ограниченная область применения в системах обработки информации, работающих в реальном масштабе времени, необходимость

применения третьего сумматора, что усложняет аппаратурную реализацию и снижает надежность работы всего устройства.

Цель изобретения

упрощение экстраполятора.

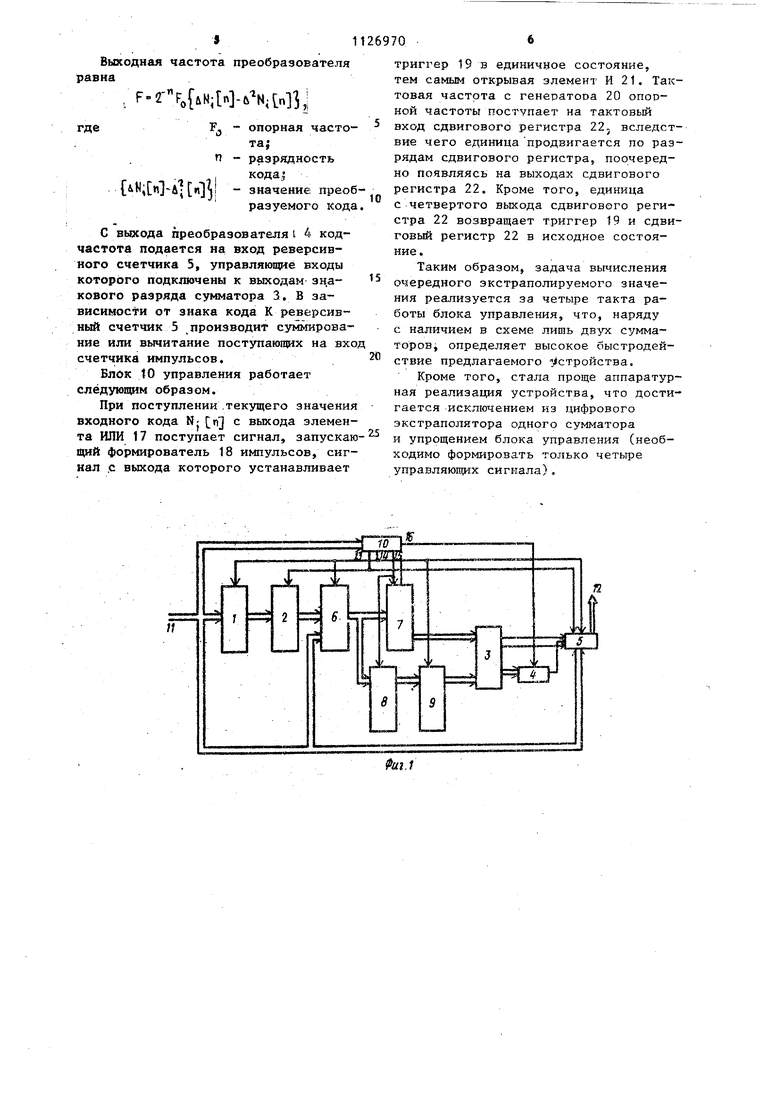

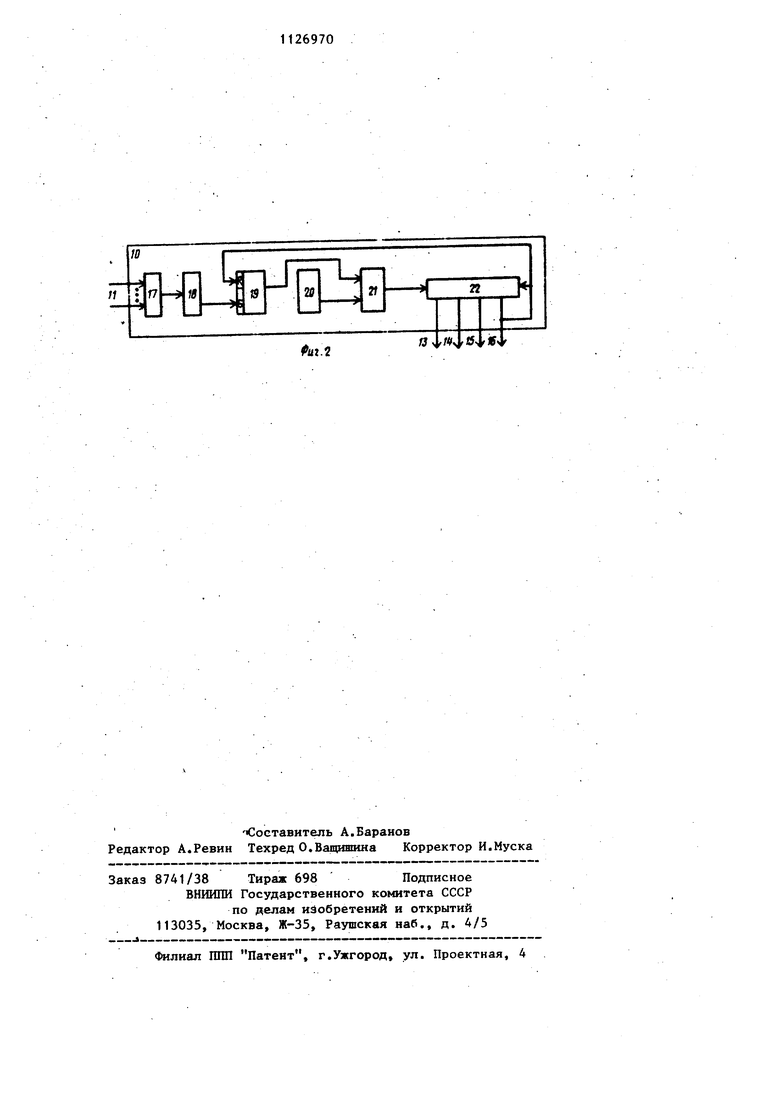

Поставленная цель достигается тем что цифровой экстраполятор содержащий блок управления, первый регистр информационные выходы которого подключены к первым входам соответствующих элементов И первой группы, выходы которых подключены к соответствующим информационным входам первой группы первого сумматора, информаЦИОННЫ.Й .;1ыход которого подключен к икфсрмационному входу второго регистра, информационные выходы котороге подключены к первым входам соответствующих элементов И второй группы, выходы которых подключены к соответствующим информационным входам первой группы второго сумматора, информационный выход которого подключен к информационному входу преобразователя код-часто.та, информационньй выход которого подключен к счетному входу реверсивного счетчика, информационный ьход которого поразрядно соединен с информационными входами второй группы первого сумматора, информационным входом первого регистра и является информационным входом экстраполятора, первый и второй знаковый выходы второго сумматора подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, информационный выход которого является информационным выходом экстраполятора, содержит третью группу элементов И, информационный выход первого сумматора подключен поразрядно к первьм входам cooTBeTCTBymijJiHx элементов И третьей группы, выходы которых под ключены к соответствующим информаци онным входам второй группы второго сумматора, причем блок управления содержит элемент ИЛИ, формировател 5 импульсов, триггер, генератор опорной частоты, элемент И и сдвиговый регистр, тактовый вход которого подключен к выходу элеменг та И, первый вх д которого подключей к выходу триггера, .вход установ ки в единицу которого подключен к выходу формирователя импульсов, вход которого подключен к выходу элемента ИЛИ, входы которого соединены поразрядно с информационным входом первого регистра, выход гене ратора опорной частоты подключен к второму входу элементаИ, выход четвертого разряда сдвигового регис ра подключен к входу обнуления сдви гового регистра,входу установки в ноль триггера и синхровходу преоб разователя код-частота, вькод перво го разряда сдвигового регистра подключен к вторым входам элементов И первой группы и установочному входу реверсивного счетчика, выход второг разряда сдвигового регистра подключен к синхровходу первого регистра, синхровходу первого сумматора, .втор входам элементов И третьей группы, вторым входам элементов И второй группы и синхровходу реверсивного счетчика, выход третьего разряда сдвигового регистра подключен к тре тьим входам элементов И третьей группы и синхровходу второго регист ра. На фиг. 1 представлена структурнал схема -цифрового экстраполятора; на фиг. 2 - блок-схема блока управления. Экстраполятор содержит регистр 1 грут лу 1. элементов И, параллельный сумматор 3, преобразователь 4 кодчастота, реверсивный счетчик 5, параллельный сумматор 6, группу 7 элементов И, регистр 8, группу 9 элементов И, блок 10 управления, информационньй вход 11, информацион ный выход 12, выходы 13 - 16 блока управления. Блок 10 управления содержит элемент ИЛИ 17, формирователь 18 импул сов, триггер 19, генератор 20 опорной частоты, элемент И 21, сдвиговы регистр 2i.. Устройство работает следующим образом. При поступлении текущего значения входного кода Nj nl его предшествующее значение N,-., п по тактовому импульсу с первого выхода 13 блока 10 управления переписывается в сумматор 6, а реверсивный счетчик 5 обнуляется. После этого, вторым тактовым импульсом с выхода 14 блока 10 управления, текущее значение Nj записывается в регистр 1, в pfEsepсивный счетчик 5 и заносится в сумматор 6, в котором вычисляется первая конечная разность 1 AN,h} N;W-N,W . Код разности третьим тактовым импульсом с выхода 15 блока 10 управления записывается в регистр 8 и заносится в сумматор 3, причем занесение происходит через группу 9 элементов И с сдвигом на один разряд в сторону старших разрядов, чем достигается умножение на два. В это время в сумматоре 3 уже находится код |bN;.,W-N..,-N-.,n, гяэлученный в предыдущем цикле работы экстраполятора и переписанный в него по второму тактовому импульсу через группу 9 элементов И из регистра 8. В сумматоре 3 вычисляется разность, ,.,, С) Перепишем выражение в фигурных скобках управления (1) следующим образом: 2&Н,Ы-йН-.,Ы М; ЛМ ., п , гделМ,-ьМ,, - разность второго порядка. . Окончательно перепишем (1) в виде: .gnf4N; n -Ab,W, С вьшода 16 блока 10 управления оступает четвертый тактовый импульс, запускающий преобразователь 4 кодастота, на первый вход которого потупает с выхода сумматора 3 код азности К, который преобразуется частоту следования импульсов. Выходная частота преобразователя равна . ,uN;In -,Ndnl,: опорная частоrajразрядность кода,| {4N, значение преоб разуемого кода С вцхода преобразователя i 4 кодчастота подается на вход реверсивного счетчика 5, управляющие входы которого подключены к выходам знакового разряда сумматора 3, В зависимости от знака кода К реверсивный счетчик 5 производит суммирование или вычитание поступаюп(нх на вхо счетчика импульсов. Блок to управления работает следующим образом. При поступлении .текущего значения входного кода с вькода элемента ИЛИ 17 поступает сигнал, запускаю 11Ц1й формирователь 18 импульсов, сигнал ,с выхода которого устанавливает триггер 19 в единичное состояние, тем самым открывая элемент И 21. Тактовая частота с генератора 20 опорной частоты поступает на тактовый вход сдвигового регистра 22. вследствие чего единица продвигается по разрядам сдвигового регистра} поочередно появляясь на выходах сдвигового регистра 22. Кроме того, единица с четвертого вькода сдвигового регистра 22 возвращает триггер 19 и сдвиговый регистр 22 в исходное состояние. Таким образом, задача вычисления очередного экстраполируемого значения реализуется за четыре такта работы блока управления, что, наряду с наличием в схеме лишь дв5гх суммаTopDBi определяет высокое быстродействие предлагаемого Устройства. Кроме того, стала проще аппаратурная реализация устройства, что достигается исключением из цифрового экстраполятора одного сумматора и упрощением блока управления (необходимо формировать только четыре управляющих сигнала),

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой экстраполятор | 1978 |

|

SU694865A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-30—Публикация

1983-07-11—Подача