(54) УСТРОЙСТВО ДЛЯ ХРАНЕНИЯ И ВЫБОРКИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

| Устройство для измерения электрической проводимости и магнитной проницаемости | 1989 |

|

SU1659928A1 |

| Устройство для хранения и выборки информации | 1981 |

|

SU982096A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Устройство выборки и хранения | 1979 |

|

SU826564A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU634374A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1062794A1 |

| Устройство выборки и хранения | 1982 |

|

SU1056463A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании аналого-цифровых преобразователей.

Известно устройство выборки и хранения, содержащее буферный операционный усилитель, аналоговый ключ на диодном мосту, запоминающий конденсатор и выходной буферный усилитель 1.

Недостаток устройства - больщое энергопотребление в режиме хранения.

Наиболее близким по технической сущности к изобретению является устройство выборки и хранения, содержащее дифференциальный каскад на транзисторах, объединенные эмиттеры которых соединены с коллектором третьего транзистора, на базу которого подается управляющий сигнал, а эмиттер соединен с отрицательным источником питания, коллекторы первого и второго транзисторов дифференциального каскада соединены, соответственно, с коллекторами четвертого и пятого транзисторов, эмиттеры которых объединены и соединены с положительным источником питания, базы объединены л соединены с коллектором четвертого, транзистора, коллектор второго транзистора дифференциального каскада соединен с одной из обкладок конденсатора 2.

Недостаток устройства - малое быстродействие, ограниченное полосой пропускания операционного усилителя при значительном энергопотреблении в режиме хранения. Например, при использовании операционного усилителя с полосой пропускания 15 МГц время выборки 1 МКС при потреблении в режиме хранения 200 мВт.

Цель изобретения - повышение быстродействия устройства и уменьщение им потребляемой мощности.

Поставленная цель достигается тем, что в устройство для хранения и выборки информации, содержащее накопительный элемент, например, конденсатор, одна из обкладок которого соединена с щиной нулевого потен5циала, дифференциальный каскад, выполненный на первом, втором, третьем и четвертом транзисторах, база первого транзистора соединена с щиной входного сигнала, коллекторы первого и второго транзис0торов соединены соответственно с коллекторами третьего и четвертого транзисторов, эмиттеры которых подключены к положительной щине питания, коллектор первого транзистора соединен с базами третьего и четвертого транзисторов, ключ, выполненный на пятом транзисторе, коллектор которого соединен с эмиттерами первого и второго транзисторов, база пятого транзистора подсоединена к шине управления, а эмиттер - к отрицательной шине питания, введены элемент подзаряда, выполяенный на шестом транзисторе, и эмиттерный повторитель, выполненный -на седьмом транзисторе и элементе нагрузки, например, резистора, один вьшод которого соединен с шиной нулевого потенциала, а другой вывод - с выходной шиной устройства,эмиттерэм седьмого транзистора и базой второго транзистора, база седьмого транзистора подключена к другой обкладке конденсатора, коллектор седьмого транзистора соединен с эмиттером шестого транзистора, база которого подключена к коллектору первого транзистора, коллектор шестого транзистора соединен с положительной шиной питания.

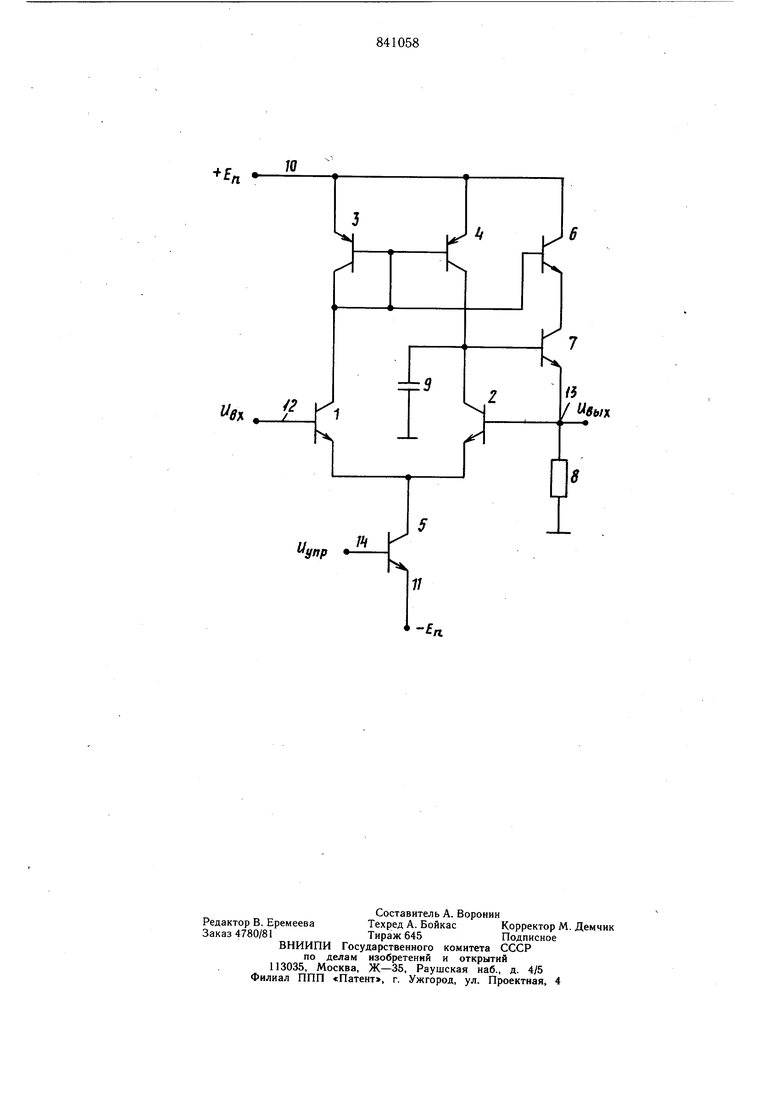

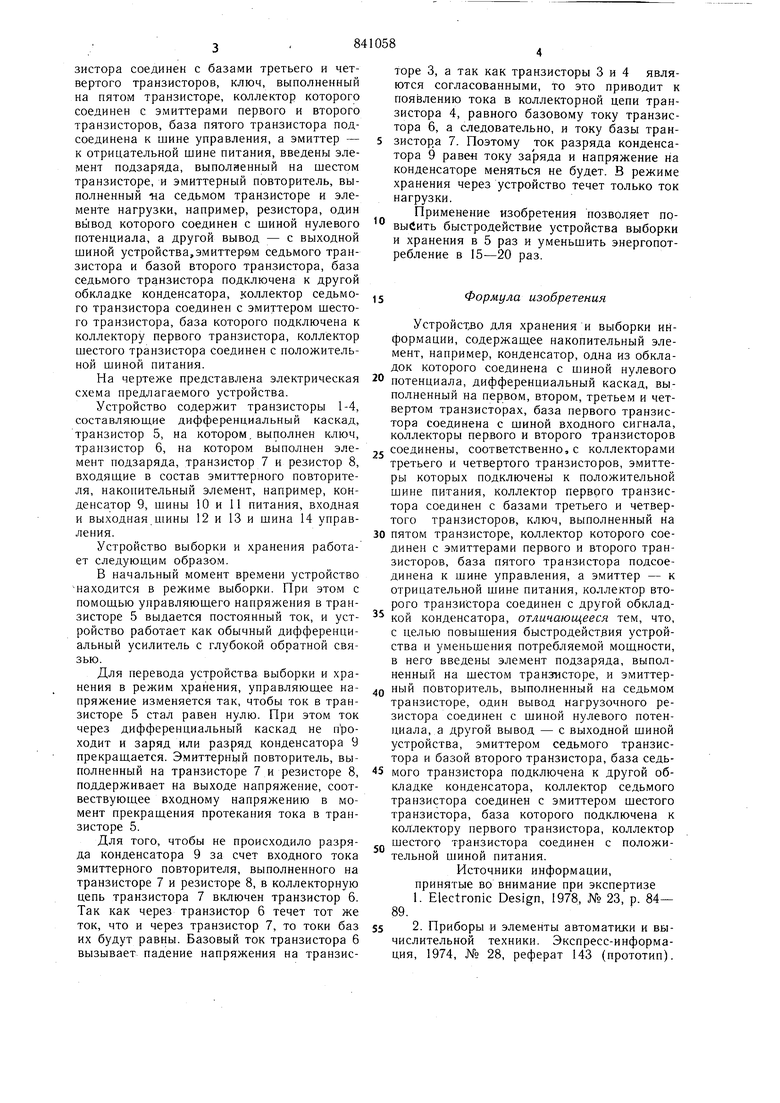

На чертеже представлена электрическая схема предлагаемого устройства.

Устройство содержит транзисторы 1-4, составляюш,ие дифференциальный каскад, транзистор 5, на котором, выполнен ключ, транзистор 6, на котором выполнен элемент подзаряда, транзистор 7 и резистор 8, входящие в состав эмиттерного повторителя, накопительный элемент, например, конденсатор 9, шины 10 и 11 питания, входная и выходная шины 12 и 13 и шина 14 управления.

Устройство выборки и хранения работает следующим образом.

В начальный момент времени устройство находится в режиме выборки. При этом с помощью управляющего напряжения в транзисторе 5 выдается постоянный ток, и устройство работает как обычный дифференциальный усилитель с глубокой обратной связью.

Для перевода устройства выборки и хранения в режим хранения, управляющее напряжение изменяется так, чтобы ток в транзисторе 5 стал равен нулю. При этом ток через дифференциальный каскад не про.ходит и заряд или разряд конденсатора 9 прекращается. Эмиттерньш повторитель, выполненный на транзисторе 7 и резисторе 8, поддерживает на выходе напряжение, соотвествующее входному напряжению в момент прекращения протекания тока в транзисторе 5.

Для того, чтобы не происходило разряда конденсатора 9 за счет входного тока эмиттерного повторителя, выполненного на транзисторе 7 и резисторе 8, в коллекторную цепь транзистора 7 включен транзистор 6. Так как через транзистор 6 течет тот же ток, что и через транзистор 7, то токи баз их будут равны. Базовый ток транзистора б вызывает падение напряжения на транзисторе 3, а так как транзисторы 3 и 4 являются согласованными, то это приводит к появлению тока в коллекторной цепи транзистора 4, равного базовому току транзистора 6, а следовательно, и току базы транзистор а 7. Поэтому ток разряда конденсатора 9 раве« току заряда и напряжение на конденсаторе меняться не будет. В режиме хранения через устройство течет только ток нагрузки.

Применение изобретения позволяет повыйить быстродействие устройства выборки и хранения в 5 раз и уменьшить энергопотребление в 15-20 раз.

Формула изобретения

Устройство для хранения и выборки информации, содержащее накопительный элемент, например, конденсатор, одна из обкладок которого соединена с шиной нулевого

потенциала, дифференциальный каскад, выполненный на первом, втором, третьем и четвертом транзисторах, база первого транзистора соединена с шиной входного сигнала, коллекторы первого и второго транзисторов

r соединены, соответственно, с коллекторами третьего и четвертого транзисторов, эмиттеры которых подключены к положительной щине питания, коллектор первого транзистора соединен с базами третьего и четвертого транзисторов, ключ, выполненный на

0 пятом транзисторе, коллектор которого соединен с эмиттерами первого и второго транзисторов, база пятого транзистора подсоединена к шине управления, а эмиттер - к отрицательной шине питания, коллектор второго транзистора соединен с другой обкладкой конденсатора, отличающееся тем, что, с целью повышения быстродействия устройства и уменьшения потребляемой мощности, в него введены элемент подзаряда, выполненный на шестом транзисторе, и эмиттерный повторитель, выполненный на седьмом транзисторе, один вывод нагрузочного резистора соединен с шиной нулевого потенциала, а другой вывод - с выходной шиной устройства, эмиттером седьмого транзистора и базой второго транзистора, база седьмого транзистора подключена к другой обкладке конденсатора, коллектор седьмого транзистора соединен с эмиттером шестого транзистора, база которого подключена к коллектору первого транзистора, коллектор шестого транзистора соединен с положительной шиной питания.

Источники информации, принятые во внимание при экспертизе 1. Electronic Design, 1978, № 23, p. 84- 89.

5 2. Приборы и элементы автоматики и вычислительной техники. Экспресс-информация, 1974, № 28, реферат 143 (прототип).

W

n

-r-

r

zb5

/3 V Wewx

f/.

77

Авторы

Даты

1981-06-23—Публикация

1979-09-06—Подача