Изобретение относится к радиотехнике и электротехнике и может быть использовано в устройствах автоматики и измерительной техники для умножения частоты сигналов и повышения разрешающей спо- собности измерительных приборов.

Известно устройство, содержащее последовательно соединенные согласующий фильтр и диод с накоплением заряда, причем свободные выводы согласующего филь- тра и диода соединены с входами и общими выводами соответственно, а также последовательно соединенные разделительный конденсатор и ферритовый фильтр, свободным выводом соединенный с выходным вы- водом, а частотнозависимый элемент включенный между общей точкой соединения согласующего фильтра с диодом и сво- бодным выводом разделительного конденсатора.

Недостатком устройства является низкая стабильность амплитуды и частоты высших гармоник входного сигнала, а также низкая надежность в работе из-за сложности фильтрации нужной гармоники при од- новременном наличии на выходе гармоник входного сигнала,

Наиболее близким техническим решением является умножитель частоты, содержащий импульсный усилитель, один выход которого непосредственно, а другой через фазоинверсный каскад подключены к входу дифференцирующих цепочек, выходы которых через разделительные диоды соединены с выходной клеммой устройства, ждущий мультивибратор, преобразователь частоты в напряжение и управляемый мультивибратор, вход запуска которого подключены к выходу ждущего мультивибратора непосредственно, вход управления через преоб- разователь частоты в напряжение, а выход соединен с входом импульсного усилителя.

Недостатком данного устройства является низкая стабильность амплитуды, сложность схемного решения, нестабильность во времени фронта и среза импульсов удвоенной частоты.

Цель изобретения - повышение стабильности амплитуды выходного сигнала и надежности работы устройства в целом.

Предложенный умножитель частоты позволяет получить стабильную амплитуду вы- ходного сигнала с коэффициентом умножения 2 раз при существенном уменьшении габаритных размеров устройства. Повышение надежности достигается за счет сокращения количества используемых в устройстве деталей и работы при высоких уровнях сигнала.

Поставленная цель достигается тем, что устройство, содержащее входной, выходной и общий выводы для подключения источника импульсного сигнала и нагрузки, соответственно, а также дифференцирующие цепи, диоды и инверторы, выполнено в виде N блоков, вход первого из которых соединен с входным выводом, выход последнего - с выходным выводом, а выход каждого предыдующего - с входом последующего, причем каждый блок включает дифференцирующую цепь, включенную между его входом и указанным общим выводом, выход которой через первый диод соединен с первым входом дополнительно введенной в каждой из блоков схемы ИЛИ, а через второй диод с входом инвертора, выходом соединенного с вторым входом схемы ИЛИ, выход которого образует выход блока. Постоянная времени дифференцирующей цепи удовлетворяет условию, при котором

0,5 ги

ги -

UIQ

U(1)где т ц -постоянная времени дифференцирующей цепи;

- длительность импульса на входе дифференцирующей цепи;

U(1), U(o) - напряжения логической единицы и логического нуля схемы ИЛИ соответствующего блока.

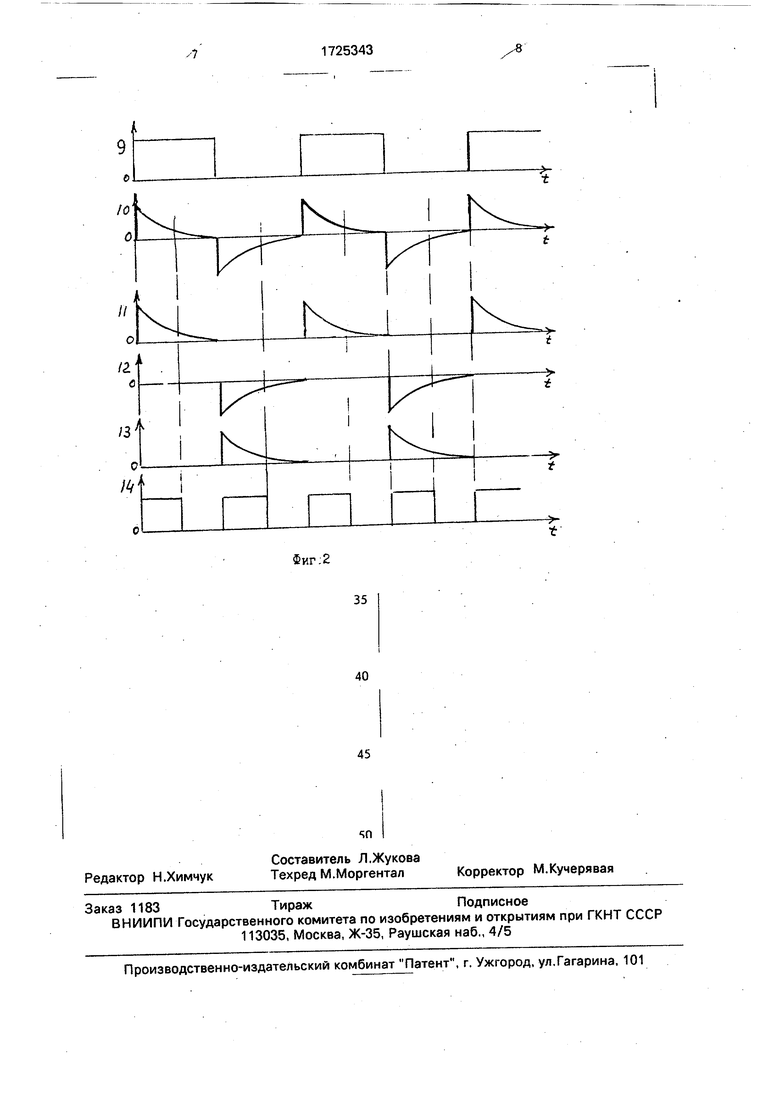

На фиг. 1 изображена функциональная схема двоичного умножителя частоты; на фиг. 2 - эпюры напряжений, поясняющие работу двоичного умножителя.

Двоичный умножитель частоты состоит из N блоков. Каждый блок включает дифференцирующую цепь, состоящую из конденсатора 1 и резистора 2, диодов 3 и 4, инвертор, включающий транзистор 5 и резистор 6 и схему ИЛИ 7. В каждом блоке дво- ичного умножителя частоты вход дифференцирующей цепи соединяют с источником импульсного напряжения, подле- жающего умножению, выход к двум диодам 3 и 4, служащих для передачи положительной полярности продифференцированного входного сигнала на первый вход схемы ИЛИ и отрицательного продифференцированного сигнала на вход инвертора, собранного, на полевом транзисторе 5 и резисторе 6 в цепи истока, Выход первого диода 3 соединен с первым входом схемы ИЛИ 7, а выход второго диода 4 - с входом инвертора. Выход инвертора соединен с вторым входом схемы ИЛИ 7.

Двоичный умножитель частоты работает следующим образом.

На вход дифференцирующей цепи подают последовательность прямоугольных импульсов со скважностью два (меандр) (эпюра 9, на фиг. 2). Если для умножения выбран синусоидальный сигнал, то он предварительно ограничивается или подается на компаратор с нулевым уровнем опорного напряжения. На выходе дифференцирующей цепи получаем импульсы положительной и отрицательной полярности (эпюра 10 на фиг. 2), положительные импульсы передаются через диод 3 на первый вход логической схемы ИЛИ 7 (эпюра 11 на фиг. 2). Длительность выходного импульса на выходе схемы ИЛИ 7 определяется временем превышения дифференциальным импульсом на первом входе порога срабатывания схемы ИЛИ; Для получения на выходе схемы ИЛИ импульсов длительностью в два раза меньше входного импульса, постоянная времени дифференцирующей цепи выбирается из равенства

-г - ° 5Ги

и(1)

где Гц -постоянная времени дифференцирующей цепи;

т и -длительность импульса на входе дифференцирующей цепи;

U(i), U(o) - напряжение логической единицы и логического нуля логической схемы ИЛИ выбранной серии.

0

5

0

5

0

5

Формула изобретения

1.Двоичный умножитель частоты, содержащий входной, выходной и общий выводы для подключения источника импульсного сигнала и нагрузки, соответственно, в также дифференцирующие цепи, диоды и инверторы, отличающийся тем, что, с целью повышения стабильности амплитуды выходного сигнала и надежности, он выполнен в виде N блоков, вход переого из которых соединен с входным выводом, выход последнего - с выходным выводом, а выход каждого преды дующего - с входом последующего, причем каждый блок включает дифференцирующую цепь, включенную между его входом и указанным об- щим выводом, выход которой через первый диод соединен с первым входом дополнительно введенной в каждый из блоков схемы ИЛИ, а через второй диод - с входом инвертора, выходом соединенного с вторым входом схемы ИЛИ, выход которой образует выход блока.

2.Умножитель поп. 1,отличающийся тем, что постоянная Гц времени дифференцирующей цепи удовлетворяет условию, при котором

0,5 ги

In

г и , л U ( о )

U(i)

где Ти - длительность импульса на входе дифференцирующей цепи;

U(i), U(o) - напряжение логической единицы и логического нуля схемы ИЛИ соответствующего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1978 |

|

SU767950A1 |

| ИМПУЛЬСНЫЙ РАДИОЛОКАТОР | 1985 |

|

SU1840927A1 |

| Преобразователь частоты | 1983 |

|

SU1201988A1 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

| Устройство для контроля пламени | 1986 |

|

SU1322017A2 |

| Умножитель частоты | 1981 |

|

SU1001115A1 |

| Устройство для контроля времени выключения тиристоров | 1990 |

|

SU1725316A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Преобразователь постоянного напряжения в постоянное | 1989 |

|

SU1713057A1 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1981 |

|

SU978077A1 |

Изобретение относится к электротехнике и может быть использовано в устройствах автоматики и измерительной техники для умножения частоты сигналов и повышения разрешающей способности измерительных приборов. Цель изобретения - повышение стабильности амплитуды выходного сигнала и надежности. Двоичный умножитель частоты состоит из четырех идентичных блоков. Каждый блок включает дифференцирующую цепь из конденсатора 1 и резистора 2, диоды 3 и 4, инвертор, состоящий из полевого транзистора 5 и резистора 6 и схемы ИЛИ 7. В каждом блоке вход дифференцирующей цепи соединен с источником импульсного напряжения, подлежающего умножению, а выход - с диодами 3, 4, служащими для передачи положительной полярности продифференцированного входного сигнала на первый вход схемы ИЛ И 7 и отрицательного продифференцированного сигнала - на вход инвертора, собранного на полевом транзисторе 5 и резисторе 6 в цепи истока. Выход диода 3 соединен с первым входом схемы ИЛИ, а выход диода 4 - с входом инвертора. Выход инвертора соединен с вторым входом схемы ИЛИ 7. За счет исключения катушек индук- тивностей достигается высокая стабильность по амплитуде, которая определяется стабильностью напряжения источника питания схемы умножения. Стабильность по частоте обеспечивается жесткой синхронизацией по фронту и срезу импульсов периодического сигнала, подлежащего умножению. Надежность обеспечивается возможностью использования типовых унифицированных элементов. 1 з.п.ф-лы, 2 ил. & Ё

| Умножитель частоты | 1984 |

|

SU1201986A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1972 |

|

SU429503A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-07—Публикация

1990-02-14—Подача