Изобретение относится к электро- texHHKe, в частности к преобразователям параметров электрической энергии при одновременной их стабилиза- |ции, и может быть использовано при про ектировании источников вторичного электропитания радиоэлектронной аппаратуры небольшой мощности (до 20 Вт) и напряжении первичной сети В постоянного тока, а именно в слу- чаях повышенных требований к КПД в процессе преобразования и стабилизации.

Целью изобретения является повышение КПД, а также исключение сквозных токов в транзисторах силового инвертора и стабилизация выходного напряжения при изменении тока нагрузки или стабилизация выходного тока.

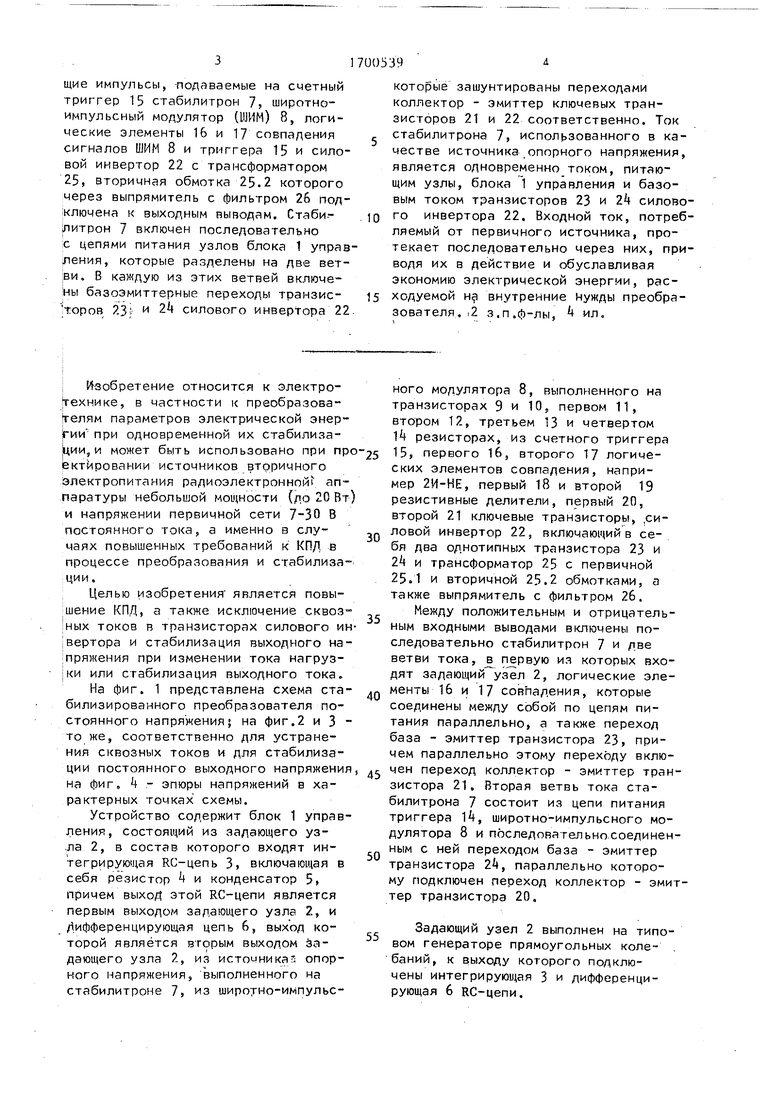

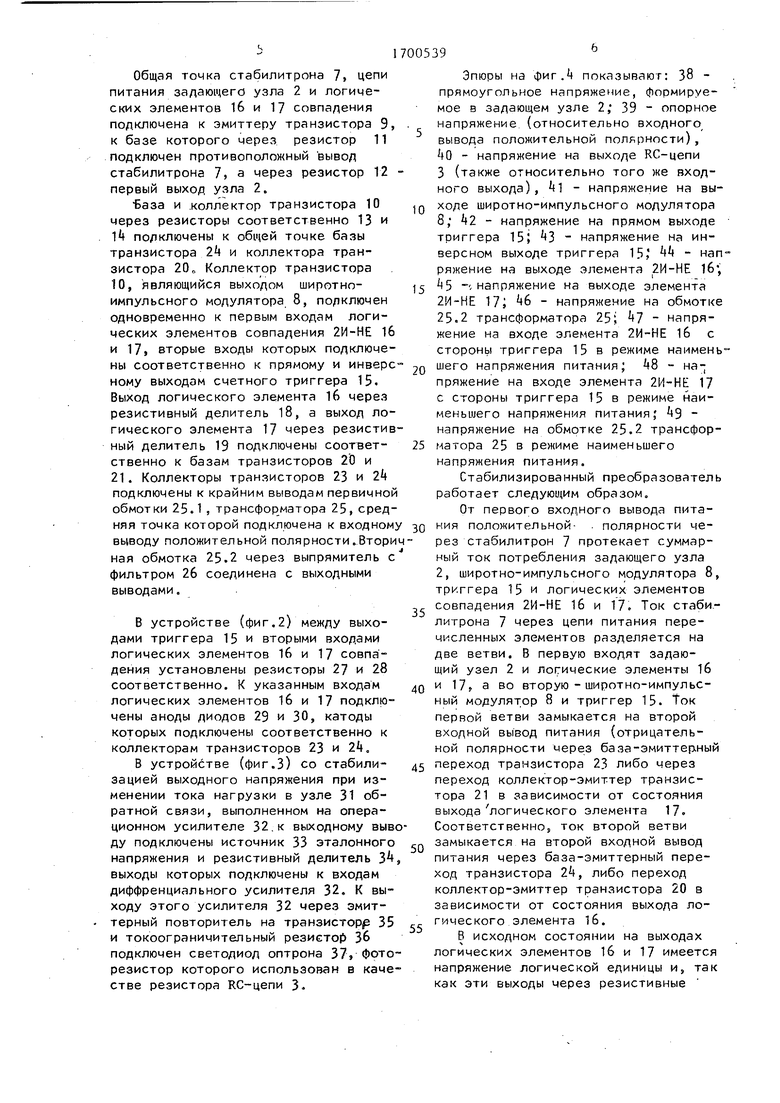

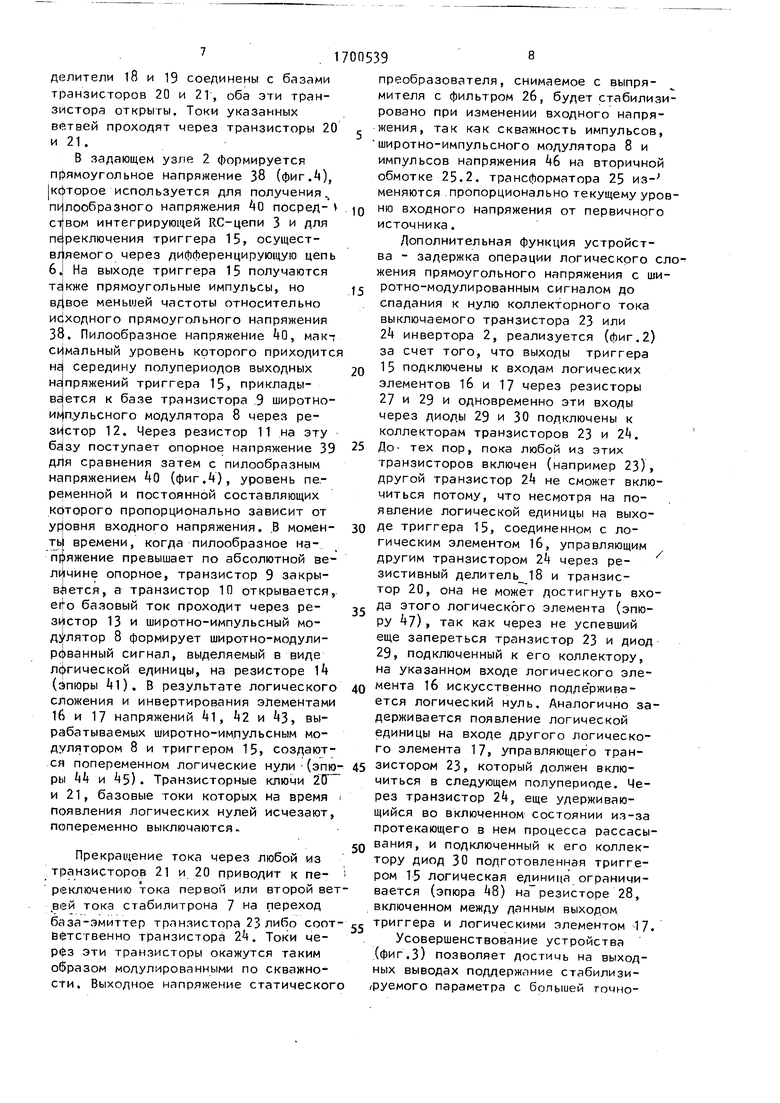

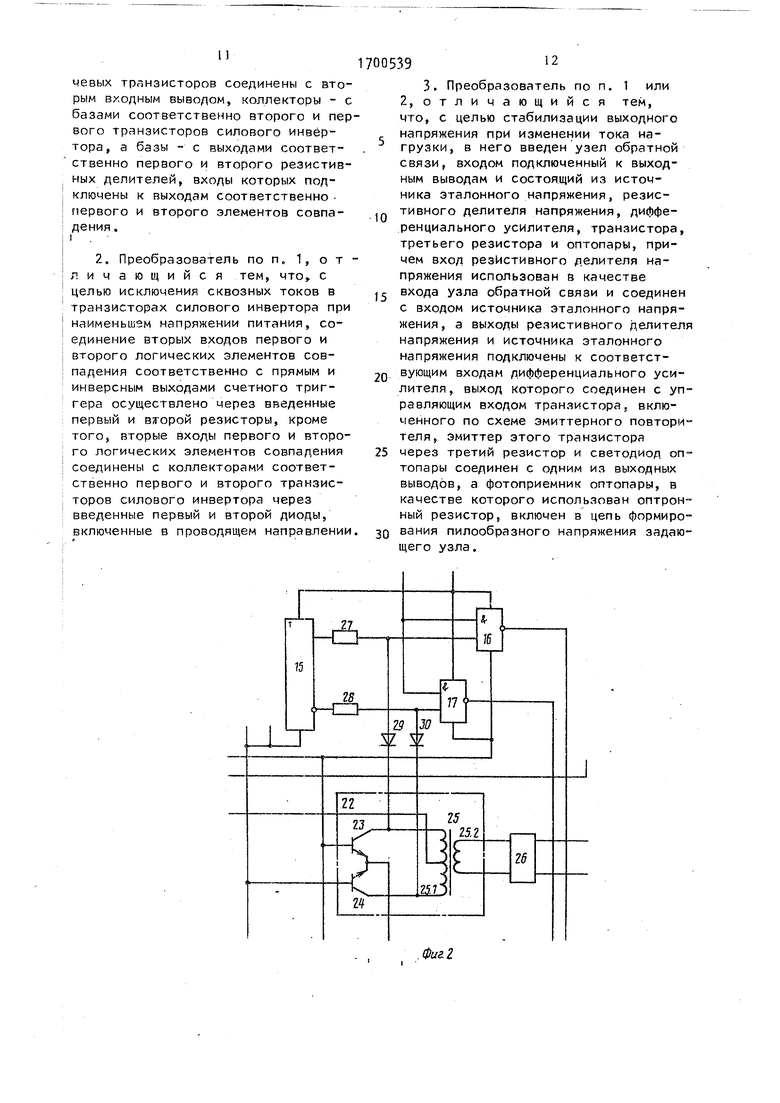

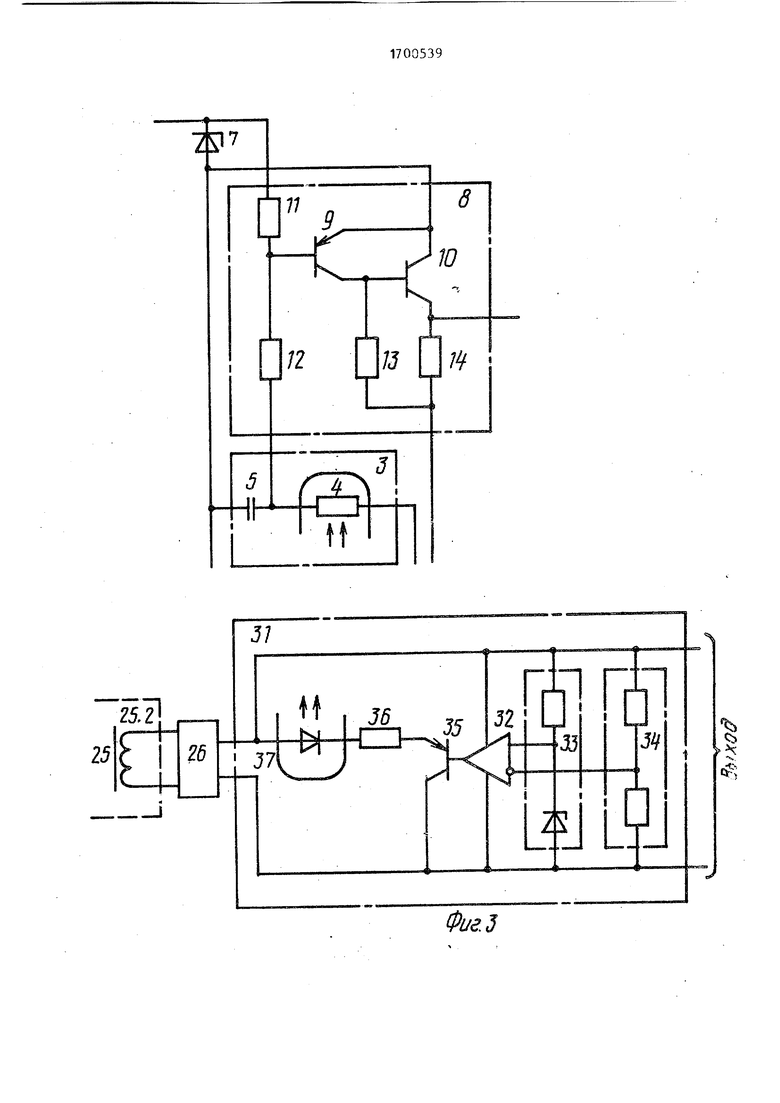

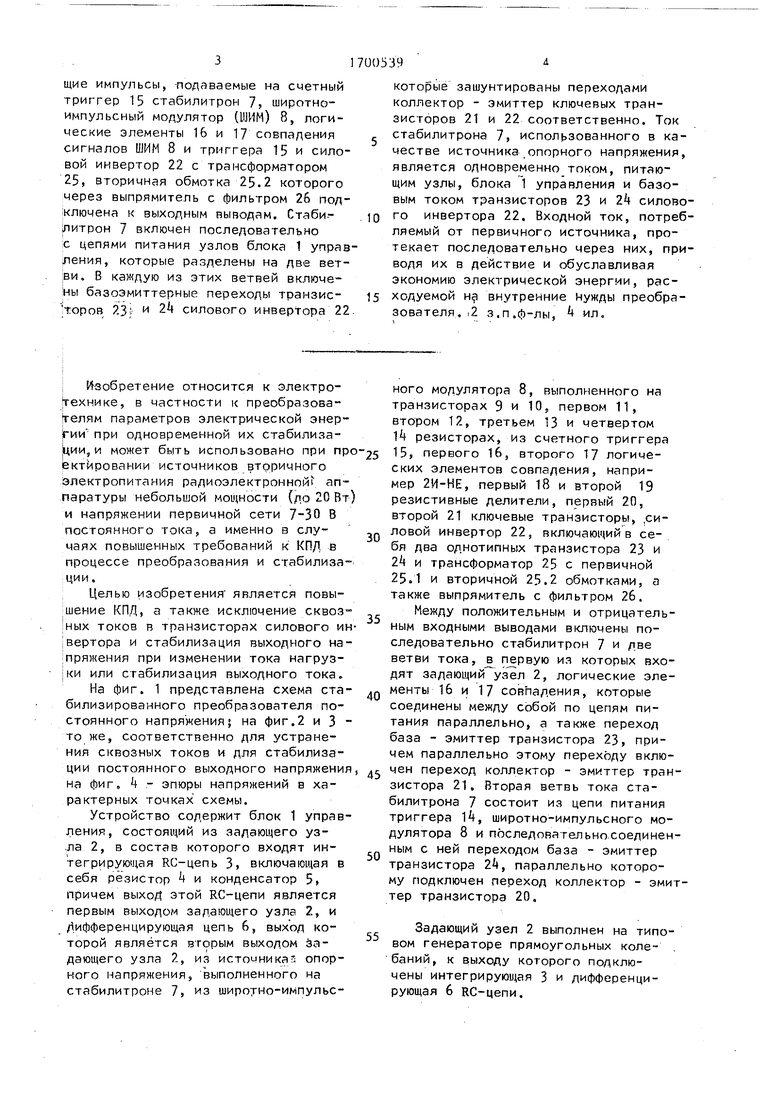

На фиг. 1 представлена схема ста- билизированного преобразователя постоянного напряжения; на фиг.2 и 3 то же, соответственно для устранения сквозных токов и для стабилизации постоянного выходного напряжения на Лиг. 4 - эпюры напряжений в характерных точках схемы.

Устройство содержит блок 1 управления, состоящий из задающего узла 2, в состав которого входят интегрирующая RC-цепь З, включающая в себя резистор 4 и конденсатор 5, причем выхоД этой RC-цепи является первым выходом задающего узла 2, и Дифференцирующая цепь 6, выход которой является вторым выходом задающего узла 2, из источника опорного напряжения, выполненного на стабилитроне 7, из широтно-импульс5

ного модулятора 8, выполненного на транзисторах 9 и 10, первом 11, втором 12, третьем 3 и четвертом 14 резисторах, из счетного триггера 15, первого 16, второго 17 логических элементов совпадения, например 2И-НЕ, первый 18 и второй 19 резистивные делители, первый 20, второй 21 ключевые транзисторы, .силовой инвертор 22, включающий в себя два однотипных транзистора 23 и 2k и трансформатор 25 с первичной 25.1 и вторичной 25.2 обмотками, а также выпрямитель с фильтром 26.

Между положительным и отрицательным входными выводами включены последовательно стабилитрон 7 и две ветви тока, в первую из которых входят задающий узел 2, логические элементы 16 и 17 совпадения, которые соединены между собой по цепям питания параллельно, а также переход база - эмиттер транзистора 23, причем параллельно этому переходу включен переход коллектор - эмиттер транзистора 21. Вторая ветвь тока стабилитрона 7 состоит из цепи питания триггера 14, широтно-импульсного модулятора 8 и последовательно соединенным с ней переходом база - эмиттер транзистора 24, параллельно которому подключен переход коллектор - эмиттер транзистора 20.

Задающий узел 2 выполнен на типовом генераторе прямоугольных колебаний, к выходу которого подключены интегрирующая 3 и дифференцирующая 6 RC-цепи.

Общая точка стабилитрона 7 цепи питания задающего узла 2 и логических элементов 16 и 17 совпадения подключена к эмиттеру транзистора 9, к базе которого через резистор 11 подключен противоположный вывод стабилитрона 7, а через резистор 12 первый выход узла 2.

База и коллектор транзистора 10 через резисторы соответственно 13 и подключены к общей точке базы транзистора 2k и коллектора транзистора 20о Коллектор транзистора 10, являющийся выходом широтно- импульсного модулятора 8, подключен одновременно к первым входам логических элементов совпадения 2И-НЕ 16 и 17 вторые входы которых подключены соответственно к прямому и инверсному выходам счетного триггера 15. Выход логического элемента 16 через резистивный делитель 18, а выход логического элемента 17 через резистивный делитель 19 подключены соответственно к базам транзисторов 20 и 21. Коллекторы транзисторов 23 и 2k подключены к крайним выводам первичной обмотки 25.1 , трансформатора 25, средняя точка которой подключена к входному выводу положительной полярности.Втори ная обмотка 25.2 через выпрямитель с фильтром 26 соединена с выходными выводами.

В устройстве (фиг.2) между выходами триггера 15 и вторыми входами логических элементов 16 и 17 совпадения установлены резисторы 27 и 28 соответственно. К указанным входам логических элементов 16 и 17 подключены аноды диодов 29 и 30, катоды которых подключены соответственно к коллекторам транзисторов 23 и 2k.

В устройстве (фиг.З) со стабилизацией выходного напряжения при изменении тока нагрузки в узле 31 обратной связи, выполненном на операционном усилителе 32 к выходному выводу подключены источник 33 эталонного напряжения и резистивный делитель 3 выходы которых подключены к входам диффренциального усилителя 32. К выходу этого усилителя 32 через эмит- терный повторитель на транзисторр 35 и токоограничительный резистор 36 подключен светодиод оптрона 37 фоторезистор которого использован в качестве резистора RC-цепи З.

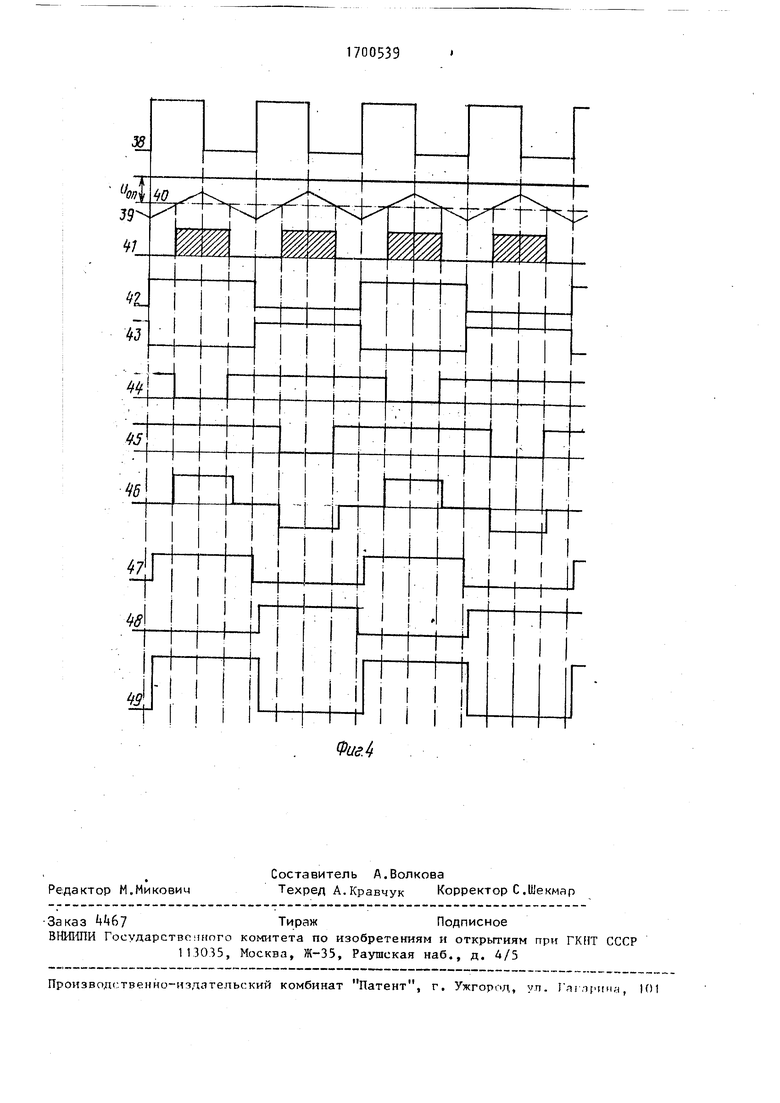

Эпюры на фиг.k показывают: 38 - прямоугольное напряжение, формируемое в задающем узле 2; 39 - опорное напряжение (относительно входного вывода положительной полярности), kQ - напряжение на выходе RC-цепи 3 (также относительно того же входного выхода), kl - напряжение на выQ ходе широтно-импульсного модулятора 8; k2 - напряжение на прямом выходе тоиггера 15} 3 - напряжение на инверсном выходе триггера 15, kk - напряжение на выходе элемента 2И-НЕ 16,

5 4 5 -. напряжение на выходе элемента 2И-НЕ 17; 46 - напряжение на обмотке 25.2 трансформатора 25; kj - напряжение на входе элемента 2И-НЕ 16 с стороны триггера 15 в режиме наименьшего напряжения питания; 48 - напряжение на входе элемента 2И-НЕ 17 с стороны триггера 15 в режиме наименьшего напряжения питания; 49 - напряжение на обмотке 25.2 трансформатора 25 в режиме наименьшего напряжения питания.

Стабилизированный преобразователь работает следующим образом.

От первого входного вывода питао ния положительной полярности через стабилитрон 7 протекает суммарный ток потребления задающего узла 2, широтно-импульсного модулятора 8, триггера 15 и логических элементов совпадения 2И-НЕ 16 и 17. Ток стабилитрона 7 через цепи питания перечисленных элементов разделяется на две ветви. В первую входят задающий узел 2 и логические элементы 16

0 и 17. а во вторую - широтно-импульс- ный модулятор 8 и триггер 15. Ток первой ветви замыкается на второй входной вывод питания (отрицательной полярности через база-эмиттер.ный

5 переход транзистора 23 либо иерез переход коллектор-эмиттер транзистора 21 в зависимости от состояния

0

5

5

выхода логического элемента 17. Соответственно5 ток второй ветви замыкается на второй входной вывод питания через база-эмиттерный переход транзистора 2k, либо переход коллектор-эмиттер транзистора 20 в зависимости от состояния выхода логического элемента 16.

В исходном состоянии на выходах логических элементов 16 и 17 имеется напряжение логической единицы и, так как эти выходы через резистивные

делители 18 и 19 соединены с базами транзисторов 20 и 21, оба эти транзистора открыты. Токи указанных ветвей проходят через транзисторы 20 и 21.

В задающем узле 2 формируется прямоугольное напряжение 38 (фиг.А), которое используется для получения „, пилообразного напряжения kG посреД- ством интегрирующей RC-цепи З и для переключения триггера 15, осуществляемого через дифференцирующую цепь 6 На выходе триггера 15 получаются та;юке прямоугольные импульсы, но меньшей частоты относительно походного прямоугольного напряжения 38. Пилообразное напряжение 0, макт сИмальный уровень которого приходитс не середину полупериодов выходных напряжений триггера 15, прикладывается к базе транзистора 9 широтно- икпульсного модулятора 8 через резистор 12. Через резистор 11 на эту базу поступает опорное напряжение 39 дЛя сравнения затем с пилообразным напряжением 40 (фиг.), уровень переменной и постоянной составляющих которого пропорционально зависит от входного напряжения. В моменты времени, когда пилообразное напряжение превышает по абсолютной ве- опорное, транзистор 9 закры- , а транзистор 10 открывается, его базовый ток проходит через резистор 13 и широтно-импульсный модулятор 8 формирует широтно-модули- рфванный сигнал, выделяемый в виде лфгической единицы, на резисторе 1 (эпюры М). В результате логического сложения и инвертирования элементами 16 и 17 напряжений А1, 2 и A3, вырабатываемых широтно-импульсным модулятором 8 и триггером 15 создаются попеременном логические нули (эпю ры kk и 5) . Транзисторные ключи 20 и 21, базовые токи которых на время появления логических нулей исчезают попеременно выключаются.

Дополнительная функция устройства - задержка операции логического с жения прямоугольного напряжения с ши ротно-модулированным сигналом до спадания к нулю коллекторного тока выключаемого транзистора 23 или 2k инвертора 2, реализуется (йиг.2) за счет того, что выходы триггера 15 подключены к входам логических элементов 16 и 17 через резисторы 27 и 29 и одновременно эти входы через диоды 29 и 30 подключены к коллекторам транзисторов 23 и 2k. До- тех пор, пока любой из этих транзисторов включен (например 23), другой транзистор 2k не сможет включиться потому, что несмотря на появление логической единицы на выходе триггера 15, соединенном с логическим элементом 16, управляющим другим транзистором 24 через ре- зистивный делитель 18 и транзистор 20, она не может достигнуть входа этого логического элемента (эпю- РУ 7), так как через не успевший еще запереться транзистор 23 и диод 29, подключенный к его коллектору, на указанном входе логического элемента 16 искусственно подде ржива- ется логический нуль. Аналогично задерживается появление логической единицы на входе другого логического элемента 17, управляющего транзистором 23, который должен включиться в следующем полупериоде. Через транзистор 2k, еще удерживающийся во включенном состоянии из-за протекающего в нем процесса рассасы- CQ вания, и подключенный к его коллектору диод 30 подготовленная триггером 15 логическая единица ограничивается (эпюра kQ) на резисторе 28, включенном между данным выходом

Прекращение тока через любой из транзисторов 21 и 20 приводит к пе- реключению тока первой или второй вет- ,вей тока стабилитрона 7 на переход база-эмиттер транзистора 23 либо соот- 55 триггера и логическими элементом 17. вфтсгвенно транзистора 2k. Токи че- Усовершенствование устройства р$з эти транзисторы окажутся таким образом модулированными по скважности. Выходное напряжение статического

(фиг.З) позволяет достичь на выходных выводах поддержание стабилизируемого параметра с большей томно

5

0

5

45

преобразователя, снимаемое с выпрямителя с фильтром 26, будет стабилизировано при изменении входного напряжения, так как скважность импульсов, широтно-импульсного модулятора 8 и импульсов напряжения k6 на вторичной обмотке 25.2. трансформатора 25 из-; меняются пропорционально текущему уровню входного напряжения от первичного источника.

Дополнительная функция устройства - задержка операции логического сложения прямоугольного напряжения с ши- ротно-модулированным сигналом до спадания к нулю коллекторного тока выключаемого транзистора 23 или 2k инвертора 2, реализуется (йиг.2) за счет того, что выходы триггера 15 подключены к входам логических элементов 16 и 17 через резисторы 27 и 29 и одновременно эти входы через диоды 29 и 30 подключены к коллекторам транзисторов 23 и 2k. До- тех пор, пока любой из этих транзисторов включен (например 23), другой транзистор 2k не сможет включиться потому, что несмотря на появление логической единицы на выходе триггера 15, соединенном с логическим элементом 16, управляющим другим транзистором 24 через ре- зистивный делитель 18 и транзистор 20, она не может достигнуть входа этого логического элемента (эпю- РУ 7), так как через не успевший еще запереться транзистор 23 и диод 29, подключенный к его коллектору, на указанном входе логического элемента 16 искусственно подде ржива- ется логический нуль. Аналогично задерживается появление логической единицы на входе другого логического элемента 17, управляющего транзистором 23, который должен включиться в следующем полупериоде. Через транзистор 2k, еще удерживающийся во включенном состоянии из-за протекающего в нем процесса рассасы- CQ вания, и подключенный к его коллектору диод 30 подготовленная триггером 15 логическая единица ограничивается (эпюра kQ) на резисторе 28, включенном между данным выходом

30

35

40

55 триггера и логическими элементом 17. Усовершенствование устройства

триггера и логическими элементом 17. Усовершенствование устройства

(фиг.З) позволяет достичь на выходных выводах поддержание стабилизируемого параметра с большей томно

стью при воздействии на него других дестабилизирующих факторов (например, тока нагрузки при стабилизации напряжения, или наоборот, напряжения при стабилизации тока). В примере конкретной реализации (фиг.З) стабилизируется напряжение. Здесь действует обратная связь с нагрузки. С помощью узла 31 стабилизируемый параметр сравнивается с заданным его значением и производится дополнительно к описанным процессам управление фоторезистором k оптрона 37 проводимость которого зависит от степени отклонения выходного напряжения от номинального значения.

В предлагаемом преобразователе экономится электрическая энергия, расходуемая на внутренние нужды: получение опорного и пилообразного напряжения, придание последнему амплитудной зависимости от уровня входного напряжения, Формирование широтно-модулироваиного сигнала с скважностью, пропорциональной входному напряжению, поочередной коммутации в цепь тока источника опорного напряжения (стабилитрона) управляю- шей цепи (база-эмиттерного перехода) одного из транзисторов двухтактного силового инвертора - достигается общим током источника опорного напряжения (стабилитрона).

Устранение сквозных токов в транзисторах силового инвертора также достигается без дополнительных затрат электрической энергии. Автоматически выполняемые операции задержки логического сложения прямоугольны напряжений с широтно-модулированны- ми сигналами производятся пассивными элементами (резисторы 27 и 28, диоды 29 и 30 совместно с транзисторами силового инвертора) в процессе их работы по основному назначению.

При стабилизации выходного параметра с использованием обратной связи с нагрузки достигается дополнительное полезное свойство: улучшаются динамические характеристики при всплесках и провалах входного напряжения. В самом деле при изменении входного напряжения отслеживается ширина управляющих импульсов за счет непосредственного изменения амплитуды пилообразного напряжения без участия обратной связи, благодаря

5

0

5

0

0

5

5

0

5

чему устраняется задержка регулирования из-за инерционности элементов, сходящих в контур регулирования (главным образом в фильтре).

Формула изобретения

1. Стабилизированный преобразователь постоянного напряжения, содержащий блок управления, состоящий из задающего узла, формирующего пилообразное напряжение на первом выходе и синхронизирующие импульсы на втором выходе, из счетного триггера, первого и второго логических элементов совпадения, из источника опорного напряжения и из широтно-импульсного модулятора, причем входы широтно-импульсного модулятора соединены соответственно с источником опорного напряжения и первым выходом задающего узла, а выход подключен к первым входам первого и второго логических элементов совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами счетного триггера, входом подключенного к второму выходу задающего узла, и силовой инвертор, включающий в себя первый и второй транзисторы и трансформатор, первичная обмотка которого крайними выводами подключена к коллекторам транзисторов силового инвертора, средняя точка первичной обмотки и эмиттеры транзисторов сило-, вого инвертора подключены соответственно к первому и второму входным выводам, а вторичная обмотка через выпрямитель и фильтр соединена с выходными выводами.отличающийся тем, что, с целью повышения КПЛ, в него введены первый и второй ключевые транзисторы того же типа проводимости, что и транзисторы силового инвертора, и первый и второй резистивные делители, а в качестве источника опорного напряжения использован стабилитрон, причем стабилитрон включен между первым входным выводом и цепями питания остальных узлов блока управления, которые разделены на две ветви, каждая из которых соединена с вторым входным выводом через базоэмиттер- ный переход первого или второго тран- зисторов силового инвертора, при этом эмиттеры первого и второго клюЩ

п

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1408425A1 |

| Стабилизированный преобразователь постоянного напряжения | 1990 |

|

SU1728950A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1980 |

|

SU904148A2 |

| Управляемый широтно-импульсный модулятор | 1987 |

|

SU1614108A1 |

| Импульсный стабилизированный преобразователь напряжения постоянного тока | 1986 |

|

SU1339522A1 |

| Течеискатель | 1986 |

|

SU1401309A1 |

Изобретение относится к электротехнике, в частности к технике маломощных преобразователей электрической энергии, и может быть использовано в качестве источника вторичного электропитания. Цель изобретения - повышение КПД. В преобразователе имеется блок 1 управления с задающим узлом 2, формирующим пилообразное напряжение и синхронизирую

АГ

ЈГ

I I

ш ш

ZЈ

ЈЈ

6escoЈi

/Г

Z

9Ј

И

iTE

| Стабилизированный преобразователь постоянного напряжения | 1980 |

|

SU936286A1 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| , Авторское свидетельство СССР № 479Ю1, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-12-23—Публикация

1989-10-09—Подача