(54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1982 |

|

SU1083353A1 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| Триггерное устройство | 1981 |

|

SU970649A1 |

| УСТРОЙСТВО КОМПЛЕКСНОЙ ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1996 |

|

RU2117372C1 |

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| Формирователь импульсов | 1979 |

|

SU864523A1 |

| Устройство для задержки импульсов | 1981 |

|

SU1046924A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| УСТРОЙСТВО КОМПЛЕКСНОЙ ЗАЩИТЫ ЭЛЕКТРОТЕХНИЧЕСКОЙ СИСТЕМЫ | 1995 |

|

RU2115986C1 |

| Устройство сравнения | 1979 |

|

SU845277A1 |

, ;; ;.; i -. ; Изобретение относится к импульс.ной технике, а именно к задержкам, испЬльзуеиьш в различных логических схемах устройств автоматики, Н8П| Имер,-в устройствах для управлений; Переключением реверсивного вентидм р го преобразователя с раздельным ynfiaB лением. Известно устройство, выполнйкччее функцию задержки на появление вьЕКОД т ного сигнала и содержащее входной HH вертор, параллельно соединенные кон денсатор и резистор, подключенные, к входу RS-триггераП 1.. . В этом устройстве время заряда . конденсатора задержки должно быть, ми нимальньм, так как является временем восстановления схемы устройства. Поэтому величина ограничивающего резистора должна быть выбрана по условиям максимально допустимой параллельной нагрузки логического элемент а.- И-НЕ. Уровень напряжения , до которого заряжается конденсатор задержки, заг: висит от параметров внутренних элементов входного инвертора, ограничивающго резистора, параллельно соединенных резистора и конденсатора. При неизменных параметрах ограничивающего резистора и RS-цепи параметры внутренних элементов входного инвертора могут отличаться для задержек, используемых при изготовлении серийных устройств автоматики, что приводит к заряду конденсатора до различных уровней напряжения.. Время задержки на появление выходного сигнала зависит от .параметров резистора и конденсатора, соединенных параллельно и подключенных ко входу Я5-тоигге.ра, и уровня напряжения на конденсаторе к моменту его эазряда через резистор. Поскольку уровень напряжения может быть различньм, . различным будет и воемя задержки на появление выходного сигнала. Это снижает точность работы задержки на появление выходного сигнала на выхо де RS-триггера. Кроме того, подключение диода и ограничивающего резистора, величина которого .выбирается из условия допустимой параллельной нагрузки входного инвертора и достаточно велика, к выходу входного инвертора значительно увеличивает время восстановления схемы устройства задержки. Это ограничивает функционал ные возможности при использовании устройства задержки в схемах автоматики. Наиболее близким по технической сущности к изобретению является уст ройство для задержки импульсов, сод жащее выходной RS-триггер на двух элементах И-НЕ, инвертор, выход которого подключен к одному из входов RS-триггера, интегрирующую RC-цепь, выход которой подключен к входу инвертора и к другому входу RS-тригге ра, входной инвертор, выход которого подключен к входу интегрирующей RC-цепи, а также последовательную диодно-резистивную цепь, подключенную параллельно резистору интегрирующей RC-цепи, причем катод диода подключен к выходу входного инверто . Известное устройство выполняет ф кции задержки на появление и пропадание выходного сигнала на выходе RS-триггера. Врея заряда конденсатора до напряжения, уровень которого соответствует логинескому сигналу единицы на входах RS-триггера и .инвертора, зависит не толькй-от параметров интегрирующей RC-цепи, но также и от параметров внутренних эл ментов входного инвертора, построенного на элементе И-НЕ. В элементах И-НЕ внутренними элементами, влияющими на время конденсатора являются резистор, транзистор и диод. При массовом производстве интегральных микросхем неизбежен разбро параметров указанных элементов. Это в свою очередь, может привести при неизменных параметрах интегрирующей RC-цепи и задержках, используемых при изготовлении серийных устройств автоматики, к заряду конденсатора до различных уровней напряжения и при этом время заряда конденсатора также будет различным. Эт снижает точность работы задержки на пропадание выходного сигнгша на выходе RS-триггера. Время разряда конденсатора до напряжения, уровень которого соответствует логическому сигналу нуль на входах RS-триггера и инвертора зависит от параметров параллельно соединенных резистора и диодно-резистивной цепи, конденсатора и уровня напряжения на нем. Этот уровень напряжения, как было указано, может быть различным. Это также снижает точность работы задержки на появление выходного сигнала ня выходе RS-TOHrгера. Кроме того, параллельное соединение резистора и диодно-резистивной цепи создает трудности при настройке задержки и может привести к дополнительной неточности работы задержки на появление выходного сигнала.. К недостатку известного устройства следует также отнести одновременно подключение конденсатора интегрирующей RC-цепи ко входам RS-триггера и инвертора. Это приводит к дополнительной неточности работы задержки при разных порогах срабатывания и отпускания RS-тригрера и инвертора. Это объясняется тем, что логические сигналы, соответствующие единице и нулю, для разных элементов И-НЕ могут отличаться по уровню напряжения. Так, например, если уровень напряжения , соответствующий логическому сигналу единица на входе инвертора выше, чем на входе RS-триггера, то пропадание сигнала на основном выходе RS-триггера произойдет после появления сигнала логической единицы на инверсном выходе RS-триггера,и, следовательно, время задержки на пропадание выходного сигнала определяется внутренними параметрами инвертора. Это также снижает точность работы задержки на пропадание выходного сигнала. Если уровень напряжения, соответветствующий логическому сигналу единица на входе инвертора ниже,чем на входе RS-тpиггepaJ то одновременно на основном и инверсном выходах RS-триггера кратковременно появляются сигналы логической единицы. Это приводит к тому, что основной и инверсньй выходы RS-триггера не являются взаимно инверсными, что резко снижает функциональные возможности устройства.

Цель изобретения - повьппение точности задержки.

Указанная цель достигается тем. что в устройство, содержащее выходной К5-триггео на двух элементах И-НЕ, инвертор, выход которого подключен к одному из входов RS-триггера, КС-цепь, подключенную к другому входу RS-триггера, входной инвертор и диодно-резистивную цепь, подключенную .катодом диода к выходу входного инвертора, введен дополнительный диод, причем анод его соединен со средней точкой диодно-резистивной цепи, резистор которой подключен к шине питания, а катод-Дополнительного диода соединен с выходом RC-цепи, выполненной в виде параллельно соединенньк ре зистора и конденсатора, второй выход которой подключен к общей шине.

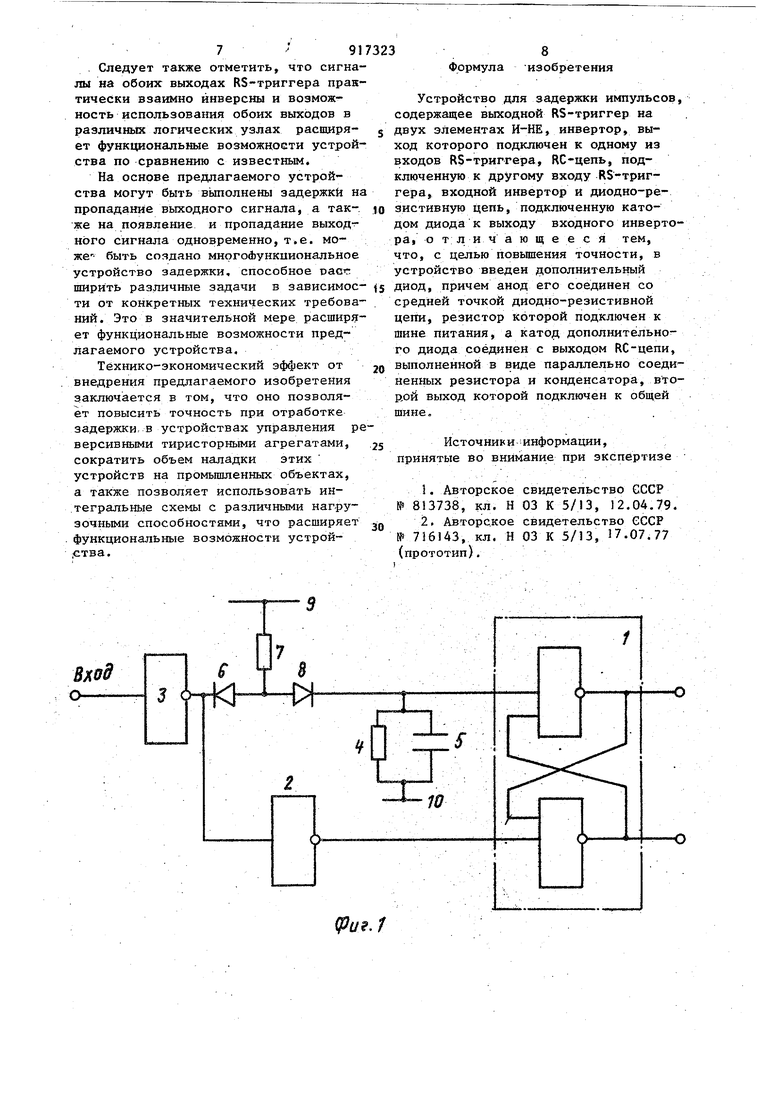

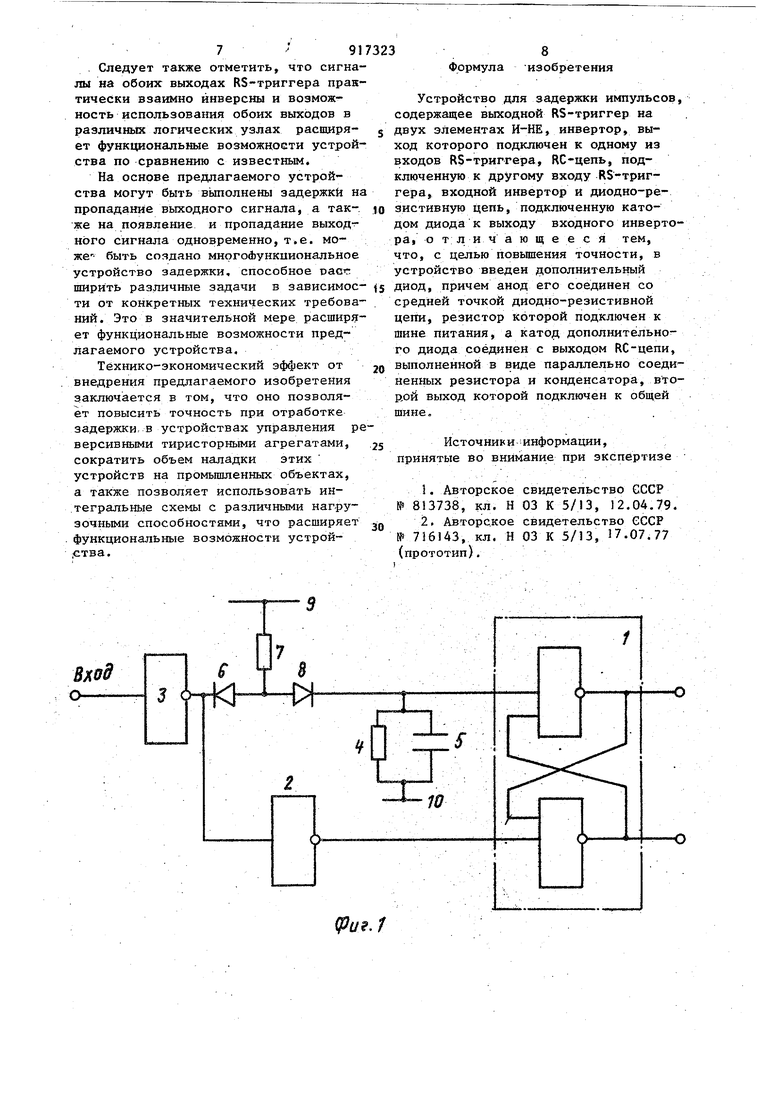

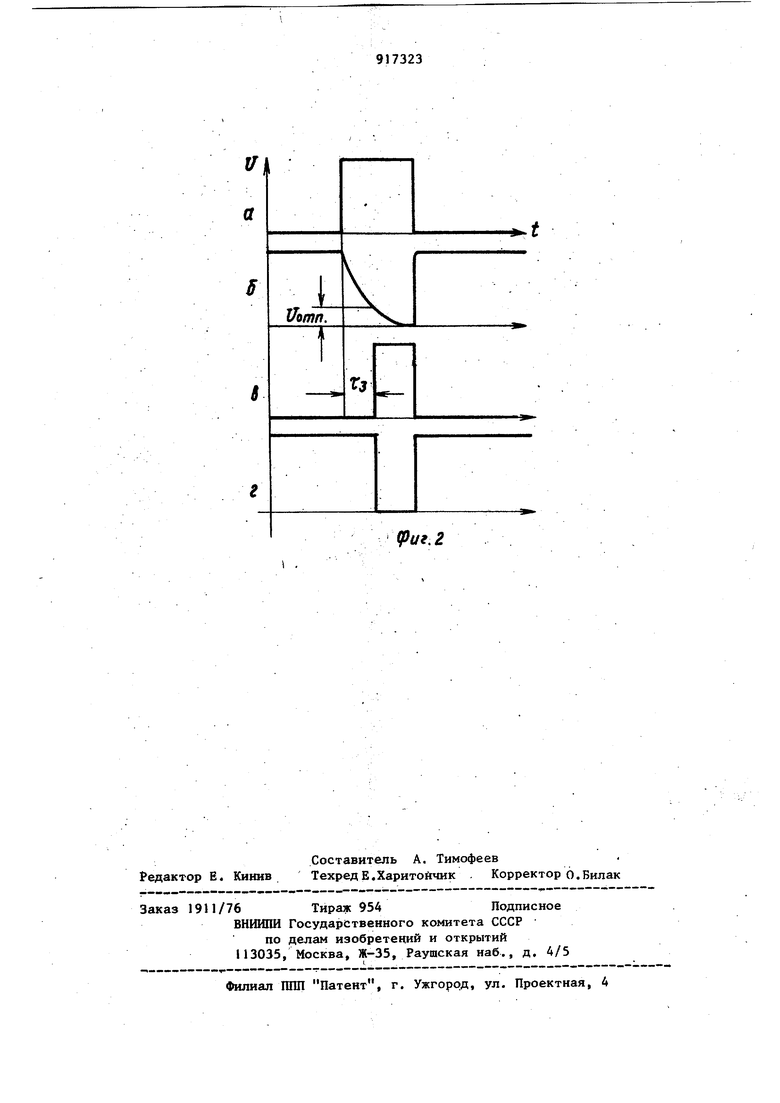

На фиг, 1 приведена принципиальная схема предлагаемого устройства; на фиг. 2 - временная диаграмма его работы.

Устройство содержит RS-триггер 1 на двух элементах И-НЕ, инвертор 2 и входной инвертор 3 на элементах И-НЁ, RC-цепь, состоящую из параллельно соединенш,гх резистора 4 и канденсатора 5, диодно-резистивную цепь, состоящую из диода 6 и резистора 7, дополнительный диод 8, шину 9 питания, общую шину 10.

Устройство выполняет функцию задержки на появление выходного сигнала и работаетследующим образом,

В исходном состоянии, когда входной сигнал равен нулю (фиг. 2 а), на первом выходе RS-триггера 1 (фиг.2 в ггрисутствует нулевой потенциал, а на втором выходе (фиг. 2 г) высокий потенциал. На выходе входного.инвертора 3 высокий потенциал запирает, диод 6 и конденсатор 5 заряжается по цепи: щина 9 питания, резистор 7, диод 8, практически до напряжения, источника питания. Постоянная времени заряда выбрана минимально возможной, т.е. резистор 7 выбран из условия допустимой последовательной йагрузки входного.инвертора ЭТО время заряда конденсатора 5 минимально возможное и не зависит от параметров внутренних элементов входного инвертора 3.

Входной сигнал положительной полярности (фиг. 2 а) изменяет состояние входного инвертора 3 и инвертов ра 2, в результате на выходе первого устанавливается нулевой потенциал, а на выходе второго высокий потенциал, Высокий потенциал на выходе инвертора 2 не изменяет состояния RS-триггера 1. В то же время нулевой потенциал на выходе входного инвертора 3 запирает дополцителышй диод 8 и открывает диод 6; в результате по цепи: шина 9 питания, резистор 7, диод 6, выход входного инвертора 3протекает ток, ограниченный резистором 7. Конденсатор 5 в это же время разряжается через резистор 4 по экспоненциальному закону (фиг. 2 б). Состояние RS-триггера 1 изменится в момент, когда напряжение на конденсаторе 5 снизится до величины соответствующей сигналу логического нуля для элемента И-НЕ RS-TOHrreoa 1, который изменит свое--состояние, в результа1е на первом выходе установится высокий потенциал (фиг.2 в), а на втором выходе низкий потенциал (фиг. 2 г).

После снятия входного сигнала устройство за короткий промежуток времени приходит в исходное состояние, так как на втором выходе RS-триггера высокий потенциал устанавливается практически мгновенно, а нулевой потенциал на первом выходе устанавливается, когда конденсатор 5 зарядится до напряжения соответствующего сигналу логической единицы на входе элемента И-НЕ RS-триггера.

Точность работы задержки при использовании различных логических элементов всерийном производстве устройств автоматики обеспечивается за счет постоянного уровня напряжения при заряде конденсатора , который соответствует -напряжению источника питания, так как ограничивающий резистор 7 значительно меньше резистора 4 RC-цепи, а также за счет предлагаемого подключения элементов задержки, в результате которого время задержки не зависит от внутренних параметров логического элемента .И-НЕ типа ТТЛ.

Точность работы задержки определяется лишь параметрами RC-цепи и уровнем напряжения соответствукндего сигналу логического нуля элемента И-НЕ RS-триггера, которые практически остаются неизменными. 7 91 Следует также отметить, что сигналы на обоих выходах RS-триггера практически взаимно инверсны и возможность использования обоих выходов в раэличньсс логических узлах расширяет функциональные возможности устройства по сравнению с известным. На основе предлагаемого устройства могут быть выполнены задержки на пропадание выходного сигнала, а также на появление и пропадание выходкого сигнала одновременно, т.е. може быть соядано мнргоЛункпиональное устройство задержки, способное pact: ширить различные задачи в зависимоети от конкретных технических требований. Это в значительной мере расширяет функциональные возможности предлагаемого устройства. Технико-экономический эффект от внедрения предлагаемого изобретения заключается в том, что оно позволяет повысить точность при отработке задержки в устройствах управления ре

версивными тиристорными агрегатами, сократить объем наладки этих устройств на промышленных объектах, а также позволяет использовать интегральные схемы с различными наг-ру3O4HbWH способностями, что расширяет функциональные возможности устройства.

Источники-; информации, принятые во внимание при экспертизе

№ 813738, кл. Н 03 К 5/13, 12.04.79.

Вхо

f

о--

о(ри.1

W

иг. 2

Авторы

Даты

1982-03-30—Публикация

1980-08-12—Подача