от

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемая линия задержки | 1984 |

|

SU1197068A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2229200C2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1985 |

|

SU1840083A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ШУМОПОДОБНОГО СИГНАЛА | 1975 |

|

SU1840645A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗОВОГО СДВИГА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2013016C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОДОВЫХ СЛОВАРЕЙ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2009 |

|

RU2439657C2 |

Изобретение относится к дискретной технике, может быть использовано в имитаторах помех для широкополосных систем связи и в устройствах поиска и слежения за задержкой широкополосного сигнала. Целью изобретения является расширение функциональных возможностей управляемой линии задержки, заключающееся в обеспечении управления задержкой неизвестной псевдослучайной последовательности, принимаемой от внешнего по отношению к линии задержки источника, имеющего известную среднюю скорость поступления информации. Цель достигается тем, что в управляемую линию задержки включены переключатель режима работы, блок выделения фронтов посылок, блок тактовой синхронизации, счетчик-делитель, первый и второй ключи. 5 ил.

Изобретение относится к дискретной технике и может быть использовано в имитаторах каналов и помех для широкополос- ных систем связи и является усовершенствованием известного устройства по авт.св. № 1197068.

Цель изобретения - расширение функциональных возможностей управляемой линии задержки, заключающееся в обеспечении управления задержкой псевдослучайной последовательности, принимаемой от внешнего по отношению к устройству задержки источника, имеющего известную среднюю скорость поступления информации.

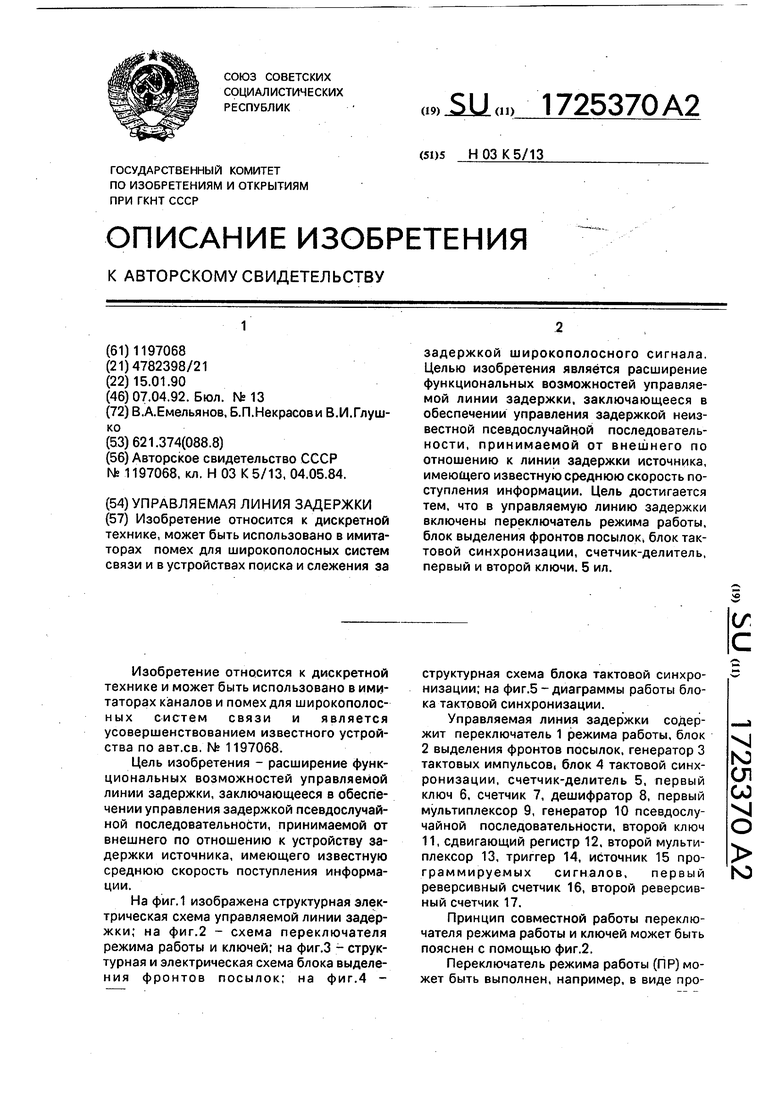

На фиг.1 изображена структурная электрическая схема управляемой линии задержки; на фиг.2 - схема переключателя режима работы и ключей; на фиг.З - структурная и электрическая схема блока выделения фронтов посылок; на фиг.4 структурная схема блока тактовой синхронизации; на фиг.5 - диаграммы работы блока тактовой синхронизации.

Управляемая линия задержки содержит переключатель 1 режима работы, блок 2 выделения фронтов посылок, генератор 3 тактовых импульсов, блок 4 тактовой синхронизации, счетчик-делитель 5, первый ключ 6, счетчик 7, дешифратор 8, первый мультиплексор 9, генератор 10 псевдослучайной последовательности, второй ключ 11, сдвигающий регистр 12, второй мультиплексор 13, триггер 14, источник 15 программируемых сигналов, первый реверсивный счетчик 16, второй реверсивный счетчик 17.

Принцип совместной работы переключателя режима работы и ключей может быть пояснен с помощью фиг.2.

Переключатель режима работы (ПР) может быть выполнен, например, в виде проVI

ND СЛ

СО

VI о

hO

стого двухпозиционного переключателя, ключи - в виде двух идентичных мультиплексоров, у которых в качестве информационных входов используются лишь входы Д2 и ДЗ. Входы Д2 и ДЗ соответствуют первому и второму входам ключей. Адресные входы мультиплексоров являются управляющими. Верхнее положение ПР соответствует режиму работы линии задержки от внешнего по отношению к ней источника псевдослучайной последовательности, нижнее положение переключателя режима работы - работе от внутреннего генератора псевдослучайной последовательности, т.е. соответствует работе прототипа. Если ПР работ находится в верхнем положении, то на управляющие входы ключей постоянно поступает двоичная комбинация 1 0, так потенциал высокого уровня от источника питания поступает на адресные входы А1 обоих мультиплексоров 6 и 11 (это соответствует подаче сигнала 1 на входе А1 и подаче сигнала О на входе А2), тем самым обеспечивается коммутация вторых входов ключей ДЗ. При этом информация, поступающая от внешнего по отношению к линии задержки источника и от блока тактовой синхронизации, коммутируется соответственно на сдвигающий регистр 12, на счетчик 7 и источник 15 программируемых сигналов, Если ПР 1 работы находится в нижнем положении, то потенциал высокого уровня поступает на выходы А2, напряжения на выходах А1 обоих мультиплексоров нет, что обеспечивает коммутацию первых входов Д2 ключей. При этом информация, поступающая к сдвигающему регистру 12 и одновременно к счетчику 7 и источнику 15 программируемых сигналов, коммутируется соответствен но от генератора 10 псевдослучайной последовательности и счетчика-делителя 5. Параллельное подключение управляющих входов ключей б и 11 к переключателю 1 режима работы обеспечивает их синхронную работу.

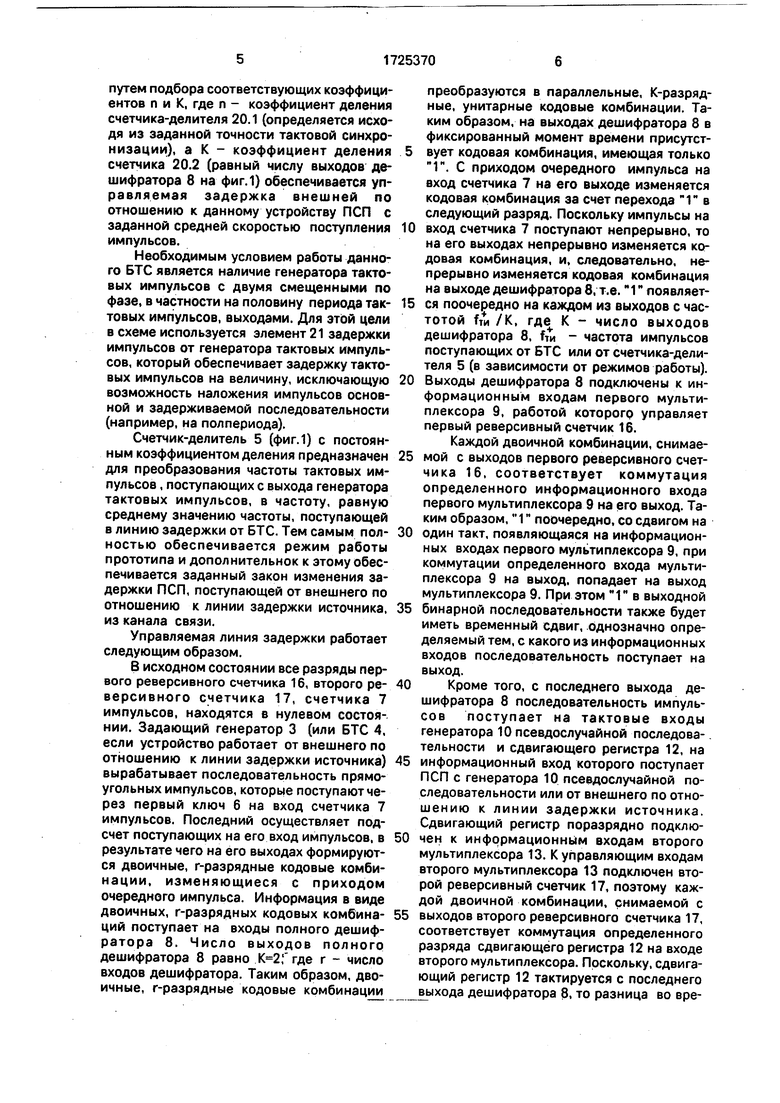

Принцип работы блока выделения фронтов посылок.

Блок выделения фронтов посылок (БВФ) предназначен для выделения значащих моментов импульсов, идущих от внешнего по отношению к линии задержки источника. Вариант структурной и электрической схемы БВФ показан на фиг.З. В исходном состоянии по выходам Д1 элемента приложены сигналы уровня 1, следовательно, на его выходе сигнал будет иметь уровень О. При поступлении перепада напряжения 0/1 срабатывает сначала элемент ДЗ, формируя передний фронт выходного импульса, затем появляется высокий потенциал на выходе Д1 элемента, который вызывает переключение выхода Д2 элемента. При этом на выходе Д2 элемента появляется сигнал уровня О, что приводит к

отклонению выхода ДЗ элемента и формированию заднего фронта выходного импульса. Длительность импульса на выходе схемы равна утроенной задержке срабатывания примененных инверторов.

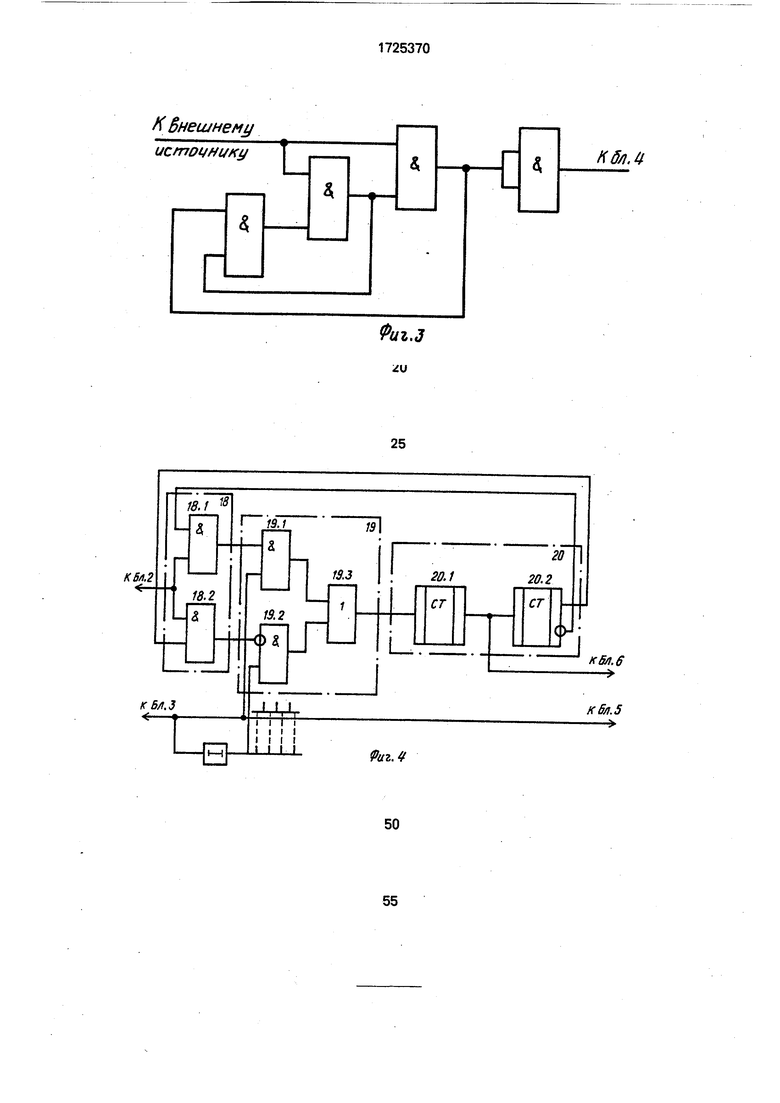

Вариант структурной схемы блока тактовой синхронизации (БТС) представлен на фиг.4.

БТС состоит из фазового дискриминатора 18, управляющего устройства 19, счетчика-делителя 20 и элемента 21 задержки.

Счетчик-делитель 20 состоит из двух счетчиков-делителей 20.1 и 20.2. С целью обеспечения нормальной работоспособности устройства, в схему блока 4 тактовой

синхронизации дополнительно введен счетчик-делитель 20.1 с коэффициентом деления п, В этом случае схема блока тактовой синхронизации обеспечивает нормальную работу, когда на один ее вход поступают

импульсы в характеристические моменты, определяемые fn - частотой поступления сигналов посылок внешней псевдослучайной последовательности (ПСП), а на другой ее вход поступают тактовые импульсы с частотой ттц fn K-n, где К - число выводов дешифратора 8, п - коэффициент деления счетчика-делителя 20.1, причем на выходе блока 4 вырабатывается сигнал с частотой f™ , где йнжекс + означает, что частота f™ ,

точно равна fn-К.

Принцип работы блока можно пояснить с помощью диаграмм, представленных на фиг.5.

Тактовые импульсы от генератора 3 тактовых импульсов через элементы И 19.2 и ИЛИ 19.3, поступают на вход первого счетчика-делителя 20.1 (диаграмма А на фиг.5), где происходит деление частоты f™ на п.

, На выходе счетчика-делителя 20.1 присутствуют импульсы с частотой f™ f™/n К fn Очиаграмма Б на фиг.5), где fn частота, соответствующая скорости поступления символов внешней ПСП.

Импульсы с частотой f™ поступают на вход блока (фиг.1) для обеспечения нормальной работы устройства задержки и на вход второго счетчика 20.2, где происходит деление частоты на К. То есть на прямом и

инверсном выходах счетчика 20.2 появляются импульсы с частотой (диаграмма В на фиг.5), равной средней скорости поступления символов внешней ПСП, т.е. f™/K fn, что обеспечивает надежную работу блока тактовой синхронизации. Следовательно,

путем подбора соответствующих коэффициентов п и К, где п - коэффициент деления счетчика-делителя 20.1 (определяется исходя из заданной точности тактовой синхронизации), а К - коэффициент деления счетчика 20.2 (равный числу выходов дешифратора 8 на фиг.1) обеспечивается управляемая задержка внешней по отношению к данному устройству ПСП с заданной средней скоростью поступления импульсов.

Необходимым условием работы данного БТС является наличие генератора тактовых импульсов с двумя смещенными по фазе, в частности на половину периода тактовых импульсов, выходами. Для этой цели в схеме используется элемент 21 задержки импульсов от генератора тактовых импульсов, который обеспечивает задержку тактовых импульсов на величину, исключающую возможность наложения импульсов основной и задерживаемой последовательности (например, на полпериода).

Счетчик-делитель 5 (фиг.1) с постоянным коэффициентом деления предназначен для преобразования частоты тактовых импульсов , поступающих с выхода генератора тактовых импульсов, в частоту, равную среднему значению частоты, поступающей в линию задержки от БТС. Тем самым полностью обеспечивается режим работы прототипа и дополнительнок к этому обеспечивается заданный закон изменения задержки ПСП, поступающей от внешнего по отношению к линии задержки источника, из канала связи.

Управляемая линия задержки работает следующим образом.

В исходном состоянии все разряды первого реверсивного счетчика 16, второго реверсивного счетчика 17, счетчика 7 импульсов, находятся в нулевом состоянии. Задающий генератор 3 (или БТС 4, если устройство работает от внешнего по отношению к линии задержки источника) вырабатывает последовательность прямоугольных импульсов, которые поступают через первый ключ 6 на вход счетчика 7 импульсов. Последний осуществляет подсчет поступающих на его вход импульсов, в результате чего на его выходах формируются двоичные, r-разрядные кодовые комбинации, изменяющиеся с приходом очередного импульса. Информация в виде двоичных, r-разрядных кодовых комбинаций поступает на входы полного дешифратора 8. Число выходов полного дешифратора 8 равно , г - число входов дешифратора. Таким образом, двоичные, r-разрядные кодовые комбинации

преобразуются в параллельные, «-разрядные, унитарные кодовые комбинации. Таким образом, на выходах дешифратора 8 в фиксированный момент времени присутствует кодовая комбинация, имеющая только Т. С приходом очередного импульса на вход счетчика 7 на его выходе изменяется кодовая комбинация за счет перехода 1 в следующий разряд. Поскольку импульсы на

0 вход счетчика 7 поступают непрерывно, то на его выходах непрерывно изменяется кодовая комбинация, и, следовательно, непрерывно изменяется кодовая комбинация на выходе дешифратора 8, т.е. Г появляет5 ся поочередно на каждом из выходов с частотой тти /К, где К - число выходов дешифратора 8, f™ - частота импульсов поступающих от БТС или от счетчика-делителя 5 (в зависимости от режимов работы).

0 Выходы дешифратора 8 подключены к информационным входам первого мультиплексора 9, работой которого управляет первый реверсивный счетчик 16.

Каждой двоичной комбинации, снимае5 мой с выходов первого реверсивного счет- чика 16, соответствует коммутация определенного информационного входа первого мультиплексора 9 на его выход. Таким образом, Г поочередно, со сдвигом на

0 один такт, появляющаяся на информационных входах первого мультиплексора 9, при коммутации определенного входа мультиплексора 9 на выход, попадает на выход мультиплексора 9. При этом Г в выходной

5 бинарной последовательности также будет иметь временный сдвиг, однозначно определяемый тем, с какого из информационных входов последовательность поступает на выход.

0 Кроме того, с последнего выхода дешифратора 8 последовательность импульсов поступает на тактовые входы генератора 10 псевдослучайной последовательности и сдвигающего регистра 12, на

5 информационный вход которого поступает ПСП с генератора 10 псевдослучайной последовательности или от внешнего по отношению к линии задержки источника. Сдвигающий регистр поразрядно подклю0 чен к информационным входам второго мультиплексора 13. К управляющим входам второго мультиплексора 13 подключен второй реверсивный счетчик 17, поэтому каждой двоичной комбинации, снимаемой с

5 выходов второго реверсивного счетчика 17, соответствует коммутация определенного разряда сдвигающего регистра 12 на входе второго мультиплексора. Поскольку, сдвигающий регистр 12 тактируется с последнего выхода дешифратора 8, то разница во времени между импульсами, идущими с первого и последнего выходов дешифраторов 8, соответствует задержке одного разряда сдвигающего регистра 12. При управлении вторым реверсивным счетчиком 17 второго мультиплексора 13 на выходе мультиплексора 13 коммутируется ПСП с разрядов сдвигающего регистра 12, причем, задержка ПСП однозначно определяется номером разряда, коммутируемого на выходе второго мультиплексора 13. Таким образом, изменяя состояние второго реверсивного счетчика 17, можно управлять задержкой ПСП в пределах числа разрядов сдвигающего регистра 12 с дискретным шагом, равным одному такту. Выход первого мультиплексора 9 соединен с управляющим входом D-триггера, а выход второго мультиплексора 12 соединен с информационным входом D-триггера 14. Как известно, D-триг- гер является элементом задержки в том смысле, что информация поступает на выход информационного входа только тогда, когда на управляющем входе есть импульс. Таким образом, импульс с выхода первого мультиплексора 9 является управляющим для прохождения ПСП с выхода мультиплексора 13 на выход D-триггера 14. Тем самым осуществляется изменение задержки. ПСП, поступающей с выхода второго мультиплексора 13 на информационный вход D-триггера, в пределах одного разряда сдвигающего регистр 12 с дискретным шагом, равным разнице во времени появления 1 на двух последовательных выводах дешифратора 8, т.е. равным периоду следования импульсов со счетчика-делителя 5 либо блока 4 тактовой синхронизации.

Изменение задержки ПСП на выходе D- триггера осуществляется по требуемому за- кону, задаваемому источником 15 программируемых сигналов. Если импульсы от источника программируемых сигналов поступают на счетный вход +1, то первый реверсивный счетчик 16 осуществляет счет импульсов от 0 до г, где г - число выходов счетчика, соответствующее числу ячеек, т.е. обеспечивает линейно-возрастающий закон изменения задержки, Если же импульсы поступают на счетный вход -1, счет происходит от г до 0, тем самым обеспечивается линейноубывающий закон изменения задержки. Осуществляя счет поступающих на вход импульсов, первый реверсивный счетчик 16 управляет первым мультиплексором 9, т.е. выход первого мультиплексора 9 последовательно коммутирует информационные входы с частотой управляющих импульсов, поступающих на счетный вход первого реверсивного счетчика 16. При полном заполнении первого реверсивного счетчика 16 импульс с выхода переноса г поступает на счетный вход 1 второго реверсивного счетчика 16. При поступлении управляющих импульсов на счет- ный вход -1 первого реверсивного счетчика 16 происходит обратный счет импульсов, и при переходе счетчика из состояния полного обнуления в состояние 2

0 импульс с выхода переноса О поступает на счетный вход -1 второго реверсивного счетчика 17. Второй реверсивный счетчик 18, осуществляя прямой и обратный подсчет поступающих импульсов от первого ревер5 сивного счетчика 16, управляет вторым мультиплексором 13, коммутируя ПСП с разрядом сдвигающего регистра 12 на выход второго мультиплексора 13.

Таким образом, изменение задержки

0 ПСП осуществляется путем подсчета управляющих импульсов реверсивными счетчиками 16 и 17. Первый реверсивный счетчик 16 осуществляет изменение задержки ПСП в пределах одного разряда сдвигающего

5 регистра 9, а второй реверсивный счетчик 17 - в пределах от первого до последнего разряда сдвигающего регистра 12. Поскольку управляющие импульсы от задающего генератора 3 либо от БТС 4 через источник 15

0 программируемых сигналов поступают на счетный вход первого реверсивного счетчика 16, то и изменения задержки псевдослучайного сигнала также происходит непрерывно. Подключение счетных входов

5 реверсивного счетчика 16 к внешним программируемым устройствам позволяет получить в общем случае произвольный закон изменения задержки, определяемый структурой внешнего программирующегоустрой0 ства.

Таким образом, принципы работы управляемой линии задержки в режимах от генератора псевдослучайной последовательности и от внешнего по отношению к

5 линии задержки источника аналогичны.

Отличие заключается в том, что во втором из них тактовые импульсы, управляющие работой линии задержки, поступают от блока тактовой синхронизации и определя0 ются частотой поступления символов ПСП от внешнего источника, которая поступает на вход устройства задержки вместо ПСП от генератора 10.

Формула изобретения

5 Управляемая линия задержки по авт.св. № 1197068, отличающаяся тем, что, с целью расширения функциональных возможностей, заключающихся в обеспечении управления задержкой неизвестной псевдослучайной последовательностью, принимаемой от внешнего по отношению к устройству задержки источника, в нее дополнительно введены переключатель режима работы, блок выделения фронтов посылок, вход которого соединен с шиной псевдослучайной последовательности от внешнего по отношению к линии задержки источника, счетчик-делитель, вход которого соединен с выходом генератора тактовых импульсов, блок тактовой синхронизации, первый вход которого соединен с выходом блока выделения фронтов посылок, а второй - с выходом генератора тактовых импульсов, первый ключ, первый и второй входы которого соек блоку 5

Кблоку4

ГЦК блоку Ю

К бнеш.

источнику

0

5

динены соответственно с выходами блока тактовой синхронизации и счетчика-делителя, а выход его соединен с входами счетчика импульсов и источника программируемых сигналов, а также второй ключ, первый вход которого соединен с выходом генератора псевдослучайной последовательности, второй вход которого соединен с шиной сигнала от внешнего истопника, а выход его соединен с входом сдвигающего регистра, первый и второй выходы переключателя режима работы соединены соответственно с первым и вторыми управляющими входами первого и второго ключей.

Риг.1 35

г

WJf

К5/10ку7

X Влаху 15

них

К блоху/2

луг

i i i i i i i i i i i II II

г

д

К 8л. Ц

Фиг.З

и

кб/1.5

Риг. 4

Фиг. 5

| Управляемая линия задержки | 1984 |

|

SU1197068A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-07—Публикация

1990-01-15—Подача