Изобретение относится к автоматике и вычислительной технике, в частности, к системам защиты ресурсов вычислительного комплекса (ВК) от несанкционированного доступа (НСД), и может быть использовано для защиты системы ввода паролей в системах коллективного пользования.

Особенность решаемой задачи состоит в том, что пользователям автоматизированной системы управления представляются полномочия в соответствии с их паролями. При использовании стандартных технических средств возможно хищение паролей посредством наблюдения за их вводом на клавиатуре рабочих мест (РМ). В связи с этим возникает задача создания таких средств, которые бы значительно затрудняли возможность хищения кодов паролей, выбираемых на клавиатуре своих РМ.

Известное устройство реализует алго- ритм приема цветового пароля, заключающийся в воспроизведении на экране дисплея РМ серии цветовых гамм, причем после окончания генерации каждой гаммы пользователь должен нажать одну из разно- цветных клавиш, вынесенных на дополнительный пульт и соответствующих кодам символов обычного пароля.

Недостатки данного технического решения заключаются в необходимости ис- пользования дополнительной клавиатуры, число клавиш которой растет вместе с увеличением числа цветов, применяемых для генерации цветовых гамм. Это обстоятельство приводит к увеличению времени набо- ра пароля из-за поиска соответствующих клавиш.

Наиболее близким к изобретению является устройство, содержащее первый элемент И, первый вход которого является первым синхронизирующим входом устройства, первый триггер, единичные вход которого является вторым синхронизирующим входом устройства, а выход соединен с вторым синхронизирующим входом первого элемента И, первый элемент задержки, вход которого подключен к выходу первого элемента И, второй элемент задержки, вход которого соединен с вторым синхронизирующим входом устройства, первый счетчик, счетный вход которого подключен к выходу первого элемента задержки, третий элемент задержки, вход которого соединен с выходом первого элемента задержки, второй элемент И, один вход которого подключен к выходу переноса первого счетчика, а другой вход соединен с выходом третьего элемента задержки, первый элемент ИЛИ, один вход которого подключен к выходу второго элемента задержки, другой вход соединен с выходом второго элемента И, а выход первого элемента ИЛИ подключен к обнуляющему входу первого триггера, дешифратор, вход которого соединен с информационным выходом первого счетчика, группу элементов И, одни входы которых подключены к соответствующим выходам дешифратора, а другие входы соединены с выходом первого элемента И, группу регистров, информационные входы которых подключены к первому информационному входу устройства, а синхронизирующие входы соединены с выходами соответствующих элементов И группы, группу цифровых компараторов, одни информационные входы которых подключены к выходам соответствующих регистров группы, второй счетчик, обнуляющий вход которого соединен с выходом второго элемента И, второй элемент ИЛИ, один вход которого подключен к выходу второго элемента И, четвертый элемент задержки, вход которого соединен с выходом второго элемента ИЛИ, третий элемент И, прямой вход которого подключен к выходу переноса второго счетчика, а инверсный вход соединен с выходом четвертого элемента задержки, четвертый элемент И, один вход которого подключен к выходу переноса второго счетчика, а другой вход соединен с выходом элемента задержки, первый блок памяти, адресный вход которого подключен к информационному выходу второго счетчика, синхронизирующий вход соединен с выходом третьего элемента И, одни выходы первого блока памяти подключены к вторым информационным входам соответствующих цифровых компараторов, а другие выходы первого блока памяти являются первым информационным выходом устройства, пятый элемент задержки, вход которого соединен с выходом третьего элемента И, а выход подключен к синхронизирующим входам цифровых компараторов группы, шестой элемент задержки, вход которого соединен с выходом пятого элемента задержки, пятый элемент И, первые входы которого подключены к прямым выходам соответствующих

цифровых компараторов группы, последний вход соединен с выходом шестого элемента задержки, а выход пятого элемента И является первым синхронизирующим выходом устройства, третий элемент ИЛИ, входы ко- торого подключены к инверсным выходам соответствующих цифровых компараторов группы, шестой элемент И, один вход которого соединен с выходом третьего элемента ИЛИ, другой вход подключен к выходу шее- того элемента задержки, а выход шестого элемента И соединен со счетным входом второго счетчика и с другим входом второго элемента ИЛИ, третий счетчик, счетный вход которого подключен к выходу второго элемента задержки, седьмой элемент задержки, вход которого соединен с выходом второго элемента задержки, седьмой элемент И, один вход которого подключен к выходу третьего счетчика, а другой вход со- единен с выходом седьмого элемента задержки, вход которого является третьим синхронизирующим входом устройства, четвертый элемент ИЛИ, первый вход которого подключен к выходу четвертого элемента И, второй вход соединен с выходом седьмого элемента И, третий вход четвертого элемента ИЛИ подключен к выходу восьмого элемента задержки, а выход четвертого элемента ИЛИ соединен с обнуляю- щими входами первого и третьего счетчиков, девятый элемент задержки, вход которого подключен к выходу четвертого элемента ИЛИ, четвертый счетчик, обнуляющий вход которого соединен с третьим синхронизирующим входом устройства, а счетный вход подключен к выходу четвертого элемента ИЛИ, восьмой элемент И, один вход которого соединен с выходом переноса четвертого счетчика, другой вход подклю- чен к выходу девятого элемента задержки, а выход восьмого элемента И является вторым синхронизирующим выходом устройства, пятый элемент ИЛИ, первый вход которого соединен с третьим синхронизиру- ющим входом устройства, второй вход подключен к выходу первого элемента И, а третий вход пятого элемента ИЛИ соединен с выходом второго элемента задержки.

Недостаток этого устройства заключается в невысоком быстродействии, обусловленном затратами времени на считывание кодов кадров, содержащих стохастическую информацию, с внешних запоминающих ус- тройств (ВЗУ).

Цель изобретения заключается в повышении быстродействия, что возможно за счет генерации кодов случайных кадров с помощью узлов и элементов устройства.

Поставленная цель достигается тем, что в известное устройство, содержащее первый элемент И, первый вход которого является первым синхронизирующим входом устройства, первый триггер, единичный вход которого является вторым синхронизирующим входом устройства, а выход соединен со вторым входом первого элемента И, первый элемент задержки, вход которого подключен к выходу первого элемента И, второй элемент задержки, вход которого соединен с вторым синхронизирующим входом устройства, первый счетчик, счетный вход которого подключен к выходу первого элемента задержки, третий элемент задержки, вход которого соединен с выходом первого элемента задержки, второй элемент И, один вход которого подключен к выходу переноса первого счетчика, а другой вход сое- динен с выходом третьего элемента задержки, первый элемент ИЛИ, один вход которого подключен к выходу второго элемента задержки, другой вход соединен с выходом второго элемента И, а выход первого элемента ИЛИ подключен к обнуляющему входу первого триггера, дешифратор, вход которого соединен с информационным выходом первого счетчика, группу элементов И, одни входы которых подключены к соответствующим выходам дешифратора, а другие входы соединены с выходом первого элемента И, группу регистров, информационные входы которых подключены к первому информационному входу устройства, а синхронизирующие входы соединены с выходами соответствующих элементов И группы, группу цифровых компараторов, одни информационные входы которых подключены к выходам соответствующих регистров группы, второй счетчик, обнуляющий вход которого соединен с выходом второго элемента И, второй элемент ИЛИ, один вход которого подключен к выходу второго элемента И, четвертый элемент задержки, вход которого соединен с выходом второго элемента ИЛИ, третий элемент И, прямой вход которого подключен к выходу переноса второго счетчика, а инверсный вход соединен с выходом четвертого элемента задержки, четвертый элемент И, один вход которого подключен к выходу переноса второго счетчика, а другой вход соединен с выходом четвертого элемента задержки, первый блок памяти, адресный вход которого подключен к информационному выходу второго счетчика, синхронизирующий вход соединен с выходом третьего элемента И, одни выходь первого блока памяти подключены к вторые информационным входам соответствующи цифровых компараторов, а другие выходь

первого блока памяти являются первым информационным выходом устройства, пятый элемент задержки, вход которого соединен с выходом третьего элемента И, а выход подключен к синхронизирующим входам цифровых компараторов группы, шестой элемент задержки, вход которого соединен с выходом пятого элемента задержки, пятый элемент И, первые входы которого подключены к прямым выходам соответствующих цифровых компараторов группы, последний вход соединен с выходом шестого элемента задержки, а выход пятого элемента И является первым синхронизирующим выходом устройства, третий элемент ИЛИ, входы ко- торого подключены к инверсным выходам соответствующих цифровых компараторов группы, шестой элемент И, один вход которого соединен с выходом третьего элемента ИЛИ, другой вход подключен к выходу шее- того элемента задержки, а выход шестого элемента И соединен со счетным входом второго элемента ИЛИ, третий счетчик, счетный вход которого подключен к выходу второго элемента задержки, седьмой эле- мент задержки, вход которого соединен с выходом второго элемента задержки, седьмой элемент И, один вход которого подключен к выходу третьего счетчика, а другой вход соединен с выходом седьмого элемен- та задержки, вход которого является третьим синхронизирующим входом устройства, четвертый элемент ИЛИ, первый вход которого подключен к выходу четвертого элемента И, второй вход соединен с выходом седьмого элемента И, третий вход четвертого элемента ИЛИ подключен к выходу восьмого элемента задержки, а выход четвертого элемента ИЛИ соединен с обнуляющими входами первого и третьего счет- чиков, девятый элемент задержки, вход которого подключен к выходу четвертого элемента ИЛИ, четвертый счетчик, обнуляющий вход которого соединен с третьим синхронизирующим входом устройства, а счетный вход подключен к выходу четвертого элемента ИЛИ, восьмой элемент И, один вход которого соединен с выходом переноса четвертого счетчика, другой вход подключен к выходу девятого элемента задержки, а выход восьмого элемента И является вторым синхронизирующим выходом устройства, пятый элемент ИЛИ, первый вход которого соединен с третьим синхронизирующим входом устройства, второй вход под- ключей к выходу первого элемента И, а третий вход пятого элемента ИЛИ соединен с выходом второго элемента задержки введены шестой элемент ИЛИ, один вход которого соединен с выходом пятого элемента

ИЛИ, седьмой элемент ИЛИ, вход которого подключен к выходу пятого элемента ИЛИ, пятый счетчик, обнуляющий вход которого соединен с выходом шестого элемента ИЛИ, шестой счетчик, обнуляющий вход которого подключен к выходу седьмого элемента ИЛИ, десятый элемент задержки, вход которого соединен с выходом пятого элемента ИЛИ, восьмой элемент ИЛИ, первый вход которого подключен к выходу десятого элемента задержки, второй блок памяти, адресный вход которого является вторым информационным входом устройства, а синхронизирующий вход соединен с выходом восьмого элемента ИЛИ, одиннадцатый элемент задержки, вход которого подключен к выходу восьмого элемента ИЛИ, регистр, информационный вход которого соединен с выходом второго блока памяти, а синхронизирующий вход подключен к выходу одиннадцатого элемента задержки, двенадцатый элемент задержки, вход которого соединен с выходом одиннадцатого элемента задержки, девятый элемент ИЛИ, один вход которого подключен к выходу двенадцатого элемента задержки, третий блок памяти, информационный вход которого соединен с первыми входами регистра, адресный вход подключен к выходу пятого счетчика, а синхронизирующий вход третьего блока памяти соединен с выходом девятого элемента ИЛИ, тринадцатый элемент задержки, вход которого подключен к выходу девятого элемента ИЛИ, а выход соединен со счетным входом пятого и шестого счетчиков, четырнадцатый элемент задержки, вход которого подключен к выходу тринадцатого элемента задержки, девятый элемент И, один вход которого соединен с выходом переноса шестого счетчика, другой вход подключен к выходу четырнадцатого элемента задержки, а выход девятого элемента И соединен с другим входом седьмого элемента ИЛИ, десятый элемент И, прямой вход которого подключен к выходу четырнадцатого элемента задержки, инверсный вход соединен с выходом переноса шестого счетчика, а выход десятого элемента И подключен к другому входу девятого элемента ИЛИ, одиннадцатый элемент И, один вход которого соединен с выходом переноса пятого счетчика, а другой вход подключен к выходу девятого элемента И, двенадцатый элемент И, прямой вход которого соединен с выходом девятого элемента И, инверсный вход подключен к выходу переноса пятого счетчика, а выход двенадцатого элемента И соединен со вторым входом восьмого элемента ИЛИ, тринадцатый элемент И, один вход которого подключен к последнему выходу регистра, а другой вход соединен с выходом девятого элемента ИЛИ, второй триггер, обнуляющий вход которого подключен к выходу пятого элемента ИЛИ, единичный вход соединен с выходом тринадцатого элемента И, а выход второго триггера подключен к третьему входу первого элемента И, седьмой счетчик, обнуляющий вход которого соединен с выходом одиннадцатого элемента И, восьмой счетчик, обнуляющий вход которого подключен к выходу пятого элемента ИЛИ, пятнадцатый элемент задержки, вход которого соединен с выходом одиннадцатого элемента И, десятый элемент ИЛИ, один вход которого подключен к выходу пятнадцатого элемента задержки, шестнадцатый элемент задержки, вход которого соединен с выходом десятого элемента ИЛИ, а выход подключен к счетным входам седьмого и восьмого счетчиков, семнадцатый элемент задержки, вход которого соединен с выходом шестнадцатого элемента задержки, четырнадцатый элемент И, прямой вход которого подключен к выходу семнадцатого элемента задержки, инверсный вход соединен с выходом переноса седьмого счетчика, а выход четырнадцатого элемента И подключен к другому входу десятого элемента ИЛИ, пятнадцатый элемент И, один вход которого соединен с выходом семнадцатого элемента задержки, а другой вход подключен к выходу переноса седьмого счетчика, шестнадцатый элемент И, один вход которого соединен с выходом пятнадцатого элемента И, другой вход подключен к выходу переноса восьмого счетчика, а выход шестнадцатого элемента И является третьим синхронизирующим выходом устройства, семнадцатый элемент И, прямой вход которого соединен с выходом пятнадцатого элемента И, инверсный вход подключен к выходу переноса восьмого счетчика, а выход семнадцатого элемента И соединен с третьим входом восьмого элемента ИЛИ, и с другим входом шестого элемента ИЛИ, четвертый блок памяти, первый адресный вход которого подключен к выходу восьмого счетчика, второй адресный вход является третьим информационным входом устройства, информационные входы блока памяти соединены с соответствующими информационными выходами третьего блока памяти, синхронизирующий вход четвертого блока памяти подключен к выходу десятого элемента ИЛИ, а информационный выход четвертого блока памяти является вторым информационным выходом устройства.

В основу построения устройства положены следующие соображения.

Как и в случае прототипа, пользователю предъявляется на экране дисплея РМ серия кадров, содержащих стохастическую информацию, причем каждый из кадров может

содержать или не содержать отметку, т.е. определенную информацию, заранее сообщенную пользователю. Если кадр отмечен, то пользователь вводит очередной символ своего пароля. В противном случае нажимается произвольная клавиша, код которой игнорируется устройством. Таким образом накапливаются символы вводимого пароля. С точки зрения наблюдателя, не знающего отметки, при различных попытках ввода пароля один и тот же пользователь вводит различные последовательности символов, поскольку символы пароля перемежаются случайными символами, число которых зависит от типа и последовательности воспроизводимых кадров.

После окончания приема пароля W происходит его сравнение с кодами паролей зарегистрированных пользователей. Если код W совпал с одним из кодов зарегистрированных паролей Pi, то пользователю предоставляются полномочия для работы в системе в соответствии с кодом П| строки матрицы полномочий, в противном случае попытка ввода пароля считается израсходованной. Если пользователь совершил несколько неудачных попыток ввода пароля, то формируется сигнал о попытке НСД.

Рассмотрим более подробно алгоритм

генерации одного из случайных кадров, воспроизводимых на экране дисплея РМ пользователя с помощью адаптера, поддерживающего графический режим в 256 цветов. Такой адаптер поддерживает отображение графического буфера, состоящего из Вмакс строк, Смаке столбцов, причем каждый из пикселов (наименьших графических элементов) задается восьмиразрядным кодом (байтом).

Формируемые кадры разбивают экран на одинаковые прямоугольные области, каждая из которых является пересечением Гмакс строк и макс столбцов и закрашена однородным цветом, код которого равен F.

Цвета, число которых может достигать 256, прямоугольников выбираются случайно. Некоторые из цветов символизируют отметку всего кадра, т.е. кадр считается отмеченным, если некоторый из его прямоугольников закрашен цветом, входящим в заранее составленный набор отметок.

Перед началом формирования кадра обнуляют номер R текущей строки кадра.

Перед началом формирования текущей строки А кадра К обнуляется номер С теку11173061512

щего пиксела строки. В строке А будет ровно71 и третий 72 синхронизирующие входы,

СмаксЛмакс равноокрашенных отрезков, со-первый 73 и второй 74 информационные выответствующих числу прямоугольников в од-ходы, первый 75, второй 76 и третий 77 синной горизонтальной полоске.хронизирующие выходы устройства.

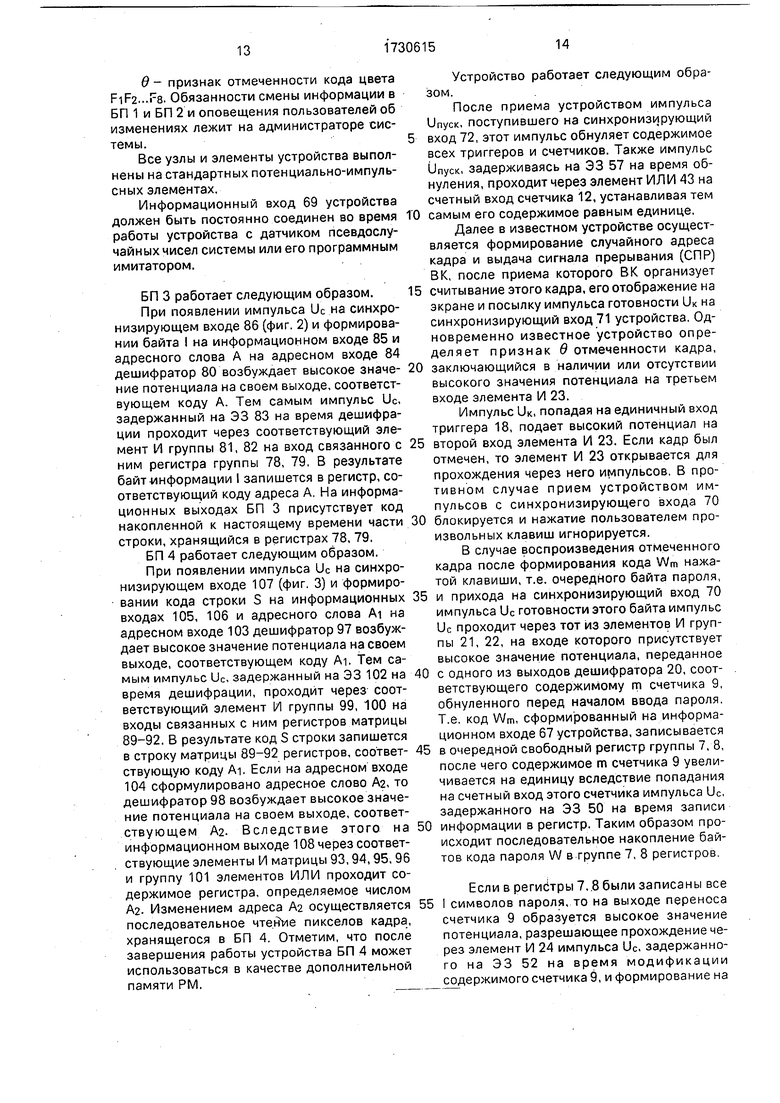

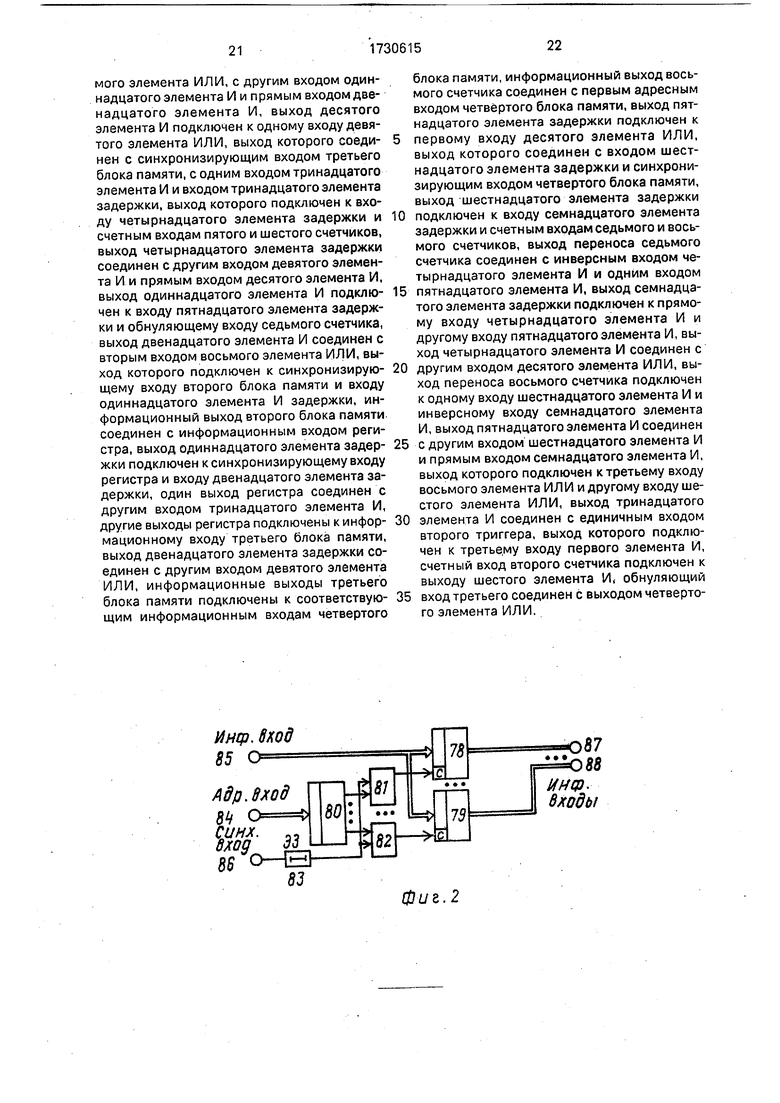

Перед началом формирования текущего 5БП 3 (фиг. 2) содержит группу 78, 79 ре- отрезка стоки А определяют некоторое слу-гистров, дешифратор 80, группу 81, 82 эле- чайное числоЈ. С помощью кода Ј выбираютментов И, ЭЗ 83. Также на фиг. 2 показаны код цвета текущего отрезка F F( Ј) и кодадресный вход 84, информационный вход 85, отметки отрезка в в ( Ј ).синхронизирующий вход 86 и информационДалее записывают F в элементы памяти, 10ные выходы 87, 88 третьего БП. соответствующие пикселам текущего отрез-БП 4 (фиг. 3) содержит матрицу 89-92

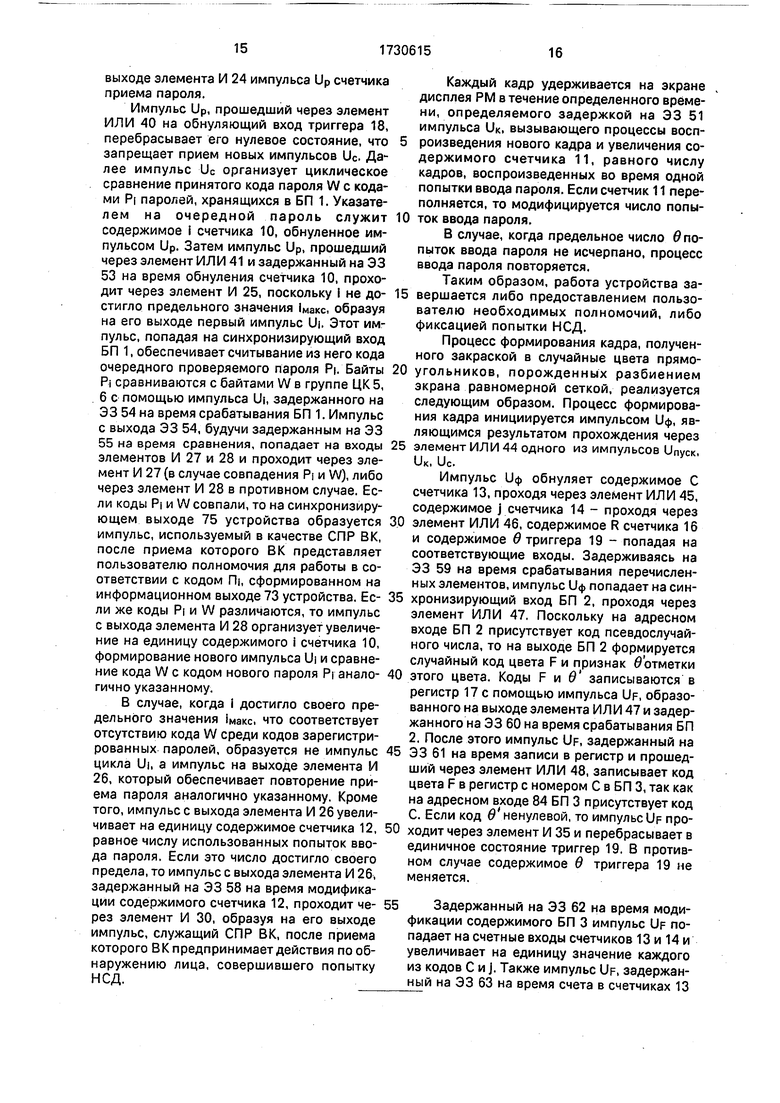

ка, т.е. пикселам текущей строки с номерамирегистров, матрицу 93-96 элементов И, перС, С+1C+JM3KC-1. После этого С увеличи-вый 97 и второй 98 дешифраторы, группу 99,

вается на ширину прямоугольника }макс , и в100 элементов И, группу 101 элементов ИЛИ

случае, когда строка А еще не сформирова- 15и ЭЗ 102. Также на фиг. 3 показаны первый

на, закрашивается случайным цветом новый103 и второй 104 адресные входы, информаотрезок строки А,ционные входы 105, 106, синхронизируюЕсли строка А сформирована, то она за-щий вход 107 и информационный выход 108

писывается в элементы памяти, соответству-четвертого блока памяти.

ющие строкам кадра К с номерами R, R+1 20 Разрядность элементов, входящих в огR+rMaKc-1. После этого R увеличивается нараничительную часть устройства, описана в

высоту прямоугольника Гмакс, и в случае, ког-известном устройстве. Разрядность оставда кадр К еще не сформирован, порождаетсяшихся элементов выбирается следующим

новая полоска случайно окрашенных прямо-образом, угольников. 25 Разрядность счетчика 13 равна

Готовый кадр считается отмеченным, ее-(Iog2 Смаке + 1), счетчика 14 - (loga +

ли в него входит хотя бы один прямоуголь-+ 1), счетчика 15 - (loga Гмакс + 1), счетчика

ник, отметка в которого не нулевая, и не16 - (loga Рмакс + 1). Входная шина БП 2

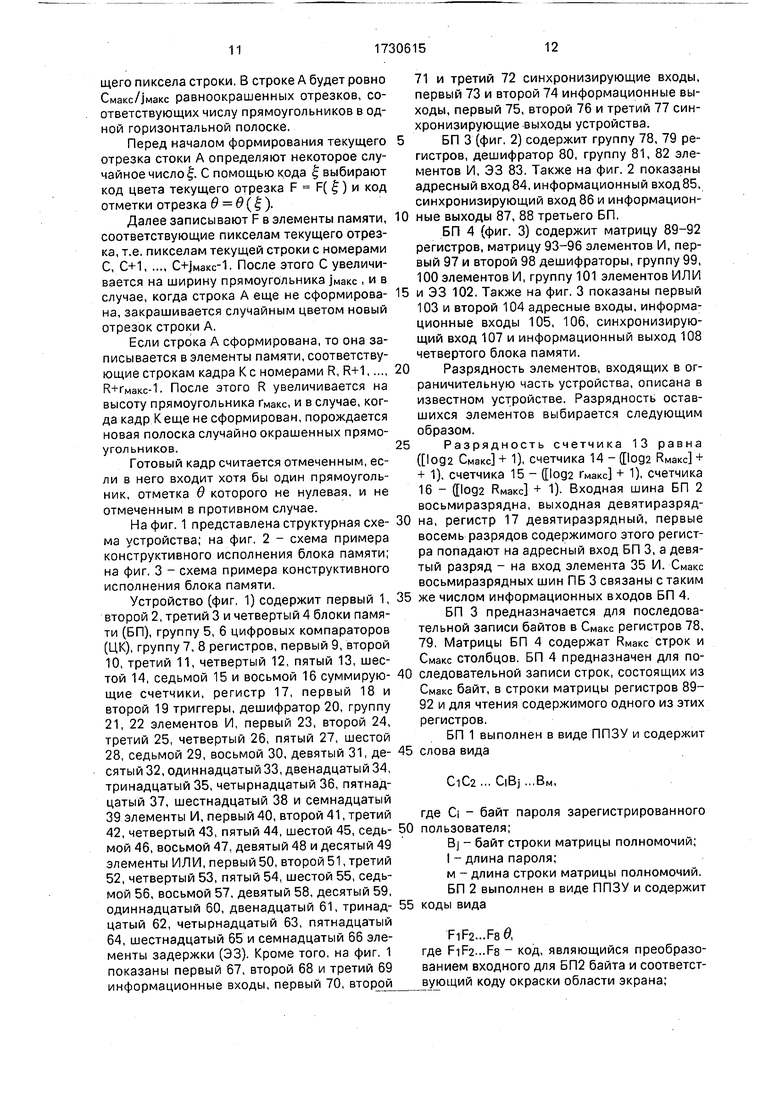

отмеченным в противном случае.восьмиразрядна, выходная девятиразрядНа фиг. 1 представлена структурная схе- 30на, регистр 17 девятиразрядный, первые

ма устройства; на фиг, 2 - схема примеравосемь разрядов содержимого этого регистконструктивного исполнения блока памяти;ра попадают на адресный вход БП 3, а девяна фиг. 3 - схема примера конструктивноготый разряд - на вход элемента 35 И. Смаке

исполнения блока памяти.восьмиразрядных шин ПБ 3 связаны с таким

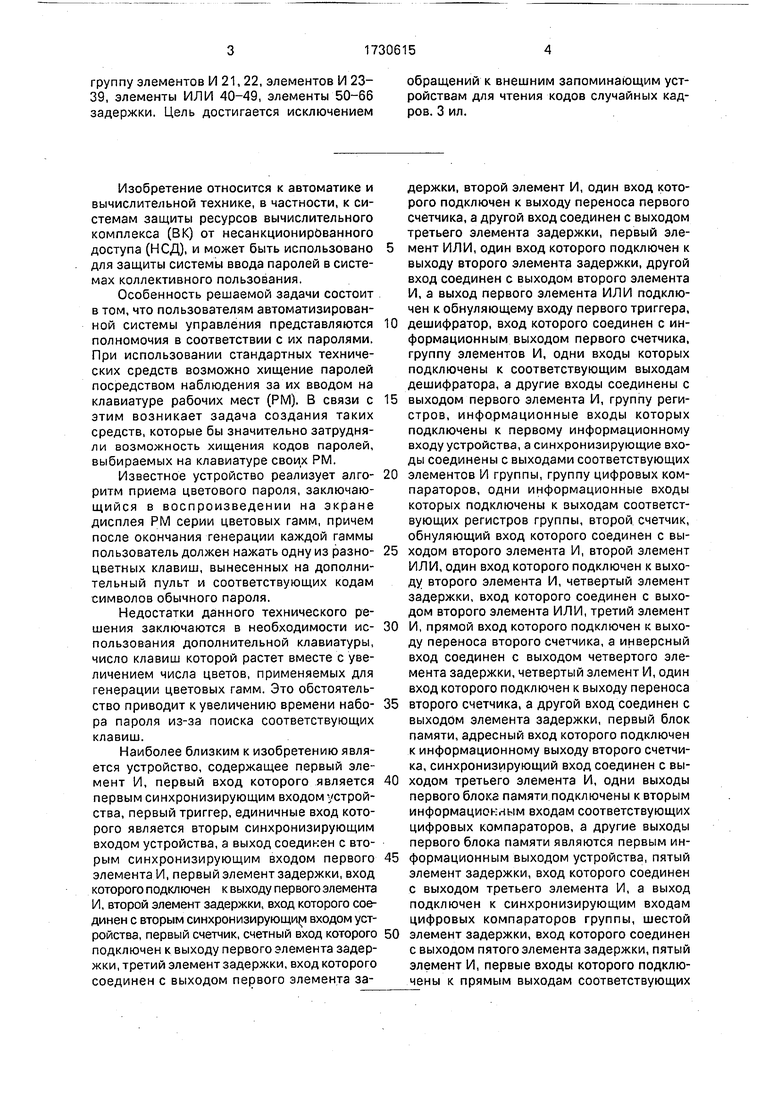

Устройство (фиг, 1) содержит первый 1, 35же числом информационных входов БП 4. второй 2, третий 3 и четвертый 4 блоки памя-БП 3 предназначается для последовати (БП), группу 5, 6 цифровых компараторовтельной записи байтов в Смаке регистров 78,

(ЦК), группу, 8 регистров, первый 9, второй79. Матрицы БП 4 содержат RMaKc строк и

10, третий 11, четвертый 12, пятый 13, шее-Смаке столбцов. БП 4 предназначен для потой 14, седьмой 15 и восьмой 16 суммирую- 40следовательной записи строк, состоящих из

щие счетчики, регистр 17, первый 18 иСмаке байт, в строки матрицы регистров 89второй 19 триггеры, дешифратор 20, группу92 и для чтения содержимого одного из этих

21, 22 элементов И, первый 23, второй 24,регистров.

третий 25, четвертый 26, пятый 27, шестойБП 1 выполнен в виде ППЗУ и содержит

28, седьмой 29, восьмой 30, девятый 31, де- 45слова вида сятый 32, одиннадцатый 33, двенадцатый 34,

тринадцатый 35, четырнадцатый 36, пятнад-CiC2 ... CiBj ...BM,

цатый 37, шестнадцатый 38 и семнадцатый

39 элементы И, первый 40, второй 41, третийгде Q - байт пароля зарегистрированного

42, четвертый 43, пятый 44, шестой 45, седь- 50пользователя;

мой 46, восьмой 47. девятый 48 и десятый 49Bj - байт строки матрицы полномочий;

элементы ИЛИ, первый 50, второй 51, третий - длина пароля;

52, четвертый 53, пятый 54, шестой 55, седь-м - длина строки матрицы полномочий.

мой 56, восьмой 57, девятый 58, десятый 59,БП 2 выполнен в виде ППЗУ и содержит

одиннадцатый 60, двенадцатый 61, тринад- 55коды вида цатый 62, четырнадцатый 63, пятнадцатый 64, шестнадцатый 65 и семнадцатый 66 эле-FiF2...Fs в,

менты задержки (ЭЗ). Кроме того, на фиг, 1где FiF2...Fs - код, являющийся преобразопоказаны первый 67, второй 68 и третий 69ванием входного для БП2 байта и соответстинформационные входы, первый 70, второйвующий коду окраски области экрана;

13173061514

в - признак отмеченности кода цветаУстройство работает следующим обраFiF2...Fs. Обязанности смены информации в зом.

БП 1 и БП 2 и оповещения пользователей обПосле приема устройством импульса

изменениях лежит на администраторе сие- ипуск, поступившего на синхронизирующий темы.5 вход 72, этот импульс обнуляет содержимое

Все узлы и элементы устройства выпол- всех триггеров и счетчиков. Также импульс нены на стандартных потенциально-импуль- Опуск, задерживаясь на ЭЗ 57 на время об- сных элементах.нуления, проходит через элемент ИЛИ 43 на

Информационный вход 69 устройства счетный вход счетчика 12, устанавливая тем должен быть постоянно соединен во время ТО самым его содержимое равным единице, работы устройства с датчиком псевдослу-Далее в известном устройстве осущестчайных чисел системы или его программным вляется формирование случайного адреса имитатором.кадра и выдача сигнала прерывания (СПР)

ВК, после приема которого ВК организует

БП 3 работает следующим образом. 15 считывание этого кадра, его отображение на При появлении импульса Uc на синхро- экране и посылку импульса готовности UK на низирующем входе 86 (фиг. 2) и формирова- синхронизирующий вход 71 устройства. Од- нии байта I на информационном входе 85 и повременно известное устройство опре- адресного слова А на адресном входе 84 деляет признак В отмеченности кадра, дешифратор 80 возбуждает высокое значе- 20 заключающийся в наличии или отсутствии ние потенциала на своем выходе, соответст- высокого значения потенциала на третьем вующем коду А. Тем самым импульс Uc, входе элемента И 23.

задержанный на ЭЗ 83 на время дешифра-Импульс UK, попадая на единичный вход

ции проходит через соответствующий эле- триггера 18, подает высокий потенциал на мент И группы 81, 82 на вход связанного с 25 второй вход элемента И 23. Если кадр был ним регистра группы 78, 79. В результате отмечен, то элемент И 23 открывается для байт-информации I запишется в регистр, со- прохождения через него импульсов. В про- ответствующий коду адреса А. На информа- тивном случае прием устройством им- ционных выходах БП 3 присутствует код пульсов с синхронизирующего входа 70 накопленной к настоящему времени части 30 блокируется и нажатие пользователем про- строки, хранящийся в регистрах 78, 79.извольных клавиш игнорируется.

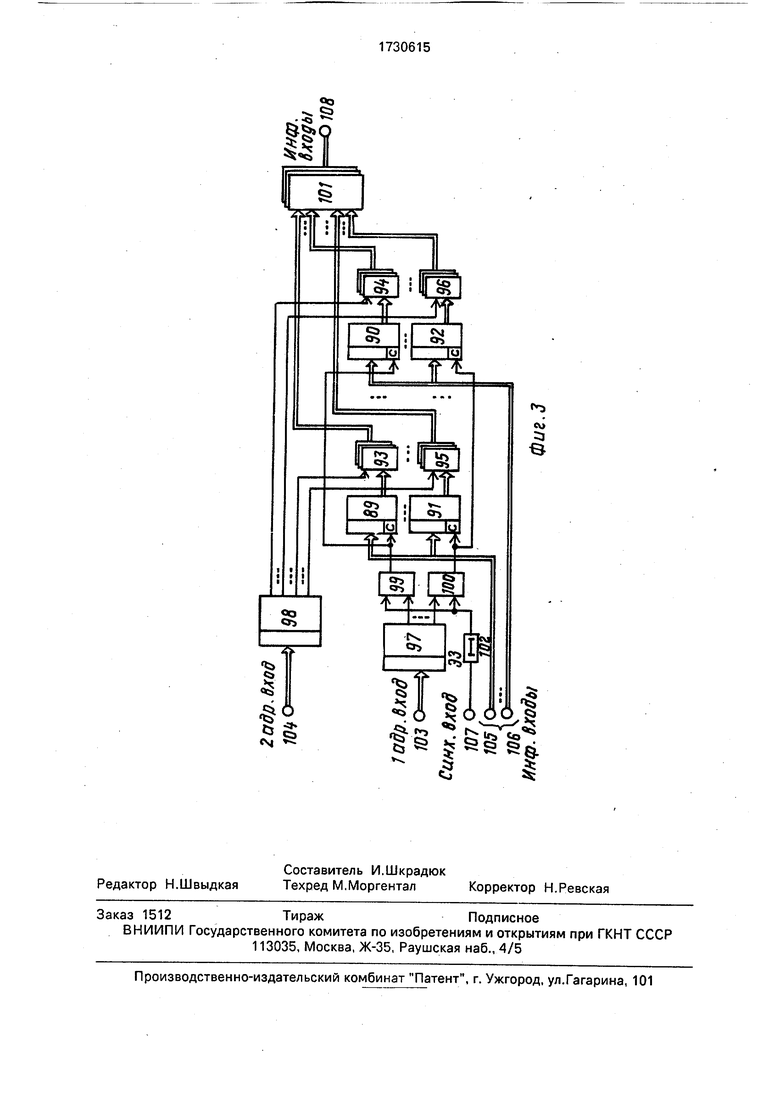

БП 4 работает следующим образом.В случае воспроизведения отмеченного

При появлении импульса Uc на синхро- кадра после формирования кода Wm нажа- низирующем входе 107 (фиг. 3) и формиро- той клавиши, т.е. очередного байта пароля, вании кода строки S на информационных 35 и прихода на синхронизирующий вход 70 входах 105, 106 и адресного слова AI на импульса Uc готовности этого байта импульс адресном входе 103 дешифратор 97 возбуж- Uc проходит через тот из элементов И груп- дает высокое значение потенциала на своем пы 21, 22, на входе которого присутствует выходе, соответствующем коду AL Тем са- высокое значение потенциала, переданное мым импульс ис, задержанный на ЭЗ 102 на 40 с одного из выходов дешифратора 20, соот- время дешифрации, проходит через соот- ветствующего содержимому m счетчика 9, ветствующий элемент И группы 99, 100 на обнуленного перед началом ввода пароля, входы связанных с ним регистров матрицы Т.е. код Wm, сформированный на информа- 89-92. В результате код S строки запишется ционном входе 67 устройства, записывается в строку матрицы 89-92 регистров, соответ- 45 в очередной свободный регистр группы 7, 8, ствующую коду AL Если на адресном входе после чего содержимое m счетчика 9 увели- 104 сформулировано адресное слово Аа, то чивается на единицу вследствие попадания дешифратор 98 возбуждает высокое значе- на счетный вход этого счетчика импульса Uc, ние потенциала на своем выходе, соответ- задержанного на ЭЗ 50 на время записи ствующем А2. Вследствие этого на 50 информации в регистр. Таким образом про- информационном выходе 108 через соответ- исходит последовательное накопление бай- ствующие элементы И матрицы 93,94,95. 96 тов кода пароля W в группе 7, 8 регистров, и группу 101 элементов ИЛИ проходит содержимое регистра, определяемое числомЕсли в регистры 7,8 были записаны все А2. Изменением адреса Аа осуществляется 55 I символов пароля, то на выходе переноса последовательное чтение пикселов кадра, счетчика 9 образуется высокое значение хранящегося в БП 4. Отметим, что после потенциала, разрешающее прохождение че- завершения работы устройства БП 4 может рез элемент И 24 импульса Uc, задержанно- использоваться в качестве дополнительной го на ЭЗ 52 на время модификации памяти РМ. содержимого счетчика 9, и формирование на

выходе элемента И 24 импульса Up счетчикаКаждый кадр удерживается на экране

приема пароля.дисплея РМ в течение определенного времеИмпульс Up, прошедший через элементни, определяемого задержкой на ЭЗ 51 ИЛИ 40 на обнуляющий вход триггера 18,импульса UK, вызывающего процессы восп- перебрасывает его нулевое состояние, что5 роизведения нового кадра и увеличения со- запрещает прием новых импульсов Uc. Да-держимого счетчика 11, равного числу лее импульс Uc организует циклическоекадров, воспроизведенных во время одной сравнение принятого кода пароля W с кода-попытки ввода пароля. Если счетчик 11 пере- ми PI паролей, хранящихся в БП 1. Указате-полняется, то модифицируется число попы- лем на очередной пароль служит10 ток ввода пароля.

содержимое i счетчика 10, обнуленное им-В случае, когда предельное число 0по- пульсом Up. Затем импульс Up, прошедшийпыток ввода пароля не исчерпано, процесс через элемент ИЛИ 41 и задержанный на ЭЗввода пароля повторяется. 53 на время обнуления счетчика 10, прохо-Таким образом, работа устройства за- дит через элемент И 25, поскольку i не до-15 вершается либо предоставлением пользо- стигло предельного значения макс, образуявателю необходимых полномочий, либо на его выходе первый импульс Ui. Этот им-фиксацией попытки НСД. пульс, попадая на синхронизирующий входПроцесс формирования кадра, получен- БП 1, обеспечивает считывание из него коданого закраской в случайные цвета прямо- очередного проверяемого пароля PI. байты20 угольников, порожденных разбиением Pi сравниваются с байтами W в группе ЦК 5,экрана равномерной сеткой, реализуется 6 с помощью импульса Ui, задержанного наследующим образом. Процесс формирова- ЭЗ 54 на время срабатывания БП 1. Импульсния кадра инициируется импульсом , яв- с выхода ЭЗ 54, будучи задержанным на ЭЗляющимся результатом прохождения через 55 на время сравнения, попадает на входы25 элемент ИЛ И 44 одного из импульсов UnycK, элементов И 27 и 28 и проходит через эле-UK, Uc.

мент И 27 (в случае совпадения PI и W), либоИмпульс обнуляет содержимое С

через элемент И 28 в противном случае. Ее-счетчика 13, проходя через элемент ИЛИ 45,

ли коды PI и W совпали, тона синхронизиру-содержимое j счетчика 14 - проходя через

ющем выходе 75 устройства образуется30 элемент ИЛИ 46, содержимое R счетчика 16

импульс, используемый в качестве СПР ВК,и содержимое в триггера 19 - попадая на

после приема которого ВК представляетсоответствующие входы. Задерживаясь на

пользователю полномочия для работы в со-ЭЗ 59 на время срабатывания перечисленответствии с кодом П|, сформированном наных элементов, импульс попадает на сининформационном выходе 73 устройства. Ее-35 хронизирующий вход БП 2, проходя через

ли же коды PI и W различаются, то импульсэлемент ИЛИ 47. Поскольку на адресном

с выхода элемента И 28 организует увеличе-входе БП 2 присутствует код псевдослучайние на единицу содержимого i счетчика 10,ного числа, то на выходе БП 2 формируется

формирование нового импульса Ui и сравне-случайный код цвета F и признак 0отметки

ние кода W с кодом нового пароля Pi знало-40 этого цвета. Коды F и в записываются в

гично указанному.регистр 17 с помощью импульса UF, образоВ случае, когда i достигло своего пре-ванного на выходе элемента ИЛ И 47 и задер- дельного значения Макс, что соответствуетжанного на ЭЗ 60 на время срабатывания БП отсутствию кода W среди кодов зарегистри-2. После этого импульс UF, задержанный на рованных паролей, образуется не импульс45 ЭЗ 61 на время записи в регистр и прошед- цикла Ui, а импульс на выходе элемента Иший через элемент ИЛИ 48, записывает код 26, который обеспечивает повторение при-цвета F в регистр с номером С в БП 3, так как ема пароля аналогично указанному. Кромена адресном входе 84 БП 3 присутствует код того, импульс с выхода элемента И 26 увели-С. Если код в ненулевой, то импульс Up про- чивает на единицу содержимое счетчика 12,50 ходит через элемент И 35 и перебрасывает в равное числу использованных попыток вво-единичное состояние триггер 19. В против- да пароля. Если это число достигло своегоном случае содержимое в триггера 19 не предела, то импульс с выхода элемента И 26,меняется, задержанный на ЭЗ 58 на время модификации содержимого счетчика 12, проходит че-55 Задержанный на ЭЗ 62 на время моди- рез элемент И 30, образуя на его выходефикации содержимого БП 3 импульс Up по- импульс, служащий СПР ВК, после приемападает на счетные входы счетчиков 13 и 14 и которого В К предпринимает действия по об-увеличивает на единицу значение каждого наружению лица, совершившего попыткуиз кодов С и J. Также импульс Up, задержан- НСД.ный на ЭЗ 63 на время счета в счетчиках 13

и 14, проходит через один из элементов И 31кадра из БП 4. Признаком отмеченности кад- и 32. Если на выходе переноса счетчика 14ра является содержимое в триггера 19. присутствует низкое значение потенциала,В случае, когда R меньше RMSKC, т.е. БП 4 не т.е. код был записан в БП з менее чем максзаполнен, в дополнение к описанным процессам раз, то на выходе элемента И 32 образуется5 импульс UR проходит через элемент И 39 и импульс, проходящий через элемент ИЛИ 48элементы ИЛИ 45 и 47. В результате этого и обеспечивающий новую запись кода F в БПсодержимое С счетчика 13 обнуляется, а на 3 и модификацию содержимого счетчиков 13выходе элемента ИЛИ 47 образуется им- и 14. Таким образом в БП 3 будет записанапульс Up, начинающий формирование новой макс кодов F. После этого на выходе эле-10 строки в БП 3 аналогично указанному, мента И 31 образуется импульс Uj, который,Таким образом, введение дополнитель- проходя через элемент ИЛИ 46, обнуляетных узлов и элементов позволяетсуществен- содержимое j счетчика 14. Кроме того, им-но повысить быстродействие устройства за пульс DJ проходит через один из элементовсчет исключения обращения к ВЗУ. И 33 и 34. Если на выходе переноса счетчика15 Чтение и воспроизведение графическо- 13 присутствует низкое значение потенциа-го кадра, хранящегося в виде отдельного нала, т.е. строка в БП 3 еще не сформирована,бора данных на магнитном диске типа то импульс, образованный на выходе эле- Винчестер для персональной ЭВМ, выпол- мента И 34, проходит через элемент ИЛИ 47,няющей роль интеллектуального рабочего порождая на выходе этого элемента новый20 места, занимает 2-3 с, в то время как форми- импульс UF, который обеспечивает записьрование кадра данного устройства требует новых JMaKc байтов в БП 3 аналогично ука-не более 1,5 с. Кроме того, предлагаемое занному.устройство не занимает пространство на

ВЗУ и предоставляет в распоряжение польВ противном случае, соответствующем25 зователя дополнительный блок оперативной

заполнению БП 3, на выходе элемента И 33памяти.

образуется импульс UCT, попадающий на об-Формула изобретения нуляющий вход счетчика 15, обнуляя тем са-Устройство для идентификации паролей мым его содержимое г. Импульс UCT,пользователей, содержащее первый и вто- задержанный на ЭЗ 64 на время срабатыва-30 рой блоки памяти, группу цифровых компания счетчика 15, проходит через элементраторов, группу регистров, с первого по ИЛИ 49 на синхронизирующий вход 107 БПпятый счетчики, первый триггер, дешифра- 4, обеспечивая запись в R-ю строку матрицутор, группу элементов И, первый, третий, 89-92 кода строки S, сформулированной напятый и шестой элементы И, с первого по выходах 87, 88 БП 3. Задерживаясь на ЭЗ 6535 девятый элементы ИЛИ, с первого по один- на время срабатывания БП 4, импульс Us,надцатый элементы задержки, причем пер- образованный на выходе элемента ИЛИ 49,вый вход первого элемента И является попадает на счетные входы счетчиков 15 ипервым синхронизирующим входом устрой- 16, увеличивая тем самым на единицу значе-ства, информационные входы группы реги- ние каждого из кодов г и R, После этого40 стров являются первым информационным импульс Us, задержанный на ЭЗ 66 на времявходом устройства, единичный вход первого счета, проходит через один из элементов Итриггера является вторым синхронизиру- 36 и 37. Если на выходе переноса счетчикающим входом устройства, выход пятого 15 присутствует низкое значение потенциа-элемента И является первым синхронизи- ла, т.е. строка S была записана в БП 4, менее45 рующим выходом устройства, последние вы- чем Гмакс раз, то образуется импульс на вы-ходы первого блока памяти являются ходе элемента И 36, который проходит черезпервым информационным выходом устрой- элемент ИЛИ 49, порождая новый импульсства, вход первого элемента задержки сое- Us, обеспечивающий новую запись строки Sдинен с выходом первого элемента И, одни в БП 4 аналогично указанному выше. В про-50 входы элементов И группы подключены к тивном случае образуется импульс UR на вы-выходу первого элемента И, другие входы ходе элемента И 37. Если в БП 4 былоэлементов И группы соединены с соответст- записано ровно Рмакс строк, то на выходевующими выходами дешифратора, счетный переноса счетчика 16 формируется высокоевход первого счетчика подключен к выходу значение потенциала, разрешающее про-55 первого элемента задержки, информацион- хождение импульса UR через элемент И 38ный выход первого счетчика соединен с вхо- на синхронизирующий выход 77 устройства.дом дешифратора, выходы элементов И Импульс на выходе 77 применяется в качест-группы подключены к синхронизирующим ве СПР ВК, после приема которого ВК, ис-входам соответствующих регистров группы, пользуя вход 69 устройства, считывает кододни информационные входы цифровых

компараторов соединены с выходами соответствующих регистров группы, другие информационные входы цифровых компараторов подключены к соответствующим выходам первого блока памяти, прямые выходы цифровых компараторов соединены с одними входами пятого элемента И, инверсные выходы цифровых компараторов под- ключены к соответствующим входам третьего элемента ИЛИ, другой вход пятого элемента И соединен с выходом шестого элемента задержки, один вход шестого элемента И подключен к выходу третьего элемента ИЛИ, другой вход шестого элемента И соединен с выходом шестого элемента задержки, адресный вход первого блока памяти соединен с информационным выходом второго счетчика, вход второго элемента задержки подключен к второму синхронизирующему входу устройства, первый вход первого элемента ИЛИ соединен с выходом второго элемента задержки, обнуляющий вход первого триггера подключен к выходу первого элемента ИЛИ, второй вход первого элемента И соединен с выходом первого триггера, счетный вход третьего счетчика подключен к выходу второго элемента задержки, вход восьмого элемента задержки соединен с третьим синхронизирующим входом устройства и входом сброса четвертого счетчика, первый вход четвертого элемента ИЛИ подключен к выходу восьмого элемента задержки, выход четвертого элемента ИЛ И соединен со счетным входом четвертого счетчика, выход пятого элемента задержки подключен к синхронизирующим входам цифровых компараторов и входу шестого элемента задержки, отличающее- с я тем, что, с целью повышения быстродействия, в устройство введены третий и четвертый блоки памяти, регистр, пятый-восьмой счетчики, второй триггер, второй, третий, четвертый, седьмой-семнадцатый элементы И, десятый элемент ИЛИ, двенадцатый-сем- надцатый элементы задержки, причем адресный вход второго блока памяти является вторым информационным входом устройства, второй адресный вход четвертого блока памяти является третьим информационным входом устройства, выход восьмого элемента И является вторым синхронизирующим выходом устройства, выход шестнадцатого элемента И является третьим синхронизирующим выходом устройства, информационный выход четвертого блока памяти является вторым информационным выходом устройства, вход третьего элемента задержки соединен с выходом первого элемента задержки, один вход второго элемента ИЛИ подключен к выходу шестого элемента И,

выход второго элемента ИЛИ соединен с входом четвертого элемента задержки, один вход второго элемента И подключен к выходу переноса первого счетчика, другой вход

второго элемента И соединен с выходом третьего элемента задержки, выход второго элемента И подключен к другим входам первого и второго элементов ИЛИ и обнуляющему входу второго счетчика, выход переноса

0 второго счетчика соединен с инверсным входом третьего элемента И и одним входом четвертого элемента И, выход четвертого элемента задержки подключен к прямому входу третьего элемента И и другому входу

5 четвертого элемента И, выход третьего элемента И соединен с синхронизирующим входом первого блока памяти и входом пятого элемента задержки, выход четвертого элемента И подключен к второму входу четвер0 того элемента ИЛИ, выход седьмого элемента И соединен с третьим входом четвертого элемента ИЛИ, вход седьмого элемента задержки подключен к выходу второго элемента задержки, выход седьмого элемен5 та задержки соединен с одним входом седьмого элемента И, другой вход которого подключен к выходу переноса третьего счетчика, обнуляющий вход первого счетчика соединен с выходом четвертого элемента ИЛИ

0 и входом девятого элемента задержки, один вход восьмого элемента И соединен с выходом девятого элемента задержки, другой вход восьмого элемента И подключен к выходу переноса четвертого счетчика, первый

5 вход пятого элемента ИЛИ соединен с выходом первого элемента И, второй вход пятого элемента ИЛИ подключен к выходу второго элемента задержки, третий вход пятого элемента ИЛИ соединен с третьим синхронизи0 рующим входом устройства, выход пятого элемента ИЛИ подключен к обнуляющему входу восьмого счетчика, к обнуляющему входу второго триггера к первым входам шестого и седьмого элементов ИЛИ и входу

5 десятого элемента задержки, выход которого соединен с первым входом восьмого элемента ИЛИ, выход шестого элемента ИЛИ подключен к обнуляющему входу пятого счетчика, выход седьмого элемента ИЛИ со0 единен с обнуляющим входом шестого счетчика, информационный выход пятого счетчика подключен к адресному входу третьего блока памяти, выход переноса пятого счетчика соединен с одним входом

5 одиннадцатого элемента И и инверсным входом двенадцатого элемента И, выход переноса шестого счетчика подключен к одному входу девятого элемента И и инверсному входу десятого элемента И, выход девятого элемента И соединен с другим входом седьмого элемента ИЛИ, с другим входом одиннадцатого элемента И и прямым входом двенадцатого элемента И, выход десятого элемента И подключен к одному входу девятого элемента ИЛИ, выход которого соеди- нен с синхронизирующим входом третьего блока памяти, с одним входом тринадцатого элемента И и входом тринадцатого элемента задержки, выход которого подключен к входу четырнадцатого элемента задержки и счетным входам пятого и шестого счетчиков, выход четырнадцатого элемента задержки соединен с другим входом девятого элемента И и прямым входом десятого элемента И, выход одиннадцатого элемента И подклю- чен к входу пятнадцатого элемента задержки и обнуляющему входу седьмого счетчика, выход двенадцатого элемента И соединен с вторым входом восьмого элемента ИЛИ, выход которого подключен к синхронизирую- щему входу второго блока памяти и входу одиннадцатого элемента И задержки, информационный выход второго блока памяти соединен с информационным входом регистра, выход одиннадцатого элемента задер- жки подключен к синхронизирующему входу регистра и входу двенадцатого элемента задержки, один выход регистра соединен с другим входом тринадцатого элемента И, другие выходы регистра подключены к инфор- мационному входу третьего блока памяти, выход двенадцатого элемента задержки соединен с другим входом девятого элемента ИЛИ, информационные выходы третьего блока памяти подключены к соответствую- щим информационным входам четвертого

блока памяти, информационный выход восьмого счетчика соединен с первым адресным входом четвертого блока памяти, выход пятнадцатого элемента задержки подключен к первому входу десятого элемента ИЛИ, выход которого соединен с входом шестнадцатого элемента задержки и синхронизирующим входом четвертого блока памяти, выход шестнадцатого элемента задержки подключен к входу семнадцатого элемента задержки и счетным входам седьмого и восьмого счетчиков, выход переноса седьмого счетчика соединен с инверсным входом четырнадцатого элемента И и одним входом пятнадцатого элемента И, выход семнадцатого элемента задержки подключен к прямому входу четырнадцатого элемента И и другому входу пятнадцатого элемента И, выход четырнадцатого элемента И соединен с другим входом десятого элемента ИЛИ, выход переноса восьмого счетчика подключен к одному входу шестнадцатого элемента И и инверсному входу семнадцатого элемента И, выход пятнадцатого элемента И соединен с другим входом шестнадцатого элемента И и прямым входом семнадцатого элемента И, выход которого подключен к третьему входу восьмого элемента ИЛИ и другому входу шестого элемента ИЛИ, выход тринадцатого элемента И соединен с единичным входом второго триггера, выход которого подключен к третьему входу первого элемента И, счетный вход второго счетчика подключен к выходу шестого элемента И, обнуляющий вход третьего соединен с выходом четвертого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации паролей пользователей | 1990 |

|

SU1784961A1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| Устройство для идентификации паролей пользователей | 1989 |

|

SU1734108A2 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| Устройство для экспертной оценки экстремальных ситуаций | 1988 |

|

SU1550528A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1698885A1 |

| СИСТЕМА ОПОЗНАВАНИЯ "СВОЙ-ЧУЖОЙ" | 2000 |

|

RU2189610C1 |

| Устройство для вывода графической информации | 1990 |

|

SU1833858A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для управления памятью | 1977 |

|

SU748414A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к системам защиты ресурсов вычислительных комплексов от несанкционированного доступа, и может быть использовано для защи- ты системы ввода паролей. Целью изобретения является повышение быстродействия. Устройство содержит блоки 1-4 памяти, группу цифровых компараторов 5, 6, группу регистров 7, 8, счетчики 9-16, регистр 17, триггеры 18, 19, Дешифратор 20,

Фиг.2

II

CM

i t

| Устройство для идентификации паролей пользователей | 1987 |

|

SU1564608A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1990-01-25—Подача