рого соединен с четвертым выходом генератора тактовых импульсов, а второй выход блока восстановления формы сигнала - с третьим входом блока индикации.

2.Устройство по П.1, отличающееся тем, что, блок сокращения избыточности содержит первый регистр, вычитатель, первую схему сравнения и второй коммутатор, управляющий вход которого соединен с выходом первой схемы сравнения первый информационный вход которой является вторым входом блока, а второй информационньй вход соединен с выходом вычитателя, первый в&од которого соединен с информадионньм входом первого регистра и является первым входом блока, второй вход вычитателя подключен к выходу первого регистра и является вторым выходом блока, выход второго коммутатора соединен с установочным входом первого регистра и является первым выходом блока, информационный вход второго коммутатора является третьим входом блока.

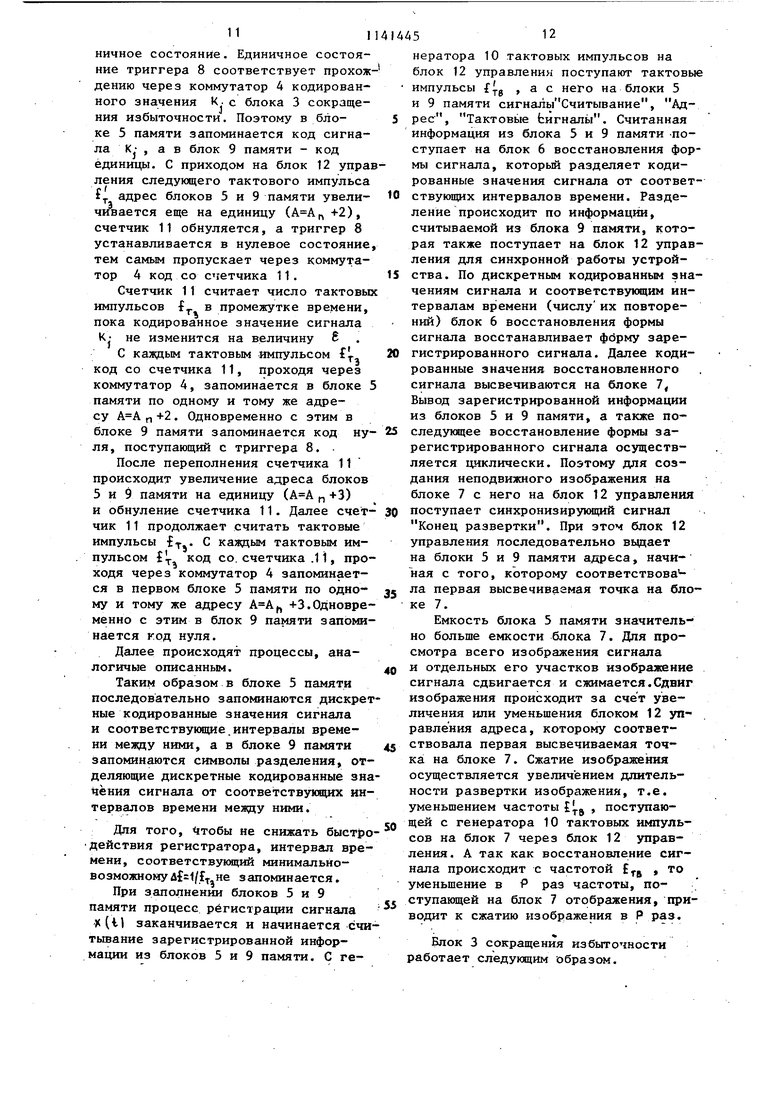

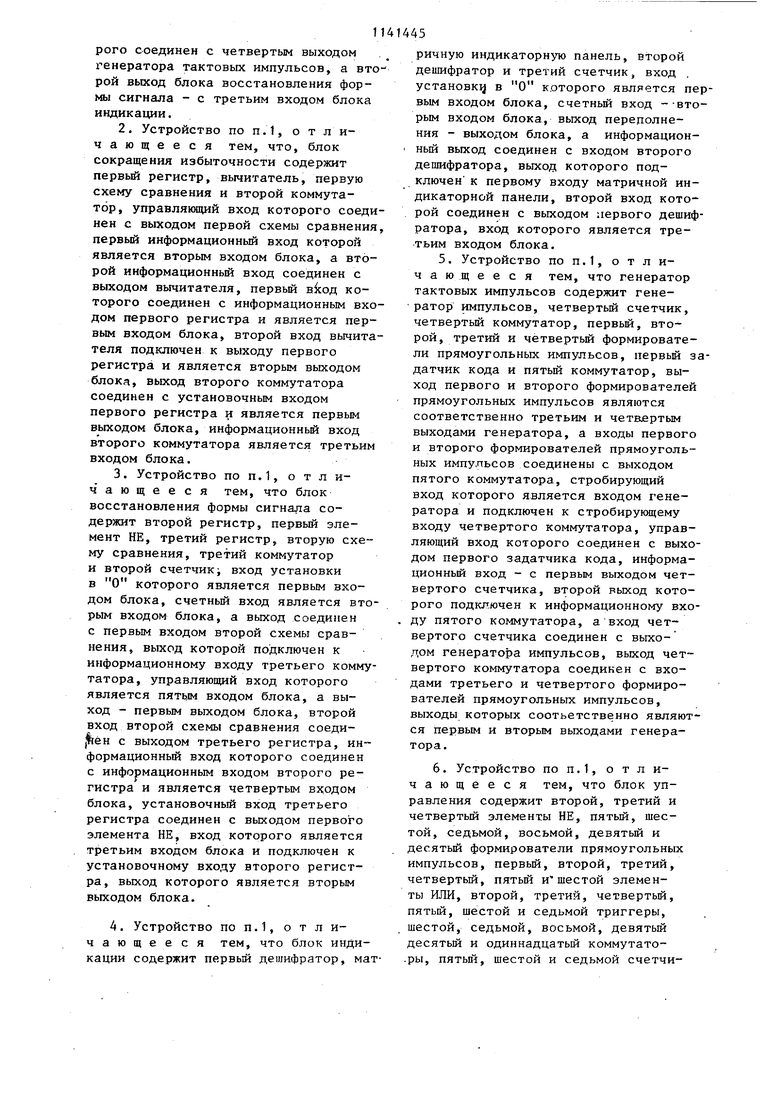

3.Устройство по П.1, о т л ичающееся тем, что блок восстановления формы сигнала содержит второй регистр, первый элемент НЕ, третий регистр, вторую схему сравнения, третий коммутатор

и второй счетчикi вход установки в О которого является первым входом блока, счетньй вход является вторым входом блока, а вьпсод соединен с первым входом второй схемы сравнения, выход которой подключен к информационному входу третьего коммутатора, управляющий вход которого является пятым входом блока, а выход - первым выходом блока, второй вход второй схемы сравнения соедирён с выходом третьего регистра, ин формационный вход которого соединен с информационным входом второго регистра и является четвертым входом блока, установочный вход третьего регистра соединен с выходом первого элемента НЕ, вход которого является третьим входом блока и подключен к установочному входу второго регистра, выход которого является вторым выходом блока.

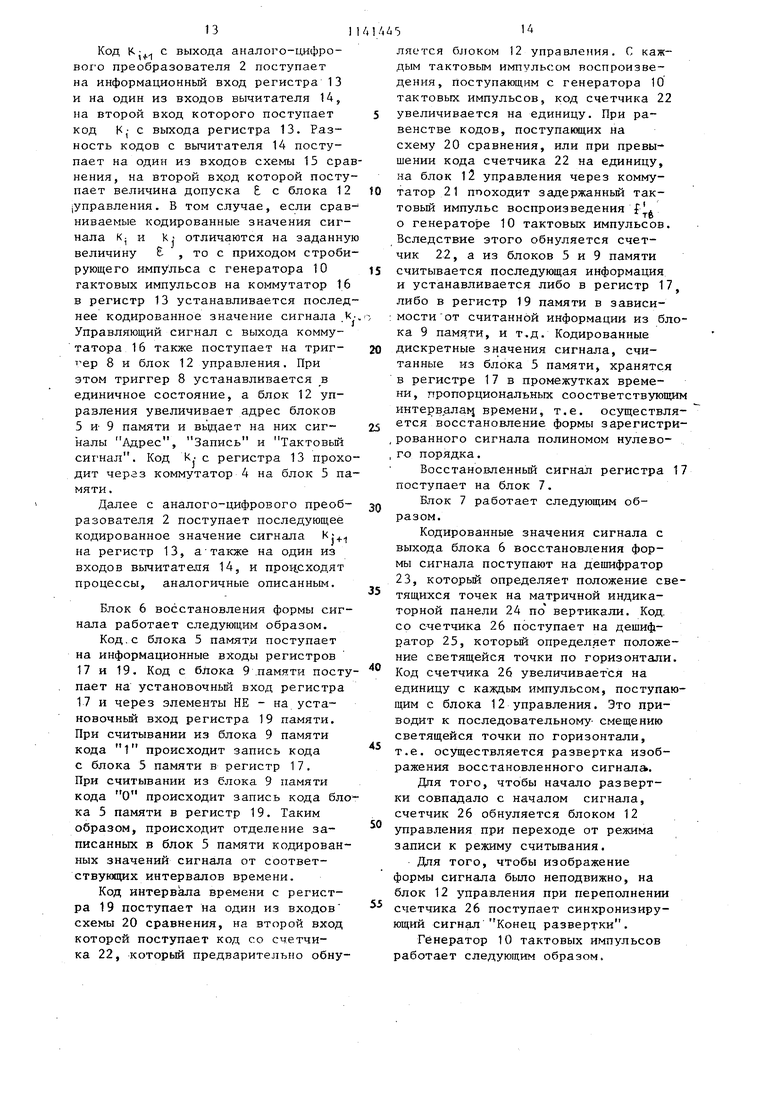

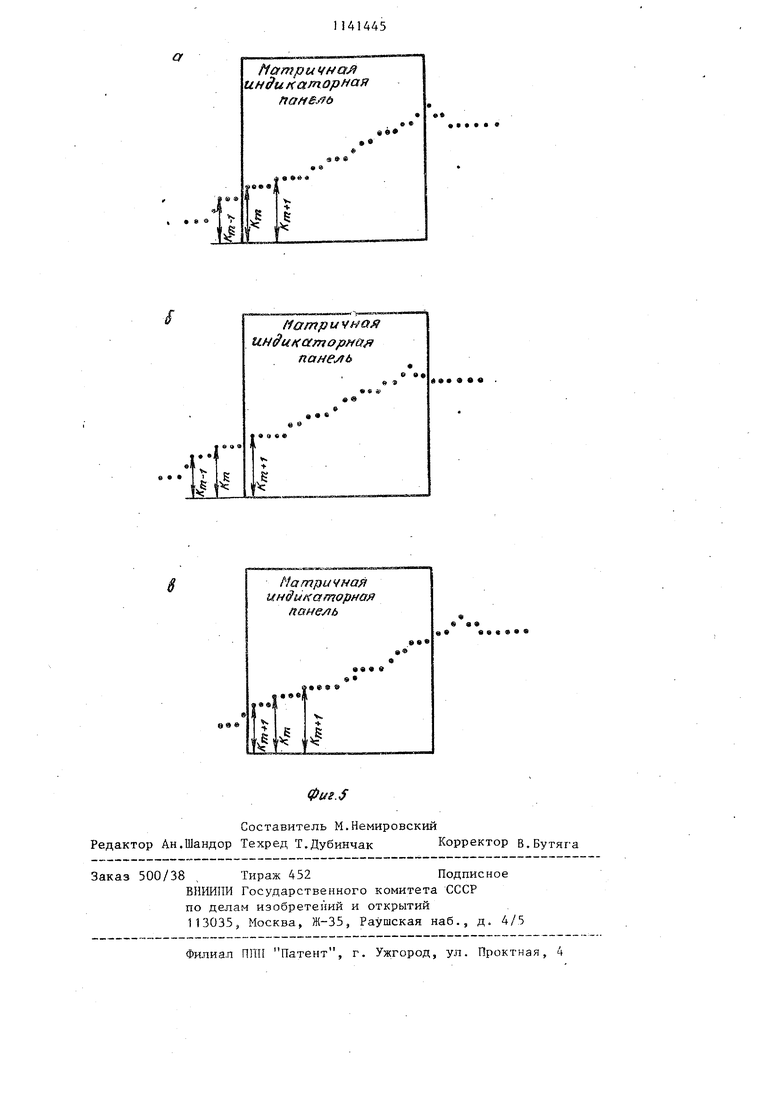

4.Устройство по П.1, отличающееся тем, что блок индикации содержит первый дешифратор, маричную индикаторную панель, второй дешифратор и третий счетчик, вход . установку в О которого является певым входом блока, счетньй вход - -вторым входом блока, выход переполнения - выходом блока, а информационный выход соединен с входом второго дешифратора, выход которого подключен к первому входу матричной индикаторной панели, второй вход которой соединен с выходом первого дешифратора, вход которого является третьим входом блока.

5.Устройство по П.1, о т л ичающееся тем, что генератор тактовых импульсов содержит генератор импульсов, четвертьй счетчик, четвертьй коммутатор, первьй, второй, третий и четвертьй формирователи прямоугольных импульсов, первьй здатчик кода и пятьй коммутатор, выход первого и второго формирователей прямоугольных импульсов являются соответственно третьим и четвертым выходами генератора, а входы первого

и второго формирователей прямоугольных импульсов соединены с выходом пятого коммутатора, стробирующий вход которого является входом генератора и подключен к стробирующему входу четвертого коммутатора, управляющий вход которого соединен с выходом первого задатчика кода, информационньй вход - с первым выходом четвертого счетчика, второй РЫХОД которого подключен к информационному входу пятого коммутатора, а вход четвертого счетчика соединен с выходом генератора импульсов, выход четвертого коммутатора соединен с входами третьего и четвертого формирователей прямоугольных импульсов, выходы которых соотьетственно являются первым и вторым выходами генератора.

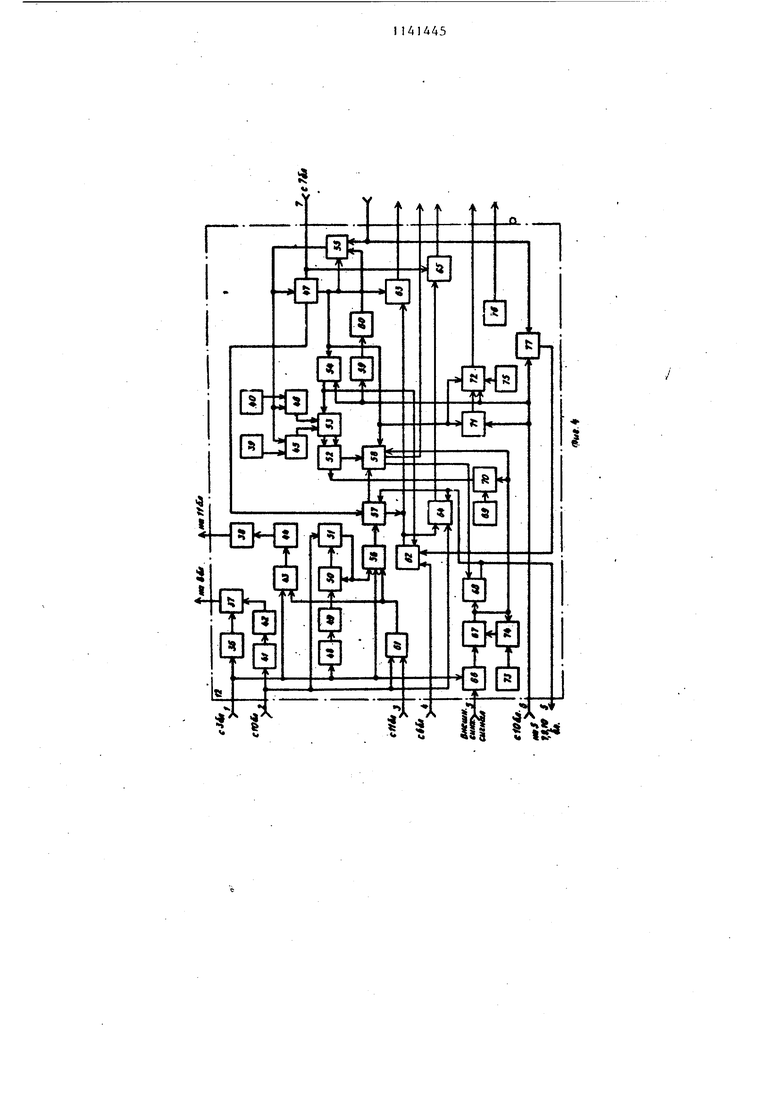

6.Устройство по П.1, отличающееся тем, что блок управления содержит второй, третий и четвертьй элементы НЕ, пятьй, шестой, седьмой, восьмой, девятьй и десятьй формирователи прямоугольных импульсов, первьй, второй, третий, четвертьй, пятьй и шестой элементы ИЛИ, второй, третий, четвертьй, пятьй, шестой и седьмой триггеры, шестой, седьмой, восьмой, девятьй десятьй и одиннадцатьй коммутато-ры, пятьй, шестой и седьмой счетчики, третий дешифратор, переключатель, второй и третий задатчики кода, первый второй, третий и четвертый элементы И, первый вход первого элемента И соединен с первым входом второго элемента И и является восьмым входом блока, второй вход второго элемента И соединен с первым входом третьего элемента И, . с входом пятого формирователя прямоугольных импульсов, с первым информационным входом шестого коммутатора, счетным входом пятого счетчика

И является шестым входом блока, выход второго элемента И соединен; с первым входом первого элемента ИЛИ, второй.вход которого является четвертым входом блока, третий вход первого элемента ИЛИ соединен со стробирующим входом третьего дешифратора и с выходом третьего элемента И, выход первого элемента. ИЛИ соединен с первыми информационными входами седьмого и восьмого коммутаторов и с первым входом второго элемента ИЛИ, выход которого является восьмым выходом блока, а второй вход соединен с вторыми входами первого и третьего элементов И, и с первым выходом второго триггера, с устанойленным выходом шестого счетчика, с входом установки в О пятого счетчика, со стробирующим входом шестого коммутатора, второй информационный вход которого подключен к выходу пятого счетчика, управляющий вход - к выходу второго задатчика кода, а выход шестого ко1ммутатора является шестым выходом блока, выход третьего задатчика кода является седьмым выходом блока, вход третьего элемента ИЛИ соединен с выходом девятого коммутатора с первыми входами третьего и четвертого триггеров, с входом установки в О шестого счетчика, выход третьего элемента ИЛИ подключен к входу установки в О седьмого счетчика, суммирующий и вычитающий входы которого соответственно соединены с соответствуюпщм выходом третьего дешифратора, а выход седьмого счетчика соединен с информационным входом шестого счетчика, информационный выход которого является четвертым выходом блока, выход переполнения

шестого счетчика соединен с вторым входом третьего триггера, а счетный вход - с выходом седьмого коммутато-- .

45

ра, первьй управляющий вход которо- : го подключен к управляющему входу восьмого коммутатора, к выходу третьего триггера и является вторым входом блока, второй управляющий вход седьмого коммутатора соединен с вторым выходом второго триггера, а второй информационньм вход - с выходом четвертого элемента ИЛИ, первьй вход которого подключен к выходу десятого коммутатора и к первому входу пятого элемента ИЛИ, второй вход - к первому входу переключателя, к второму входу пятого элемента ИЛИ, к входу второго элемс нта НЕ, к входу шестого формирователя прямоугольных импульсов и является первым входом блока, третий вход четвертого элемен та ИЛИ соединен с выходом одиннадцатого коммутатора и с первым входом пятого формирователя прямоугольньк импульсов, вход которого соединен с выходом седьмого формирователя прямоугольных импульсов, вход которого соединен с выходом шестого формирователя прямоугольных импульсов, выход пятого триггера подключен к управляющему входу одиннадцатого коммутатора, информационный вход которого соединение вторым информационным входом восьмого коммутатора, с информационным входом десятого коммутатора, с входом третьего элемента НЕ и является вторым входом блока, выход третьего элемента НЕ подключен к входу четвертого элемента НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом второго элемента НЕ, а выход является третьим выходом блока, выход пятого элемента ИЛИ соединен с , входом восьмого формирователя прямоугольных импульсов, выход которого соединен с входом девятого формирователя прямоугольных импульсов, выход которого является первым выходом блока, выход четвертого триггера соединен с управляющим входом девятого коммутатора, информагщонный вход которого подключен к выходу переключателя, второй вход которого является пятым входом блока, . , входы шестого и седьмого триггеров

соединены с вторым входом второго триггера и с выходом первого элемента И, третий вход которого соединен с выходом десятого формирователя прямоугольных импульсOB,соединенного с

J

ВЫХОДОМ пятого формирователя прямоугольных импульсов, выходы шестого и седьмого триггеров соединены с соответствукяцими информационными входами третьего дешифратора, выход восьмого коммутатора соединен с первым входом

1445

шестого элемента ИЛИ, второй вход которого соединен с первым входом второго триггера и является седьмым входом блока, а выход шестого элемента ИЛИ является пятым выходом блока, управляющий вход десятого коммутатора является третьим входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1784993A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983741A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для регистрации однократных процессов | 1980 |

|

SU959111A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

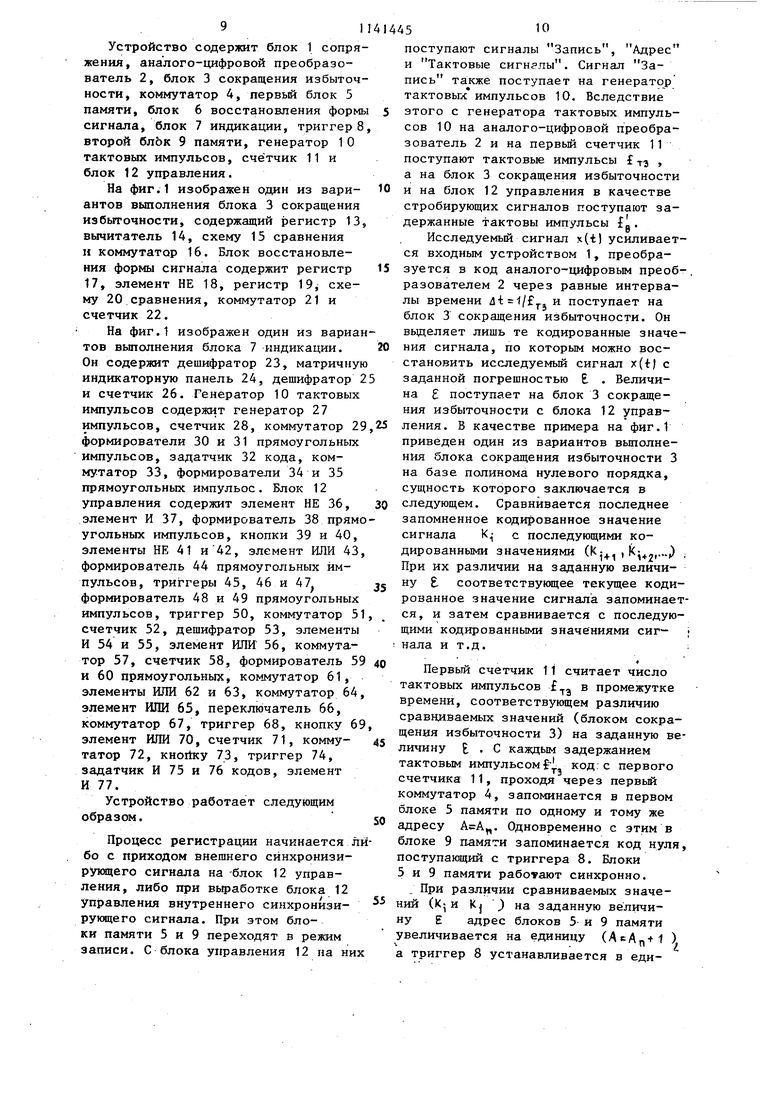

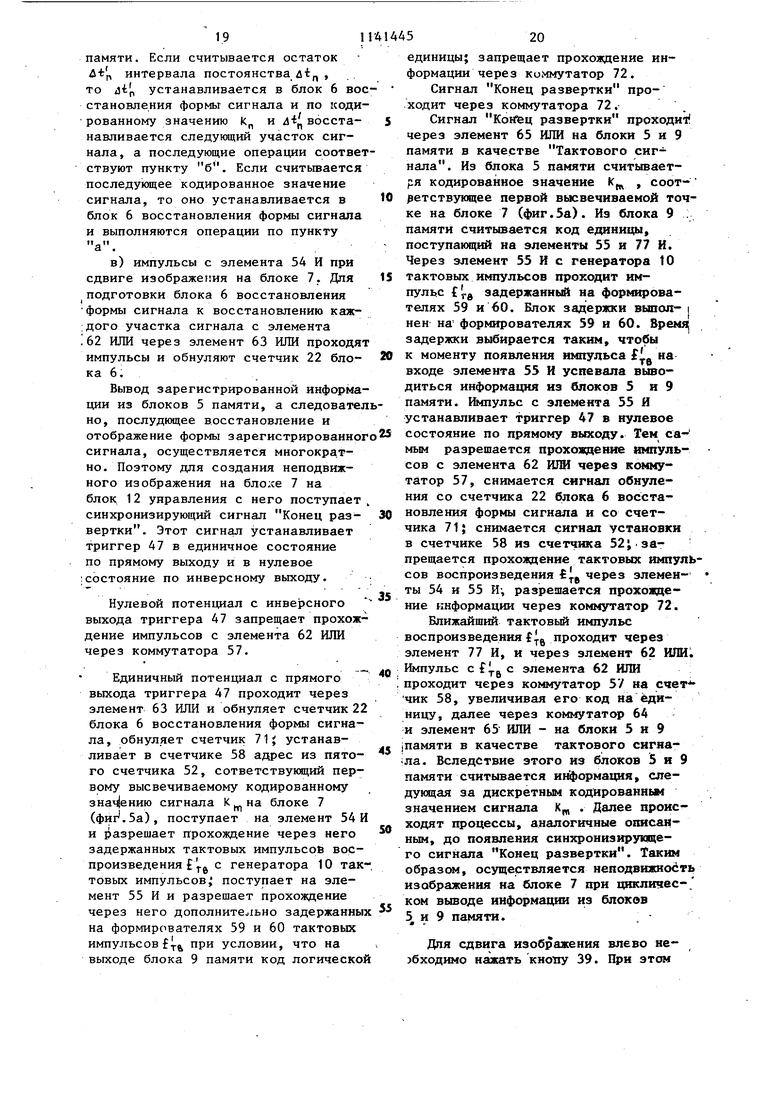

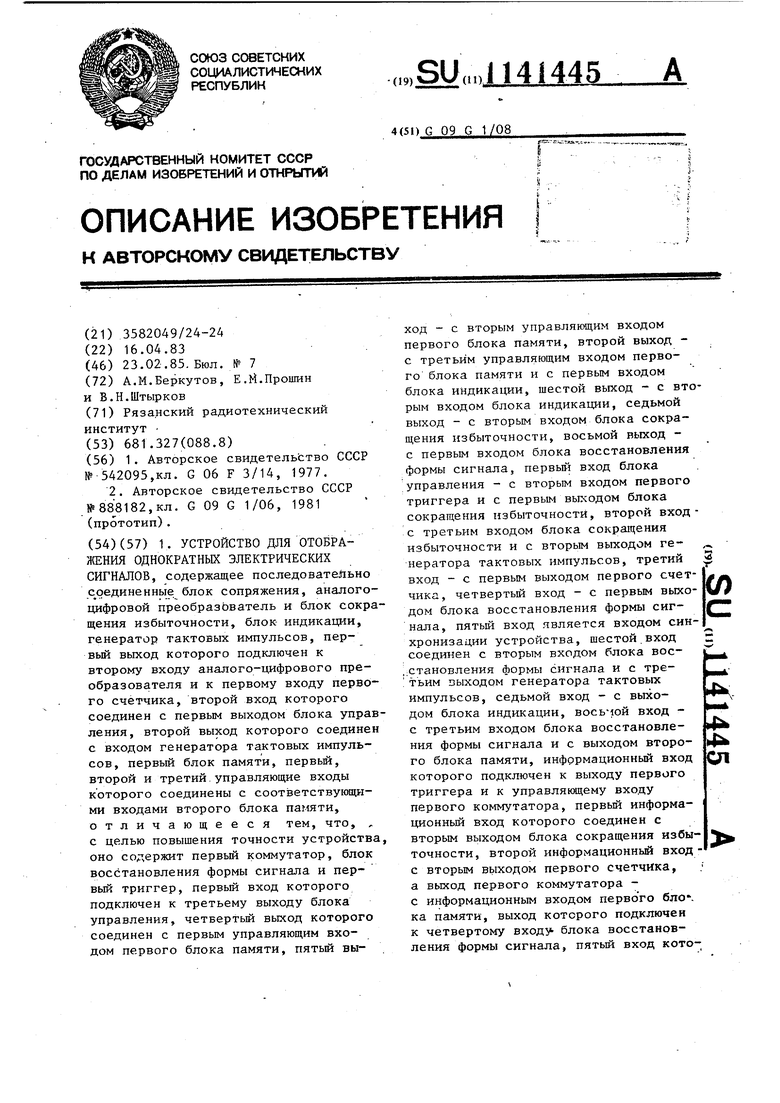

1. УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ОДНОКРАТНЫХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ, содержащее последоватейьно соединенные блок сопряжения, аналогоцифровой преобразЬватель и блок сокращения избыточности, блок индикации, генератор тактовых импульсов, первый выход которого подключен к второму входу аналого-цифрового преобразователя и к первому входу первого счетчика, второй вход которого соединен с первым выходом блока управления , второй выход которого соединен с входом генератора тактовых импульсов, первый блок памяти, первьй, второй и третий.управляющие входы которого соединены с соотзветствующими входами второго блока памяти, отличающееся тем, что, , с целью повышения точности устройства, оно содержит первый коммутатор, блок восстановления формы сигнала и первый триггер, первый вход которого подключен к третьему выходу блока управления, четвертьй выход которого соединен с первым управляющим входом первого блока памяти, пятый выход - с вторым управляющим входом первого блока памяти, второй выход с третьим управляющим входом первого блока памяти и с первым входом блока индикации, шестой выход - с вторым входом блока индикации, седьмой выход - с вторым входом блока сокращения избыточности, восьмой выход с первым входом блока восстановления формы сигнала, первый вход блока управления - с вторым входом первого триггера и с первым выходом блока сокращения избыточности, второй вход с третьим входом блока сокращения избыточности и с вторым выходом генератора тактовых импульсов, третий вход - с первым выходом первого счет(Л чика, четвертый вход - с первым выходом блока восстановления формы сигнала, пятьй вход является входом синхронизации устройства, шестой.вход соединен с вторым входом блока вос,;Становления формы сигнала и с тре;тьим выходом генератора тактовых импульсов, седьмой вход - с выходом блока индикации, восьмой вход 4: 4i с третьим входом блока восстановления формы сигнала и с выходом второСП го блока памяти, инфррмационный вход которого подключен к выходу первого триггера и к управляющему входу первого коммутатора, первый информационный вход которого соединен с вторым выходом блока сокращения избыточности, второй информационный входс вторым выходом первого счетчика, а выход первого коммутатора с информационным входом первого бло. ка памяти, выход которого подключен к четвертому входу блока восстановления формы сигнала, пятый вход кото

f

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для отображения однократных электрических сигналов.

Известно устройство отображения формы однократных электрических сигналов, содержащее входной усилитель, аналого-цифровой преобразователь, преобразователь кодов, матричную индикаторную панель, распределитель, счетчик, дешифратор, делитель, двухчастотньш генератор, два коммутатора частот,,коммутатор, режимов, два триггера, сумматор, блок запрета, переключатель, связанные между собой и с блоком -управления определенным o6pa3OMflJ.

Недостатком устройства является большая емкость памяти, необходимая для регистрации исследуемого сигнала с высокой точностью.

Наиболее близким решением по технической сущности и достигаемому результату к изобретению является устройство отображения информации, содержащее последовательно соединенные усилитель, аналого-цифровой преобразователь, первую схему сравнения первый блок памяти, подключенньй к второму блоку памяти, и индикатор, первый реверсивньй счетчик, первый выход которого соединен с другим входом индикатора, второй выход - с вторыми входами первого и второго блоков памяти и один из входов первого реверсивного счетчика, генератор импульсов, первьй выход которого соединен с вторым входом анадого-цифрового преобразователя, второй выход - с другим входом первого реверсивного счетчика, блок управления, первый выход

которого соединен с одним из входов генератора импульсов, второй выход - с третьим входом аналогоцифрового преобразователя, содержит вторую и третью схемы сравнения, первьй и второй элементы ИЛИ, счетчик и второй реверсивньй счетчик, первьй вход которого соединен с первым выходом генератора импульсов, второй вход - с одним из выходов второго блока памяти и первым входом второй схемы сравнения, третий вход - с третьим выходом блока управления, четвертьй вход - с вторым выходом первого реверсивного счетчика, пятьй вход - с выходом второй схемы сравнения с одним из входов певого элемента ИЛИ, первьй выход с одним из входов второго элемента ИЛИ, второй выход - с первым входом второго блока памяти, третий выход - с другим входом первого элемента ИЛИ, другой вход второго элемента ИЛИ, соединен с другим выходом первой схемы сравнения, выход - с четвертыми в содами первого и второго блоков памяти, другой вход второй схемы сравнения подключен к второму выходу первого реверсивного счетчика, выход первого элемента ИЛИ соединен с третьим выходами первого и второго блоков памяти, первьй вход счетчика подключен к выходу третьей схемы сравнения, второй вход - к другому выходу второго блока памяти, третий вход - к третьему выходу генератора импульсов, выход - к другому входу генератора импульсов.

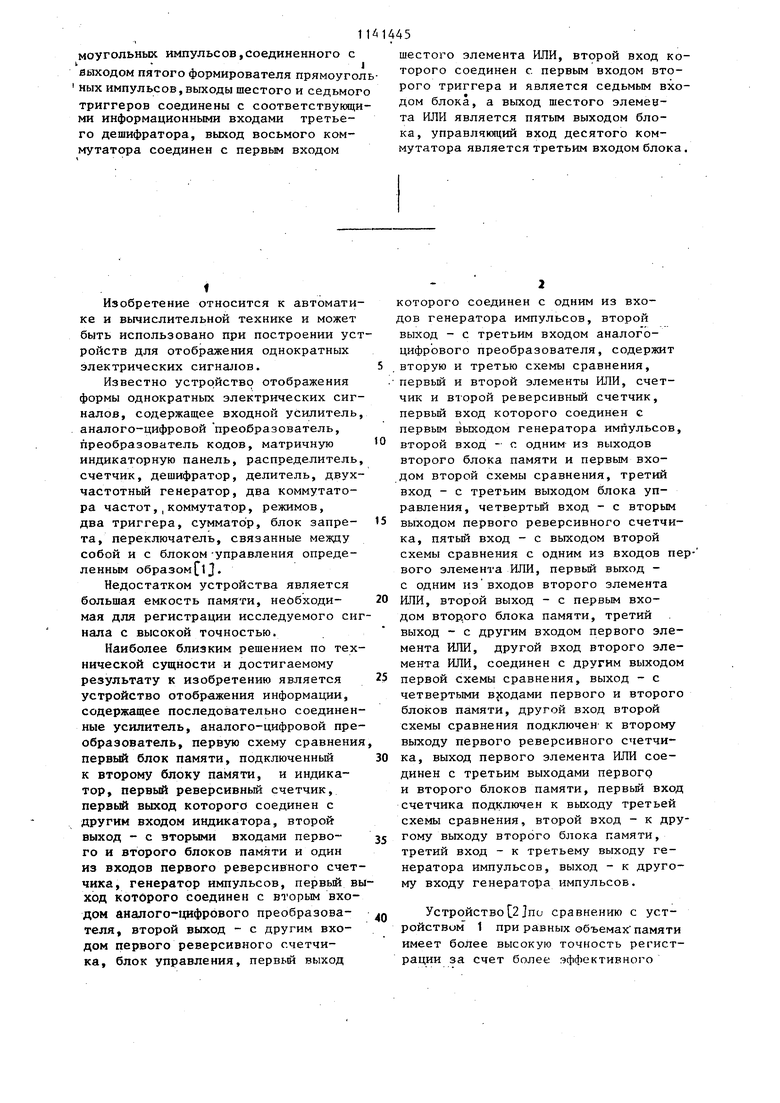

Устройство 2 по сравнению с устройством 1 при равных объемахпамяти имеет боЛее высокую точность регистрации за счет более эффективного использования объема памяти. Чем эффективнее используется объем памяти регистрирующего устройства тем больше запоминается информации об исследуемом сигнале, а это в свою очередь приводит к повьпиению точности регист рации. Более эффективное использование памяти устройства 21 достигается сокращением избыточных кодированных значений сигналов - записью кодированных значений сигнала и числа их последовательных повторений12 Недостатком этого устройства является низкая точность регистрации з счет низкой эффективности использования объема памяти, вызванной следующим: с записью кодированных значений сигнала, отстоящих друг от друга на интервале дискретизации dt-l/f-P , требуется запоминать интервал времени ut f/fyj (число повторений равное едийице); при каждом переполнении счетчика 8, измеряющего интервал времени в течение которого кодированные значения не разливаются требуется запоминать соответствующие кодированные значения сигналаi жесткое разделение объе ма памяти под запись кодированных значений сигнала и соответствующих интервалов времени. Целью изобретения является повышение точности устройства. Поставленная цель достигается тем что устройство для регистрации и отображения однократных эл1ектрически сигналов, содержащее последовательно соединенные блок сопряжения, аналого цифровой преобразователь и блок сокращения избыточности, блок индикации, генератор тактовых импульсов, первый выход которого подключен к второму входу аналого-цифрового преобразователя и к первому входу перво го счетчика, второй вход которого соединен с первым выходом блока упра ления, второй выход которого соедине с входом генератора тактовых импульсов, первый, второй и третий управляющие входы первого блока памяти соединены с соответствующими входами второго блока памяти, содержит первьй коммутатор, бйок восстановления формы сигнала, первый триггер, первьй вход которого подключен к третьему выходу блока управления, четвертьй выход которого соединен с первым управляющим входом первого блока памяти, пятый выход - с вторым управляющим входом первого блока памяти, второй выход - с третьим управляющим входом первого блока памяти и с первым входом блока индикации, шестой выход - с вторым входом блока индикации, седьмой выход - с вторым входом блока сокращения избыточности, восьмой выход - с -первьм . входом блока восстановления формы сигнала, первый вход блока управления - с вторым входом первого триггера и с первым выходом блока сокращения избыточности, второй вход - с третьим входом блока сокращения избыточности с вторым выходом генератора тактовых импульсов, третий вход с первым выходом первого счегчика, четвертьй вход - с первым выходом блока восстановления формы сигнала, пятьш вход - является входом синхронизации1,шестой вход соединен с вторым входом блока восстановления формы сигнала и с третьим выходом генератора тактовых импульсов, седьмой.вход - с выходом блока отображения, восьмой вход - с третьим входом блока восстановления формы сигнала и с выходом второго блока памяти, информационньй вход которого подключен к выходу первого триггера и к управляющему входу первого коммутатора, первьй информационньй вход которого соединен с вторым выходом блока сокращения избыточности, второй информационньй вход - с вторым выходом первого счетчика,а вы- ход первого коммутатора - с информационным входом первого блока памяти, выход которого подключен к четвертому входу блока восстановления формы сигнала, пятьй вход которого соединен с четвертым выходом генератора тактовых импульсов, а второй выход блока восстановления формы сигнала - с тертьим входом блока индикации . При этом блок индикации сокращения избыточности содержит .первьй регистр, вычитатель, первую схему сравнения и второй коммутатор, управляющий вход которого соединен с выходом первой схемы сравнения, первьй информационньй вход которой является вторым входом блрка, а второй информационньй вход соединен с выходом вычитателя, первьй вход которого соединен с информационным

входом первого регистра и является первым входом блока, второг вход вычитателя подключен к выходу первого регистра памяти и является вторым выходом блока, выход второго , 5 коммутатора соединен с установочным входом первого регистра и является первым выходом блока, информационный вход второго коммутатора является третьим входом блока.О

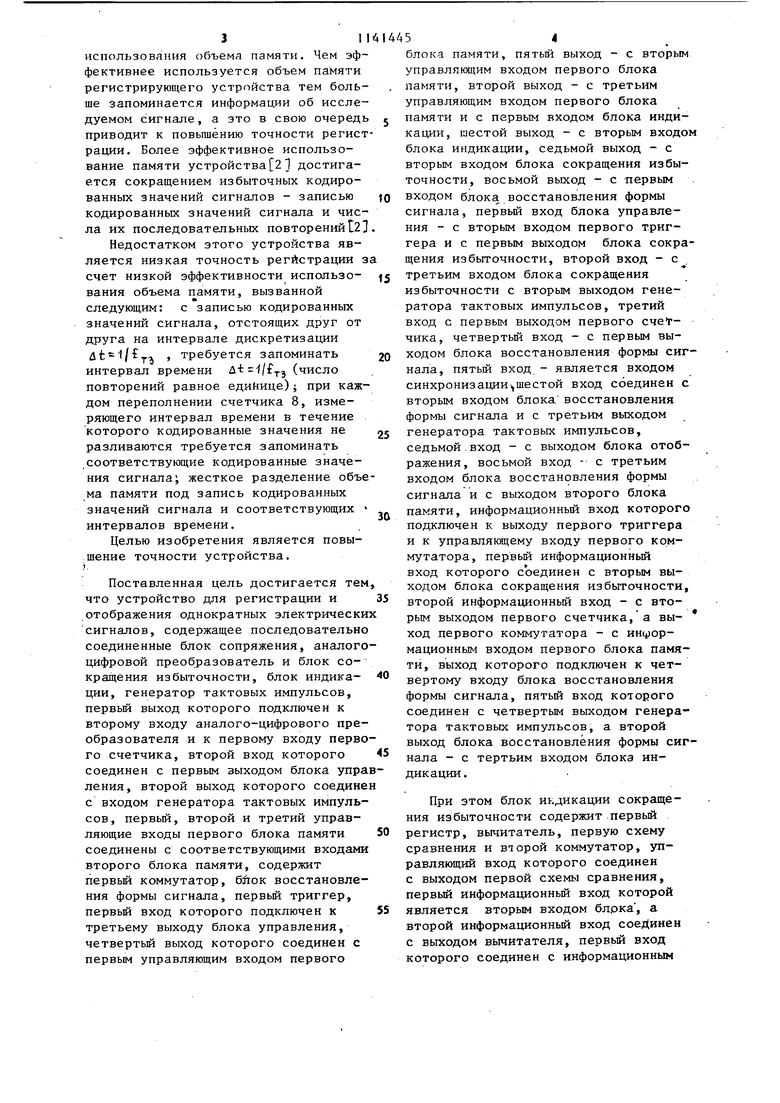

Причем блок восстановления формы сигнала содержит второй регистр, первьй элемент НЕ третий регистр, вторую схему сравнения, третий коммутатор и второй счетчик, вход 15 установки и О которого является первым входом блока, счетньм вход является вторым входом блока, а выход соединен с первым входом второй схемы сравнения, выход которой 20 подключен к информационному входу третьего коммутатора, управляющий вход которого является пятым входом блока, а выход - первым выходом блока, второй вход второй схемы . 25 сравнения соединен с выходом третьего регистра, информационньй вход которого соединен с информационным входом второго регистра и является четвертым входом блока, ус- 30

тановочньй вход третьего регистра соединен с выходом первого элемента НЕ, вход которого является третьим входом блока и подключен к установочному входу второго регист- ., ра, выход которого является вторым выходом блока.

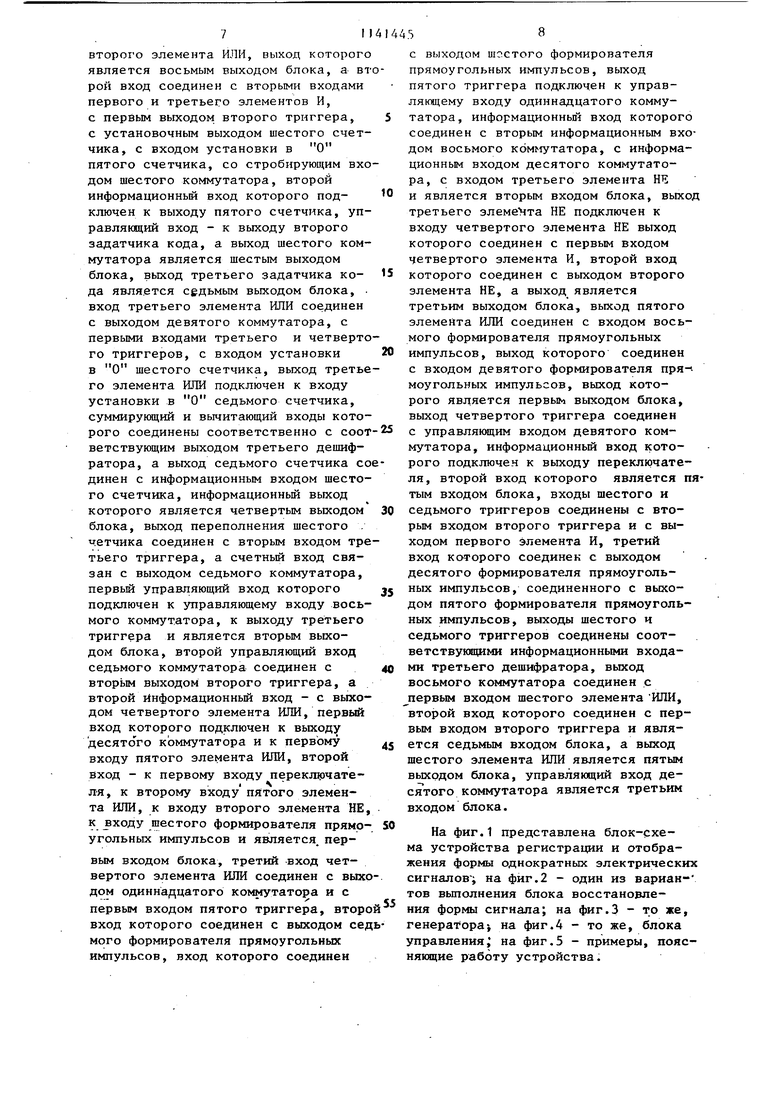

Блок индикации содержит первый дешифратор, матричную индикаторную. панель, второй дешифратор и третий Q счетчик, вход установки в О которого является первым входомблока, счетньй вход - вторым входом блока, выход переполнения - выходом блока, а информационньй выход соединен д с входом второго дешифратора, выход которого подключен к первому входу матричной индикаторной панели, второй вход которой соединен с выходом первого дешифратора вход которого JQ является третьим входом блока.

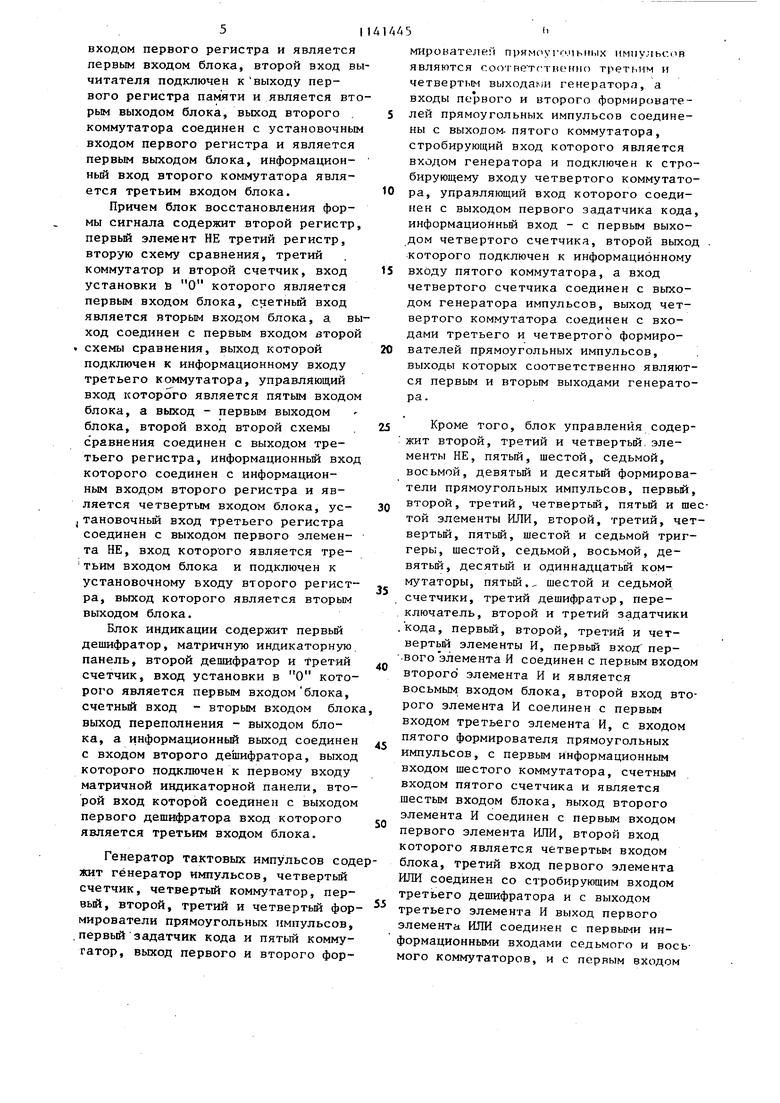

Генератор тактовых импульсов содержит генератор импульсов, четвертьй счетчик, четвертый коммутатор, первьй, второй, третий и четвертьй формирователи прямоугольных импульсов, первьй задатчик кода и пятый коммутатор, выход первого и второго формирователеГ прямоу гс-льных импульсов являются соотнетстнешк) третг,им и четвертым выходами генератора, а входы первого и второго формирователей прямоугольных импульсов соединены с выходом, пятого коммутатора, стробирующий вход которого является входом генератора и подключен к стробирующему входу четвертого коммутатора, управляющий вход которого соединен с выходом первого задатчика кода информационньй вход - с первым выходом четвертого счетчика, второй выход которого подключен к информационному входу пятого коммутатора, а вход четвертого счетчика соединен с выходом генератора импульсов, выход четвертого коммутатора соединен с входами третьего и четвертого формирователей прямоугольных импульсов, выходы которых соответственно являются первым и вторым выходами генератора.

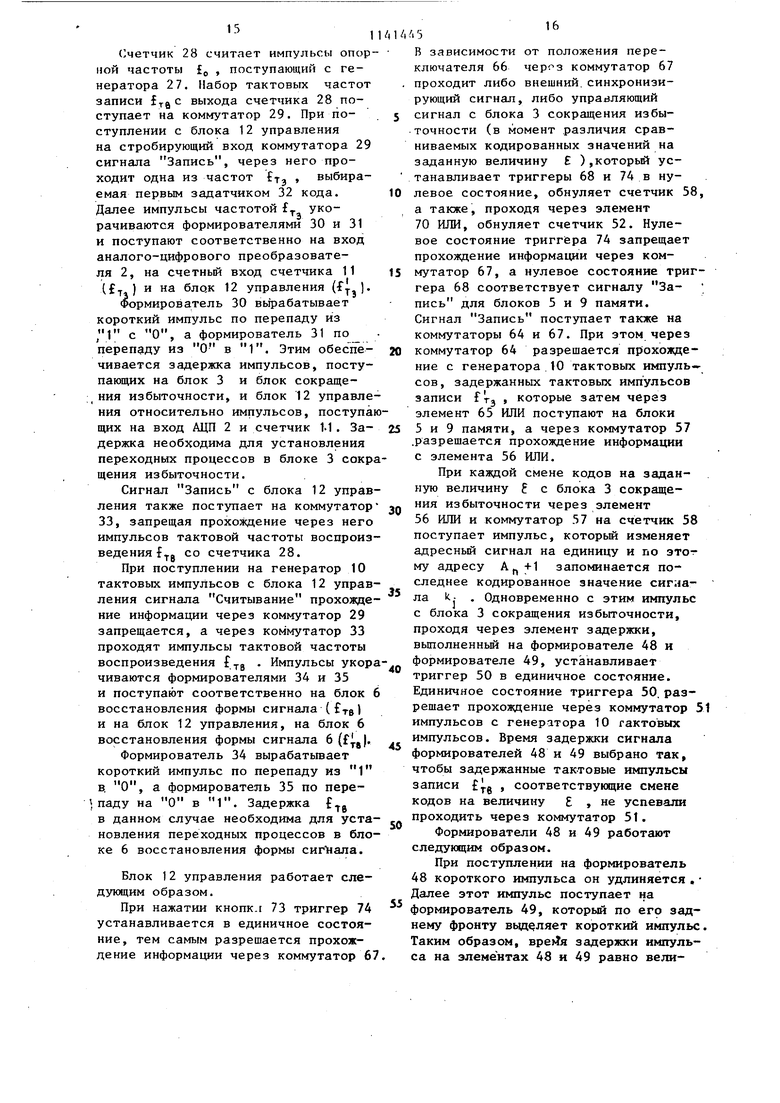

Кроме того, блок управления содержит второй, третий и четвертьй,элементы НЕ, пятый, шестой, седьмой, восьмой, девятьй и десятьй формирователи прямоугольных импульсов, первьй второй, третий, четвертьй, пятьй и шетой элементы ИЛИ, второй, третий, четвертьй, пятьй, шестой и седьмой триггеры, шестой, седьмой, восьмой, девятьй, десятьй и одиннадцатьй коммутаторы, пятьй,, шестой и седьмой счетчики, третий дешифратор, переключатель, второй и третий задатчики .кода, первьй, второй, третий и четвертьй элементы И, первьй вход первого элемента И соединен с первым входо второго элемента И и является восьмым входом блока, второй вход второго элемента И соединен с первым входом третьего элемента И, с входом пятого формирователя прямоугольных импульсов, с первым информационным входом шестого коммутатора, счетным входом пятого счетчика и является шестым входом блока, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого является четвертым входом блока, третий вход первого элемента ИЛИ соединен со стробирующим входом третьего дешифратора и с выходом третьего элемента И выход первого элемента ИЛИ соединен с первыми информационными входами седьмого и восьмого коммутаторов, и с первым входом 71 второго элемента ИЛИ, выход которого является восьмым выходом блока, а вт рой вход соединен с вторыми входами первого и третьего элементов И, с первым выходом второго триггера, с установочным выходом шестого счетчика, с входом установки в О пятого счетчика, со стробирующим вхо дом шестого коммутатора, второй информационный вход которого подключен к выходу пятого счетчика, управлякщий вход - к выходу второго задатчика кода, а выход шестого коммутатора является шестым выходом блока, выход третьего задатчика кода является седьмым выходом блока, вход третьего элемента ИЛИ соединен с выходом девятого коммутатора, с первыми входами третьего и четверто го триггеров, с входом установки в О шестого счетчика, выход третье го элемента ИЛИ подключен к входу установки в О седьмого счетчика, суммирующий и вычитающий входы которого соединены соответственно с соот ветствующим выходом третьего дешиф- ратора, а выход седьмого счетчика со динен с информационным входом шестого счетчика, информационный выход которого является четвертым выходом блока, выход переполнения шестого . четчика соединен с вторым входом тре тьего триггера, а счетный вход связан с выходом седьмого коммутатора, первьм управляющий вход которого подключен к управляющему входу восьмого коммутатора, к выходу третьего триггера и является вторым выходом блока, второй управляющий вход седьмого коммутатора соединен с вторьм выходом второго триггера, а второй йнформационньй вход - с выходом четвертого элемента ИЛИ, первый вход которого подключен к выходу десятого коммутатора и к первому входу пятого элемента ИЛИ, второй первому входу переключатевход - к второму входу пятого элемента ИЛИ, к входу второго элемента НЕ к ходу шестого формирователя прямоугольных импульсов и является, первым входом блока, третий вход четвертого элемента ИЛИ соединен с выхо дом одиннадцатого коммутатора и с первым входом пятого триггера, второ вход которого соединен с выходом сед мого формирователя прямоугольных импульсов, вход которого соединен 5 с выходом шестого формирователя прямоугольных импульсов, выход пятого триггера подключен к управлякщему входу одиннадцатого коммутатора, информационньш вход которого соединен с вторым информационным входом восьмого коммутатора, с информационным входом десятого коммутатора, с входом третьего элемента НЕ и является вторым входом блока, выход третьего элемента НЕ подключен к входу четвертого элемента НЕ выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом второго элемента НЕ, а выход является третьим выходом блока, выход пятого элемента ИЛИ соединен с входом восьмого формирователя прямоугольных импульсов, выход которого соединен с входом девятого формирователя пря-моугольных импульсов, выход которого является первым выходом блока, выход четвертого триггера соединен с управлякнцим входом девятого коммутатора, информационный вход которого подключен к выходу переключателя, второй вход которого является пятым входом блока, входы шестого и седьмого триггеров соединены с вторым входом второго триггера и с выходом первого элемента И, третий вход которого соединен с выходом десятого формирователя прямоугольных импульсов, соединенного с выходом пятого формирователя прямоугольных импульсов, выходы шестого и седьмого триггеров соединены соответствующими информационными входами третьего дешифратора, выход восьмого коммутатора соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с первым входом второго триггера и является седьмым входом блока, а выход шестого элемента ИЛИ является пятым выходом блока, управляющий вход деся того коммутатора является третьим входом блока. На фиг.1 представлена блок-схема устройства регистрации и отображения формы однократных электрических сигналов на фиг.2 - один из вариантов вьтолнения блока восстановления формы сигнала; на фиг.З - то же, генератораi на фиг.4 - то же, блока управления; на фиг.З - примеры, поясняющие работу устройства. Устройство содержит блок 1 сопря жения, аналого-цифровой преобразователь 2, блок 3 сокращения избыточ ности, коммутатор 4, первьй блок 5 памяти, блок 6 восстановления форм сигнала, блок 7 индикации, триггере второй блЬк 9 памяти, генератор 10 тактовых импульсов, счётчик 11 и блок 12 управления. На фиг.1 изображен один из вариантов выполнения блока 3 сокращения избыточности, содержащий регистр 13 вычитатель 14, схему 15 сравнения и коммутатор 16. Блок восстановления формы сигнала содержит регистр 17, элемент НЕ 18, регистр 19 схему 20 сравнения, коммутатор 21 и счетчик 22. На фит.1 изображен один из вариа тов выполнения блока 7 индикации. Он содержит дешифратор 23, матричну индикаторную панель 24, дешифратор и счетчик 26. Генератор 10 тактовых импульсов содержит генератор 27 импульсов, счетчик 28, коммутатор 2 формирователи 30 и 31 прямоугольных импульсов, задатчик 32 кода, коммутатор 33, формирователи 34 и 35 прямоугольных импульос. Блок 12 управления содержит элемент НЕ 36, элемент И 37, формирователь 38 прям угольных импульсов, кнопки 39 и 40, элементы НЕ 41 и42, элемент ИЛИ 43 формирователь 44 прямоугольных импульсов, триггеры 45, 46 и 47 формирователь 48 и 49 прямоугольных импульсов, триггер 50, коммутатор 5 счетчик 52, дешифратор 53, элементы И 54 и 55, элемент ИЛИ 56, коммутатор 37, счетчик 58, формирователь 5 и 60 прямоугольных, коммутатор 61, элементы ИЛИ 62 и 63, коммутатор 64 элемент ИЛИ 65, переключатель 66, коммутатор 67, триггер 68, кнопку 6 элемент ИЛИ 70, счетчик 71, коммутатор 72, кнойку 73, триггер 74, задатчик И 75 и 76 кодов, элемент И 77. Устройство работает следующим образом. Процесс регистрации начинается л бо с приходом внешнего синхронизирующего сигнала на -блок 12 управления, либо при выработке блока 12 Управления внутреннего синхронйзирукяцего сигнала. При этом блоки памяти 5 и 9 переходят в режим записи. С блока утфавления 12 на ни 5 поступают сигналы Запись, Адрес и Тактовые сигналы. Сигнал Запись также поступает на генератор тактовых импульсов 10. Вследствие этого с генератора тактовых импульсов 10 на аналого-цифровой преобразователь 2 и на первый счетчик 11 поступают тактовые импульсы тэ а на блок 3 сокращения избыточности и на блок 12 управления в качестве стробирующих сигналов поступают задержанные тактовы импульсы fg. Исследуемый сигнал x(t) усиливается входным устройством 1, преобразуется в код аналого-цифровым преоб-. разователем 2 через равные интервалы времени ui-ijf и поступает на блок 3 сокращения избыточности. Он Бьщеляет лишь те кодированные значения сигнала, по которым можно восстановить исследуемый сигнал х(:) с заданной погрешностью Е. . Величина поступает на блок 3 сокращения избыточности с блока 12 управления. В качестве примера на фиг.1 приведен один из вариантов вьшолнения блока сокращения избыточности 3 на базе полинома нулевого порядка, сущность которого заключается в следующем. Сравнивается последнее запомненное кодированное значение сигнала с последующими кодированными значениями (К:, ) К.,...,) При их различии на заданную величину соответствующее текущее кодированное значение сигнала запоминается, и затем сравнивается с последующими кодированными значениями сиг- нала и т.д.; . Первый счетчик 11 считает число тактовых импульсов f в промежутке времени, соответствующем различию сравниваемых значений (блоком сокращения избыточности 3) на заданную величину Е. . С каждым задержанием тактовым импульсом - : код. с первого счетчика 11, проходя через первьй коммутатор 4, запоминается в первом блоке 5 памяти по одному и тому же адресу . Одновременно с этим в блоке 9 памяти запоминается код нуля, поступающий с триггера 8. Блоки 5 и 9 памяти работают синхронно. При различии сравниваемых значений (К-и Kj ) на заданную величину Е адрес блоков 5 и 9 памяти увеличивается на единицу (AcAn+l ) .Z а триггер В устанавливается в единичное состояние. Единичное состояние триггера 8 соответствует прохож дению через коммутатор 4 кодированного значения К. с блока 3 сокращения избыточности. Поэтому в блоке 5 памяти запоминается код сигнала К- , а в блок 9 памяти - код единицы. С приходом на блок 12 упра ления следукицего тактового импульса f адрес блоков 5 и 9 памяти увеличивается еще на единицу ( +2), счетчик 11 обнуляется, а триггер 8 устанавливается в нулевое состояние тем самым пропускает через коммутатор 4 код со счетчика 11. Счетчик 11 считает число тактовы импульсов f в промежутке времени, пока кодированное значение сигнала К- не изменится на величину 6 С каждым тактовым импульсом fL код со счетчика 11, проходя через коммутатор 4, запоминается в блоке памяти по одному и тому же адресу п+2. Одновременно с этим в блоке 9 памяти запоминается код ну ля, поступающий с триггера 8. После переполнения счетчика 11 происходит увеличение адреса блоков 5 и 9 памяти на единицу ( „ +3) и обнуление счетчика 11. Далее счет чик 11 продолжает считать тактовые импульсы f.- С каядым тактовым импульсом fL код со. счетчика .11, про ходя через коммутатор 4 запоминается в первом блоке 5 памяти по одному и тому же адресу , +3.Одновре менно с этим в блок 9 памяти запоми нается код нуля. Далее происходят процессы, аналогичые описанным. Таким образом в блоке 5 памяти последовательно запоминаются дискре ные кодированные значения сигнала и соответствующие.интервалы времени между ними, а в блоке 9 памяти запоминаются символы разделения, от деляющие дискретные кодированные зн чения сигнала от соответствующих ин тервалов времени меяду ними. Для того, тобы не снижать быстро действия регистратора, интервал времени, соответствукидий минимальновозможному л 1/Цне запоминается. При заполнении блоков 5 и 9 памяти процесс регистрации сигнала X(i) заканчивается и начинается счи тьшание зарегистрированной информации из блоков 5 и 9 памяти. С ге512нератора 10 тактовых импульсов на блок 12 управлении поступают тактовые импульсы , а с него на блоки 5 и 9 памяти сигналы Считывание, Адрее, TaKTOBbie Ьигналы. Считанная информация из блока 5 и 9 памяти поступает на блок 6 восстановления формы сигнала, которьш разделяет кодированные значения сигнала от соответствующих интервалов времени. Разделение происходит по информации, считываемой из блока 9 памяти, которая также поступает на блок 12 управления для синхронной работы устройства. По дискретным кодированным значениям сигнала и соответствующим интервалам времени (числу их повторений) блок 6 восстановления формы сигнала восстанавливает фирму зарегистрированного сигнала. Далее кодированные значения восстановленного сигнала высвечиваются на блоке 7, Вывод зарегистрированной информации из блоков 5 и 9 памяти, а также последующее восстановление формы зарегистрированного сигнала осуществляется циклически. Поэтому для создания неподвижного изображения на блоке 7 с него на блок 12 управления поступает синхронизирующий сигнал Конец развертки. При этом блок 12 управления последовательно водает на блоки 5 и 9 памяти адреса, начиная с того, которому соответствовала первая высвечиваемая точка на блоке 7. Емкость блока 5 памяти значитель- но больше емкости блока 7. Для просмотра всего изображения сигнала и отдельных его участков изображение сигнала сдвигается и сжимается.Сдвиг изображения происходит за счет увеличения или уменьшения блоком 12 управления адреса, которому соответствовала первая высвечиваемая точка на блоке 7. Сжатие изображения осуществляется увеличением длительности развертки изображения, т.е. уменьшением частоты , поступающей с генератора 10 тактовых импульсов на блок 7 через блок 12 управления. А так как восстановление сигнала происходит с частотой Е , то уменьшение в Р раз частоты, поступающей на блок 7 отображения, приводит к сжатию изображения в Р раз. Блок 3 сокращения избыточности работает следующим образом. Код К-- с выхода аналого-цифрового преобразователя 2 поступает на информационный вход регистра 13 и на один из входов вычитателя 14, на второй вход которого поступает код К,- с выхода регистра 13. Разность кодов с вычитателя 14 поступает на один из входов схемы 15 сра нения, на второй вход которой посту пает величина допуска с блока 12 |Управления. В том случае, если срав ниваемые кодированные значения сигнала К- и К; отличаются на заданну величину , то с приходом строби рующего импульса с генератора 10 тактовых импульсов на коммутатор 16 в регистр 13 устанавливается послед нее кодированное значение сигнала . Управляющий сигнал с выхода коммутатора 16 также поступает на триг ер 8 и блок 12 управления. При этом триггер 8 устанавливается в единичное состояние, а блок 12 управления увеличивает адрес блоков 5 и- 9 памяти и вьщает на них сигналы Адрес, Запись и Тактовьм сигнал. Код К/ с регистра 13 прох дит чергз коммутатор 4 на блок 5 п мяти. Далее с аналого-цифрового преоб разователя 2 поступает последующее кодированное значение сигнала Kj на регистр 13, атакже на один из входов вычитателя 14, и проч.сходят процессы, аналогичные описанным. Блок 6 восстановления формы сиг нала работает следующим образом. Код,с блока 5 памяти поступает на информационные входы регистров 17 и 19. Код с блока 9 .памяти пост пает на установочньй вход регистра 17 и через элементы НЕ - на установочньй вход регистра 19 памяти. При считывании из блока 9 памяти кода 1 происходит запись кода с блока 5 памяти в регистр 17. При считывании из блока 9 памяти кода О происходит запись кода бл ка 5 памяти в регистр 19. Таким образом, происходит отделение записанных в блок 5 памяти кодирован ных значений сигнала от соответствунмцих интервалов времени. Код интервала времени с регистра 19 поступает на один из входов схемы 20 сравнения, на второй вход которой поступает код со счетчика 22, которьш предварительно обну ляется блоком 12 управления. С каждым тактовым импульсом воспроизведения. Поступающим с генератора 10 тактовых импульсов, код счетчика 22 увеличивается на единицу. При равенстве кодов, поступающих на схему 20 сравнения, или при превышении кода счетчика 22 на единицу, на блок 12 управления через коммутатор 2 1 ппоходит задержанньм тактовьй импульс воспроизведения fi о генераторе 10 тактовых импульсов. Вследствие этого обнуляется счетчик 22, а из блоков 5 и 9 памяти считывается последующая информация и устанавливается либо в регистр 17, либо в регистр 19 памяти в зависимостиОТ считанной информации из блока 9 памяти, и т.д. Кодированные дискретные значения сигнала, считанные из блока 5 памяти, хранятся в регистре 17 в промежутках времени, пропорциональных соостветствующим интервалаь5 времени, т.е. осуществляется восстановление формы зарегистрированного сигнала полиномом нулевого порядка. Восстановленный сигнал регистра 17 поступает на блок 7. Блок 7 работает следующим образом. Кодированные значения сигнала с выхода блока 6 восстановления формы сигнала поступают на дешифратор 23, которьй определяет положение светящихся точек на матричной индикаторной панели 24 по вертикали. Код. со счетчика 26 поступает на дешифратор 25, которьй определяет положение светящейся точки по горизонтали. Код счетчика 26 увеличивается на единицу с кажяым импульсом, поступающим с блока 12 управления. Это приводит к последовательному- смещению светящейся точки по горизонтали, т.е. осуществляется развертка изображения восстановленного сигнала. Для того, чтобы начало развертки совпадало с началом сигнала, счетчик 26 обнуляется блоком 12 управления при переходе от режима записи к режиму считывания. Для того, чтобы изображение формы сигнала было неподвижно, на блок 12 управления при переполнении счетчика 26 поступает синхронизирующий сигнал Конец развертки. Генератор 10 тактовых импульсов работает следующим образом. (Счетчик 28 считает импульсы опор ной частоты fj, , поступающий с генератора 27. Набор тактовых частот записи f та выхода счетчика 28 поступает на коммутатор 29. При поступлении с блока 12 управления на стробирующий вход коммутатора 29 сигнала Запись, через него проходит одна из частот 73 выбираемая первым задатчиком 32 кода. Далее импульсы частотой f укорачиваются формирователями 30 и 31 и поступают соответственно на вход аналого-цифрового преобразователя 2, на счетный вход счетчика 11 ( ) и на блок 12 управления (fij). Формирователь 30 вь1рабатывает короткий импульс по перепаду из /Ч с О, а формирователь 31 по перепаду из О в 1. Этим обеспечивается задержка импульсов, поступаюпщх на блок 3 и блок сокраще ния избыточности, и блок 12 управле ния относительно импульсов, поступа щих на вход АЦП 2 и счетчик М. Задержка необходима для установления переходных процессов в блоке 3 сокр щения избыточности. Сигнал Запись с блока 12 управ ления также поступает на коммутатор 33, запрещая прохождение через него импульсов тактовой частоты воспроиз ведения f.. со счетчика 28. При поступлении на генератор 10 тактовых импульсов с блока 12 управ ления сигнала Считывание прохожде ние информации через коммутатор 29 запрещается, а через коммутатор 33 проходят импульсы тактовой частоты воспроизведения f.j . Импульсы укор чиваются формирователями 34 и 35 и поступают соответственно на блок восстановления формы сигнала (тв) и на блок 12 управления, на блок 6 восстановления формы сигнала 6 (f|g). Формирователь 34 вырабатьшает короткий импульс по перепаду из 1 в. О, а формирователь 35 по пере, паду на О в 1. Задержка f. в данном случае необходима для уста новления переходных процессов в бло ке 6 восстановления формы сигйала. Блок 12 управления работает следующим образом. При нажатии кнопкл 73 триггер 74 устанавливается в единичное состояние, тем самым разрешается прохождение информации через коммутатор 6 В зависимости от положения переключателя 66 коммутатор 67 проходит либо внешний, синхронизирующий сигнал, либо управляющий сигнал с блока 3 сокращения избыточности (в момент различия сравниваемых кодированных значений на заданную величину ),который устанавливает триггеры 68 и 74 в нулевое состояние, обнуляет счетчик 58, а также, проходя через элемент 70 ИЛИ, обнуляет счетчик 52. Нулевое состояние триггера 74 запрещает прохождение информации через коммутатор 67, а нулевое состояние триггера 68 соответствует сигналу Запись для блоков 5 и 9 памяти. Сигнал Запись поступает также на коммутаторы 64 и 67. При этом через коммутатор 64 разрешается прохождение с генератора 10 тактовых импульсов, задержанных тактовых импульсов записи f V3 которые затем через элемент 65 ИЛИ поступают на блоки 5 и 9 памяти, а через коммутатор 57 .разрешается прохождение информации с элемента 56 ИЛИ. При каждой смене кодов на заданную величину 8 с блока 3 сокращения избыточности через элемент 56 ИЛИ и коммутатор 57 на счетчик 58 поступает импульс, который изменяет адресный сигнал на единицу и по этот му адресу А,+1 запоминается последнее кодированное значение сигнала k- . Одновременно с этим импульс с блока 3 сокращения избыточности, проходя через элемент задержки, выполненньй на формирователе 48 и формирователе 49, устанавливает триггер 50 в единичное состояние. Единичное состояние триггера 50, разрешает прохождение через коммутатор 51 импульсов с генератора 10 тактовых импульсов. Время задержки сигнала формирователей 48 и 49 выбрано так, чтобы задержанные тактовые импульсы записи g , соответствующие смене кодов на величину , не успевали проходить через коммутатор 51. Формирователи 48 и 49 работают следующим образом. При поступлении на формирователь 48 короткого импульса он удлиняется , Далее этот импульс поступает на ормирователь 49, который по его заднему фронту короткий импульс. Таким образом, задержки импульса на элементах 48 и 49 равно величине расширения короткого импульса формирователем 49. Ближайший задержанньм тактовый импульс записи f поступивший с генератора 10 тактовых импульсов, про ходит через коммутатор 51, опрокиды вает триггер 50 в нулевое состояние и проходит через элемент 56.ИЛИ, коммутатор 57 на счетчик 58, увеличивая его код на единицу. По этому адресу А f, +2 запоминается интервал времени постоянства кодированного значения сигнала К-. Запись интер ла времени происходит с каждым задержанным тактовым импульсом заПИСИ . При переполнении счетчика 11 на коммутатор 61 с него поступает управляющий сигнал, которьй разрешает прохождению через него задержанного тактового импульса записи f с генератора 10. Далее этот импульс проходит через элемент ИЛИ 5 коммутатор 57 на счетчик 58, увеличивая его код на единицу. По адресу А запоминается остаток интервала времени, в течение которого не изменяется код К. на заданную величи ну . При различии кодированных значений сигнала на заданную величину с блока 3 сокращения избыточности черзе элемент 36НЕ проходит импуль на один из входов первого элемента 37 И. На второй вход элемента 37 И поступает задержанньм тактовьй импульс записи f|jC генератора 10 дополнительно задерживаясь на элементах 41 и 42 НЕ. На элемент И 37 проходят импульсы в противофазе, одинаковой длительности и одновременно, поэтому через него не проход управляющий сигнал (импульс) на пер вый вход триггера 8. На второй вход триггера 8 в этот момент поступает импульс с блока 3 сокращения избыточности, который устанавливает его в единичное состояние. В том случае, если при следующем задержанном тактовом импульсе запис не происходит смены кодов на величи ну Е , то через элемент 37 И проходит импульс, который устанавливает триггер 8 в нулевое состояние. При различии кодированных значений сигнала на величину Е или при переполнении счетчика 11 через элемент 43 ИЛИ проходит импульс либо с 1 5IS блока 3 сокращения избыточности, либо с коммутатора 61, либо с них обоих. Далее этот импульс, проходя через блок задержки, выполненный на формирователе 44 и на формирователе 3.8, обнуляет счетчик 11. Время задержки выбирается таким, чтобы код из счетчика 11 успел переписаться в блок 5 памяти. С задатчика 76 кода на блок 3 сокращения избыточности поступает величина . , При переполнении счетчика 58 триггер 68 опрокидывается в нулевое состояние, соответствующее сигналу Считывание для блоков 5 и 9 памяти. Этот сигнал также поступает на коммутаторы 57 и 64, разрешая прохождение через них импульсов с элемента 62 шш. Импульсы с коммутатора 57 поступают на счетный вход счетчика 58, а с коммутатора 64 через элемент 65 ИЛИ, в {сачестве тактовых импульсов на блоки 5 и 9 памяти. Таким образом, из блоков 5 и 9 памяти последовательно считывается зарегистрированная информация, по которой блок 6 восстановления формы сигнала восстанавливает форму зарегистрированного сигнала. Затем восстановленньй сигнал высвечивается на блоке 7 . На элемент 62 ИЛИ поступают: а) импульсы с генератора 10 тактовых импульсов через элемент 77 И при появлении на выходе блока 9 памяти единицы, соответствующей считыванию с блока 5 памяти и установки в блок 6 нового восстановления формы сигнала нового кодированного значения сигнала k . Благодаря этому из блока 5 памяти считывается и устанавливается в блок 6 восстановления формы сигнала интервал постоянства dfr кодированного значения, сигнала К или последующее кодиросигнала К, ванное значение считывается д j , то последующие операции соответствуют пункту б. Если считывается Кр, то последующие операции соответствуют пункту а, б) импульсы с блока 6 восстановления формы сигнала при окончании восстановления участка сипгала, по считанной ранее информаци . Благодаря этому считывается последующая информаци из блоков 5 и 9 памяти. Если считывается остаток Д-fcp интервала постоянства 4i , то jip устанавливается в блок 6 во становления формы сигнала и по коди рованному значению « и At восстанавливается следующий участок сигнала, а последующие операции соотве ствуют пункту б, Если считывается последукидее кодированное значение сигнала, то оно устанавливается в блок 6 восстановления формы сигнала выполняются операции по пункту а. в) импульсы с элемента 54 И при сдвиге изображения на блоке 7. Для подготовки блока 6 восстановления формы сигнала к восстановлению каж:дого участка сигнала с элемента .62 ИЛИ через элемент 63 ИЛИ проходя импульсы и обнуляют счетчик 22 блока 6. Вывод зарегистрированной информа ции из блоков 5 памяти, а следовате но, послудющее восстановление и отображение формы зарегистрированно сигнала, осуществляется многокра.тно. Поэтому для создания неподвижного изображения на блоке 7 на бло1 12 управления с него поступает синхронизирующий сигнал Конец развертки. Этот сигнал устанавливает триггер 47 в единичное состояние по прямому выходу и в нулевое :состояние по инверсному выходу. Нулевой потенциал с инверсного выхода триггера 47 запрещает прохож дение импульсов с элемента 62 ИЛИ через коммутатора 57. Единичный потенциал с прямого выхода триггера 47 проходит через элемент 63 ИЛИ и обнуляет счетчик 2 блока 6 восстановления формы сигнала, обнуляет счетчик 71J устанавливает в счетчике 58 адрес из пятого счетчика 52, сответствукмций первому высвечиваемому кодированному сигнала К „ на блоке 7 (фн1.5а), поступает на элемент 54 и разрешает прохождение через него задержанных тактовых импульсов воспроизведения f,. с генератора 10 так товых импульсовi поступает на элемент 55 И и разрешает прохождение через него дополнительно задержанны на формирователях 59 и 60 тактовых импульсов при условии, что на выходе блока 9 памяти код логическо единицы; запрещает прохождение информации через коммутатор 72, Сигнал Конец развертки проходит через коммутатора 72, Сигнал Койёц развертки проходит через элемент 65 ИЛИ на блоки 5 и 9 памяти в качестве Тактового сигнала. Из блока 5 памяти считываетря кодированное значение 1С , соотЭетствующее первой вьювечиваемой точке на блоке 7 (фиг.За). Из блока 9 : памяти считывается код единицы, поступающий на элементы 55 и 77 И. Через элемент 55 И с генератора 10 тактовых импульсов прокодит импульс f задержанный на формирователях 59 и 60. Блок задержки выпол- i нен на формирователях 59 и 60. Время: задержки выбирается таким, чтобы к моменту появления импульса | на входе элемента 55 И успевала выводиться информация из блоков 5 и 9 памяти. Импульс с элемента 55 И устанавливает триггер 47 в нулевое состояние по прямому выходу. Тем самым разрешается прохоядцение импульсов с элемента 62 ИШ через коммутатор 57, снимается сигнал обнуления Со счетчика 22 блока 6 восстановления формы сигнала и со счетчика 71; снимается сигнал установки в счетчике 58 из счетчика 52;.запрещается прохождение тактовых импулЬсов воспроизведения €J.g через элемен- ты 54 и 55 И-, разрешается прохождение информации через коммутатор 72. Ближайший тактовый импульс воспроизведения f{.g проходит через элемент 77 И, и через элемент 62 ШШ. Импульс с f ц с элемента 62 ИЛИ проходит через коммутатор 57 на счет чик 58, увеличивая его код на единицу, далее через коммутатсф 64 и элемент 65 ИЛИ - на блоки 5 и 9 памяти в качестве тактового сигнаа. Вследствие этого из блоков 5 и 9 памяти считывается ин|)Ормация, следующая за дискретным кодированным значением сигнала К„ . Далее происходят процессы, аналогичные описанным, до появления синхрониэирукяцего сигнала Конец развертки. Таким образом, осуществляется неподвижность изображения на блоке 7 при цикличес-. ком выводе информации из блоков 5 и 9 памяти. Для сдвига изображения влево необходимо нажать кнопу 39. этом триггер 45 устанавливается в единич ное состояние, соответствунлцее происхождению стробирующих импульсов f элемента 54 И на суммирующий вход сче.тчика 52. Суммирующий и вычитающий входы счетчика 52 подключены к выходам дешифратора 53. Информационным сигналом дешифратора 53 является код триггеров 45 и 46, а стробирующим сигналом - импульсы , поступающие с генератора 10 тактовых импульсов через элемент 54 И. Импульсы через элемент 54 И проходят после появления ла Конец развертки. С каждым стро бирующим импульсом |g происходит увеличение кода счетчика 52. Код счетчика 52 затем передается в счет чик 58. По адресу, устанавливаемому в счетчике 58, из блоков 5 и 9 памяти последовательно считывается информация. При выводе ближайшего кодированного значения сигнала k через элемент 55 И проходит- задержанный Импульс f , который обнуляет триггеры 47 и 45. Тем самым запрещается прохождение строб рующих импульсов на суммирунщий вхо счетчика 52, снимается обнуляющий сигнал со счетчика 71 и разрешается прохождение импульсов через коммутатор 72. Поэтому изображение .сигнала теперь -начинается с кодированного значения следующего за кодированным значение .5б). Дпя сдвига изображения вправо необходимо нажать Кнопку 40. При этом триггер 46 устанавливается в единичное состояние, соответствую щее прохождению стробирующих импуль .сов f элемента 54 И на вычитающи вход счетчика 52. С каждым стробиру щим импульсом происходит уменьшение кода счетчика 52. Код счетчика 52 устанавливается в счетчик 58. Из блоков 5 и 9 памяти последовательно выводится информация. При выводе ближайшего кодированного значения сигнала К, через элемент 55 И проходит задержанньй импульс f|j , который обнуляет триггеры 47 и 45. Тем самым запрещается прохождение стробирукяцих импульсов на вычитанлций вход счетчика 52, снимается обнуляющий сигнал с счетчика 71 и разрешается прохождение импульсов через коммутатор 72. Поэтому изображение сигнала начинается с кодированного значения сигнала к,, , предшествующего кодированному значению сигнала 1Ср„ (фиг.5в). Сжатие изображения осуществляется увеличением длительности развертки изображения, т.е. уменьшением частоты (делением частоты на счетчике 71), поступающей с генератора 10 тактовых импульсов на блок 7 отображения через коммутатор 72. Так как восстановление сигнала происходит с частотой . , то уменьшение в р раз частоты, поступающей на блок отображения, приводит к сжатию изображения в р раз. Коэффициент сжатия изображения определяется задатчиком 75 кода. Если необходимо совместить начало развертки с началом изображения, то достаточно обнулить счетчик 52. Дпя этого необходимо нажать кнопку 69. Сигнал с кнопки 69 проходит через элемент ИЛИ 70 и обнуляет счетчик 52. Сравнение предложенного устройства с известным показьшает, что введение новых блоков и связей позволяет существенно повысить точность регистрации за счет более эффективного использования емкости блоков 5 и 9 памяти, а также уменьшить влияние помех за счет изменения величины Е . Это, в свою очередь, повьшгает качество проводимых экспериментов и дает значительньй эко юмический эффект.

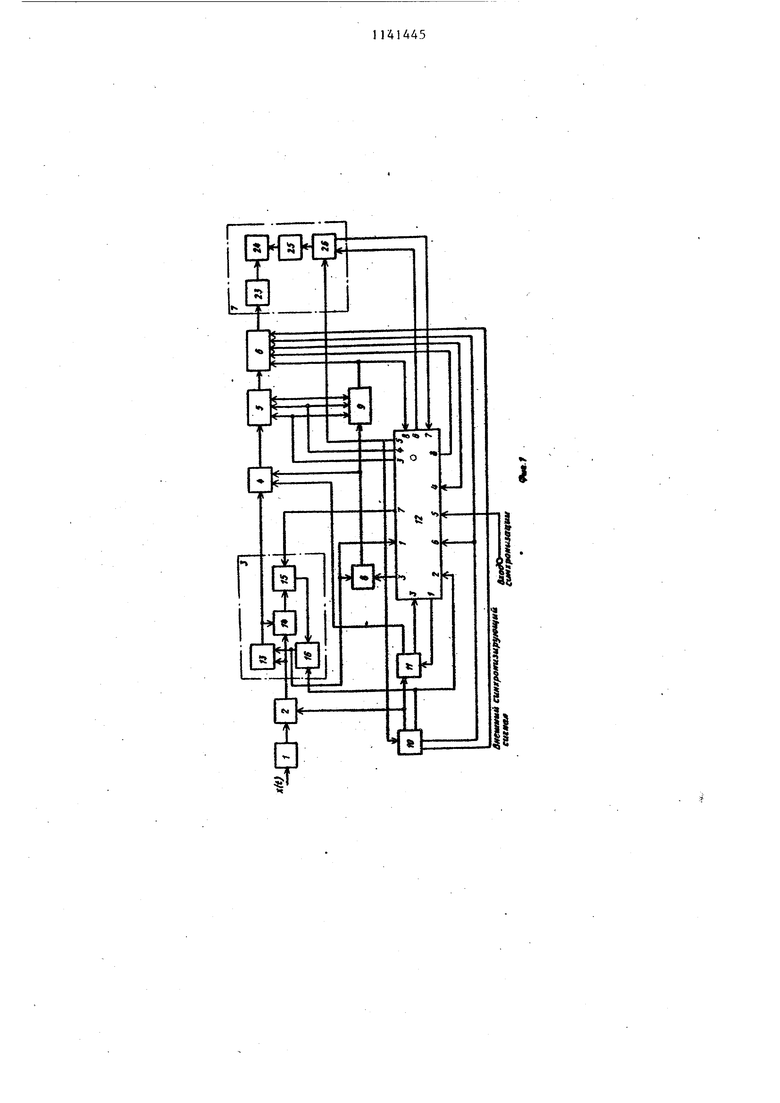

ЕНЖЗ

II

cnfjt

сЮбл.

фиг,2

Фи9

Г

H I

а

Натрычмая инди / аторная

nafi&j d

. «ваг

1

/

fiampu HQ UH uffcfmopHOfi

fv. I I

i

i

Hamj3U4Hai

8 индикаторная

пане/1Ь

«

e

«««

в

ееев«в«в

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отображения формы регистрируемого процесса | 1974 |

|

SU542095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отображения информации | 1979 |

|

SU888182A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1985-02-23—Публикация

1983-04-16—Подача