1 Изобретение относится к области вычислительной техники и технической кибернетики и предназначено для управления многомодульной памятью обмена и распределения заданий по процессорам в цифровой вычислительной системе. Известно устройство для управления памятью l , содержащее матрицу ячеек памяти, шифратор, регистры, счетчики, ге иератсф, триггеры, элементы И, ИЛИ. Недостатками этого устройства являются его ограниченные возможности при распределении заданий по блокам памяти, ориентации на узкий класс специальных задач. Наиболее близким техническим решйнием к предлагаемому изобретению является устройство Н , содержащее матрицу ячеек памяти, коммутаторы, дешифраторы, шифраторы, блок управления выборкой из памяти, блоки ассоциативной памяти, перекрестные коммутаторы, операционный блок, буферные блоки памяти, регистр, счетчик неудовлетворенных 3anpocc Однако это устройство недостаточно эффективно распределяет -задания по блокам памяти, допускает простои оборудования. Целью изоб ретения является повышение коэффициента использования оборудования. Поставленная цель дсютигается тем, что в устройство для управления блоковой основной памятью 2 , содержащее матрицу ячеек памяти, первая и вторая группы входов которой соединены с выходами первых коммутатора и дешифратора, группа выходов матрицы ячеек памяти соединена через первый шифратор с первой груйпой входов второго коммутатора, блок управления выборкой из памяти, первая группа выходов которого через второй шифратор соединена с первыми входами первой ассоциативной памяти и первого перекрестного коммутатора, операционный блок, вторую и третью ассоциативные памяти, три буферных блока памяти, реГистр, второй, третий, четвертый, пятый перекрестные коммутаторы, третий, четвертый коммутаторы и счетчид неудовлетвфеннык запросов, введены блок управления распределением заданий, счетчик и три дешифратора, причем первая группа выходов первой ассоциативной памяти соединена с группой входов первого коммутатора, первый аход которого соединен с выходном счётчика и первым ELXOAOM iMiaTрицы ячеек памяти, второй вхрд которой соединен с выходом блока управления распределением заданий и первыми аходами второй и третьей ассоциативньк памятей и первой буфёрной Т1амятй вь1ходы котор6й соединены с входами второго дешифратора

группой входов третьего коммутатора и второй группой входов второго коммутатора, выходы которого через вторую буферную память соединены с входами третьего дешифратора и первой группой входов четвертого коммутатора, выходы которого соединены с входами второго перекрестного коммутатора, входами первого дешифратора, вторыми входами первой буферной памяти и перекрестного коммутатора и первым вхоДоь т етьёгопёрёкрестного коммутатора, выходы которого чераз третью буферную память соёДйнёны с чет;вертым перекрыстным коммутатором, выходы второй группы первой ассоциативной памяти соединены с первым входом счетчика, третьей группой входов второго коммутатора и второй группой входов четвертого .коммутатора и первым входом операционного блока, выход первой ассоциативной памяти соединен со вторым аходом счетчика, первым входом счетчика неудовлетворенных запросов, вторым аходом операционного блока, третьим входом первой буферной памяти и первым входом бло-40с первыми входами восьмого триггера,

ка управления распределением заданий,четвертого и пятого элементов И, восьмой

второй и третий в.ходы которого сое дине-.вход блока соединен с первым входом де- ны с выходами соответственно второй и третьей ассоциативньк памятей, выходы

второй ассоциативной памяти соединены с 45первого элемента ИЛИ и вторыми аходами

вторыми входами счетчика неудовлетворен-пятого и шестого триггеров, первый вы- V

ньк запросов, третьего перекрестного KoiviMyraTopa, первой и третьей ассоциативных памятей, третьими входами первоiro№peKp ecTH6roK6 vtyTaTOpa, счетчика, операционного блока, четвертым входом блокауправления распределением заданий и через пятый перекрестный коммутатор с первой группой выходов устройства, выхедег третьего коймутатора соединены с третьим.входом первой ассоциативной памяти, выходы второго перекрестного коммутатора соединены со входами блока уп74

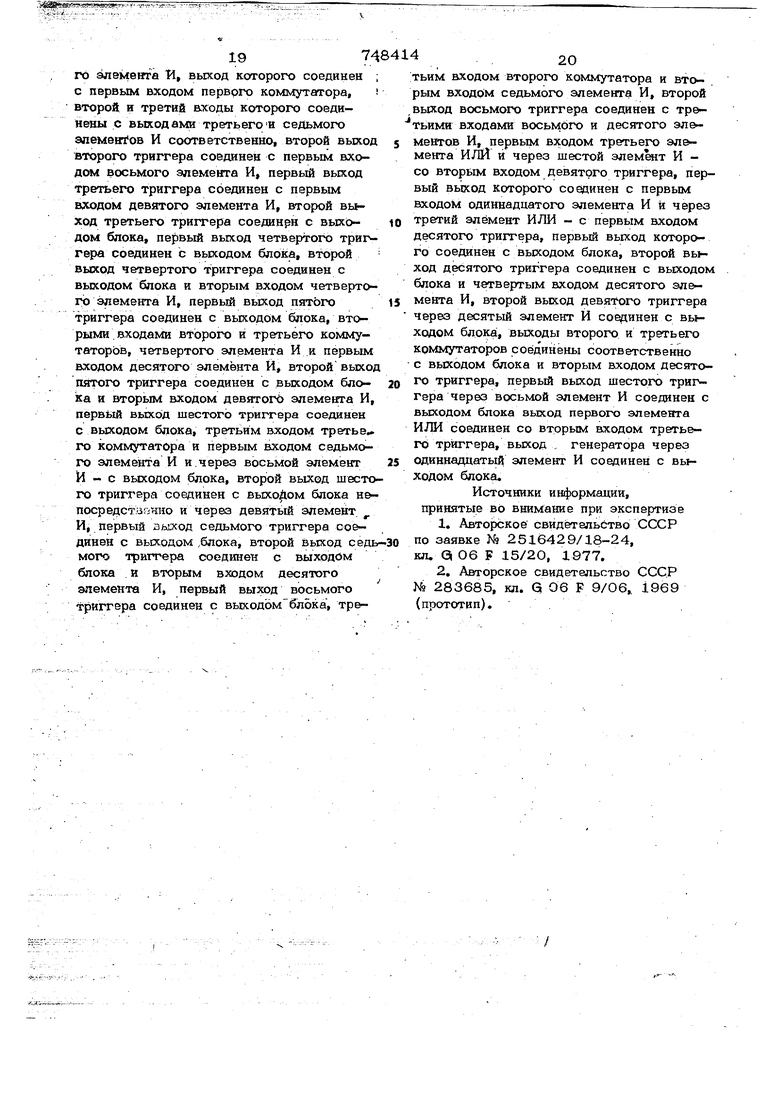

того перекрестного коммутатора соединены с второй, третьей и четвертой группой выходов устройства соответственно, а бло управления распределением заданий содержит генератор, коммутаторы, триггеры, элементы ИЛИ, И, причем первый аход блока соединен с первыми аходами первого и второго триггеров, первого элемента ИЛИ, группой аходов первого коммутатора, первым входом второго и третьего, коммутаторов и через второй элемент ИЛИ - с выходом блока, второй вход блока соединен с первыми в.ходами третьего триггера, первого и второго элементов И, третий вход блока соединен с первым входом четвертого элемента И и вторым в.ходом первого элемента ИЛИ, четвертый аход блока через первый и второй элементы И соединен с первыми аходами соответственно пятого и шестого триггеров, пятый В.ХОД блока соединен с первым входом седьмого триггера, шестой вход блока соединен с первым аходом третьего элемента И, седьмой аход блока соединен

вятого триггера и через пятый элемент И - с выходом блока, третьим аходом

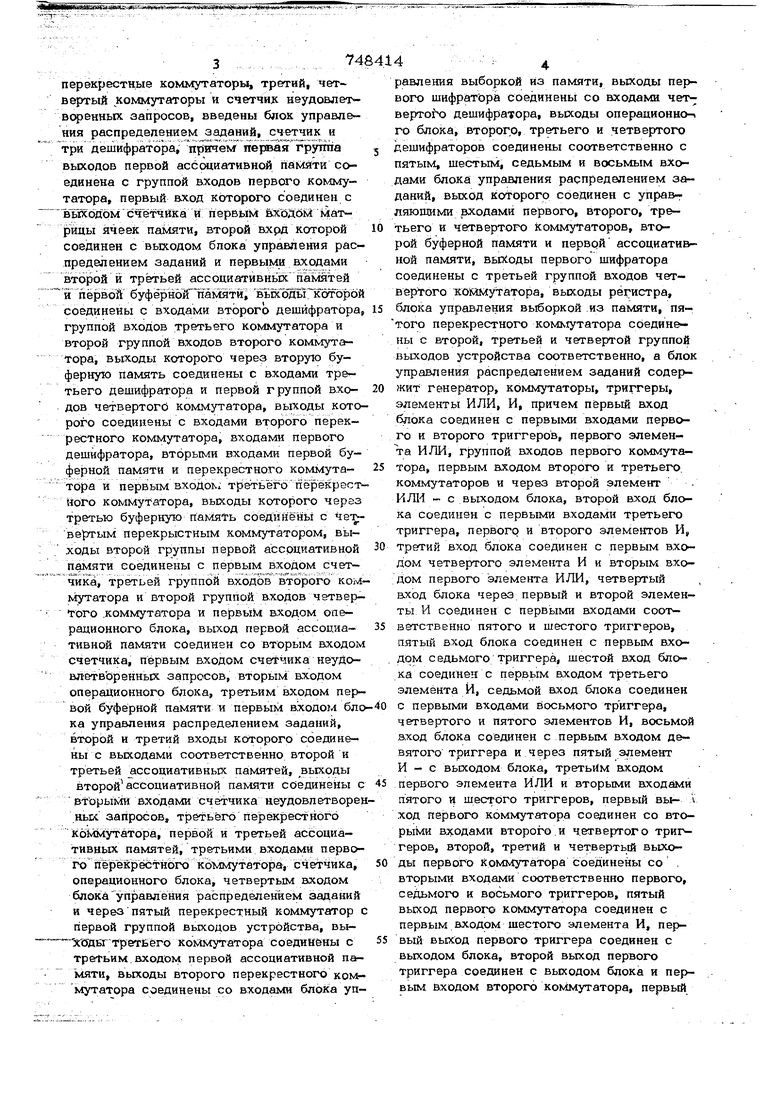

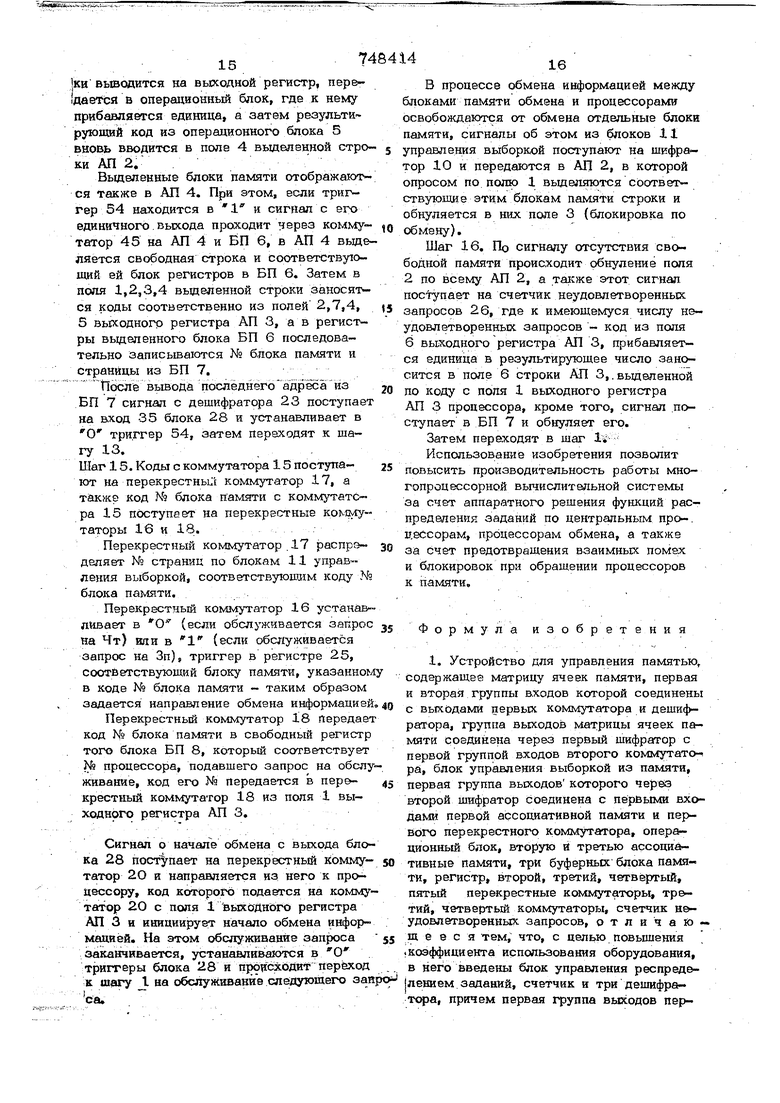

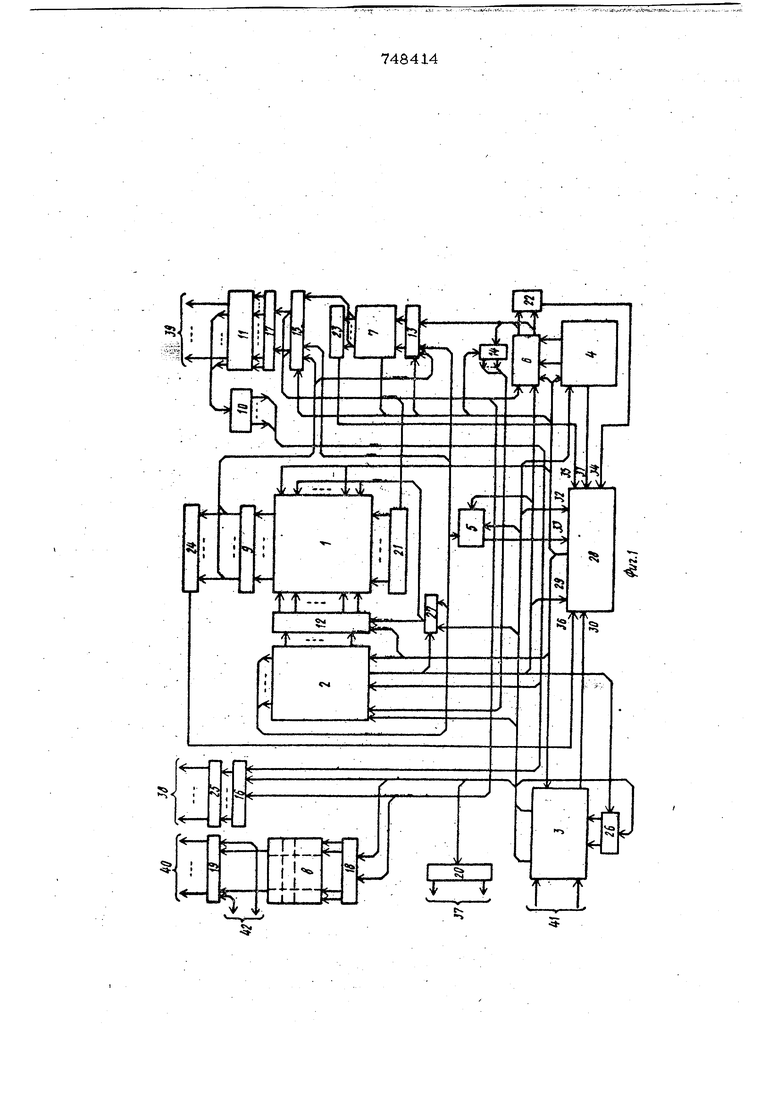

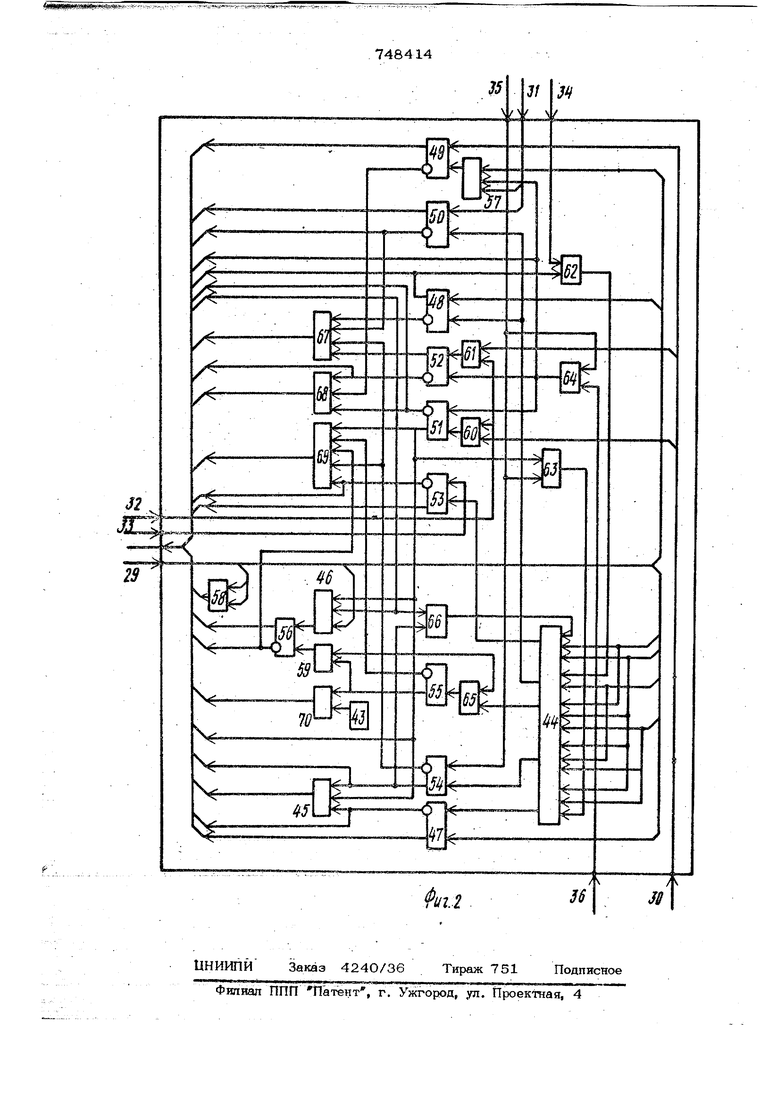

ход первого коммутатора соединен со вторыми входами второго и четвертого триггеров, второй, третий и четвертый выходы первого комзлутатора соединены со . вторыми входами соответственно первого, седьмого и восьмого триггеров, пятый выход первого коммутатора соединен с первым входом шестого элемента И, первый выход первого триггера соединен с выходом блока, второй выход первого триггера соединен с выходом блока и первым входом второго коммутатора, первый 4-4 равления выборкой Из памяти, выходы первого шифратора соединены со входами чет вертого дешифратора, выходы операционное го блока, второго, третьего и четвертого дешифраторов соединены соответственно с пятым, шестьш, седьмым и восьмым входами блока управления распределением заданий, выход которого соединен с управляющими рходами первого, второго, третьего и четвертого коммутаторов, второй буферной памяти и первой ассоциати&ной памяти, вьйоды первого шифратора соединены с третьей группой входов четвйртого К01ммутатора, выходы регистра. блока управления выборкой .из памяти, пявыход второго триггера соединен с выходом блока и вторым входом третьего элемента И, выход которого соединен с первым в,ходом первого коммутатора, второй и третий входы которого, соединены с выходами третьего и седьмого элементов И соответственно, второй вь1ход второго триггера соединен с первым входом восьмого элеме гга И, первый выход третьего триггера соединен с первым входом девятого элемента И, второй выход третьего триггера соединен с выходом блока, первый выход четвертого триггера соединен с выходом блока, второй выход четвертого триггера соединен с выходом бло ка и вторым входом четвертого элемента И, первый вьгход пятого триггера соединен с выходом блока, вторыми входами второго и третьего коммутаторов, четвертого элемента И и первым входом десятого элемента И, второй выход пятого триггера соединен с выходом блока и вторьм входом девятого элемента И, первый выход шестого триггера соединен с выходом бло ка, третьим входом третьего коммутатора, первым входом седьмого элемента И и через восьмой элемент И - с выходом блока, второй вьгход шестого триггера соединен с выходом блока непосредственно И через девятый элемент И, первьй выход седьмого триггера соединен с выходом блока, второй выход седьмого триггера соединен с выходом блока и вторым входом десятого элемента И, первзый выход восьмого триггера соединен с вьгходом блока, третьим входом второго коммутатора и BTOpbfivi входом седьмого элемента И, второй вьрсод восьмрго триггера соединен с третьими входами восьмого и десятого элементов И, первым входом третьего элемента ИЛИ и через шестой элемент И - со вторым входом девятого триггера, первый выход которого соединен с первым входом одиннадцатого элемента И и через третий элемент ИЛИ - с первым в.ходом десятого триггера, первый выход которого соединен с выходом блока, второй выход десятого триггера соединен с выходом блока и четвертым в.ходом десятого элемента И, второй выход девятого триггера через десятый элемент И соединен с выходом блока, вьгходы вторЬго и третьего коммутаторов соединены соответственно с выходом блока и вторым входом десятогч) триггера. Первый выход шестого триггера через восьмой элемент и соединен с выходом блока, выход первого элемента ИЛИ соединен со вторым аходом третьего тригТера, вь1ход генератора через одиннадцатый элемент И соединен с вькодом блок На фиг. 1 показана блок-схема устройства; на фиг. 2 -структура блока уп-. равлення распределением задания, где 1 - матрица ячеек памяти, 2 - первая ассоциативная память (АП); 3 - втррая ассоциативная память (АЛ); 4 - третья ассоциативная память (АП) 5 - операционный блок; 6 - первый буферный блок памяти (БП).; 7 - второй буферный блок памяти (БП); 8 - третий буферный блок памяти (БП); Э - первый шифратор; 10второй шифратор,; 11 - блок управления выборкой из памяти, 12 - первый коммутатор; 13 - второй коммутатор; 14 - третий коммутатор; 15 - четвертый коммутатор; 16 - первый перекрестный коммутатор; 17 - второй перекрестный коммутатор; 18 - третий перекрестный коммутатор; 19 - четвертый перекрестный коммутатор; 20 - пятый перекрестный коммутатор; 21 - первый дешифратор; 22 - второй дешифратор; 23 - третий дешифратор; 24 - четвертый дешифратор; 25 - регистр, 26- счетчик неудовлетвореннь1Х запросов; 27- счетчик} 28 - блок управления распределением заданий; -29 - первый вход блока управления распределением заданий; 30 - второй вход бдока управления распределением заданий; 31 - третий вход блока управления распределением заданий; 32 - четвертый вход блока управления распределением заданий 33 - пятый вход блока управления распределением заданий; 34 - шестой вход блока управления распределением заданий , 35 - седьмой вход блока управления распределением заданий; 36 - восьмой вход блока управления распределением заданий; 37 -первая группа выходов устройства; 38 - вторая группа выходов устройства; 39 - третья группа выходов устройства; 40 - четвертая группа выходов устройства; 41 - группа входов устройства , 42 - .группа числовых шин; 43 - генератор, 44 - первый коммутатор; 45 - второй коммутатор; 46 - третий коммутатор; 47 - первый триггер; 48 второй триггер; 49 - третий триггер; 50 - четвертый триггер, 51. - пятый : . триггер; 52 - шестой триггер; 53 - седьмой триггер; 54 - восьмой триггер; 55 девятый триггер; 56 - десятый триггер; 57 - первый элемент ИЛИ, 58 - второй элемзнт ИЛИ; 59 - третий элемент ИЛИ; 60 - первый элемент И; 61 -.второй, элемент И} 62 - третий элемент И; 63 - четвертый элемент И$ 64 - пятый элемент И; 65 - шестой элемент Hj 66 - седьмой :элемб ИТ И; 67 восьмой элемент И; 68девятый элэмет- И; 69 - десятьй элемент И, 70 - одиннадцатый элемент И У1 тройство работает следующим образом. Запросы на вьщеление памяти для чтения и записи от центральных процессоров ,и проадассоров обмени поступают в устройство на группу входов 41 в АП 3, д ко

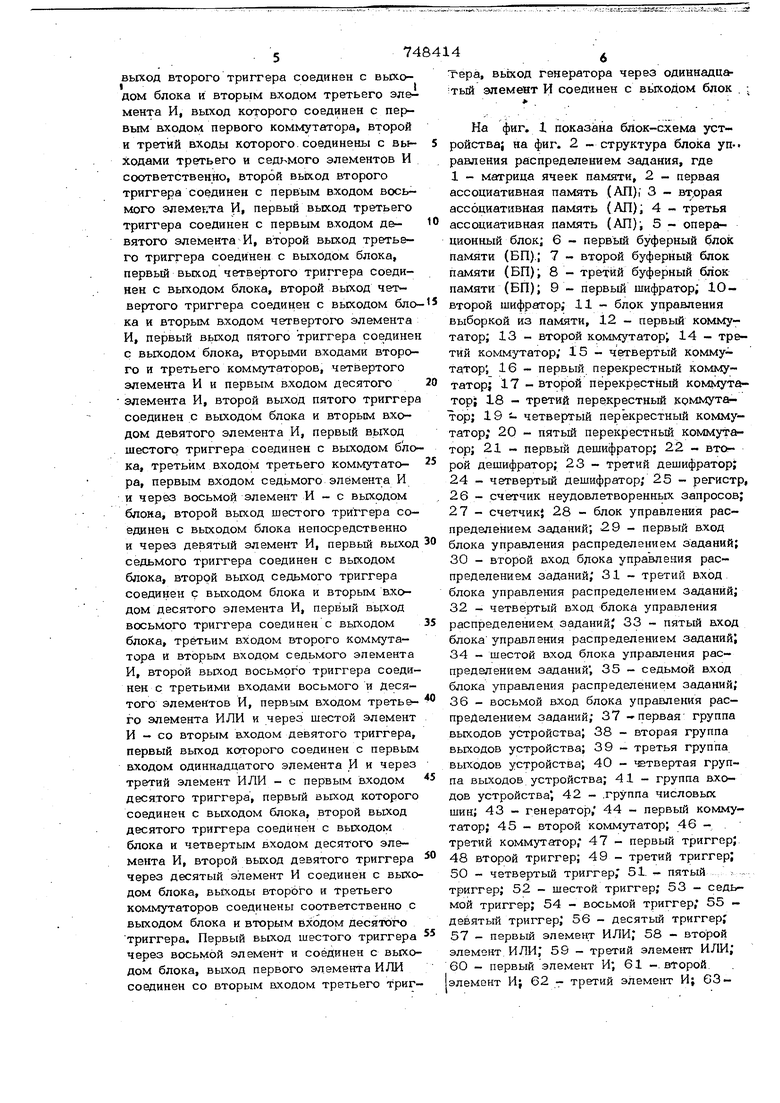

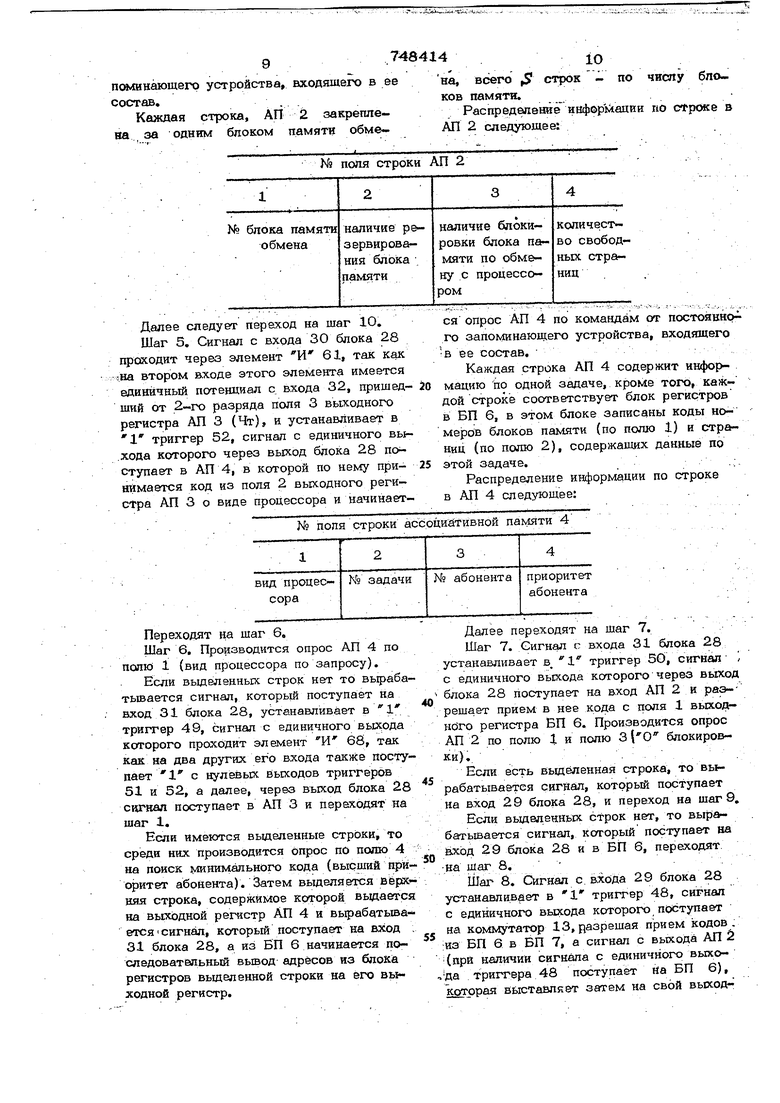

К поля строки АЛ 3 горой каждая строка закреплена за отдельным процессором. В запросе на запись н формации, кроме типа запроса (чтени запись), указьшается также номер абонента и его приоритет, номер задачи, к которой относится передаваемая информация и ко личество передаваемой информации (в страницах). Распределение информации по строке в АП -3 следующее:

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Процессор для сопряжения цвм с каналами передачи данных | 1978 |

|

SU744541A1 |

| Устройство управления регенерацией динамической памяти | 1989 |

|

SU1615727A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для управления распределением задач | 1977 |

|

SU696471A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ | 1991 |

|

RU2049349C1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Генератор случайного процесса | 1978 |

|

SU840896A1 |

При наличии сигнала с выхода блока управления 28 прбизводится опрос АП 3 по командам от постоянного запрминаю щёго устройства, входящего в его состай Б следующей последовательности, содержащей 4 этапа алгоритк1й работы устройства.. Этап 1. В первую очередь производится определение наличия запросов от процессоров обмена (ПО) на чтение (Чт) «уги такозых нет, то переходят на этап, Этап 2. Производится определение нал чия запросов от ПО на запись (Зп), если таковых нет, то переходят на этап 3, Этап 3. Производится определение нал чня запросов от центральных процессоров (ЦП) на Чт , если таковых нет, то переходят на этап 4, 4. Производится определение наличия запросов от ЦП на Зп. Обслуживание запросов на вьоделение памяти производится в следующем порядке, срдержащем 16 maiTOB: Шаг 1. Опрос АП 3 по полю 2 (вид процессора: 1О - ЦЩ О - ПО) и по полю 3 (тип запроса: Ю - Saj 01 Чт)} если тип запроса Зп, то переходят на шаг 2, если тип Запроса Чт, то переходят на щаг 3, Если вьщеленных строк нет, то пере ходят к щагу 1 на определение .наличия запросов другого типа сотасно программе, если имеются выдал энные строки, то cjJBAH них производится опрос по погао 6 нл поиск максимального кода ( по числу неудовлетворенных запросов); если вьоделвнньсс строк нет, то восстанавливается индикация по предьщушему опросу (по щагу l)j если имеются выделенные строки, то по ним производится опрос по ПОЛЮ 5 на поиск минимшхьного кода (высщйй приритет), выделяется верхняя строка и ее содержимое выводится на выходной регистр АП 3 и выделяется сигнал, поступающий на вход 30 блока 28. Далее следует шаг 4, Шаг 3. Ёслк выделенных строк нет, то переходят к шагу 1 на определение нали- чяя запросов другого типа согласно программе, если имеютсявьщеленные строки, :то из HEX выделяется верхняя и ее содержимое выводится на выходной регистр АПЗ и вьщается сигнал на вход ЗО блока 28, Далее следует переход на шаг 5, Шаг 4. Сигнал с входа 30 блока 28 проходит через элемент И 60, так как на втором входе этого элемента имеется единичный потенциал с ахода 32, прищедшйй от первого разряда поля 3 выходного регистра АПЗ (Зп), и устанавливает в триггер 51, сигнал с единичного выхода которого через выход блока 28 поступает в АП 2, По этому сигнш1у в АП 2 принимается код ИЗ поля 8 выходного регистра АП 3 о количестве требуемых страниц памяти обмена для Зп и начинается ее опрос по ксжандам от постоянного за9

псйлинающегр устройства, входящего в ее состав.

Каждая строка, АП 2 закреплена за одним блоком памяти обме№ поля строки АП 2

Далее следует переход на шаг 10.ся опрос АП 4 по командам аг постоянн Шаг 5. Сигнал с входа 30 блока 28го запоминающего устройства, входящего

проходит через элемент И 61, так какв ее состав,

чНа втором аходе этого элемента имеетсяКаждая строка АП 4 содержит инфорединйчный потенциал с входа 32, пришад- 20мадию по одной задаче, кроме того, кажший от 2-го разряда поля 3 выходногодои строке соответствует блок регистров

регистра АП 3 (Чт), и устанавливает вв БП б, в этом блоке записаны коды триггер 52, сигнал с единичного вы-меров блоков памяти (по полк 1) и стра.хода которого через выход блока 28 (по полю 2), содержащих данные по

ступает в АП 4, в которой по нему при- 25этой задаче.

нймается код из поля 2 выходного реги-Распределение информации по строке

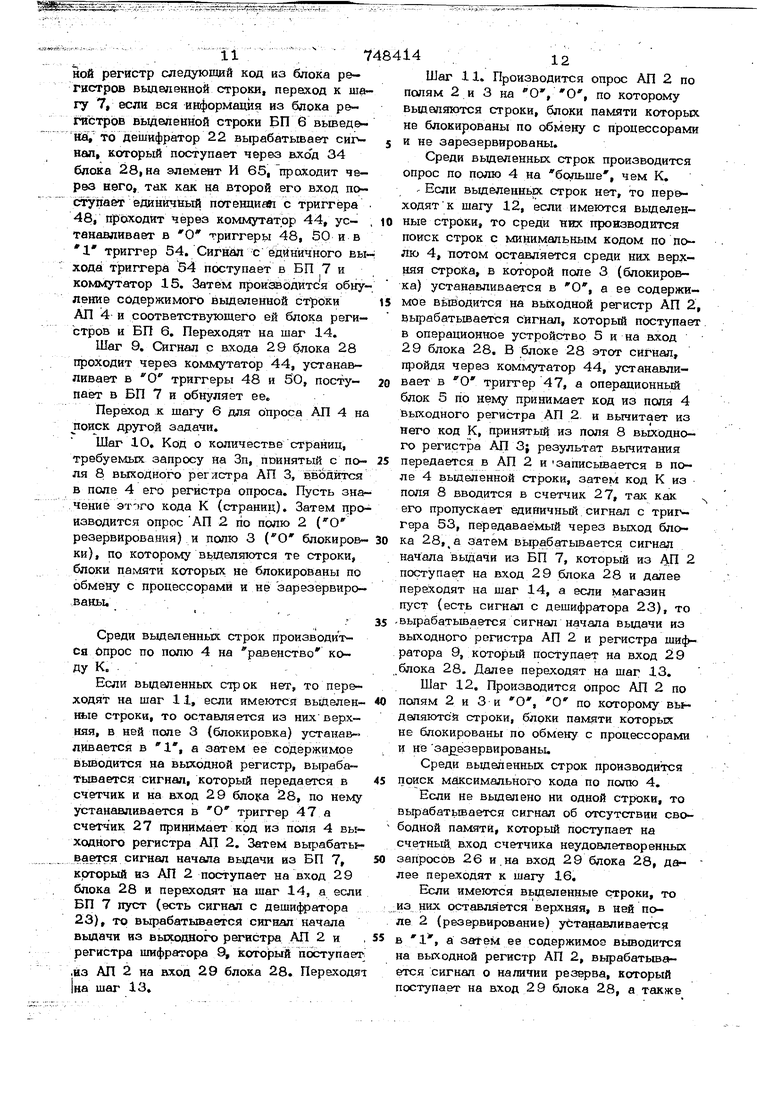

cfpa АП 3 о виде процессора и начинает-в АП 4 следующее:

М попя строки ассоцийтивной памяти 4

Переходят на шаг 6,

Шаг 6. Производится опрос АП 4 по полю 1 (вид процессора по запросу).

Если вьщеленных строк нет то вырабатьшается сигнал, которь1й поступает на вход 31 блока 28, устанавливает в триггер 49, сигнал с единичного выхода которого проходит элемент И 68, так как на два других его входа также поступает 1 с нулевых выходов триггеров 51 и 52, а далее, через выход блока 28 сигнал поступает в АП 3 и переходят на шаг 1.

ЕСЛИ имеются вьщеленные строки, то среди них производится Опрос по полю 4 на поиск минимального кода (высший приоритет абонента). Затем вьвделяется Верхняя строка, содержимое которой вьщается на выходной регистр АП 4 и вырабатываетсясигнал, который поступает на вход , 31 блока 28, а из БП 6 начинается последовательный вьтод адресов из блока регистров вьщеленной строки на его выходной регистр.

748414

lo

на, всего строк - по числу блоков памяти.. Распределение инфор1Лации по строке в АП 2 следуюшее:

Далее переходят на шаг 7.

Шаг 7. Сигнал с входа 31 блока 28 устанавливает в, 1 триггер 50, сигнал / с единичного выхода которого через выход блока 28 поступает на вход АП 2 и раэ0решает прием в нее кода с поля 1 выходного регистра БП 6. Производится опрос АП 2 по полю 1 и полю 3 0 блокировки),.

Если есть выделенная строка, то вы5рабатывается сигнал, который поступает на вход 29 блока 28, и переход на шаг 9.

Если вьщаденных строк нет, то вырабатьшается сигнал. Который поступает на &xbjDi 29 блока 28 и в БП 6, переходят на шаг 8. - ,

lilai 8. Сигнал с. входа 29 блока 28 устанавливает в 1 триггер 48, сигнал с единичного выхода которого поступает на коммутатор 13,разрешая прием кодов. :из БП 6 в БП 7, а сигнал с выхода АП 2 Чпри наличии сигнала с единичного выхо,да триггера 48 поступает йа БП 6), которая выставляет затем на свой выходкой регистр сугедуюшйй код из блока регистров вьщвпенной строки, переход к шагу 7, если вся информация из блока регистров выделенной строки БП 6 выведена, то дешифратор 22 вьфабатывает , который поступает через ьход 34 блока 28|На элемент И 65, проходит через него, так как на второй его вход поступает единичный потендиая с триггера 48, проходит через коммутатор 44, устанавливает в О триггеры 48, 50 и в триггер 54. Сигнал с единичного выч хода триггера 54 поступает в БП 7 и коммутатор 15. Затем производится обнуление содержимого вьщеленной строки АП 4 и соответствующего ей блока регистров и БП б. Переходят на шаг 14.

Шаг 9. Сигнал с входа 29 блока 28 проходит через коммутатор 44, устанавливает в О триггеры 48 и SO, поступает в БП 7 и обнуляет ее.

Переход к шагу 6 для опроса АП 4 на Т10ИСК другой задачи.

Шаг 10. Код о количестве страниц, требуемых запросу йа Зп, поинятый с поля 8 выкоДного регистра АП 3, вводится в поле 4 его регистра опроса. Пусть значение этэго кода К (страниц). Затем производится опрос АП 2 по полю 2 {О резервирования) и полю 3 (О блокировки), по которому вьщел5потся те строки, блоки памяти которых не блокированы по обмену с процессорами и не зарезёрвиро- ваньи

Среди вьщеленных строк производится опрос по полю 4 на равенство коду К. . - ,

Если выделенных строк нет, то переходят на шаг 11, если имеются выДеленiftie строки, то оставляется из них верхняя, в ней поле 3 (блокировка) устанав-. ливается в , а затем ее содержимое вьюодится на выходной регистр, вырабатывается сигнал, который передается в счетчик и на аход 29 блока 2&, по нему устанавливается в О триггер 47 а счетчик 27 принимает код из поля 4 выходного регистра АП 2. Затем вьфабатывается сигнал начала вьщачи из БП 7, который из АП 2 поступает на вход 29 блока 28 и переходят на шаг 14, а если БП 7 пуст (есть сигнал с дешифратора 23), то вырабатывается сигнал начала выдачи из выходного регистра АП 2 и регистра шифратора 9, который поступает ,йз АП 2 на вход 29 блока 28. Переходя |на шаг 13.

Шаг 11. Производится опрос АП 2 по полям 2 и 3 на О, О, по которому вьщеляются строки, блоки памяти которых не блокированы по обмену с процессорами и не зарезервированы.

Среди вьщеленных строк производится опрос по полю 4 на больше , чем К.

- Если вьщеленньрс строк нет, то пер&ходятк шагу 12, если имеются вьоделенные строки, то среди нгос производится поиск строк с минимальным кодом по полю 4, потом оставляется среди них верхняя строка, в которой поле 3 (блокировка) устанавливается в О, а ее содержимое вьшодится на вькодной регистр АП 2 вырабатывается сигнал, который поступает в операционное устройство 5 и на аход 29 блока 28, В блоке 28 этот сигнал, пройдя через коммутатор 44, устанавливает в О триггер 47, а операционньй блок 5 по нему принимает код из поля 4 выходного регистра АП 2 и вычитает из него код К, принятый из поля 8 выходного регистра АП 3j результат вычитания передается в АП 2 и записьшается в поле 4 выделенной строки, затем код К из поля 8 вводится в счетчик 27, так как его пропускает единичный сигнал с триггера 53, передаваемый через выход блока 28, а затем вырабатьюается сигнал начала выдачи из БП 7, который из АП 2 поступает на вход 29 блока 28 и далее переходят на шаг 14, а если магазин пуст (есть сигнал с дешифратора 23), то -вырабатывается сигнал начала вьщачи из вьрсодного регистра АП 2 и регистра шифратора 9, который поступает на вход 2.9 .блока 28. Далее переходят на шаг 13.

Шаг 12. Производится опрос АП 2 по полям 2 и 3 и О, О по которому вЬьдепяюто а строки, блоки памяти которых не блокированы по обмену с процессорами И не за взервированьи

Среди вьщеленных строк производится поиск максимального кода по полю 4.

Если не вьщелено ни одной строки, то вырабатьюается сигнал об отсутствии свободной памяти, который поступает на счетный аход счетчика неудовлетворенных запросов 26 и.на вход 29 блока 28, далее переходят к шагу 16.

Если имеются вьщеленные строки, то из них оставляется верхняя, в ней поле 2 (резервирование) устанавливается в 1, а затем ее содержимое вьюодится на выходной регистр АП 2, вьфабатывается сигнап о наличии резерва, который поступает на вход 29 блока 28, а также IB счетчик 27 и в операционный блок 5. В блоке 28 до этому сигналу устанавливаетрся в триггер 47, в операционный блок 5 вводится код из поля 4 выходного регистра АП 2, его вычитают из кода К, принятого из попя 8 выходного регистра АП 3, а результат вьиитания - число дополнительно требуемых для процессора страниц памяти - вводится из операционного блока 5 в АП 2. В счетчик 27 принимается код из 4 выходного регистра АП 2 и вырабатььвается сигнал о вводе в БП 7, который поступает на вход 29 блока 28, проходит в нем через элемент ИЛИ 58 и поступает в БП 7. Переходят на шаг 13. Шаг 13. По коду из поля 1 (№ блока памяти выходного регистра АП 2) производится опрос АП 2 и выделение соответствующей строки, затем счетчик 27 начинает вьщавать laa вход матрицй 1 памяти импульсы, поступающие в него из генератора импульссов 43. Общее число импульсов, посылаемых в матрицу 1 памяти определяется кодом, введенным в счетчик 27 - либо кодом К с поля 8 выходного регистра АП 3, либо - с поля 4 выходного регистра АП 2 (количество имеющихся свободных страниц). . В матрице 1 импульсы проходят только в ту ее строку, которая выделена .строкой АП 2, и поступают на вход первой в строке ячейки памяти. Логическая схема ячейки памяти матрицы 1 обеспечивает прохождение импульса опроса с входа ш вьгход только в том случае, если данная ячейка еще не опрашивалась и если в ней основной триггер находится в , причем тогда этот же импульс устанавливает в 1 дополнительньЕЙ триггер, если имеетсй сигйал с , триггера 47 (при вводе № блоков памяти и страниц в БП 7), или обнуляет основной триггер, если триггер 47 находится в О (привводе № блоков памяти и страниц непосредственно, в перекрестные коммутаторы), что позволяет следующел импульсу опроса проходить беспрепитс1 венно через эту уже опрошенную ячейку и опрашивать следующую по строке ячейку После прохождения всех импульсов чик 27 вьщает сигнал, по которому все дополнительные триггеры ячеек матрицы 1 устанавливаются в О. Если триггер 47 находится в , то код № блока памяти из поля 1 выходного регистра АП 2 и код № страницы из регистра шифратора 9 записываются в последовательные ячейки памяти БП 7. Если триггер 47 находится в О, то коды с поля выходного регистра АП 2 и шифратора 9 поступают непосредственно в выходные перекрестные коммутаторы 16-17 через открытый коммутатор 15, Кроме того, если триггер 47 находится в О, то вьщеляемые процессору блоки памяти и страницы отображаются в АП 4, при этом в свободную строку АП 4 записьтаются коды кз полей 2, 4, 5, 7 выходного регистра АП 3 - о виде процессора (через инвертор), N9 абонента. его приоритете и № задачи - соответст ° ° 1.3 4,2 выделенной свобод регистров БП 6 этой f последоватепьно записываются № ° лТо xf ° Т регистра АП 2 и № страницы (в 2-е поле 2) из регистра шифратора 9. Когда регистр шифратора 9 пуст - имеется сигнал с дешифратора 24 или если триггер 47 в О, то вырабатывается сигнал начала обмена на вьгходе блока 28 и переходят к шагу 15, если триггер 47 в I, то переходят к шагу 10. Шаг 14. Сигналы с входа 29 блока 28, а также сигнал с входа 34 (от дешифратора 22 при пустом выходном регистре БП 6) устанавливают в триггер 54, сигнал с единичного выхода которого разрешает вьщачу кодов № блока памяти и JNo страницы из БП 7 через коммутатор 15 на выходные перекрестные коммутаторы 16-18, кроме того, при этом производитсяотображение в АП 2 и матрице 1 памяти освобождения или занятия страниц блоков памяти. Для этого с коммутатора 15 код № блока памяти поступает в АП 2, а код № страницы - на дешифратор 21. В АП 2 производится опрос по полю 1 и вьщеляется строка, соответствующая заданному блоку памяти. В ней устанавливается в О поле 2 (резервировацие) ив - поле 3 (блокировка по обмену, с процессором). А в матрице 1 рамяти, в выделенной строке по столбцу, указанному дешиЛоатооом 21 по коду № страницы, основной триггер устанавлива- . ется в О, если обслуживается запрос на Зц (это показывает что данная страница занята) или в , если обслуживается запрос на Чт, что показь.шает, что данная страница свободна. Кроме того, если обслуживае я запрос на Зп, в вьщеленной строке АП 2 поле 4 обнуляется, а если обслуживается запрос , на Чт, то код из поля 4 вьщеленной стро|ки вьшодится на выходной регистр, пере дается в операционный блок, где к нему прибавляется единица, а затем результирующий код из операционного блока 5 вновь вводится в поле 4 вьщеленной строки АЛ 2. Вьоделенные блоки памяти отображаются также в АП 4. При этом, если триггер 54 находится в 1 н сигнал с его единичного. выхода проходит т герез коммутатор 45 на АП 4 и БП 6, в АП 4 вьще ляется свободная строка и соответствующий ей блок регистров в БП 6. Затем в поля 1,2,3,4 вьзделенной строки заносятся коды соответственно из полей 2,7,4, 5 выходного регистра АП 3, а в регистры вьщеленного блока БП 6 последовательно записьюаются № блока памяти и страницы из БП 7. После вьшода последнегоадресаиз БП 7 СИГНШ1 с дешифратора 23 поступает на В.ХОД 35 блока 28 и устанавливает в О триггер 54, затем переходят к шагу 13., Шаг 15. Коды с коммутатора 15 поступают на перекрестны; ; коммутатор 17, а также код N9 блока памяти с коммутатс- ра 15 поступает на перекрестные коммутаторы 16 и 18. Перекрестный коммутатор .17 распрэделяет № страниц по блокам 11 управления выборкой, соответствуюшдм коду Ng блока памяти. . Перекрестный коммутатор 16 устанавливает в О (если обслуживается запрос на Чт) иди в 1 (если обслуживается запрсс на Зп), триггер в регистре 25, соответствующий блоку памяти, указанном в коде № блока памяти - таким образом задается направление обмена информацией Перекрестный коммутатор 18 передает код № блока памяти в свободный регистр того блока БП 8, который соответствует N9 процессора, подавшего запрос на обслу живание, код его № передается в пер&крестный коммутатор 18 из поля 1 выходного регистра АП 3. Сигнал о начале обмена с выхода блока 28 поступает на перекрестный комму- татор 2О и направляется из него к про цессору, код которого подается на комму татор 20 с поля 1 вьгхоДнЬго регистра АП 3 и инициирует начало обмена информацией. На этом обслуживание запроса заканчивается, устанавливаются в О триггеры блока 28 и происходит переход к шагу J. на обслуживание следующего заи са, В процессе обмена информацией между блоками памяти обмена и процессорами освобождаются от обмена отдельные блоки памяти, сигналы об этом из блоков 11 управления выборкой поступают на шифратор 10 и передаются в АЛ 2, в которой опросом по полю 1 вьщеляются соответствующие этим блокам памяти строки и обнуляется в них поле 3 (блокировка по обмену). Шаг 16. По сигналу отсутствия свободной памяти происходит обнуление поля 2 по всему АП 2, а этот сигнал, поступает на счетчик неудовлетворенных запросов 26, где к имеющемуся числу неудовлетворенных запросов - код из поля б выходного регистра АП 3, прибавляется единица в результирующее число заносится в поле 6 строки АП 3,.вьщеленной по коду с поля 1 выходного регистра АП 3 процессора, кроме того, сигни поступает в БП 7 и обнуляет его. Затем переходят в шаг 1-i Использование изобретения позволит повысить производительность работы многопроцессорной вычислительной системы за счет аппаратного решения функций распределения заданий по центральным про-. цеСсорам, процессорам обмена, а также за счет предотвращения взаимных помех и блокировок при обращении процессоров к памяти. ф о рмула изобретения 1. Устройство для управления памятью, содержащее матрицу ячеек памяти, первая и вторая группы в.ходов которой соединены с вькйдамй первых коммутатора и дешифратора, труппа выходов матрицы ячеек памяти соединена через первый шифратор с первой группой входов второго коммутато ра, блок управления выборкой из памяти, первая группа выходов которого через второй шифратор соединена с первыми входами первой ассоциативной памяти и первого перекрестного коммутатора, опера ционный блок, вторую а третью ассоциативные памяти, три буферных блока памяти, регистр, второй, третий, четвёртый, пятый перекрестные коммутаторы, тр&тий, четвертый коммутаторы, счетчик неудовлетворенных запросов, отличаю- щ е е с я тем, что, с целью повьш1ения коэффициента использования оборудования, в наго введены блок управления респреде. . j пени ем заданий, счетчик и три дешифратора, причем первая группа выходов первой ассоциативной памяти соединена с группой входов первого коммутатора, пер вый вход которого соединен с выходом счетчика и первым входом матрицы яч&ек памяти, второй аход которой соединен с выходом блока управления распределе нием заданий и первыми входами второй и третьей ассоциативных памятей и первой буферной памяти, выходы которой со единены с входами второго дешифратора, группой входов третьего коммутатора и второй группой входов второго тора, выходы которого через вторую буферную память соединены с входа ми третьего дешифратора н первой группой входов четвертого коммутатора, выходы которого соединены с входами второго перекрестного коммутатора входами первого дешифратора, вторыми, входами первой буферной памяти и перекрестного коммутатора и первым входом третьего перекрестного коммутатора, выходы которого через третью буферную память соединены с четвертым перекрестным коммутаторок выходы второй группы первой ассоциативной памяти соединены с первым входом счетчика, третьей группой входов второго коммутатора и второй группой входов четвертого коммутатора и первым аходом операционного блока, выход первой ассоциативной памяти соединен со вторым .входом счетчика, первым входом счетчика неудовлетворенных запросов, вторым входом операционного блока, третьим входом первой буферной памяти и первым входом блока управления распределением заданий, второй и третий входы которого соединены с выходами соответственно . .второй и третьей ассоциативных пaмятeйi выходы второй ассоциативной памяти соединены с вторьгми аходйми счётчика не удовлетворенных, запросов, третьего пере крестного коммутатора, первой и третьей ассоциативных памятей, третьими входами первого перекрестного коммутатора, счетчика, операционного блока, четвертым вх.о дом блока управления распределением заданий и через пятый перекрестный коммутатор - с первой группой выходов устройства, выходы третьего коммутатора со&динены с третьим входом первой ассоциативной памяти, выходы второго перекрестного комму йтора соединены- со входами блока управления вьтборкой из памяти, вь ходы первого шифратора соединены со входами четвертого дешифратора, выходы операционного блока, второго, третьего и четвертого дешифраторов соединены соответственно с пятым, шестым, седьмым и восьмым входами блока управления распределением заданий, выход которого соединен с управляющими входами первого, вторр1Ч), третьего и четвертого коммутаjTOpOB, второй буферной памяти и первой ассоциативной памяти, выходы первого шифратора соединены с третьей группой входов четвертого коммутатора, выходы регистра, блока управления выборкой из |памяти, пятого перекрес5тного коммутатора соединены с второй, третьей и четверрой группой выходов устройства соответртвенно. I 2, Устройство по п. 1, отличающее с я тем, что блок управления распределением заданий содержит генер jTop, коммутаторы, триггеры, элементы ИЛИ, И, причем первьй вход блока сое ди&ен с первыми входами первого и второго триггеров, первого элемента ИЛИ, ;группой входов первого коммутатора, первым входом второго и третьего коммутаторов и через второй элемент ИЛИ - с ; выходом блока, второй вход блока соеди нен с первьшн входами третьего триггера, первого и второго элементов И, третий аход блока соединен с первым входом четвертого элембнта И и вторым входом первого элемента ИЛИ четвертый вход блока через первый и второй элементы И соединен с первыми входами соответственно пятого и шестого триггеров, пятый вход блока соединен с первьм входом седьмого триггера, шестой вход блока соединен с первым входом третьего,элемента И, седьмой вход блока соединен с первыми входами восьмого триггера, четвертого и пятого элементов И, .восьмой вход блока соединен с первым входом девятого триггера и через пятый элемеет ;И р- с выходом блока, третьим аходом пер вого элемента ИЛИ и вторыми входами ПЯТОГО и шестого триггеров, первый вы--. .ход первого коммутатора соединен со |вторь1ми входами второго и четвертого триггеров, второй , третий и четвертый выходы первого комомутатора соединены со вторыми входами соответственно пер:вого, седьмого и восьмого триггеров, пятый выход первого коммутатора соедн|Нен с первым входом шестого элемента И, первый выход первого триггера соедиен с выходом блока второй выход первого триггера соединен с выходом блрка и первым входбм второго коммутатора, первый выход второго триггера соединен с выходом блока и вторым входок треть 1974го элемента tl, выход которого соединен с первым входом первого коммутатора, второй и третий аходы которого соединены с выход акш третьего И седьмого aneMBHfOB И соответственно, второй выход второго триггера соединен с первым входом восьмого элемента И, первый выход третьего триггера соединен с первым входом девятого элемента И, второй вььход третьего триггера соединен с вькодом блока, первый выход четвертого триггера соединен с выходом блока, второй выход четвертого триггера соединен с выходом блока и вторым входом четвертого элемента И, первый выход пятого триггера соединен с выходом блока, вторыми входами второго и третьего коммутаторов, четвертого элемента И и первым входом десятого элемента И, второй выход шггого триггера соединен с выходом блока и вторым входом девятого злемеета И, аерв1 й выход шестого триггера соединен с выходом блока, третьим входом третье., го коммутатора и первым входом седьмого элемента И и через восьмой элемент И - с выходом блока, второй выход шесто го триггера соединен с выходом блока н& посредстаггчно и через девятый элемент И, первый аьйсод седьмого триггера соединен с выходом ,блока, второй выход седь мого триггера соединен с выходом блока и вторым входом десятого элемента И, первый выход восьмого триггера соединен с выходом блока, третьим входом второго коммутатора и вторым входом седьмого элемента И, второй выход восьмого триггера соединен с тр&тьими входами восьмого и десятого элементов И, первым входом третьего элемента ИЛИ и через шестой элемент И со вторым входом девятого триггера, первый выход Которого соединен с первым входом одиннадцатого элемента И и через третий элемент ИЛИ - с первым входом десятого триггера, первый выход которого соединен с выходом блока, второй выход десятого триггера соединен с выходом блока и четвертым входом десятого элемента И, второй выход девятого триггера через десятый элемент И соединен с выходом блока, выходы второго и третьего коммутаторов соединены соответственно с выходом блока и вторым входом десятого триггера, первый выход шестого трих гера через восьмой элемент И соединен с выходом блока выход первого элемента ИЛИ соединен со вторым входом третьего триггера, выход генератора через одиннадцатый элемент И соединен с выходом блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР по заявке № 2516429/18-24, кл. Q 06 F 15/20, 1977. 2,Авторское свидетельство СССР № 283685, кл. 6 06 F 9/06 1969 (прототип).

Авторы

Даты

1980-07-15—Публикация

1977-12-08—Подача