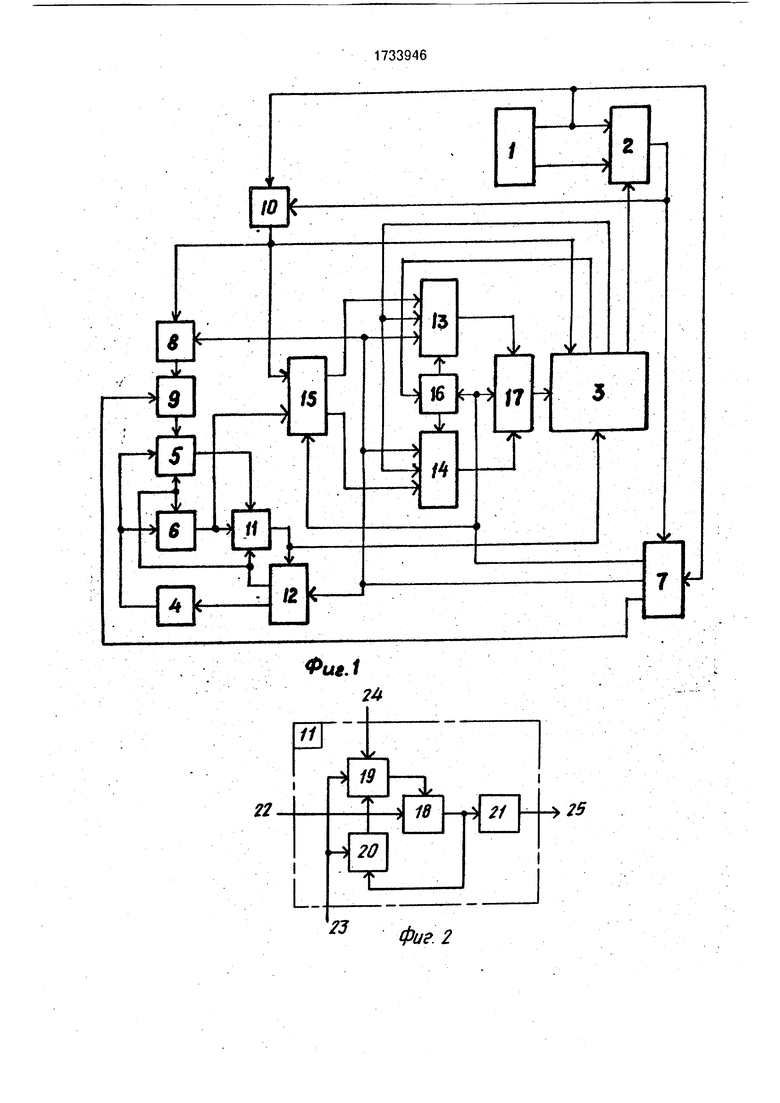

регистр 9 периода угловых меток. Первый и второй выходы формирователя 1 соединены соответственно с установочным и счетным входами блока 2, управляющий вход блока 2 соединен с первым управляющим выходом блока 3. Выход генератора 4 соединен с счетным входом управляемого делителя 5. Выход счетчика 8 соединен с кодовым входом регистра 9, вход записи которого соединен с первым выходом блока 7, второй выход-которого соединен с установочным входом счетчика 8, а первый вход соединен с вторым выходом формирователя 1.

В устройство введены умножитель 10 частоты, временной селектор 11 импульсов выборок, блок 12 счета импульсов выборок, первый и второй блоки 13 и 14 буферной памяти, переключатель 15 импульсов адресации, переключатель 16 импульсов записи и переключатель 17 данных. Импульсный вход умножителя 10 соединен с вторым выходом формирователя 1, управляющий вход соединен с выходом блока 2 и с вторым входом блока 7, а выход соединен с первым синхронизирующим входом блока 3, с первым входом переключателя 15 и со счетным входом счетчика 8. Выход регистра 9 соединен с управляющим входом управляемого делителя 5, импульсный выход которого соединен с опорным входом временного селектора 11, а установочный вход соединен с импульсным выходом блока 12 и с установочными входами временного селектора 11 и делителя 6. Счетный вход делителя 6 соединен с выходом генератора 4, а потенциальный выход соединен с вторым входом переключателя 15 и с импульсным входом временного селектора 11, выход которого соединен с вторым синхронизирующим входом блока 3 и со счетным входом блока 12, Потенциальный выход блока 12 соединен с управляющим входом генератора 4, а вход запуска соединен с установочными входами блоков 13 и 14 и с вторым выходом блока 7, третий выход которого соединен с управляющими входами переключателей 15-17. Первый и второй выходы переключателя 15 соединены с входами адресации соответственно блоков 13 и 14, входы данных которых соединены с выходом данных блока 3, входы записи соединены соответственно с первым и вторым выходами переключателя 16, а выходы - соответственно с первым и вторым входами данных переключателя 17. Выход переключателя 17 соединен с входом данных блока 3, второй управляющий выход которого соединен с импульсным входом переключателя 16.

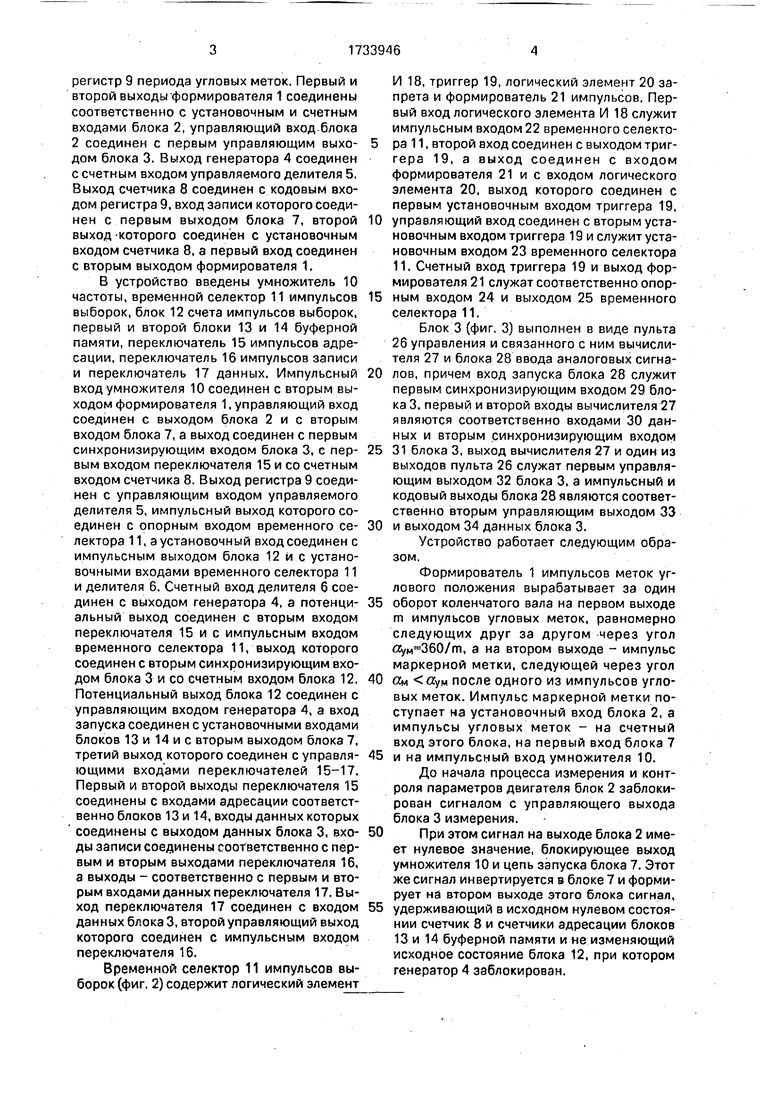

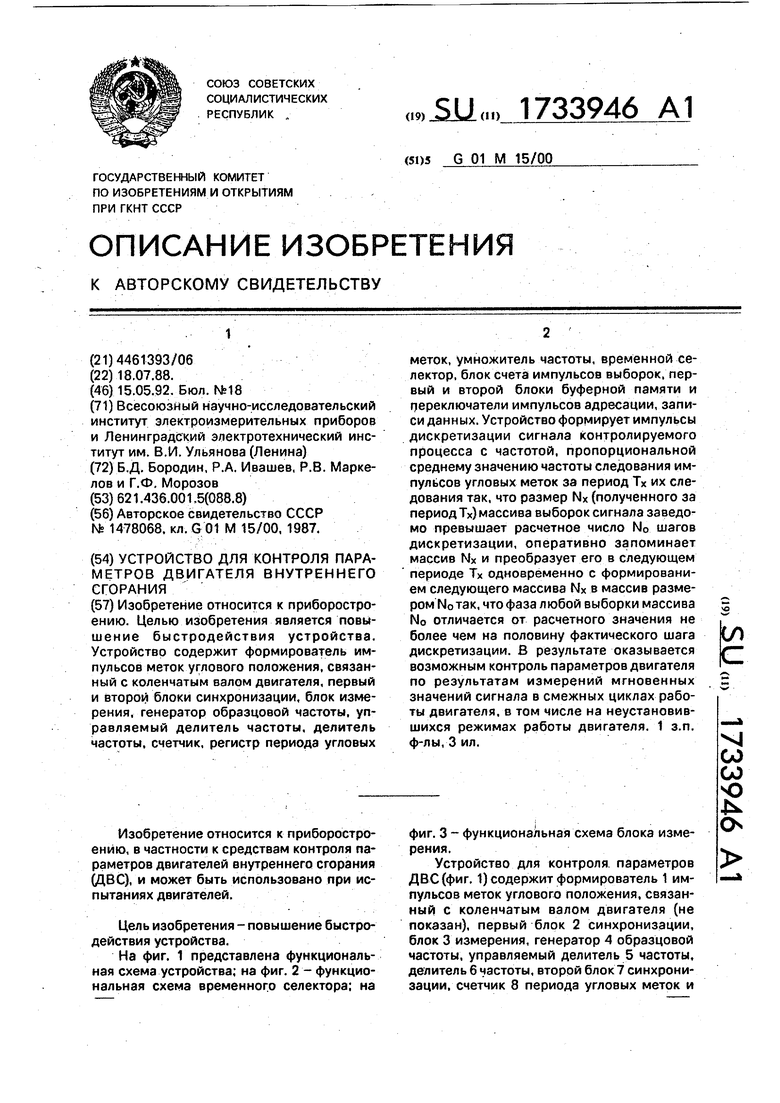

Временной селектор 11 импульсов выборок (фиг. 2) содержит логический элемент

И 18, триггер 19, логический элемент 20 запрета и формирователь 21 импульсов. Первый вход логического элемента И 18 служит импульсным входом 22 временного селектора 11, второй вход соединен с выходом триг- гера 19, а выход соединен с входом формирователя 21 и с входом логического элемента 20, выход которого соединен с первым установочным входом триггера 19,

управляющий вход соединен с вторым установочным входом триггера 19 и служит установочным входом 23 временного селектора 11. Счетный вход триггера 19 и выход формирователя 21 служат соответствен но опорным входом 24 и выходом 25 временного селектора 11.

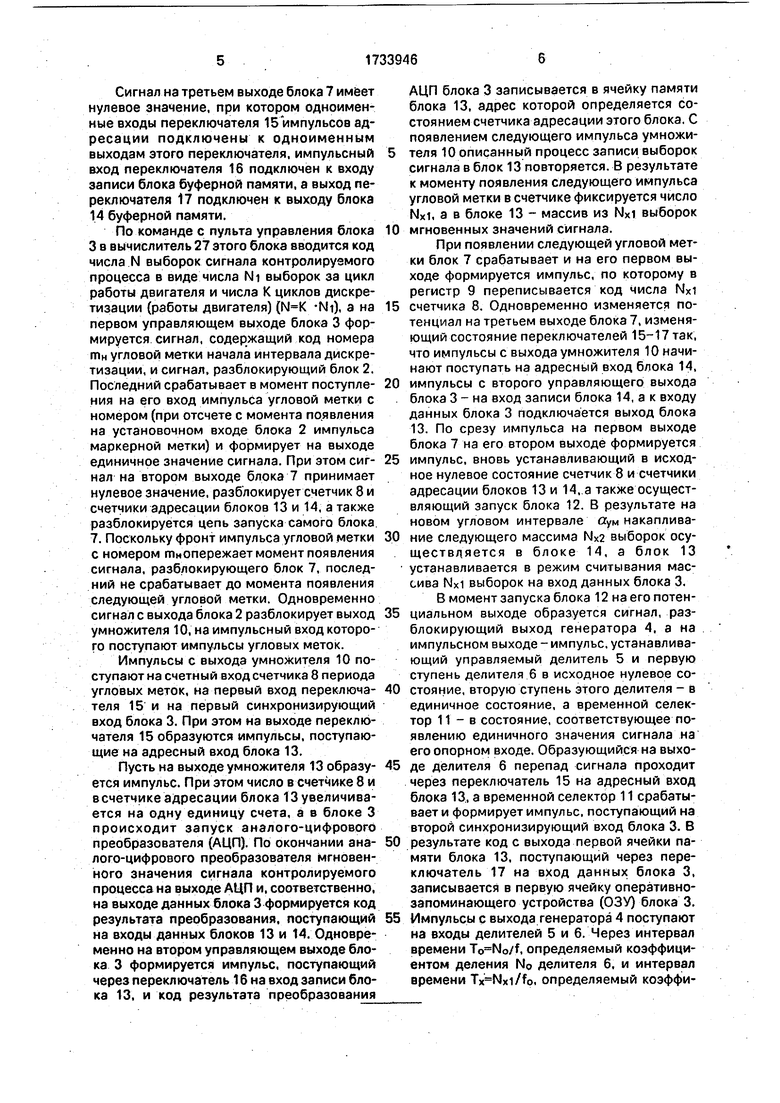

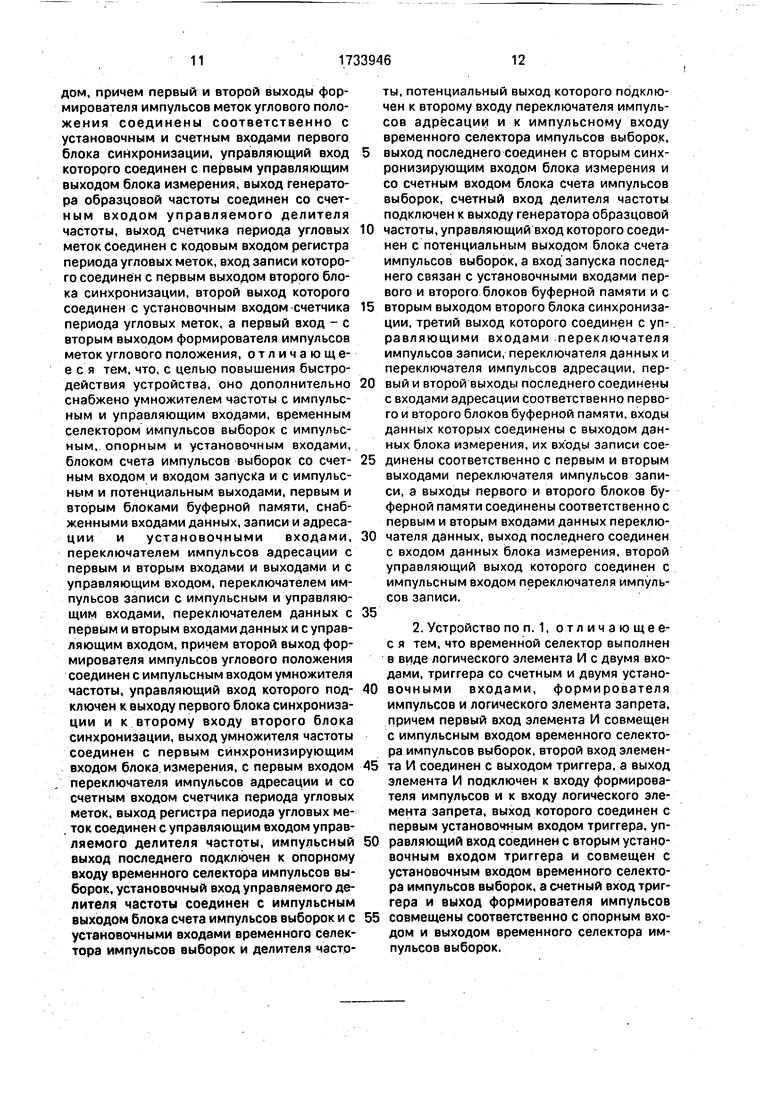

Блок 3 (фиг. 3) выполнен в виде пульта 26 управления и связанного с ним вычислителя 27 и блока 28 ввода аналоговых сигналов, причем вход запуска блока 28 служит первым синхронизирующим входом 29 блока 3, первый и второй входы вычислителя 27 являются соответственно входами 30 данных и вторым синхронизирующим входом

31 блока 3, выход вычислителя 27 и один из выходов пульта 26 служат первым управляющим выходом 32 блока 3, а импульсный и кодовый выходы блока 28 являются соответственно вторым управляющим выходом 33

и выходом 34 данных блока 3.

Устройство работает следующим образом.

Формирователь 1 импульсов меток углового положения вырабатывает за один

оборот коленчатого вала на первом выходе m импульсов угловых меток, равномерно следующих друг за другом через угол Оум 360/т, а на втором выходе - импульс маркерной метки, следующей через угол

«м «Ум после одного из импульсов угловых меток. Импульс маркерной метки поступает на установочный вход блока 2, а импульсы угловых меток - на счетный вход этого блока, на первый вход блока 7

и на импульсный вход умножителя 10.

До начала процесса измерения и контроля параметров двигателя блок 2 заблокирован сигналом с управляющего выхода блока 3 измерения.

При этом сигнал на выходе блока 2 имеет нулевое значение, блокирующее выход умножителя 10 и цепь запуска блока 7. Этот же сигнал инвертируется в блоке 7 и формирует на втором выходе этого блока сигнал,

удерживающий в исходном нулевом состоянии счетчик 8 и счетчики адресации блоков 13 и 14 буферной памяти и не изменяющий исходное состояние блока 12, при котором генератор 4 заблокирован.

Сигнал на третьем выходе блока 7 имеет нулевое значение, при котором одноименные входы переключателя 15 импульсов адресации подключены к одноименным выходам этого переключателя, импульсный вход переключателя 16 подключен к входу записи блока буферной памяти, а выход переключателя 17 подключен к выходу блока 14 буферной памяти.

По команде с пульта управления блока 3 в вычислитель 27 этого блока вводится код числа N выборок сигнала контролируемого процесса в виде числа NI выборок за цикл работы двигателя и числа К циклов дискретизации (работы двигателя) ( -Ni), а на первом управляющем выходе блока 3 формируется сигнал, содержащий код номера гпн угловой метки начала интервала дискретизации, и сигнал, разблокирующий блок 2. Последний срабатывает в момент поступления на его вход импульса угловой метки с номером (при отсчете с момента появления на установочном входе блока 2 импульса маркерной метки) и формирует на выходе единичное значение сигнала. При этом сигнал на втором выходе блока 7 принимает нулевое значение, разблокирует счетчик 8 и счетчики адресации блоков 13 и 14, а также разблокируется цепь запуска самого блока 7. Поскольку фронт импульса угловой метки с номером тмопережает момент появления сигнала, разблокирующего блок 7, последний не срабатывает до момента появления следующей угловой метки. Одновременно сигнал с выхода блока 2 разблокирует выход умножителя 10, на импульсный вход которого поступают импульсы угловых меток.

Импульсы с выхода умножителя 10 поступают на счетный вход счетчика 8 периода угловых меток, на первый вход переключателя 15 и на первый синхронизирующий вход блока 3. При этом на выходе переключателя 15 образуются импульсы, поступающие на адресный вход блока 13.

Пусть на выходе умножителя 13 образуется импульс. При этом число в счетчике 8 и в счетчике адресации блока 13 увеличивается на одну единицу счета, а в блоке 3 происходит запуск аналого-цифрового преобразователя (АЦП). По окончании аналого-цифрового преобразователя мгновенного значения сигнала контролируемого процесса на выходе АЦП и, соответственно, на выходе данных блока 3 формируется код результата преобразования, поступающий на входы данных блоков 13 и 14. Одновременно на втором управляющем выходе блока 3 формируется импульс, поступающий через переключатель 16 на вход записи блока 13, и код результата преобразования

АЦП блока 3 записывается в ячейку памяти блока 13, адрес которой определяется состоянием счетчика адресации этого блока. С появлением следующего импульса умножи- 5 теля 10 описанный процесс записи выборок сигнала в блок 13 повторяется. В результате к моменту появления следующего импульса угловой метки в счетчике фиксируется число Nxi, а в блоке 13 - массив из Nxi выборок

0 мгновенных значений сигнала.

При появлении следующей угловой метки блок 7 срабатывает и на его первом выходе формируется импульс, по которому в регистр 9 переписывается код числа Nxi

5 счетчика 8. Одновременно изменяется потенциал на третьем выходе блока 7, изменяющий состояние переключателей 15-17 так, что импульсы с выхода умножителя 10 начинают поступать на адресный вход блока 14,

0 импульсы с второго управляющего выхода блока 3 - на вход записи блока 14, а к входу данных блока 3 подключается выход блока 13. По срезу импульса на первом выходе блока 7 на его втором выходе формируется

5 импульс, вновь устанавливающий в исходное нулевое состояние счетчик 8 и счетчики адресации блоков 13 и 14, а также осуществляющий запуск блока 12. В результате на новом угловом интервале аум накаллива0 ние следующего массима NX2 выборок осуществляется в блоке 14, а блок 13 устанавливается в режим считывания массива Nxi выборок на вход данных блока 3. В момент запуска блока 12 наегопотен5 циальном выходе образуется сигнал, разблокирующий выход генератора 4, а на импульсном выходе - импульс, устанавливающий управляемый делитель 5 и первую ступень делителя 6 в исходное нулевое со0 стояние, вторую ступень этого делителя - в единичное состояние, а временной селектор 11 - в состояние, соответствующее появлению единичного значения сигнала на его опорном входе. Образующийся на выхо5 де делителя 6 перепад сигнала проходит через переключатель 15 на адресный вход блока 13, а временной селектор 11 срабатывает и формирует импульс, поступающий на второй синхронизирующий вход блока 3. В

0 результате код с выхода первой ячейки памяти блока 13, поступающий через переключатель 17 на вход данных блока 3, записывается в первую ячейку оперативно- запоминающего устройства (ОЗУ) блока 3.

5 Импульсы с выхода генератора 4 поступают на входы делителей 5 и 6. Через интервал времени , определяемый коэффициентом деления No делителя 6, и интервал времени Tx Nxi/f0, определяемый коэффициентом деления управляемого делителя 5, равным значению кода регистра 9, появляются импульсы соответственно на выходах делителей 6 и 5. Импульс с выхода делителя 6 наращивает адрес ячеек блока 13, а в момент появления импульса на выходе делите- ля 5 временной селектор 11 вновь срабатывает и код с выхода второй ячейки блока 13 записывается во вторую ячейку ОЗУ блока 3. Процесс наращивания адресов ячеек 5лока 13 и записи данных в ОЗУ блока 3 продолжается до появления на выходе делителя 6 импульса, срез которого опережает момент появления импульса на выходе делителя 5. В результате временной селектор 11 срабатывает только в момент появления следующего импульса на выходе делителя б, вновь изменяющего адрес ячейки блока 13, а запись в ОЗУ блока 3 кода, хранящегося в ячейке блока 13 с предыдущим адресом, не производится. Импульсы с выхода временного селектора 11 одновременно подсчитываются блоком 12. Последний срабатывает в момент поступления на его счетный вход N0 импульсов и блокирует генератор 4.

Таким образом, в ОЗУ блока 3 из NX1 выборок, хранящихся в блоке 13, переписываются только No выборок, фазы которых отличаются от расчетных не более чем на половину реального шага дискретизации, а ос- тальные NX-N0 выборок массива NX1 отбрасываются.

С приходом следующего импульса угловой метки вновь изменяется положение переключателей 15-17 и происходит запуск блока 12. Аналогично описанному в блок 13 записывается массив выборок, а М0 выборок массива NX2 переписывается в ОЗУ блока 3.

При (N-Ni) описанный процесс дискретизации продолжается до поступления на второй синхронизирующий вход блока 3 NI импульсов. В этот момент блок 3 формирует единичный сигнал, блокирующий блок 2, и процесс дискретизации прекращается. При и No после поступления очередной серии NI импульсов блок 3 формирует короткий импульс, сбрасывающий выходной триггер блока 2 в исходное нулевое состояние и прекращающий процесс дискретизации до момента появления очередной угловой метки с номером

ГПн.

При и блок 3 формирует единичный сигнал, блокирующий блок 2 после поступления импульсов, т.е. процесс дискретизации продолжается до этого момента непрерывно.

При , начиная с второго массива NI выборок, -коды синфазных выборок суммируются в одноименных ячейках ОЗУ блока 3, а после окончания записи N выборок вычислитель блока 3 осуществляет усреднение полученных значений.

После окончания процесса дискретизации () или после окончания процесса усреднения синфазных выборок ()

0 вычислитель блока 3 производит расчет и контроль параметров, например, индикаторной диаграммы контролируемого цилиндра двигателя.

Результаты измерений и контроля выво5 дятся на экран дисплея блока 27, входящего в блок 3 измерения, и могут быть зарегистрированы на бланке печатающего устройства этого блока.

Временной селектор 11 импульсов вы0 борок работает следующим образом (фиг. 2). В исходном состоянии временного селектора 11 сигналы на импульсном входе 22 и на выходе триггера 19 имеют нулевое значение и блокируют логический элемент И 18 соот5 ветственно по первому и второму входам и сигнал на его выходе также имеет нулевое значение. Элемент 20 запрета разблокирован.

При поступлении импульса на устано0 вочный вход 23 элемент20 запрета блокируется, а триггер 19 срабатывает и разблокирует элемент И 18 по второму входу. Одновременно на импульсном входе 22 появляется первый импульс последователь5 ности Т0, имеющий скважность , и элемент 18 И разблокируется также и по первому входу. В результате сигнал на выходе логического элемента И 18 принимает единичное значение, вызывающее срабаты0 вание формирователя 21, и на выходе 25 временного селектора 11 появляется первый импульс, поступающий на второй синхронизирующий вход блока 3. После окончания импульса на установочном входе

5 23 логический элемент 20 запрета разблокируется и сигнал с выхода логического элемента И 18 сбрасывает триггер 19 в исходное состояние. Элемент И 18 вновь блокируется по второму входу, а через ин0 тервал Т0/2 блокируется также и по первому входу паузой сигнала на импульсном входе 22.

Через интервал Т0 и после появления первого импульса на выходе 25 появ5 ляются импульсы соответственно на импульсном 22.и опорном 24 входах. Импульс, появляющийся на опорном входе 24, поступает на счетный вход триггера 19 и вызывает его срабатывание, в результате чего элемент И 18 вновь оказывается разблокированным по обоим входам и на выходе 25 формируется следующий импульс. Одновременно сигнал с выхода элемента И 18 поступает через разблокированный элемент 20 запрета на установочный вход триг- гера 19 и вызывает его обратное срабатывание. Элемент И 18 вновь блокируется по второму входу, а через некоторый интервал времени также и по первому паузой сигнала на импульсндм входе 22.

Описанный процесс формирования импульсов на выходе 25 продолжается до появления импульса на импульсном входе 22, срез которого запаздывает относительно момента появления импульса на опорном входе 24. В результате в момент появления импульса на опорном входе 24, вызывающего срабатывание триггера 19. элемент И 18 оказывается разблокированным только по второму входу и формирования импульса- отклика на выходе 25 на появление прошедшего импульса на импульсном входе 22 не происходит. К моменту появления следующего импульса на импульсном входе 22 триггер 19 остается в единичном состоянии, элемент И 18 оказывается разблокированным по обоим входам и на выходе 25 вновь формируется импульс.

Блок 3 измерения работает следующим образом (фиг. 4). Перед началом измерения и контроля параметров двигателя по сигналам с пульта 27 управления включается один из измерительных каналов коммутатора блока 28 ввода аналоговых сигналов, в вычислитель 27 вводится код числа N выборок м: н ззенных значений контролируемого процесса в виде числа NI выборок за цикл работы двигателя и числа К циклов работы двигателя, а на выходе 32 формируется многолинейный сигнал, содержащий код номера угловой метки начала интервала дискретизации. Однолинейный сигнал на выходе 32 формируется вычислителем 27 и имеет единичное значение, блокирующее блок 2 устройства.

По команде Пуск, формируемой на выходе пульта 26, однолинейный сигнал на выходе вычислителя 27 принимает нулевое значение, разблокирующее блок 2 устройства, а на первый синхронизирующий вход 29 блока 3 начинают поступать импульсы запуска АЦП блока 28. По окончании очередного аналого-цифрового преобразования блок 28 формирует на выходе 34 данных код результата преобразования, а на втором управляющем выходе 33 - импульсный сигнал. В процессе дискретизации коды выборок массивов No поступают на вход 30 данных блока 3 и записываются в ячейки ОЗУ

вычислителя 27 по сигналам, поступающим на второй синхронизирующий вход блока 3. В случае , при поступлении на второй синхронизирующий 30 вход блока 3 5 NI импульсов вычислитель 27 формирует на выходе 32 единичное значение, блокирующее блок 2. и процесс дискретизации прекращается.

Пусть контроль параметров двигателя 0 производится за К циклов его работы, а число NI меньше максимально возможного значения ISIim m No. Тогда при поступлении на второй синхронизирующий выход 30 очередной серии из NI импульсов вычислитель

5 27 формирует на выходе 32 блока 3 короткий импульс, сбрасывающий выходной триггер блока 2 устройства в исходное нулевое состояние и прекращающий процесс дискретизации до появления очередной угловой

0 метки с номером тн.

При и вычислитель 27 формирует на выходе 32 блока 3 единичное зна- чение после поступления на второй синхронизирующий вход этого блока N им5 пульсов выборок, т.е. процесс дискретизации продолжается до этого момента непрерывно.

При , начиная с второго массива NI выборок, коды синфазных выборок сумми0 руются в одноименных ячейках ОЗУ вычислителя 27, а операция усреднения осуществляется после окончания записи N числа выборок.

После окончания процесса дискретиза5 ции () или усреднения () вычислитель 27 блока 3 производит расчет и контроль параметров контролируемого процесса, результаты контроля выводятся на экран дисплея вычислителя 27.

0 Формула изобретения

1. Устройство для контроля параметров двигателя внутреннего сгорания, содержащее формирователь импульсов меток углового положения, связанный с коленчатым

5 валом двигателя, первый блок синхронизации с установочным, счетным и управляющим входами, блок измерения с выходом и входом данных, первым и вторым синхронизирующими входами и первым и вторым уп0 равляющими выходами, генератор образцовой частоты с управляющим входом, управляемый делитель частоты со счетным, управляющим и установочными входами, делитель частоты со счетным и ус5 тановочным входами, второй блок синхронизации с первым и вторым входами и первым, вторым и третьим выходами, счетчик периода угловых меток с установочным и счетным входами и регистр периода угловых меток с входом записи и кодовым входом, причем первый и второй выходы формирователя импульсов меток углового поло- жения соединены соответственно с установочным и счетным входами первого блока синхронизации, управляющий вход которого соединен с первым управляющим выходом блока измерения, выход генератора образцовой частоты соединен со счет- ным входом управляемого делителя частоты, выход счетчика периода угловых меток соединен с кодовым входом регистра периода угловых меток, вход записи которого соединен с первым выходом второго блока синхронизации, второй выход которого соединен с установочным входом счетчика периода угловых меток, а первый вход - с вторым выходом формирователя импульсов меток углового положения, отличающееся тем, что, с целью повышения быстродействия устройства, оно дополнительно снабжено умножителем частоты с импульсным и управляющим входами, временным селектором импульсов выборок с импульсным, опорным и установочным входами, блоком счета импульсов выборок со счетным входом и входом запуска и с импульсным и потенциальным выходами, первым и вторым блоками буферной памяти, снабженными входами данных, записи и адресации и установочными входами, переключателем импульсов адресации с первым и вторым входами и выходами и с управляющим входом, переключателем импульсов записи с импульсным и управляющим входами, переключателем данных с первым и вторым входами данных и с управляющим входом, причем второй выход формирователя импульсов углового положения соединен с импульсным входом умножителя частоты, управляющий вход которого подключен к выходу первого блока синхронизации и к второму входу второго блока синхронизации, выход умножителя частоты соединен с первым синхронизирующим входом блока измерения, с первым входом переключателя импульсов адресации и со счетным входом счетчика периода угловых меток, выход регистра периода угловых ме- . ток соединен с управляющим входом управляемого делителя частоты, импульсный выход последнего подключен к опорному входу временного селектора импульсов выборок, установочный вход управляемого делителя частоты соединен с импульсным выходом блока счета импульсов выборок и с установочными входами временного селектора импульсов выборок и делителя частоты, потенциальный выход которого подключен к второму входу переключателя импульсов адресации и к импульсному входу временного селектора импульсов выборок,

выход последнего соединен с вторым синхронизирующим входом блока измерения и со счетным входом блока счета импульсов выборок, счетный вход делителя частоты подключен к выходу генератора образцовой

частоты, управляющий вход которого соединен с потенциальным выходом блока счета импульсов выборок, а вход запуска последнего связан с установочными входами первого и второго блоков буферной памяти и с

вторым выходом второго блока синхронизации, третий выход которого соединен с управляющими входами переключателя импульсов записи, переключателя данных и переключателя импульсов адресации, первый и второй выходы последнего соединены с входами адресации соответственно первого и второго блоков буферной памяти, входы данных которых соединены с выходом данных блока измерения, их входы записи соединены соответственно с первым и вторым выходами переключателя импульсов записи, а выходы первого и второго блоков буферной памяти соединены соответственно с первым и вторым входами данных переключателя данных, выход последнего соединен с входом данных блока измерения, второй управляющий выход которого соединен с импульсным входом переключателя импульсов записи.

2. Устройство по п. 1, отличэющее- с я тем, что временной селектор выполнен в виде логического элемента И с двумя входами, триггера со счетным и двумя установочными входами, формирователя импульсов и логического элемента запрета, причем первый вход элемента И совмещен с импульсным входом временного селектора импульсов выборок, второй вход элемента И соединен с выходом триггера, а выход элемента И подключен к входу формирователя импульсов и к входу логического элемента запрета, выход которого соединен с первым установочным входом триггера, управляющий вход соединен с вторым установочным входом триггера и совмещен с установочным входом временного селектора импульсов выборок, а счетный вход триггера и выход формирователя импульсов

совмещены соответственно с опорным входом и выходом временного селектора импульсов выборок.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2208771C2 |

| Устройство для измерения мощности цилиндров двигателя внутреннего сгорания | 1990 |

|

SU1789898A1 |

| Способ определения технического состояния двигателей внутреннего сгорания и устройство для его осуществления | 2018 |

|

RU2721992C1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2018 |

|

RU2694108C1 |

| Устройство для измерения мощности двигателя | 1982 |

|

SU1030678A1 |

| Фазоизбирательное устройство | 1984 |

|

SU1257556A1 |

| Устройство для измерения мощности | 1976 |

|

SU601586A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Устройства для вибрационной сейсморазведки | 1987 |

|

SU1566315A1 |

Изобретение относится к приборостроению. Целью изобретения является повы- шение быстродействия устройства. Устройство содержит формирователь импульсов меток углового положения, связанный с коленчатым валом двигателя, первый и второй блоки синхронизации, блок измерения, генератор образцовой частоты, управляемый делитель частоты, делитель частоты, счетчик, регистр периода угловых Изобретение относится к приборостроению, в частности к средствам контроля параметров двигателей внутреннего сгорания (ДВС), и может быть использовано при испытаниях двигателей. Цель изобретения - повышение быстродействия устройства. На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема временного селектора; на меток, умножитель частоты, временной селектор, блок счета импульсов выборок, первый и второй блоки буферной памяти и Переключатели импульсов адресации, записи данных. Устройство формирует импульсы дискретизации сигнала контролируемого процесса с частотой, пропорциональной среднему значению частоты следования импульсов угловых меток за период Тх их следования так, что размер Nx (полученного за период Тх) массива выборок сигнала заведомо превышает расчетное число N0 шагов дискретизации, оперативно запоминает массив NX и преобразует его в следующем периоде Тх одновременно с формированием следующего массива NX в массив размером No так, что фаза любой выборки массива No отличается от расчетного значения не более чем на половину фактического шага дискретизации. В результате оказывается возможным контроль параметров двигателя по результатам измерений мгновенных значений сигнала в смежных циклах работы двигателя, в том числе на неустановившихся режимах работы двигателя. 1 з.п. ф-лы, 3 ил. фиг. 3 - функциональная схема блока измерения. Устройство для контроля параметров ДВС (фиг. 1) содержит формирователь 1 импульсов меток углового положения, связанный с коленчатым валом двигателя (не показан), первый блок 2 синхронизации, блок 3 измерения, генератор 4 образцовой частоты, управляемый делитель 5 частоты, делитель 6 частоты, второй блок синхронизации, счетчик 8 периода угловых меток и СО с XI СА GJ 2 Оч

22

L

/J

18

21

25

Фиг. 2

31

29 33 34 32

Фиг 3

| Устройство для контроля параметров двигателя внутреннего сгорания | 1985 |

|

SU1478068A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-05-15—Публикация

1988-07-18—Подача